National Semiconductor

## ADC12EU050

## Ultra-Low Power, Octal, 12-bit, 40-50 MSPS Sigma-Delta Analog-to-Digital Converter

## **General Description**

The ADC12EU050 is a 12-bit, ultra-low power, octal A/D converter for use in high performance analog to digital applications. The ADC12EU050 uses an innovative continuous time sigma delta architecture offering ultra low power consumption and an alias free sample bandwidth up to 25MHz. The input stage of each channel features a proprietary system to ensure instantaneous recovery from overdrive. Instant overload recovery (IOR) with no memory effect guarantees the elimination of phase errors resulting from out of range input signals. The ADC12EU050 reduces interconnection complexity by using programmable serialized outputs which offer the industry standard LVDS and SLVS modes. Power consumption of only 48mW per channel @ 50MSPS gives a total chip power consumption of 384mW. The ADC12EU050 can operate entirely from a 1.2V supply, although a separate output driver supply of up to 1.8V can be used. The device operates from -40 to +85 °C and is supplied in a 10 x 10 mm<sup>2</sup>, 68 pin package.

## **Features**

- CT∑∆ ADC architecture with 40-50MSPS throughput

- Anti-alias filter free Nyquist sample range

- Unique Instant Overload Recovery (IOR)

- Wide 2.10 V<sub>PP</sub> input range

- 1.2V supply voltage

- Integrated precision LC PLL

- Serial control via SPI compatible interface

## **Key Specifications**

- Resolution Conversion Rate

- SNR 69.3 dBFS (typ) @ 50 MSPS

- THD

- THD

- Per Channel Power

- Total Active Power

- Inter-Channel Isolation

- Operating Temp. Range

## **Applications**

- Medical imaging, ultrasound

- Industrial ultrasound, such as non-destructive testing

- Communications

- Battery powered portable systems

## Julv 6. 2009

12 Bits

40 to 50 MSPS

f<sub>IN</sub> = 4.4MHz

$f_{IN} = 4.4 MHz$

-40 to +85 °C

-76.6 dB (typ) @ 50 MSPS

48 mW/ch (typ) @ 50MSPS

385 mW (typ) @ 50MSPS

>110 dB @ f<sub>IN</sub> = 4.4MHz

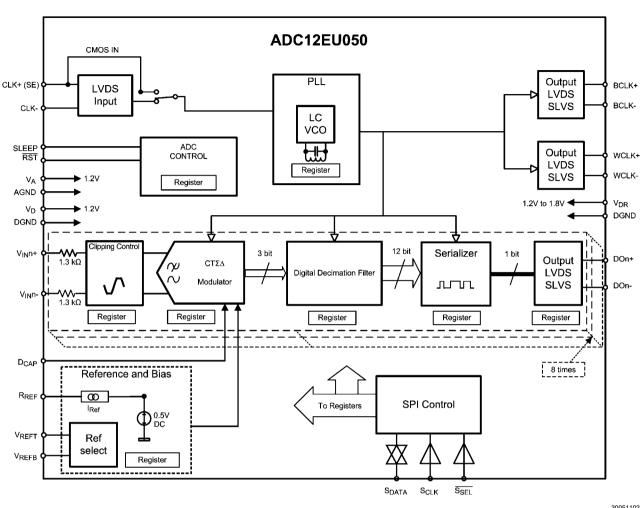

## **Block Diagram**

## **Ordering Information**

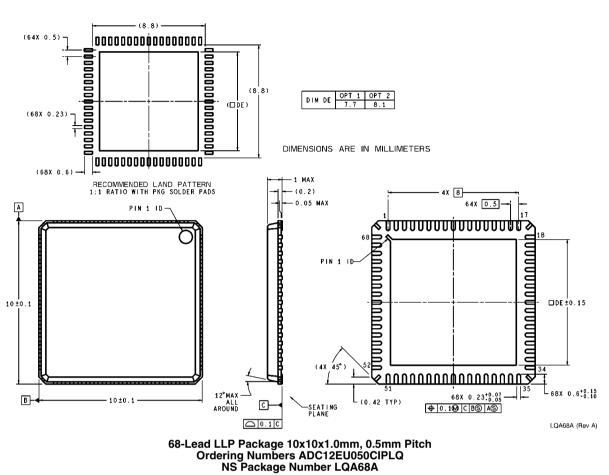

| Industrial (–40°C ≤ T <sub>A</sub> ≤ +85°C) | Package          |  |

|---------------------------------------------|------------------|--|

| ADC12EU050CIPLQ                             | 68 Pin LLP       |  |

| ADC12EU050EB                                | Evaluation Board |  |

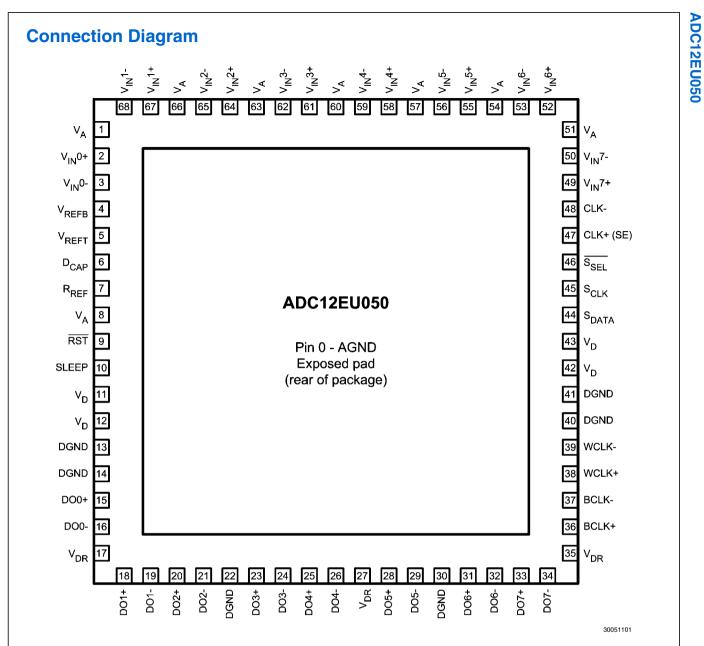

| Pin No.     | Name               | Туре         | Function and Connection                                                                                                                                                                                                                                                                                                                                                         |

|-------------|--------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ANALOG I/O  | •                  |              |                                                                                                                                                                                                                                                                                                                                                                                 |

| 2           | V <sub>IN</sub> 0+ |              |                                                                                                                                                                                                                                                                                                                                                                                 |

| 3           | V <sub>IN</sub> 0- |              |                                                                                                                                                                                                                                                                                                                                                                                 |

| 67          | V <sub>IN</sub> 1+ |              |                                                                                                                                                                                                                                                                                                                                                                                 |

| 68          | V <sub>IN</sub> 1- |              |                                                                                                                                                                                                                                                                                                                                                                                 |

| 64          | V <sub>IN</sub> 2+ |              |                                                                                                                                                                                                                                                                                                                                                                                 |

| 65          | V <sub>IN</sub> 2- |              |                                                                                                                                                                                                                                                                                                                                                                                 |

| 61          | V <sub>IN</sub> 3+ |              | Differential analog inputs to the ADC, for channels 0 to 7. The                                                                                                                                                                                                                                                                                                                 |

| 62          | V <sub>IN</sub> 3- |              | negative input pin may be connected via a capacitor to AGND or                                                                                                                                                                                                                                                                                                                  |

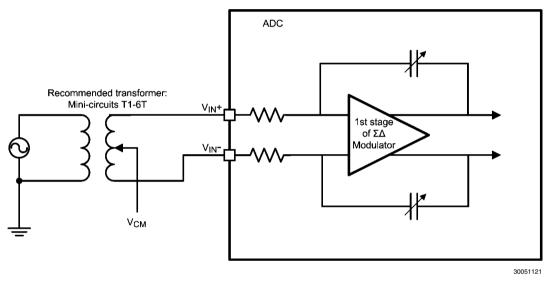

| 58          | V <sub>IN</sub> 4+ | Input        | the inputs may be transformer coupled for single ended operation                                                                                                                                                                                                                                                                                                                |

| 59          | V <sub>IN</sub> 4- |              | Differential inputs are recommended for best performance.                                                                                                                                                                                                                                                                                                                       |

| 55          | V <sub>IN</sub> 5+ |              |                                                                                                                                                                                                                                                                                                                                                                                 |

| 56          | V <sub>IN</sub> 5- |              |                                                                                                                                                                                                                                                                                                                                                                                 |

| 52          | V <sub>IN</sub> 6+ |              |                                                                                                                                                                                                                                                                                                                                                                                 |

| 53          | V <sub>IN</sub> 6- |              |                                                                                                                                                                                                                                                                                                                                                                                 |

| 49          | V <sub>IN</sub> 7+ |              |                                                                                                                                                                                                                                                                                                                                                                                 |

| 50          | V <sub>IN</sub> 7- |              |                                                                                                                                                                                                                                                                                                                                                                                 |

|             |                    |              | Optional negative reference voltage to improve multi-channel AD                                                                                                                                                                                                                                                                                                                 |

| 4           | V <sub>REFB</sub>  |              | matching. This pin must be connected to AGND.                                                                                                                                                                                                                                                                                                                                   |

| 5           | V <sub>reft</sub>  |              | Optional positive reference voltage to improve multi-channel AD<br>matching. If using the internal reference, this pin should be left tie<br>to AGND through a 100nF capacitor. If using an external reference<br>voltage, this pin should be connected to the positive reference<br>voltage, which must lie in the range specified in the Electrical<br>Characteristics table. |

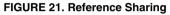

| 6           | D <sub>CAP</sub>   | Input        | This pin provides the capacitance for the low pass filter in the modulator's DAC. It must be connected to AGND through a minimum 100nF capacitor. It is possible to decrease the noise close to the carrier by increasing this capacitor, up to a maximur of 10µF. See Applications Information for further information on th selection of this capacitor.                      |

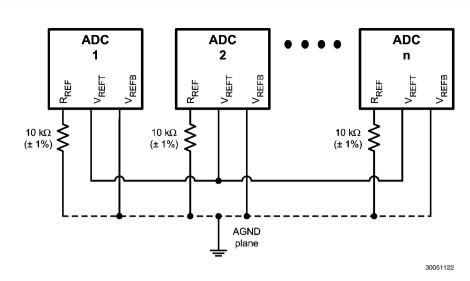

| 7           | R <sub>REF</sub>   | Input/Output | External bias reference resistor. This pin must always be<br>connected to AGND through a resistor, whether the internal<br>reference or an external reference voltage is used. The resistor<br>value must be $10k\Omega \pm 1\%$ .                                                                                                                                              |

| DIGITAL I/O |                    |              |                                                                                                                                                                                                                                                                                                                                                                                 |

| 9           | RST                | Input        | This pin is an active low reset for the entire ADC, both analog an digital components. The pin must be held low for 500ns then returned to high in order to ensure that the chip is reset correctly                                                                                                                                                                             |

| 10          | SLEEP              | Input        | Sleep mode. Toggling this pin to high will cause the ADC to enter<br>the low power sleep mode. When the pin is returned to low, the<br>chip will, after the specified time to exit sleep mode, return to normal<br>operation.                                                                                                                                                   |

| Pin No.                                                              | Name                                                                                 | Туре         | Function and Connection                                                                                                                                                                                                                                                                                                                                                      |

|----------------------------------------------------------------------|--------------------------------------------------------------------------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15<br>16<br>18<br>19<br>20                                           | D00+<br>D00-<br>D01+<br>D01-<br>D02+                                                 |              | Differential Serial Outputs for channels 0 to 7. Each pair of output                                                                                                                                                                                                                                                                                                         |

| 20<br>21<br>23<br>24<br>25<br>26<br>28<br>29<br>31<br>32<br>33<br>34 | D02-<br>D03+<br>D03-<br>D04+<br>D04-<br>D05+<br>D05-<br>D06+<br>D06-<br>D07+<br>D07- | Output       | provides the serial output for the specific channel. The default<br>output is reduced common mode LVDS format, but by<br>programming the appropriate control registers, the output format<br>can be changed to SLVS or LVDS.<br>By programming TX_term (bit 4) in the LVDS Control register, it<br>possible to internally terminate these outputs with 100 ohm<br>resistors. |

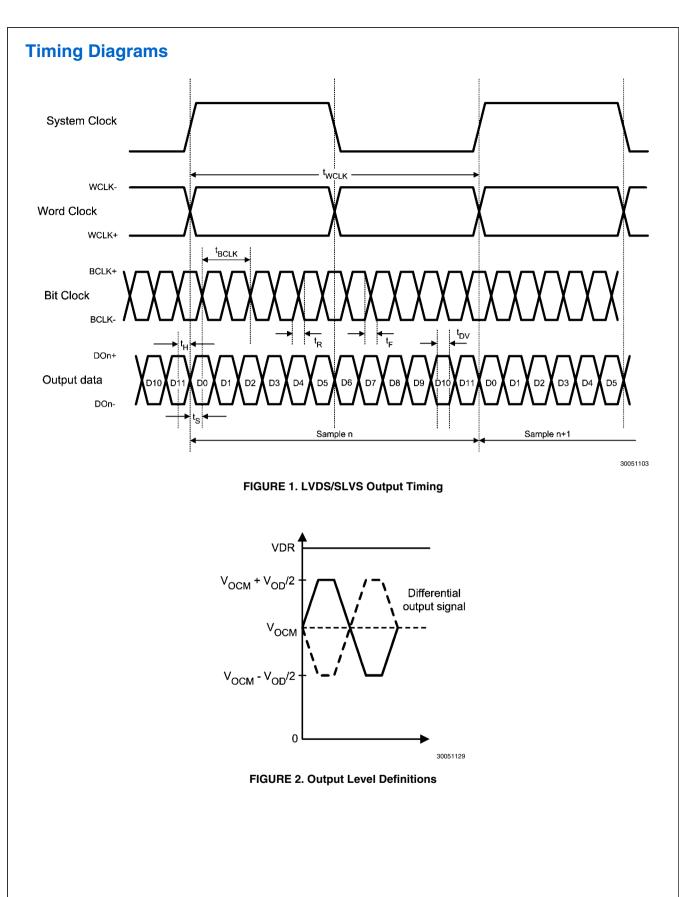

| 36<br>37                                                             | BCLK+<br>BCLK-                                                                       | Output       | Bit clock. Differential output clock used for sampling the serial<br>outputs. Information on timing can be seen in the Electrical<br>Specifications section of the datasheet.<br>By programming TX_term (bit 4) in the LVDS Control register, it is<br>possible to internally terminate these outputs with 100 ohm<br>resistors.                                             |

| 38<br>39                                                             | WCLK+<br>WCLK-                                                                       | Output       | Word Clock. Differential output frame clock. Information on timin<br>can be seen in the Electrical Specifications section of the<br>datasheet.<br>By programming TX_term (bit 4) in the LVDS Control register, it<br>possible to internally terminate these outputs with 100 ohm<br>resistors.                                                                               |

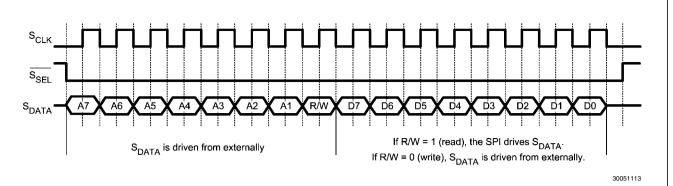

| 44                                                                   | S <sub>DATA</sub>                                                                    | Input/Output | SPI data input and output. This pin is used to send and receive SF address and data information. The direction of the pin is controlle internally by the ADC based on the SPI protocol.                                                                                                                                                                                      |

| 45                                                                   | S <sub>CLK</sub>                                                                     | Input        | SPI clock. In order to use the SPI interface, a clock must be provided on this pin. See Electrical Specifications for SPI clock an timing information.                                                                                                                                                                                                                       |

| 46                                                                   | S <sub>SEL</sub>                                                                     | Input        | SPI chip select. This active low pin is used to enable the serial interface.                                                                                                                                                                                                                                                                                                 |

| 47<br>48                                                             | CLK+ (SE)<br>CLK-                                                                    | Input        | Differential Input Clock. The input clock must lie in the range of 40MHz to 50MHz. It is used by the PLL to generate the internal sampling clocks. A single ended clock can also be used, and should be connected to pin 47.                                                                                                                                                 |

| OWER SUPP                                                            | PLY                                                                                  |              |                                                                                                                                                                                                                                                                                                                                                                              |

| 1, 8, 51, 54,<br>7, 60, 63, 66                                       | V <sub>A</sub>                                                                       | Power        | Analog Power Supply. All pins should be connected to the same 1.2V supply, with voltage limits as in the Electrical Specification.                                                                                                                                                                                                                                           |

| 0                                                                    | AGND                                                                                 | Ground       | Analog Ground Return.                                                                                                                                                                                                                                                                                                                                                        |

| 1, 12, 42, 43                                                        | V <sub>D</sub>                                                                       | Power        | Digital Power Supply. Connect to 1.2V, with voltage limits as in the Electrical Specification.                                                                                                                                                                                                                                                                               |

| 13, 14, 22,<br>30, 40, 41                                            | DGND                                                                                 | Ground       | Digital and Output Driver Ground Return.                                                                                                                                                                                                                                                                                                                                     |

| 17, 27, 35                                                           | V <sub>DR</sub>                                                                      | Power        | Output Driver Power Supply. Can be connected to 1.2V – 1.8V, depending on application requirements. Voltage limits are described in more detail in the Electrical Specification.                                                                                                                                                                                             |

### Absolute Maximum Ratings (Notes 1, 3)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| Supply Voltage (V <sub>A</sub> , V <sub>D</sub> )   | –0.3V to 1.4V |

|-----------------------------------------------------|---------------|

| IO Supply Voltage (V <sub>DR</sub> )                | -0.3 to 2.0V  |

| Voltage at Analog Inputs                            | -0.3 to 1.4V  |

| Voltage at SPI Inputs                               | -0.3 to 2.5V  |

| Input Current, V <sub>IN</sub> +, V <sub>IN</sub> - | ±1mA          |

| Input Current, other pins                           | ±10mA         |

| ESD Susceptibility                                  |               |

| Human Body Model                                    | 2000V         |

| Machine Model                                       | 200V          |

| Charged Device Mode                                 | 1,000V        |

| Soldering Temperature                               |               |

| Infrared, 10 seconds                                | 235°C         |

Storage Temperature Range -65°C to +125°C Soldering process must comply with National Semiconductor's Reflow Temperature Profile specifications. Refer to www.national.com/packaging.

### Operating Ratings (Notes 2, 3)

| Operating Temperature Range                                           | -40°C to +85°C          |

|-----------------------------------------------------------------------|-------------------------|

| Supply Voltage (V <sub>A</sub> =V <sub>D</sub> )                      | +1.14 to +1.26V         |

| IO Supply Voltage (V <sub>DR</sub> )                                  | +1.14 to +1.89V         |

| Minimum rise time on V <sub>A</sub> , V <sub>D</sub> ,                | 40µs                    |

| V <sub>DR</sub> at power-up                                           |                         |

| Analog Inputs (V <sub>IN</sub> N+, V <sub>IN</sub> N-)                | -0.10 to V <sub>A</sub> |

| SPI Inputs (S <sub>DATA</sub> , S <sub>SEL</sub> , S <sub>CLK</sub> ) | +1.14 to +2.50V         |

| V <sub>REFT</sub> (When using external reference)                     | 475mV to 525mV          |

| V <sub>REFB</sub>                                                     | AGND                    |

| V <sub>CM</sub> Input Common Mode Range<br>(Differential Input)       | 0.4V to 1.2V            |

| Ground Difference IAGND-<br>DGNDI                                     | <50mV                   |

|                                                                       |                         |

## **Electrical Characteristics**

| Symbol    | Parameter                                | Conditions                                                                     | Typical<br>(Note 4) | Limits | Units      |

|-----------|------------------------------------------|--------------------------------------------------------------------------------|---------------------|--------|------------|

| Static Co | onverter Characteristics                 | 1                                                                              |                     |        |            |

|           | Resolution (No missing codes guaranteed) |                                                                                |                     | 12     | Bits       |

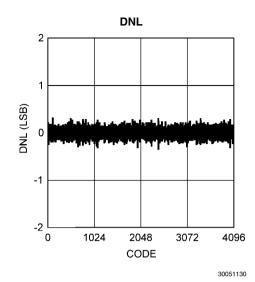

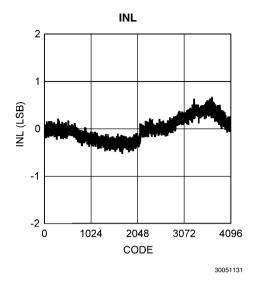

| INL       | Integral Non Linearity                   |                                                                                | ±0.75               | ±3.0   | LSB        |

| DNL       | Differential Non Linearity               |                                                                                | ±0.35               | ±0.75  | LSB        |

| PSE       | Positive Full Scale Error                |                                                                                | ±0.66               | ±3     | %FS        |

| NSE       | Negative Full Scale Error                |                                                                                | ±0.58               | ±3     | %FS        |

| GE        | Gain Error                               |                                                                                | ±1.23               |        | %FS        |

| Dynamic   | Converter Characteristics – Instant      | Overload Recovery (IOR) Off                                                    |                     |        |            |

|           | Signal to Noise Ratio(Note 5)            | $f_{CLK} = 50MHz, f_{IN} = 4.4MHz, V_{IN} = -0.5dBFS$                          | 69.3                | 67.0   | dBFS (min) |

| SNR       |                                          | $f_{CLK} = 50MHz, f_{IN} = 9.5MHz, V_{IN} = -0.5dBFS$                          | 69.0                |        | dBFS       |

|           |                                          | $f_{CLK} = 40MHz, f_{IN} = 4.4MHz, V_{IN} = -0.5dBFS$                          | 69.9                |        | dBFS       |

|           |                                          | $f_{CLK} = 40MHz, f_{IN} = 9.5MHz, V_{IN} = -0.5dBFS$                          | 69.6                |        | dBFS       |

|           | Signal to Noise and Distortion(Note 5)   | $f_{CLK} = 50MHz$ , $f_{IN} = 4.4MHz$ , $V_{IN} = -0.5dBFS$                    | 68.5                | 62.5   | dBFS (min) |

|           |                                          | f <sub>CLK</sub> = 50MHz, f <sub>IN</sub> = 9.5MHz, V <sub>IN</sub> = -0.5dBFS | 68.5                |        | dBFS       |

| SINAD     |                                          | $f_{CLK} = 40MHz, f_{IN} = 4.4MHz, V_{IN} = -0.5dBFS$                          | 69.3                |        | dBFS       |

|           |                                          | $f_{CLK} = 40MHz, f_{IN} = 9.5MHz, V_{IN} = -0.5dBFS$                          | 69.2                |        | dBFS       |

|           |                                          | $f_{CLK} = 50MHz$ , $f_{IN} = 4.4MHz$ , $V_{IN} = -0.5dBFS$                    | 11.1                | 10.1   | Bits (min) |

|           |                                          | $f_{CLK} = 50MHz, f_{IN} = 9.5MHz, V_{IN} = -0.5dBFS$                          | 11.1                |        | Bits       |

| ENOB      | Effective Number of Bits                 | f <sub>CLK</sub> = 40MHz, f <sub>IN</sub> = 4.4MHz, V <sub>IN</sub> = -0.5dBFS | 11.2                |        | Bits       |

|           |                                          | $f_{CLK} = 40MHz, f_{IN} = 9.5MHz, V_{IN} = -0.5dBFS$                          | 11.2                |        | Bits       |

|           |                                          | $f_{CLK} = 50MHz, f_{IN} = 4.4MHz, V_{IN} = -0.5dBFS$                          | -76                 | -65    | dBc (max)  |

|           |                                          | $f_{CLK} = 50MHz, f_{IN} = 9.5MHz, V_{IN} = -0.5dBFS$                          | -78                 |        | dBc        |

| THD       | Total Harmonic Distortion                | $f_{CLK} = 40MHz, f_{IN} = 4.4MHz, V_{IN} = -0.5dBFS$                          | -77                 |        | dBc        |

|           |                                          | $f_{CLK} = 40MHz$ , $f_{IN} = 9.5MHz$ , $V_{IN} = -0.5dBFS$                    | -79                 |        | dBc        |

| Symbol  | Parameter                              | Conditions                                                                     | Typical<br>(Note 4) | Limits | Units      |

|---------|----------------------------------------|--------------------------------------------------------------------------------|---------------------|--------|------------|

|         |                                        | $f_{CLK}$ = 50MHz, $f_{IN}$ = 4.4MHz, $V_{IN}$ = -0.5dBFS                      | -81                 | -66    | dBc (max)  |

| 42      | Second Harmonic Distortion             | $f_{CLK} = 50MHz, f_{IN} = 9.5MHz, V_{IN} = -0.5dBFS$                          | -79                 |        | dBc        |

| 72      | Second Harmonic Distortion             | $f_{CLK} = 40MHz, f_{IN} = 4.4MHz, V_{IN} = -0.5dBFS$                          | -82                 |        | dBc        |

|         |                                        | $f_{CLK} = 40MHz, f_{IN} = 9.5MHz, V_{IN} = -0.5dBFS$                          | -80                 |        | dBc        |

|         |                                        | $f_{CLK} = 50MHz$ , $f_{IN} = 4.4MHz$ , $V_{IN} = -0.5dBFS$                    | -83                 | -67    | dBc (max)  |

| 10      |                                        | f <sub>CLK</sub> = 50MHz, f <sub>IN</sub> = 9.5MHz, V <sub>IN</sub> = -0.5dBFS | -97                 |        | dBc        |

| 43      | Third Harmonic Distortion              | $f_{CLK} = 40MHz$ , $f_{IN} = 4.4MHz$ , $V_{IN} = -0.5dBFS$                    | -84                 |        | dBc        |

|         |                                        | $f_{CLK} = 40MHz$ , $f_{IN} = 9.5MHz$ , $V_{IN} = -0.5dBFS$                    | -108                |        | dBc        |

|         |                                        | $f_{CLK} = 50MHz$ , $f_{IN} = 4.4MHz$ , $V_{IN} = -0.5dBFS$                    | 77                  | 66     | dBc (min)  |

|         |                                        | $f_{CLK} = 50MHz$ , $f_{IN} = 9.5MHz$ , $V_{IN} = -0.5dBFS$                    | 78                  |        | dBc        |

| SFDR    | Spurious Free Dynamic Range            | $f_{CLK} = 40MHz$ , $f_{IN} = 4.4MHz$ , $V_{IN} = -0.5dBFS$                    | 78                  |        | dBc        |

|         |                                        | $f_{CLK} = 40MHz$ , $f_{IN} = 9.5MHz$ , $V_{IN} = -0.5dBFS$                    | 79                  |        | dBc        |

|         |                                        | $f_1 = 9.6$ MHz, $V_{IN} = -6$ dBFS                                            |                     |        |            |

| MD      | Intermodulation Distortion             | $f_2 = 10.1$ MHz, $V_{IN} = -6$ dBFS                                           | -70                 |        | dBFS       |

| Dvnamic | Converter Characteristics – Instant    | Į                                                                              |                     |        |            |

| ,       |                                        | $f_{CLK} = 50MHz$ , $f_{IN} = 4.4MHz$ , $V_{IN} = -0.5dBFS$                    | 67.6                | 65.5   | dBFS (min) |

|         | Signal-to-Noise Ratio(Note 5)          | $f_{CLK} = 50MHz$ , $f_{IN} = 9.5MHz$ , $V_{IN} = -0.5dBFS$                    | 67.4                |        | dBFS       |

| SNR     |                                        | $f_{CLK} = 40MHz$ , $f_{IN} = 4.4MHz$ , $V_{IN} = -0.5dBFS$                    | 68.4                |        | dBFS       |

|         |                                        | $f_{CLK} = 40MHz$ , $f_{IN} = 9.5MHz$ , $V_{IN} = -0.5dBFS$                    | 68.2                |        | dBFS       |

|         | Signal-to-Noise and Distortion(Note 5) | $f_{CLK} = 50MHz$ , $f_{IN} = 4.4MHz$ , $V_{IN} = -0.5dBFS$                    | 67.0                | 61.5   | dBFS (min) |

|         |                                        |                                                                                | 67.0                | 01.5   | dBFS       |

| SINAD   |                                        | $f_{CLK} = 50$ MHz, $f_{IN} = 9.5$ MHz, $V_{IN} = -0.5$ dBFS                   |                     |        |            |

|         |                                        | $f_{CLK} = 40MHz$ , $f_{IN} = 4.4MHz$ , $V_{IN} = -0.5dBFS$                    | 67.9                |        | dBFS       |

|         |                                        | $f_{CLK} = 40MHz, f_{IN} = 9.5MHz, V_{IN} = -0.5dBFS$                          | 67.8                |        | dBFS       |

|         |                                        | $f_{CLK} = 50MHz$ , $f_{IN} = 4.4MHz$ , $V_{IN} = -0.5dBFS$                    | 10.8                | 9.9    | Bits (min) |

| ENOB    | Effective Number of Bits               | $f_{CLK} = 50MHz$ , $f_{IN} = 9.5MHz$ , $V_{IN} = -0.5dBFS$                    | 10.8                |        | Bits       |

|         |                                        | $f_{CLK} = 40MHz$ , $f_{IN} = 4.4MHz$ , $V_{IN} = -0.5dBFS$                    | 11.0                |        | Bits       |

|         |                                        | $f_{CLK} = 40MHz, f_{IN} = 9.5MHz, V_{IN} = -0.5dBFS$                          | 11.0                |        | Bits       |

|         |                                        | $f_{CLK} = 50MHz, f_{IN} = 4.4MHz, V_{IN} = -0.5dBFS$                          | -76                 | -64    | dBc (max)  |

| ГНD     | Total Harmonic Disortion               | $f_{CLK} = 50MHz, f_{IN} = 9.5MHz, V_{IN} = -0.5dBFS$                          | -77                 |        | dBc        |

|         |                                        | $f_{CLK} = 40MHz, f_{IN} = 4.4MHz, V_{IN} = -0.5dBFS$                          | -77                 |        | dBc        |

|         |                                        | $f_{CLK} = 40MHz$ , $f_{IN} = 9.5MHz$ , $V_{IN} = -0.5dBFS$                    | -78                 |        | dBc        |

|         |                                        | $f_{CLK}$ = 50MHz, $f_{IN}$ = 4.4MHz, $V_{IN}$ = -0.5dBFS                      | -80                 | -65    | dBc (max)  |

| -12     | Second Harmonic Distortion             | $f_{CLK}$ = 50MHz, $f_{IN}$ = 9.5MHz, $V_{IN}$ = -0.5dBFS                      | -78                 |        | dBc        |

| 12      |                                        | $f_{CLK} = 40MHz$ , $f_{IN} = 4.4MHz$ , $V_{IN} = -0.5dBFS$                    | -81                 |        | dBc        |

|         |                                        | $f_{CLK} = 40MHz, f_{IN} = 9.5MHz, V_{IN} = -0.5dBFS$                          | -79                 |        | dBc        |

|         |                                        | $f_{CLK} = 50MHz, f_{IN} = 4.4MHz, V_{IN} = -0.5dBFS$                          | -83                 | -67    | dBc (max)  |

| 10      | Third Llowerseis Distantion            | $f_{CLK} = 50MHz, f_{IN} = 9.5MHz, V_{IN} = -0.5dBFS$                          | -96                 |        | dBc        |

| -13     | Third Harmonic Distortion              | $f_{CLK} = 40MHz, f_{IN} = 4.4MHz, V_{IN} = -0.5dBFS$                          | -85                 |        | dBc        |

|         |                                        | $f_{CLK} = 40MHz, f_{IN} = 9.5MHz, V_{IN} = -0.5dBFS$                          | -107                |        | dBc        |

|         |                                        | $f_{CLK} = 50MHz$ , $f_{IN} = 4.4MHz$ , $V_{IN} = -0.5dBFS$                    | 76                  | 65     | dBc (min)  |

|         |                                        | $f_{CLK} = 50MHz$ , $f_{IN} = 9.5MHz$ , $V_{IN} = -0.5dBFS$                    | 77                  |        | dBc        |

| SFDR    | Spurious Free Dynamic Range            | $f_{CLK} = 40MHz$ , $f_{IN} = 4.4MHz$ , $V_{IN} = -0.5dBFS$                    | 78                  |        | dBc        |

|         |                                        | $f_{CLK} = 40MHz$ , $f_{IN} = 9.5MHz$ , $V_{IN} = -0.5dBFS$                    | 78                  |        | dBc        |

|         |                                        | $f_1 = 9.6MHz$ , $V_{IN} = -6dBFS$                                             |                     |        |            |

| MD      | Intermodulation Distortion             | $f_2 = 10.1$ MHz, $V_{IN} = -6$ dBFS                                           | -70                 |        | dBFS       |

| Symbol              | Parameter                                                 | Conditions                                                         | Typical<br>(Note 4) | Limits | Units                |

|---------------------|-----------------------------------------------------------|--------------------------------------------------------------------|---------------------|--------|----------------------|

| Inter-cha           | annel Characteristics                                     | •                                                                  | •                   |        |                      |

|                     | Channel to channel gain match                             |                                                                    | ±0.1                | ±0.5   | dB                   |

|                     | Inter-channel Isolation                                   | f <sub>IN</sub> = 4.4MHz @ -0.1dBFS<br>Adjacent channel terminated | 110                 |        | dB                   |

| Reference           | ce And Analog Input Characteristics                       | 8                                                                  |                     |        |                      |

|                     |                                                           | IOR mode off                                                       | 2.10                |        | V <sub>PP</sub>      |

| V <sub>IN</sub>     | Full Scale Analog Input Voltage                           | IOR mode on                                                        | 1.56                |        | V <sub>PP</sub>      |

|                     | Maximum Input for Instantaneous<br>Recovery from Overload | IOR mode on, f <sub>IN</sub> < 12MHz                               |                     | 2.75   | V <sub>PP</sub> (max |

| _                   |                                                           |                                                                    |                     | 2.4    | kΩ (min)             |

| R <sub>IN</sub>     | Differential Input Impedance                              |                                                                    | 2.61                | 2.8    | kΩ (max              |

| V                   |                                                           | Generated internally                                               | 605                 | 574    | mV (min)             |

| V <sub>CM</sub>     | Internal Input Common Mode                                |                                                                    | 605                 | 637    | mv (max              |

|                     | Input Impedance of V <sub>Reft</sub>                      |                                                                    | 20                  |        | kΩ                   |

| V                   | Internal Reference Voltage                                | Generated internally                                               | 502                 | 480    | mV (min)             |

| V <sub>REFOUT</sub> | Internal helefence voltage                                |                                                                    | 502                 | 520    | mV (max              |

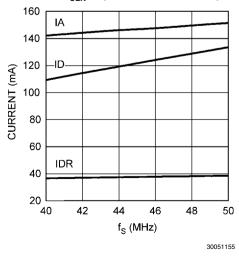

| Power C             | haracteristics                                            |                                                                    |                     |        |                      |

| I <sub>A</sub>      | Analog Supply Current                                     | f <sub>CLK</sub> = 50 MHz                                          | 152                 | 163    | mA (max              |

| I <sub>D</sub>      | Digital Supply Current                                    | f <sub>CLK</sub> = 50 MHz                                          | 130                 | 147    | mA (max              |

| I <sub>DR</sub>     | Output Driver Supply Current                              | LVDS, $V_{DR} = 1.8V$ , $f_{CLK} = 50$ MHz                         | 38                  | 45     | mA (max              |

|                     |                                                           | $f_{CLK}$ = 50 MHz, Equalizer off                                  | 385                 | 412    | mW (max              |

|                     |                                                           | $f_{CLK} = 50 \text{ MHz}$ , Equalizer on                          | 435                 | 470    | mW (max              |

|                     | Power concumption                                         | $f_{CLK} = 40 \text{ MHz}$ , Equalizer off                         | 343                 |        | mW                   |

|                     | Power consumption                                         | f <sub>CLK</sub> = 40 MHz, Equalizer on                            | 383                 |        | mW                   |

|                     |                                                           | Sleep                                                              | 40                  | 50     | mW (max              |

|                     |                                                           | Power Down                                                         | 5                   | 15     | mW (max              |

|                     |                                                           | f <sub>CLK</sub> = 50 MHz, Equalizer off                           | 48                  |        | mW                   |

|                     | Per channel power consumption                             | f <sub>CLK</sub> = 40 MHz, Equalizer off                           | 43                  |        | mW                   |

| PSRR                | Power supply rejection ratio                              | 100mV, 100kHz to 1MHz sinusoid on V <sub>A</sub>                   | 65                  |        | dB                   |

| CMRR                | Common mode rejection ratio                               | 100mV, 1MHz sinusoid on V <sub>IN</sub> + and V <sub>IN</sub> -    | 60                  |        | dB                   |

|                     | Recovery time from sleep                                  |                                                                    |                     | 12     | µs (max)             |

|                     | Recovery time from power down                             |                                                                    |                     | 18     | ms (max              |

|                     | Recovery time from single channel power down              |                                                                    |                     | 6      | µs (max)             |

## **Digital Decimation Filter Characteristics**

| Symbol | Parameter                         | Conditions(Note 6)                         | Typical<br>(Note 4) | Limits | Units        |

|--------|-----------------------------------|--------------------------------------------|---------------------|--------|--------------|

|        | Pass Band                         | f <sub>CLK</sub> = 50MHz                   | 22                  |        | MHz          |

|        |                                   | f <sub>CLK</sub> = 40MHz                   | 17.6                |        | MHz          |

|        | Pass Band Transition              | f <sub>CLK</sub> = 50MHz, -3dB attenuation | 25                  |        | MHz          |

|        |                                   | f <sub>CLK</sub> = 40MHz, -3dB attenuation | 20                  |        | MHz          |

|        | Pass Band Ripple                  | f <sub>IN</sub> < 22MHz                    |                     | ±0.01  | dB           |

|        | Stop Band Begin                   | f <sub>CLK</sub> = 50MHz                   | 34.5                |        | MHz          |

|        |                                   | f <sub>CLK</sub> = 40MHz                   | 27.6                |        | MHz          |

|        | Stop Band Attenuation             |                                            |                     | 72     | dB (min)     |

|        | Group Delay Ripple (peak to peak) | f <sub>IN</sub> < 22MHz, Equalizer on      |                     | 0.05   | Samples (max |

## **External Input Clock and PLL Characteristics**

| Symbol              | Parameter                                            | Conditions                                 | Typical<br>(Note 4) | Limits     | Units                  |

|---------------------|------------------------------------------------------|--------------------------------------------|---------------------|------------|------------------------|

| External            | Input Clock                                          |                                            |                     |            |                        |

| f <sub>CLK</sub>    | Allowed input clock frequency                        |                                            |                     | 40<br>50   | MHz (min)<br>MHz (max) |

| t <sub>CLK</sub>    | Allowed input clock period                           |                                            | 1/f <sub>CLK</sub>  |            | ns                     |

| f <sub>CLK</sub> DC | Allowed input clock duty cycle                       |                                            | 50                  | 20<br>80   | % (min)<br>% (max)     |

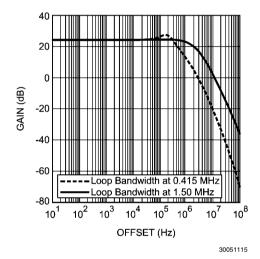

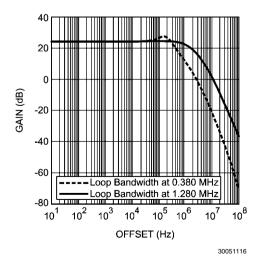

| t <sub>JIN</sub>    | Allowed RMS clock jitter on input clock.<br>(Note 9) | Integrated from 10Hz to BW <sub>loop</sub> | 300                 |            | fs rms                 |

| V <sub>CMCLK</sub>  | Allowed input clock common mode                      | (Note 8)                                   |                     | 400<br>VDR | mV (min)<br>mV (max)   |

| M                   |                                                      | Differential clock input (Nate 0)          | 400                 | 200        | mV peak-peak<br>(min)  |

| V <sub>ICLK</sub>   | Allowed input clock voltage swing                    | Differential clock input.(Note 8)          | 400                 | VDR        | mV peak-peak<br>(max)  |

| PLL                 |                                                      |                                            |                     |            |                        |

| f∑∆                 | Over-sampling frequency                              |                                            |                     | 640<br>800 | MHz (min)<br>MHz (max) |

| D\M                 | DLL Leep filter bendwidth                            | Low Bandwidth                              | 400                 |            | kHz                    |

| BW <sub>loop</sub>  | PLL Loop filter bandwidth                            | High Bandwidth                             | 1.4                 |            | MHz                    |

| tj                  | RMS Clock Jitter on Bit Clock output                 |                                            |                     | 2          | ps peak                |

## **Digital Input and Output Characteristics**

| Symbol             | Parameter                                                                 | Conditions                               | Typical<br>(Note 4) | Limits | Units    |

|--------------------|---------------------------------------------------------------------------|------------------------------------------|---------------------|--------|----------|

| Digital In         | puts (S <sub>DATA</sub> , S <sub>SEL</sub> , S <sub>CLK</sub> , SLEEP, RS | Γ)                                       | I                   |        |          |

| V <sub>IH</sub>    | Logical input "1" voltage                                                 | Test run at 2MHz                         |                     | 900    | mV (min) |

| V <sub>IL</sub>    | Logical input "0" voltage                                                 | Test run at 2MHz                         |                     | 300    | mV (max) |

| I <sub>IN1</sub>   | Logical "1" Input current                                                 |                                          |                     | 1      | µA (max) |

| I <sub>IN0</sub>   | Logical "0" Input current                                                 |                                          |                     | -1     | μA (min) |

| C <sub>IN</sub>    | Input Capacitance                                                         | Guaranteed by design                     | 5                   |        | pF       |

| Digital O          | utputs (S <sub>DATA</sub> )                                               |                                          |                     |        |          |

| V <sub>OH</sub>    | Logical output "1" voltage                                                | Test run at 2MHz, V <sub>DR</sub> = 1.2V | V <sub>DR</sub>     | 850    | mV (min) |

| V <sub>OL</sub>    | Logical output "0" voltage                                                | Test run at 2MHz, V <sub>DR</sub> = 1.2V | DRGND               | 250    | mV (max) |

| I <sub>OH</sub>    | Logical "1" Output Current                                                |                                          |                     | -0.75  | mA (min) |

| I <sub>OL</sub>    | Logical "0" Output Current                                                |                                          |                     | 1      | mA (max) |

| Output D           | Drive Capability (S <sub>DATA</sub> )                                     |                                          |                     |        |          |

| 0                  |                                                                           | R = 4.7 kohm, V <sub>DR</sub> > 1.8V     | 50                  |        | pF       |

| C <sub>LOAD</sub>  | Load capacitance                                                          | R = 4.7 kohm, V <sub>DR</sub> = 1.2V     | 50                  |        | pF       |

| Open Dr            | ain Mode                                                                  |                                          | · · ·               |        |          |

| V <sub>EXT</sub>   | Maximum allowed external voltage on $S_{\text{DATA}}$                     | Open Drain mode activated                |                     | 2.5    | V        |

| R <sub>SDATA</sub> | Recommended S <sub>DATA</sub> external pull-<br>up resistor               | Open Drain mode activated                | 4.7                 |        | kΩ       |

## **AC and Timing Characteristics**

| Symbol                          | Parameter                                        | Conditions                                              | Typical<br>(Note 4) | Limits   | Units                   |

|---------------------------------|--------------------------------------------------|---------------------------------------------------------|---------------------|----------|-------------------------|

| General                         | ADC Output Timing Parameters                     |                                                         |                     |          |                         |

| f <sub>s</sub>                  | Sample Rate                                      |                                                         |                     | 40<br>50 | MSPS (min)<br>MSPS (max |

|                                 | Conversion Latency                               |                                                         | 19                  |          | Samples                 |

| t <sub>BCLK</sub>               | Bit clock period                                 | f <sub>CLK</sub> = 50MHz                                | 3.33                |          | ns                      |

|                                 |                                                  | f <sub>CLK</sub> = 40MHz                                | 4.16                |          | ns                      |

| t <sub>WCLK</sub>               | Word clock period                                | f <sub>CLK</sub> = 50MHz                                | 20                  |          | ns                      |

|                                 |                                                  | f <sub>CLK</sub> = 40MHz                                | 25                  |          | ns                      |

| t <sub>s</sub>                  | Outputs Data Edge to Output Clock                | f <sub>CLK</sub> = 50MHz                                | 800                 | 325      | ps (min)                |

|                                 | Edge Setup Time                                  | f <sub>CLK</sub> = 40MHz (Note 7)                       | 900                 | 480      | ps (min)                |

| t <sub>H</sub>                  | Output Data Edge to Output Clock                 | f <sub>CLK</sub> = 50MHz                                | 850                 | 470      | ps (min)                |

|                                 | Edge Hold Time                                   | f <sub>CLK</sub> = 40MHz (Note 7)                       | 1150                | 770      | ps (min)                |

| t <sub>DV</sub>                 | Output Data Valid Window                         | f <sub>CLK</sub> = 50MHz (Note 7)                       | 1380                | 885      | ps (min)                |

| -                               |                                                  | f <sub>CLK</sub> = 40MHz (Note 7)                       | 1820                | 1410     | ps (min)                |

| t <sub>R</sub> , t <sub>F</sub> | Output Rise/Fall time                            | f <sub>CLK</sub> = 50MHz                                | 320                 |          | ps (min)                |

|                                 | Data Edge to Word Edge Skew                      | f <sub>CLK</sub> = 50MHz                                | -295                | -720     | ps (min)                |

| DIG                             |                                                  |                                                         |                     | 220      | ps (max)                |

| LVDS Ou                         | utput Parameters, OCM = 0 (V <sub>DR</sub> = 1.2 | 2V)                                                     |                     |          |                         |

|                                 | Differential Output Voltage                      | LVDS mode, I_drive[1:0] = 00 (2.5mA), R <sub>L</sub> =  | 270                 |          | mV                      |

|                                 |                                                  | 100Ω                                                    |                     |          |                         |

| .,                              |                                                  | LVDS mode, I_drive[1:0] = 01 (3.5mA), R <sub>L</sub> =  | 370                 | 318      | mV (min)                |

| V <sub>OD</sub>                 |                                                  | 100Ω                                                    |                     | 428      | mV (max)                |

|                                 |                                                  | LVDS mode, I_drive[1:0] = 11 (5.0mA), R <sub>1</sub> =  | 520                 |          | mV                      |

|                                 |                                                  | 100Ω                                                    |                     |          |                         |

| V                               | Output Common Made Valtage                       | LVDS mode, OCM = 0 (for $V_{DR}$ = 1.2V)                | 945                 | 895      | mV (min)                |

| V <sub>OCM</sub>                | Output Common Mode Voltage                       |                                                         |                     | 1000     | mV (max)                |

| LVDS Ou                         | utput Parameters, OCM = 1 (V <sub>DR</sub> = 1.8 | 3V)                                                     |                     |          |                         |

|                                 |                                                  | LVDS mode, I_drive[1:0] = 00 (2.5mA), R <sub>L</sub> =  | 265                 |          | mV                      |

|                                 |                                                  | 100Ω                                                    |                     |          |                         |

| v                               | Differential Output Voltage                      | LVDS mode, I_drive[1:0] = 01 (3.5mA), R <sub>L</sub> =  | 350                 | 280      | mV (min)                |

| V <sub>OD</sub>                 |                                                  | 100Ω                                                    |                     | 417      | mV (max)                |

|                                 |                                                  | LVDS mode, I_drive[1:0] = 11 (5.0mA), R <sub>L</sub> =  | 485                 |          | mV                      |

|                                 |                                                  | 100Ω                                                    |                     |          |                         |

| V <sub>OCM</sub>                | Output Common Mode Voltage                       | LVDS mode, OCM = 1                                      | 1265                | 1200     | mV (min)                |

|                                 |                                                  |                                                         |                     | 1340     | mv (max)                |

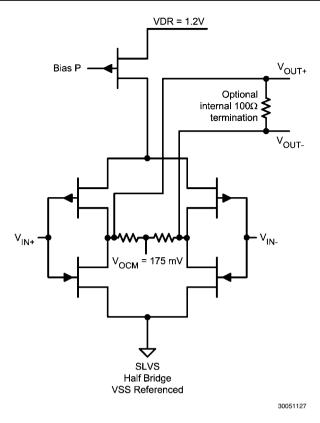

| SLVS Oι                         | utput Parameters                                 |                                                         |                     |          |                         |

|                                 |                                                  | SLVS mode, I_drive[1:0] = 00 (2.5mA), $R_L = 100\Omega$ | 245                 |          | mV                      |

|                                 |                                                  | SLVS mode, I_drive[1:0] = 01 (3.5mA), R <sub>I</sub> =  | 330                 | 262      | mV (min)                |

| V <sub>OD</sub>                 | Differential Output Voltage                      | $100\Omega$                                             |                     | 393      | mV (max)                |

|                                 |                                                  | SLVS mode, I_drive[1:0] = 11 (5.0mA), R <sub>L</sub> =  | 475                 |          | mV                      |

|                                 |                                                  | $100\Omega$                                             |                     |          |                         |

| V <sub>OCM</sub>                |                                                  |                                                         |                     | 185      | mV (min)                |

|                                 | Output Common Mode Voltage                       | SLVS mode                                               | 225                 |          | /                       |

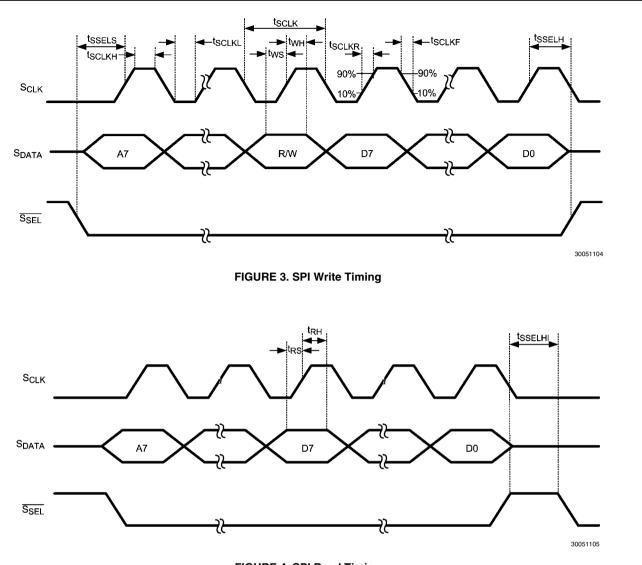

## AC and Timing Characteristics (Serial Interface)

Unless otherwise specified, the following conditions apply:  $V_A = V_D = 1.2V$ ;  $V_{DR} = 1.2V$ ;  $V_{REF} =$  internal;  $R_{REF} = 10$ kohm ±1%;  $C_L = 5pF$ ; 100 $\Omega$  terminated at the receiver;  $f_{CLK} = 50$ MHz;  $f_S = 50$ MSPS. **Boldface limits** apply for  $T_A = T_{MIN}$  to  $T_{MAX}$ ; All other limits apply for  $T_A = +25^{\circ}$ C.

| Symb<br>ol          | Parameter                                            | Conditions                             | Typical<br>(Note 4) | Limits | Units    |  |  |  |  |

|---------------------|------------------------------------------------------|----------------------------------------|---------------------|--------|----------|--|--|--|--|

| Serial I            | erial Interface                                      |                                        |                     |        |          |  |  |  |  |

| t <sub>SSELS</sub>  | S <sub>SEL</sub> setup time                          |                                        | 250                 |        | ns       |  |  |  |  |

| t <sub>SSELH</sub>  | S <sub>SEL</sub> hold time                           |                                        | 250                 |        | ns       |  |  |  |  |

| t <sub>ws</sub>     | S <sub>DATA</sub> setup time, write transaction      |                                        | 250                 | 15     | ns (max) |  |  |  |  |

| t <sub>WH</sub>     | S <sub>DATA</sub> hold time, write transaction       |                                        | 250                 | 10     | ns (max) |  |  |  |  |

| t <sub>SCLK</sub>   | S <sub>CLK</sub> period                              |                                        | 1                   | 0.2    | μs (min) |  |  |  |  |

| t <sub>SCLKL</sub>  | S <sub>CLK</sub> low time                            |                                        | 450                 |        | ns (min) |  |  |  |  |

| t <sub>SCLKH</sub>  | S <sub>CLK</sub> high time                           |                                        | 450                 |        | ns (min) |  |  |  |  |

| t <sub>SCLKR</sub>  | S <sub>CLK</sub> rise time                           |                                        | 50                  |        | ns       |  |  |  |  |

| t <sub>SCLKF</sub>  | S <sub>CLK</sub> fall time                           |                                        | 50                  |        | ns       |  |  |  |  |

| t <sub>SSELHI</sub> | S <sub>SEL</sub> high time                           | Applies to read and write transactions | 500                 |        | ns       |  |  |  |  |

| t <sub>RS</sub>     | S <sub>DATA</sub> valid setup time, read transaction |                                        | 100                 | -5     | ns (min) |  |  |  |  |

| t <sub>RH</sub>     | $S_{DATA}$ valid hold time, read transaction         |                                        | 250                 | 10     | ns (min) |  |  |  |  |

Note 1: Absolute maximum ratings are those values beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the device should be operated at these limits.

Note 2: Operating Ratings indicate conditions for which the device is guaranteed to be functional, but do not guarantee specific performance limits. Guaranteed specifications and test conditions are specified in the Electrical Characterisitcs section. Operation of the device beyond the Operating Ratings is not recommended as it may degrade the device lifetime.

Note 3: All voltages are measured with respect to GND = AGND = DGND = 0V, unless otherwise specified.

Note 4: Typical figures are at TA = 25°C, and represent most likely parametric norms at the time of product characterization. The typical specifications are not guaranteed.

Note 5: This parameter is specified in dBFS. This indicates the value which would be obtained with a full-scale input.

Note 6: As the filter is a digital circuit, Digital Decimation Filter Characteristics scale with input clock frequency, f<sub>CLK</sub>.

Note 7: This parameter is guaranteed by design and/or characterization and is not tested in production.

Note 8: The combination of common mode and voltage swing on the clock input must ensure that the positive voltage peaks are not above VDR and the negative voltage peaks are not below AGND.

Note 9: See the "Clock Conditioner Owner's Manual", Chapter 2 (www.national.com/appinfo/interface/files/clk\_conditioner\_owners\_manual.pdf) for a discussion on jitter.

FIGURE 4. SPI Read Timing

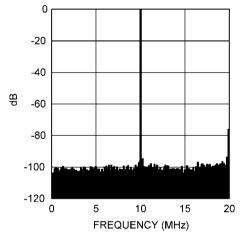

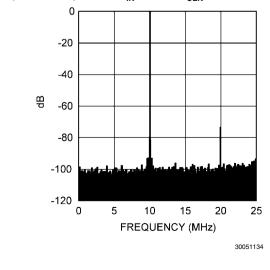

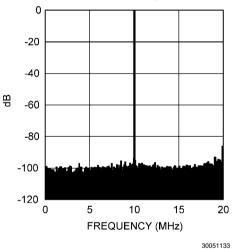

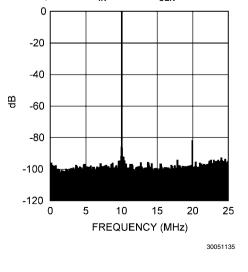

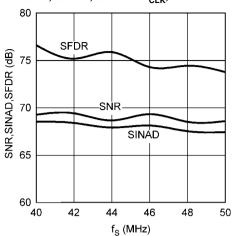

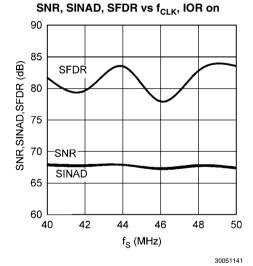

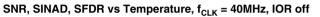

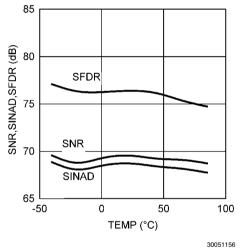

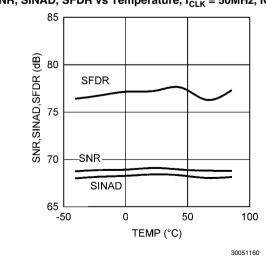

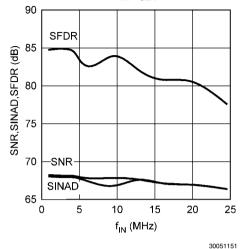

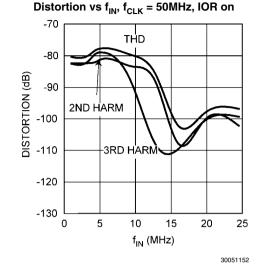

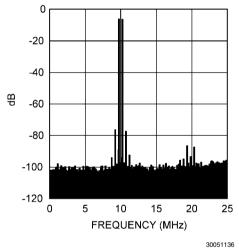

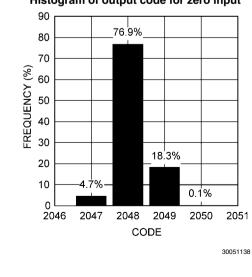

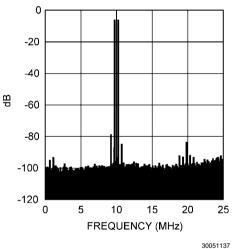

**Typical Performance Characteristics** Unless otherwise specified, the following conditions apply:  $V_A = V_D = 1.2V$ ;  $V_{DR} = 1.2V$ ;  $V_{REF} =$  internal;  $C_L = 5pF$ ;  $f_{CLK} = 50MHz$ ;  $f_S = 50MSPS$ ;  $f_{IN} = 10MHz$ . Units for SNR and SINAD are dBFS. Units for SFDR and Distortion are dBc.

Spectral Response @ f<sub>IN</sub>=10MHz, f<sub>CLK</sub>= 40MHz, IOR off

Spectral Response @  $f_{IN}$ =10MHz,  $f_{CLK}$ = 50MHz, IOR off

Spectral Response @  $\rm f_{IN}=10MHz,\,f_{CLK}=40MHz,\,IOR$  on

Spectral Response @  $\rm f_{IN}=10MHz,\, f_{CLK}=50MHz,\, IOR$  on

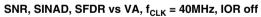

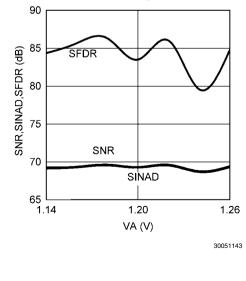

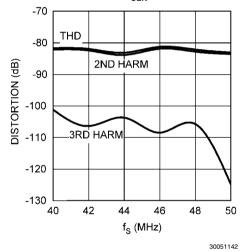

**Typical Performance Characteristics** Unless otherwise specified, the following conditions apply:  $V_A = V_D = 1.2V$ ;  $V_{DR} = 1.2V$ ;  $V_{REF} =$  internal;  $C_L = 5pF$ ;  $f_{CLK} = 50MHz$ ;  $f_S = 50MSPS$ ;  $f_{IN} = 10MHz$ . Units for SNR and SINAD are dBFS. Units for SFDR and Distortion are dBc.

SNR, SINAD, SFDR vs f<sub>CLK</sub>, IOR off

30051139

30051140

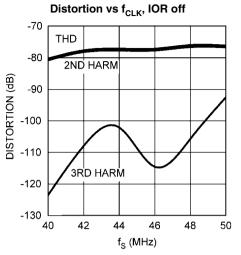

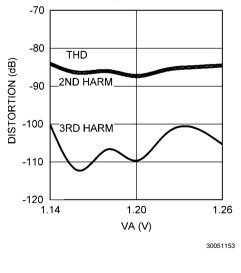

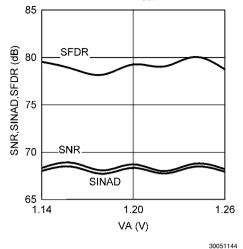

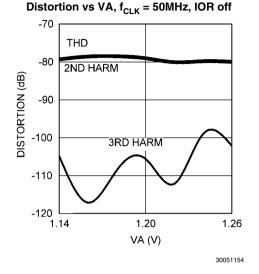

**Typical Performance Characteristics** Unless otherwise specified, the following conditions apply:  $V_A = V_D = 1.2V$ ;  $V_{DR} = 1.2V$ ;  $V_{REF} =$  internal;  $C_L = 5pF$ ;  $f_{CLK} = 50MHz$ ;  $f_S = 50MSPS$ ;  $f_{IN} = 10MHz$ . Units for SNR and SINAD are dBFS. Units for SFDR and Distortion are dBc.

#### SNR, SINAD, SFDR vs VA, f<sub>CLK</sub> = 50MHz, IOR off

SNR, SINAD, SFDR vs Temperature, f<sub>CLK</sub> = 50MHz, IOR off

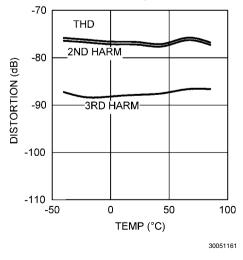

Distortion vs Temperature, f<sub>CLK</sub> = 40MHz, IOR off

Distortion vs Temperature, f<sub>CLK</sub> = 50MHz, IOR off

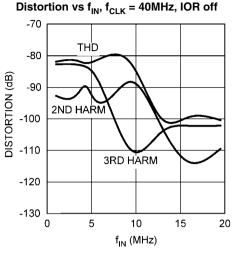

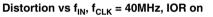

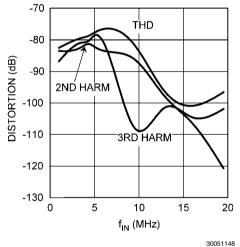

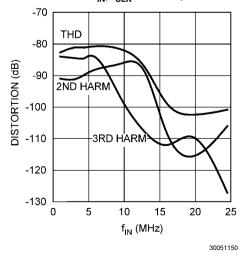

**Typical Performance Characteristics** Unless otherwise specified, the following conditions apply:  $V_A = V_D = 1.2V$ ;  $V_{DR} = 1.2V$ ;  $V_{REF} =$  internal;  $C_L = 5pF$ ;  $f_{CLK} = 50MHz$ ;  $f_S = 50MSPS$ ;  $f_{IN} = 10MHz$ . Units for SNR and SINAD are dBFS. Units for SFDR and Distortion are dBc.

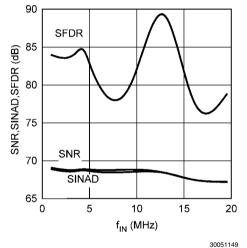

SNR, SINAD, SFDR vs f<sub>IN</sub>, f<sub>CLK</sub> = 40MHz, IOR off

SNR, SINAD, SFDR vs f<sub>IN</sub>, f<sub>CLK</sub> = 40MHz, IOR on

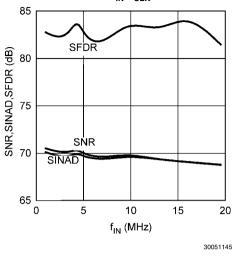

SNR, SINAD, SFDR vs  $f_{IN}$ ,  $f_{CLK}$  = 50MHz, IOR off

30051146

Distortion vs  $f_{IN}$ ,  $f_{CLK} = 50MHz$ , IOR off

**Typical Performance Characteristics** Unless otherwise specified, the following conditions apply:  $V_A = V_D = 1.2V$ ;  $V_{DR} = 1.2V$ ;  $V_{REF} =$  internal;  $C_L = 5pF$ ;  $f_{CLK} = 50MHz$ ;  $f_S = 50MSPS$ ;  $f_{IN} = 10MHz$ . Units for SNR and SINAD are dBFS. Units for SFDR and Distortion are dBc.

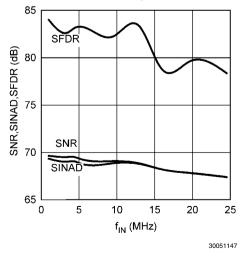

SNR, SINAD, SFDR vs  $f_{IN}$ ,  $f_{CLK} = 50MHz$ , IOR on

Histogram of output code for zero input

Spectral Response @ f<sub>IN1</sub>= 9.6MHz, f<sub>IN2</sub>= 10.1MHz, IOR off Spectral Response @ f<sub>IN1</sub>= 9.6MHz, f<sub>IN2</sub>= 10.1MHz, IOR on

Current vs f<sub>CLK</sub>, Equalizer off, LVDS output

## **Functional Description**

The ADC12EU050 employs a number of unique strategies to provide a high performance multi-channel ADC that offers a significant power consumption reduction when compared to compteting architectures, as well as easing system level design. The ultra-low power performance of the ADC12EU050 is derived from the implementation of a fast continuous time sigma delta (CT $\Sigma\Delta$ ) modulator. Other features of this technology are:

- Intrinsic anti-alias filter the digital decimating filter provides an intrinsic anti-alias filter, eliminating external analog filter components, and simplifying multi-channel designs.

- Instant overload recovery (IOR) system guarantees extremely fast recovery from overload (<1ps), and no settling errors on return from overload.

- · Ultra-low inter-channel crosstalk.

- Digital Equalizer provides low group delay and hence minimizes signal path delay variation.

The major signal path blocks are: clipping control;  $CT\Sigma\Delta$  modulator; digital decimation filter; 12 bit serializer; and finally the LVDS/SLVS outputs. The PLL is critical to the operation of the ADC12EU050, and the PLL also provides the bit and word clock outputs. The SPI Control Interface gives uncomplicated user access to the ADC registers.

#### 1.0 12-BIT SIGMA DELTA ADC CORE

The ADC12EU050 comprises eight analog ADC channels using a  $CT\sum\Delta$  architecture, which provides very high dynamic performance with ultra-low power, while operating from a minimal 1.2V supply.

The CT $\Delta$  ADC architecture uses a third order sigma delta modulator operating at a nominal 16 times over-sampling rate in combination with a 3-bit quantizer. The modulator output is coupled to a power efficient digital decimation filter that decimates the high rate modulator output (640 to 800MHz) to provide output data at a sample rate between 40 MSPS and 50 MSPS.

A benefit of the CT $\sum\Delta$  design is that the ADC requires no external anti-alias filters for most applications. This benefit is derived from a combination of the design of the analog sigma delta modulator and digital decimation filter. The digital filter achieves a steep transition band, and provides 72 dB of attenuation in the stop band. Using the digital equalizer, the signal transfer characteristics including phase performance can be optimized so as to minimise group delay variation. In applications where it is not required, the digital equalizer can be disabled to further save power.

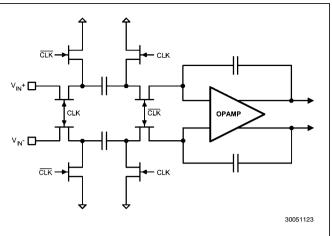

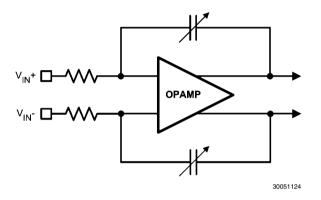

#### **1.1 DIFFERENTIAL INPUT STAGE**

The ADC can capture high speed analog signals without resorting to a complex fast sample-and-hold amplifier (SHA) as used in pipeline ADCs. This is where  $CT\sum\Delta$  technology derives much of its power and performance benefits. This feature also assists external circuit design. In the case of the SHA inputs of pipeline ADCs, the effective input capacitance is time variant, requiring a powerful input buffer to drive to the resolution limits of the system. The input stage of the ADC is purely resistive (1.3k $\Omega$  single ended) driving into virtual earth. As a result the ADC12EU050 is extremely easy to drive as its input impedance is not complex. It also means that external lower power input buffering circuitry can used, and can be completely eliminated in some cases.

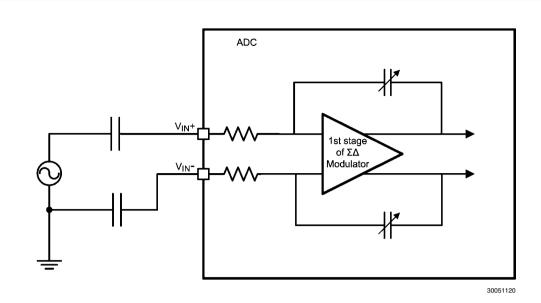

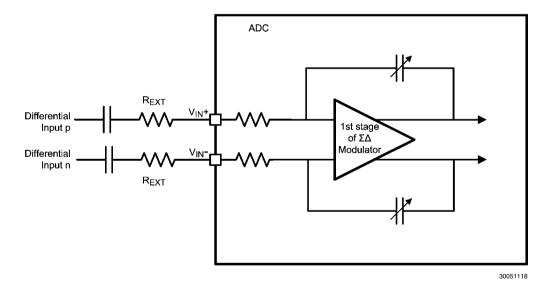

FIGURE 5. SHA Input Stage

#### FIGURE 6. Continuous Time Sigma Delta Input Stage

#### **1.2 INSTANT OVERLOAD RECOVERY**

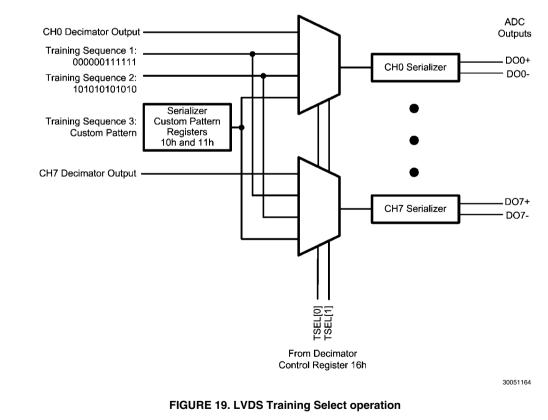

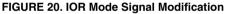

The ADC12EU050 features an overload handling system which provides instantaneous recovery from signals driving the ADC inputs beyond the full-scale input range. The ADC can operate in two different modes. In the default ADC mode (IOR mode off) a full-scale input range of 2.10  $V_{PP}$  is supported, here the ADC operates with some inherent overload recovery time, similar to a conventional ADC.

In the IOR mode, the ADC has a reduced 1.56 V<sub>PP</sub> full scale input range, but provides a significant benefit in that the ADC can now be driven by input voltages as high as 5 dB beyond the nominal full-scale ( $f_{\rm IN}$  < 12MHz), that is 2.75 V<sub>PP</sub>, and will recover instantaneously. In a number of applications this feature can help simplify input stage design and manufacturing set-up and calibration. The ADC12EU050 recovers immediately from overload with no missing codes and no settling time.

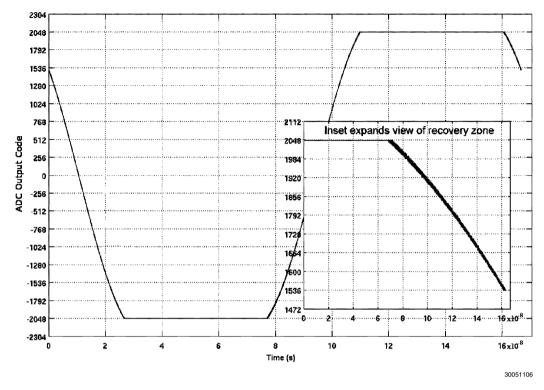

The proprietary strategy used within the ADC12EU050 uses high speed patented clamp techniques to limit the input signal and keep it within the stable input range of the ADC. This process happens at a speed equivalent to the on-chip oversampling rate of 640 to 800 MHz. The advantage of this system is that it responds immediately to out of range signals. While the inputs are over-range the ADC outputs a full scale result. As the over-range input is removed the ADC adjusts to the input signal level and is able to provide sampled data instantaneously. The ADC's behaviour on emerging from overload is repeatable and independent of whether the input signal was positive or negative going at the point of overload. The diagram below shows a 5dB overloaded input (2.75  $V_{PP}$  versus 1.56  $V_{PP}$  Full scale), with 240,000 sample periods

FIGURE 7. Instant Overload Recovery

#### **1.3 INTEGRATED PRECISION LC PLL**

The ADC12EU050 family includes an integrated high performance "clean up" phase locked loop (PLL), simplifying the need for a low jitter external clock. The PLL serves three important functions; it generates a highly accurate internal sampling clock source of up to 800 MHz; a clock for the LVDS serializers at 600 MHz; and it provides a low jitter clock for other internal components. With its jitter clean-up capability this PLL allows lower performance system clocks to be used.

#### **1.4 DIGITAL DECIMATION FILTER AND EQUALIZER**

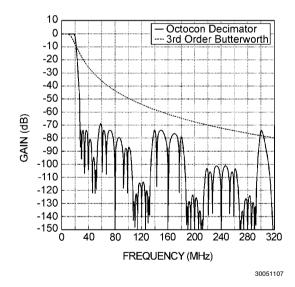

The digital decimation filter is an integral part of the sigma delta architecture. It decimates the over-sampled data from the modulator down to the sample rate, and its extremely sharp low pass characteristic combined with the modulator's broad band response provides the intrinsic anti-alias filter. The digital low pass filter exhibits 72dB of attenuation in the stop band. The following diagram shows the digital filter transfer function at 40MSPS, compared to a third order Butterworth transfer function. Due to the digital implementation of the filter, the filter parameters automatically scale with the ADC sampling frequency.

FIGURE 8. Digital Filter Transfer Function

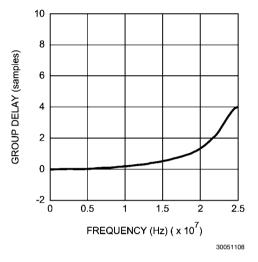

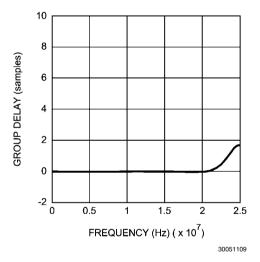

Such steep digital filters introduce group delay problems, but the ADC12EU050 includes a digital equalizer, which reduces group delay ripple variation to less than 0.05 samples. In applications where group delay is not of concern, the equalizer can be turned off through the SPI interface in order to save power.

The following two diagrams show the group delay ripple of the digital decimation filter at 50MSPS, firstly with the equalizer disabled, and secondly with the equalizer enabled.

FIGURE 9. Group Delay with Equalizer Off

FIGURE 10. Group Delay with Equalizer On

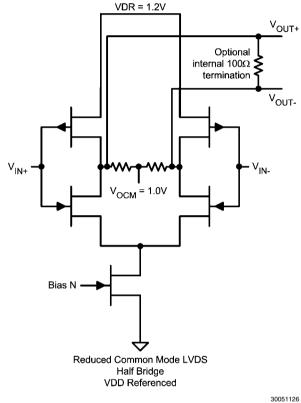

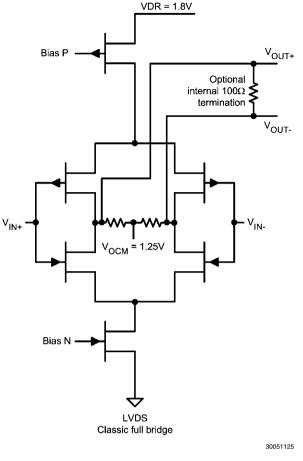

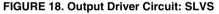

#### **1.5 SERIAL DATA OUTPUTS**

Sampled data is transformed into high speed serial LVDS/ SLVS output data streams. The low amplitude differential signal swings of LVDS/SLVS help to reduce digital system noise. It is possible to select between LVDS and SLVS modes by simple programming through the SPI control interface. The output common mode can also be programmed through the SPI control interface, allowing it to be adjusted based on the value of  $V_{DR}$ .

#### **1.6 POWER MANAGEMENT MODES**

The ADC12EU050 operates normally at ultra-low power levels. In addition, several power management modes are provided:

- Power Down (accessible through PD bit of Top Control Register)

- Sleep (SLEEP pin, or SLEEP bit of Top Control Register)

- Single channel power down (PD0-7 of ADC/LVDS Channel Power Down Register)

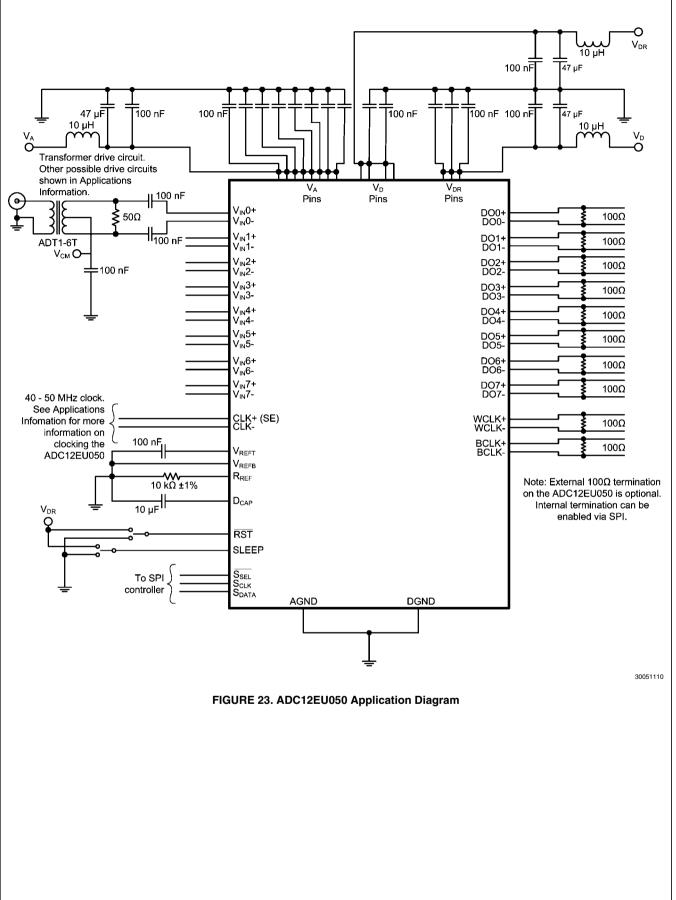

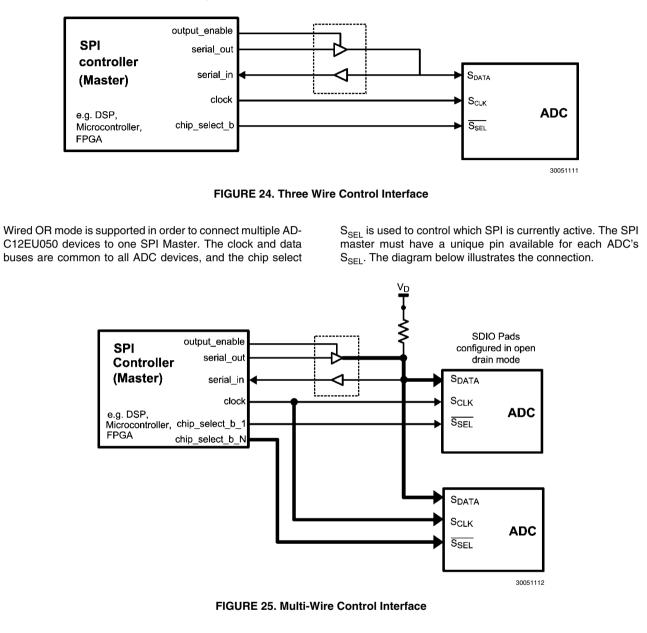

Power Down is the lowest power consumption mode, but with a longer wake-up time than Sleep mode. In power down mode, all circuits in the chip are turned off, including the PLL, reference and bias circuits.