### **Features**

- Serial Peripheral Interface (SPI) Compatible

- Supports SPI Modes 0 (0,0) and 3 (1,1) - Datasheet Describes Mode 0 Operation

- Low-voltage and Standard-voltage Operation

- 1.8 (V<sub>cc</sub> = 1.8V to 5.5V)

- 20 MHz Clock Rate (5V)

- 32-byte Page Mode

- Block Write Protection

- Protect 1/4, 1/2, or Entire Array

- Write Protect (WP) Pin and Write Disable Instructions for Both Hardware and Software **Data Protection**

- Self-timed Write Cycle (5 ms max)

- High Reliability

- Endurance: One Million Write Cycles

- Data Retention: 100 Years

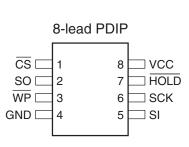

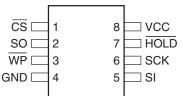

- 8-lead JEDEC PDIP, 8-lead JEDEC SOIC, 8-lead Ultra Thin Mini-MAP (MLP 2x3), 8-lead TSSOP and 8-ball dBGA2 Packages

- Die Sales: Wafer Form, Tape and Reel, and Bumped Wafers

## Description

Table 0-1

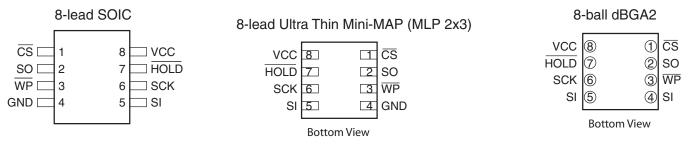

The AT25080B/160B provides 8192/16384 bits of serial electrically-erasable programmable read-only memory (EEPROM) organized as 1024/2048 words of 8 bits each. The device is optimized for use in many industrial and commercial applications where low-power and low-voltage operation are essential. The AT25080B/160B is available in space-saving 8-lead PDIP, 8-lead JEDEC SOIC, 8-lead Ultra Thin Mini-MAP (MLP 2x3) and 8-lead TSSOP packages.

The AT25080B/160B is enabled through the Chip Select pin  $\overline{(CS)}$  and accessed via a three-wire interface consisting of Serial Data Input (SI), Serial Data Output (SO), and Serial Clock (SCK). All programming cycles are completely self-timed, and no separate erase cycle is required before write.

|          | Fin Connyuration      |

|----------|-----------------------|

| Pin Name | Function              |

| CS       | Chip Select           |

| SCK      | Serial Data Clock     |

| SI       | Serial Data Input     |

| SO       | Serial Data Output    |

| GND      | Ground                |

| VCC      | Power Supply          |

| WP       | Write Protect         |

| HOLD     | Suspends Serial Input |

Pin Configuration

#### 8-lead TSSOP

**SPI Serial EEPROMs** 8K (1024 x 8) 16K (2048 x 8)

# AT25080B AT25160B

# Preliminary

5228B-SEEPR-7/08

Block write protection is enabled by programming the status register with one of four blocks of write protection. Separate program enable and program disable instructions are provided for additional data protection. Hardware data protection is provided via the  $\overline{WP}$  pin to protect against inadvertent write attempts to the status register. The HOLD pin may be used to suspend any serial communication without resetting the serial sequence.

### **Absolute Maximum Ratings\***

| Operating Temperature55°C to +125°C | *NOTICE: Stresses beyond those listed under "Absolute<br>Maximum Ratings" may cause permanent dam-     |

|-------------------------------------|--------------------------------------------------------------------------------------------------------|

| Storage Temperature65°C to +150°C   | age to the device. This is a stress rating only and functional operation of the device at these or any |

| Voltage on Any Pin                  | other conditions beyond those indicated in the                                                         |

| with Respect to Ground1.0V to +7.0V | operational sections of this specification is not<br>implied. Exposure to absolute maximum rating      |

| Maximum Operating Voltage 6.25V     | conditions for extended periods may affect device reliability.                                         |

| DC Output Current 5.0 mA            | ichability.                                                                                            |

## <sup>2</sup> AT25080B/160B [Preliminary]

Figure 0-1. Block Diagram

#### **Table 0-2.**Pin Capacitance<sup>(1)</sup>

| Applicable over recommended o | $\mathbf{T}_{\mathbf{T}} = \mathbf{T}_{\mathbf{T}}$ |                                                        | (unloss otherwise noted) |

|-------------------------------|-----------------------------------------------------|--------------------------------------------------------|--------------------------|

| ADDIICADIE OVEL LECOMMENDEU O | Defaultu fattue from $1_{\Lambda} = 23$             | $0 \ 0.1 = 1.0 \  V  \square Z. \ V \cap C = +0.0 \ V$ | (unless otherwise noted) |

|                               |                                                     | ,                                                      | (                        |

| Symbol           | Test Conditions                           | Мах | Units | Conditions     |

|------------------|-------------------------------------------|-----|-------|----------------|

| C <sub>OUT</sub> | Output Capacitance (SO)                   | 8   | pF    | $V_{OUT} = 0V$ |

| C <sub>IN</sub>  | Input Capacitance (CS, SCK, SI, WP, HOLD) | 6   | pF    | $V_{IN} = 0V$  |

Note: 1. This parameter is characterized and is not 100% tested.

#### Table 0-3.DC Characteristics

| Applicable over recommended o | perating range from: T <sub>ell</sub> = | $= -40^{\circ}$ C to $+85^{\circ}$ C. V <sub>eo</sub> $= +$ | 1.8V to +5.5V ( | unless otherwise noted) |

|-------------------------------|-----------------------------------------|-------------------------------------------------------------|-----------------|-------------------------|

|                               |                                         |                                                             |                 |                         |

|                               |                                         |                                                             |                 |                         |

| Symbol           | Parameter      | Test Condition                                    | Min | Тур | Max  | Units |

|------------------|----------------|---------------------------------------------------|-----|-----|------|-------|

| V <sub>CC1</sub> | Supply Voltage |                                                   | 1.8 |     | 5.5  | V     |

| V <sub>CC2</sub> | Supply Voltage |                                                   | 2.7 |     | 5.5  | V     |

| V <sub>CC3</sub> | Supply Voltage |                                                   | 4.5 |     | 5.5  | V     |

| I <sub>CC1</sub> | Supply Current | V <sub>CC</sub> = 5.0V at 20 MHz, SO = Open, Read |     | 7.5 | 10.0 | mA    |

| I <sub>CC2</sub> | Supply Current | $V_{CC}$ = 5.0V at 20 MHz, SO = Open, Read, Write |     | 4.0 | 10.0 | mA    |

| Symbol                         | Parameter           | Test Condition                                     |                           | Min                   | Тур   | Max                   | Units |

|--------------------------------|---------------------|----------------------------------------------------|---------------------------|-----------------------|-------|-----------------------|-------|

| I <sub>CC3</sub>               | Supply Current      | V <sub>CC</sub> = 5.0V at 5 MHz, S0<br>Read, Write | O = Open,                 |                       | 4.0   | 6.0                   | mA    |

| I <sub>SB1</sub>               | Standby Current     | $V_{CC} = 1.8V, \overline{CS} = V_{CC}$            |                           |                       | < 0.1 | 6.0 <sup>(2)</sup>    | μA    |

| I <sub>SB2</sub>               | Standby Current     | $V_{CC} = 2.7V, \overline{CS} = V_{CC}$            |                           |                       | 0.3   | 7.0 <sup>(2)</sup>    | μA    |

| I <sub>SB3</sub>               | Standby Current     | $V_{CC} = 5.0V, \overline{CS} = V_{CC}$            |                           |                       | 2.0   | 10.0 <sup>(2)</sup>   | μA    |

| I <sub>IL</sub>                | Input Leakage       | $V_{IN} = 0V$ to $V_{CC}$                          |                           | -3.0                  |       | 3.0                   | μA    |

| I <sub>OL</sub>                | Output Leakage      | $V_{IN} = 0V$ to $V_{CC}$ , $T_{AC} = 0^{\circ}$   | °C to 70°C                | -3.0                  |       | 3.0                   | μA    |

| V <sub>IL</sub> <sup>(1)</sup> | Input Low-voltage   |                                                    |                           | -0.6                  |       | V <sub>CC</sub> x 0.3 | V     |

| V <sub>IH</sub> <sup>(1)</sup> | Input High-voltage  |                                                    |                           | V <sub>CC</sub> x 0.7 |       | V <sub>CC</sub> + 0.5 | V     |

| V <sub>OL1</sub>               | Output Low-voltage  |                                                    | I <sub>OL</sub> = 3.0 mA  |                       |       | 0.4                   | V     |

| V <sub>OH1</sub>               | Output High-voltage | $4.5V \le V_{CC} \le 5.5V$                         | I <sub>OH</sub> = -1.6 mA | V <sub>CC</sub> - 0.8 |       |                       | V     |

| V <sub>OL2</sub>               | Output Low-voltage  |                                                    | I <sub>OL</sub> = 0.15 mA |                       |       | 0.2                   | V     |

| V <sub>OH2</sub>               | Output High-voltage | $1.8V \le V_{CC} \le 3.6V$                         | I <sub>OH</sub> = -100 μA | V <sub>CC</sub> - 0.2 |       |                       | V     |

Applicable over recommended operating range from:  $T_{AI} = -40^{\circ}C$  to  $+85^{\circ}C$ ,  $V_{CC} = +1.8V$  to +5.5V (unless otherwise noted)

Notes: 1.  $V_{IL}$  min and  $V_{IH}$  max are reference only and are not tested.

2. Worst case measured at  $85^{\circ}C$

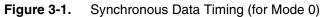

#### Table 0-4.AC Characteristics

Applicable over recommended operating range from  $T_{AI} = -40^{\circ}C$  to  $+85^{\circ}C$ ,  $V_{CC} = As$  Specified, CL = 1 TTL Gate and 30 pF (unless otherwise noted)

| Symbol           | Parameter           | Voltage                       | Min             | Max            | Units |

|------------------|---------------------|-------------------------------|-----------------|----------------|-------|

| f <sub>scк</sub> | SCK Clock Frequency | 4.5–5.5<br>2.7–5.5<br>1.8–5.5 | 0<br>0<br>0     | 20<br>10<br>5  | MHz   |

| t <sub>RI</sub>  | Input Rise Time     | 4.5–5.5<br>2.7–5.5<br>1.8–5.5 |                 | 2<br>2<br>2    | μs    |

| t <sub>ei</sub>  | Input Fall Time     | 4.5–5.5<br>2.7–5.5<br>1.8–5.5 |                 | 2<br>2<br>2    | μs    |

| t <sub>wH</sub>  | SCK High Time       | 4.5–5.5<br>2.7–5.5<br>1.8–5.5 | 20<br>40<br>80  |                | ns    |

| <sup>t</sup> wL  | SCK Low Time        | 4.5–5.5<br>2.7–5.5<br>1.8–5.5 | 20<br>40<br>80  |                | ns    |

| t <sub>cs</sub>  | CS High Time        | 4.5–5.5<br>2.7–5.5<br>1.8–5.5 | 25<br>50<br>100 |                | ns    |

| css              | CS Setup Time       | 4.5–5.5<br>2.7–5.5<br>1.8–5.5 | 25<br>50<br>100 |                | ns    |

| ссян             | CS Hold Time        | 4.5–5.5<br>2.7–5.5<br>1.8–5.5 | 25<br>50<br>100 |                | ns    |

| su               | Data In Setup Time  | 4.5–5.5<br>2.7–5.5<br>1.8–5.5 | 5<br>10<br>20   |                | ns    |

| н                | Data In Hold Time   | 4.5–5.5<br>2.7–5.5<br>1.8–5.5 | 5<br>10<br>20   |                | ns    |

| Н                | HOLD Setup Time     | 4.5–5.5<br>2.7–5.5<br>1.8–5.5 | 5<br>10<br>20   |                |       |

| СD               | HOLD Hold Time      | 4.5–5.5<br>2.7–5.5<br>1.8–5.5 | 5<br>10<br>20   |                | ns    |

| t <sub>v</sub>   | Output Valid        | 4.5–5.5<br>2.7–5.5<br>1.8–5.5 | 0<br>0<br>0     | 20<br>40<br>80 | ns    |

| t <sub>HO</sub>  | Output Hold Time    | 4.5–5.5<br>2.7–5.5<br>1.8–5.5 | 0<br>0<br>0     |                | ns    |

Table 0-4.

AC Characteristics (Continued)

Applicable over recommended operating range from  $T_{AI} = -40^{\circ}C$  to +85°C,  $V_{CC}$  = As Specified,

#### CL = 1 TTL Gate and 30 pF (unless otherwise noted)

| Symbol                   | Parameter             | Voltage                       | Min         | Max             | Units        |

|--------------------------|-----------------------|-------------------------------|-------------|-----------------|--------------|

| t <sub>LZ</sub>          | HOLD to Output Low Z  | 4.5–5.5<br>2.7–5.5<br>1.8–5.5 | 0<br>0<br>0 | 25<br>50<br>100 | ns           |

| t <sub>HZ</sub>          | HOLD to Output High Z | 4.5–5.5<br>2.7–5.5<br>1.8–5.5 |             | 40<br>80<br>200 | ns           |

| t <sub>DIS</sub>         | Output Disable Time   | 4.5–5.5<br>2.7–5.5<br>1.8–5.5 |             | 40<br>80<br>200 | ns           |

| t <sub>WC</sub>          | Write Cycle Time      | 4.5–5.5<br>2.7–5.5<br>1.8–5.5 |             | 5<br>5<br>5     | ms           |

| Endurance <sup>(1)</sup> | 3.3V, 25°C, Page Mode |                               | 1M          |                 | Write Cycles |

Note: 1. This parameter is characterized and is not 100% tested.

### 1. Serial Interface Description

MASTER: The device that generates the serial clock.

**SLAVE:** Because the Serial Clock pin (SCK) is always an input, the AT25080B/160B always operates as a slave.

**TRANSMITTER/RECEIVER:** The AT25080B/160B has separate pins designated for data transmission (SO) and reception (SI).

**MSB:** The Most Significant Bit (MSB) is the first bit transmitted and received.

**SERIAL OP-CODE:** After the device is selected with  $\overline{CS}$  going low, the first byte will be received. This byte contains the op-code that defines the operations to be performed.

**INVALID OP-CODE:** If an invalid op-code is received, no data will be shifted into the AT25080B/160B, and the serial output pin (SO) will remain in a high impedance state until the falling edge of  $\overline{CS}$  is detected again. This will reinitialize the serial communication.

**CHIP SELECT:** The AT25080B/160B is selected when the  $\overline{CS}$  pin is low. When the device is not selected, data will not be accepted via the SI pin, and the serial output pin (SO) will remain in a high impedance state.

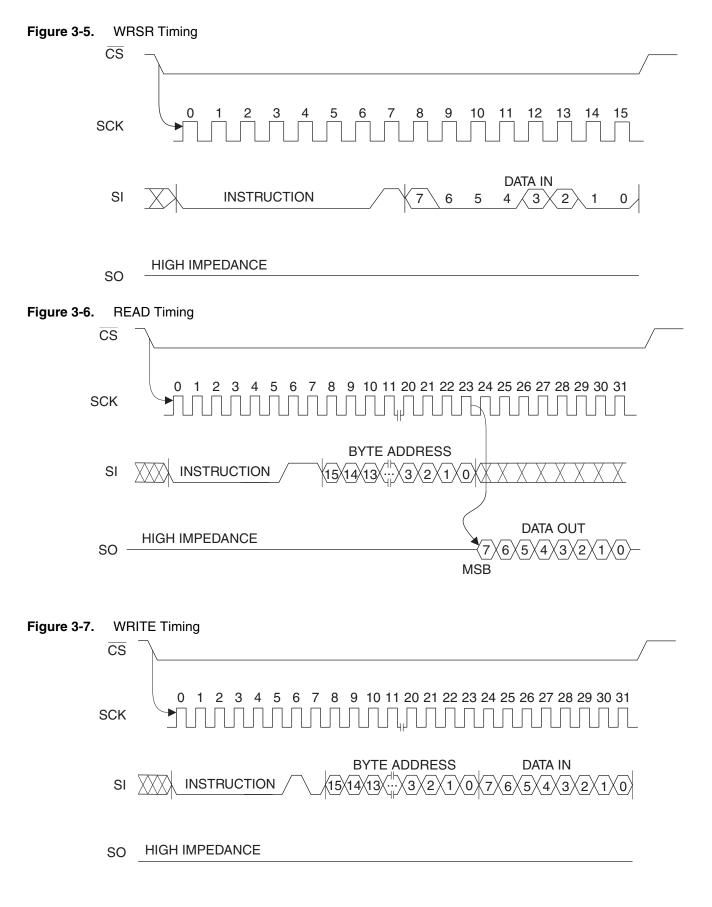

**HOLD:** The HOLD pin is used in conjunction with the  $\overline{CS}$  pin to select the AT25080B/160B. When the device is selected and a serial sequence is underway, HOLD can be used to pause the serial communication with the master device without resetting the serial sequence. To pause, the HOLD pin must be brought low while the SCK pin is low. To resume serial communication, the HOLD pin is brought high while the SCK pin is low (SCK may still toggle during HOLD). Inputs to the SI pin will be ignored while the SO pin is in the high impedance state.

**WRITE PROTECT:** The write protect pin ( $\overline{WP}$ ) will allow normal read/write operations when held high. When the WP pin is brought low and WPEN bit is "1", all write operations to the status register are inhibited.  $\overline{WP}$  going low while  $\overline{CS}$  is still low will interrupt a write to the status register. If the internal write cycle has already been initiated,  $\overline{WP}$  going low will have no effect on any write

operation to the status register. The  $\overline{WP}$  pin function is blocked when the WPEN bit in the status register is "0". This will allow the user to install the AT25080B/160B in a system with the  $\overline{WP}$  pin tied to ground and still be able to write to the status register. All  $\overline{WP}$  pin functions are enabled when the WPEN bit is set to "1".

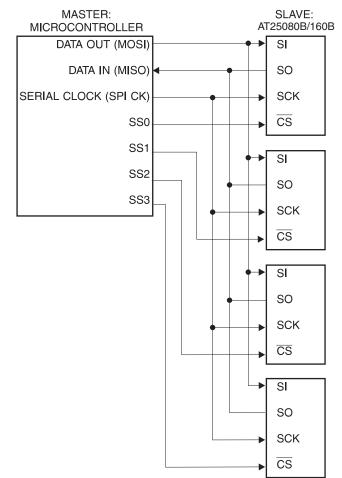

#### Figure 1-1. SPI Serial Interface

### 2. Functional Description

The AT25080B/160B is designed to interface directly with the synchronous serial peripheral interface (SPI) of the 6805 and 68HC11 series of microcontrollers.

The AT25080B/160B utilizes an 8-bit instruction register. The list of instructions and their operation codes are contained in Table 2-1. All instructions, addresses, and data are transferred with the MSB first and start with a high-to-low CS transition.

| Instruction Name | Instruction Format | Operation                |

|------------------|--------------------|--------------------------|

| WREN             | 0000 X110          | Set Write Enable Latch   |

| WRDI             | 0000 X100          | Reset Write Enable Latch |

| RDSR             | 0000 X101          | Read Status Register     |

Table 2-1.

Instruction Set for the AT25080B/160B

| Instruction Name | Instruction Format | Operation                   |

|------------------|--------------------|-----------------------------|

| WRSR             | 0000 X001          | Write Status Register       |

| READ             | 0000 X011          | Read Data from Memory Array |

| WRITE            | 0000 X010          | Write Data to Memory Array  |

| Table 2-1. Instruction Set for the AT25080B/160E |

|--------------------------------------------------|

|--------------------------------------------------|

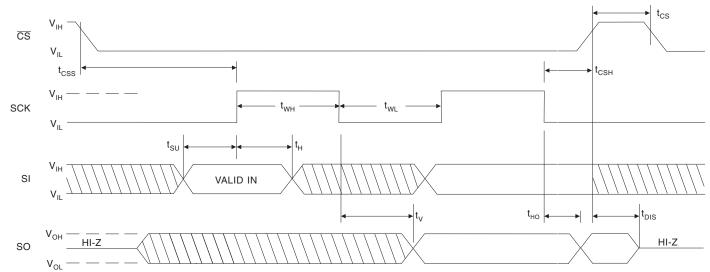

**WRITE ENABLE (WREN):** The device will power up in the write disable state when V<sub>CC</sub> is applied. All programming instructions must therefore be preceded by a Write Enable instruction.

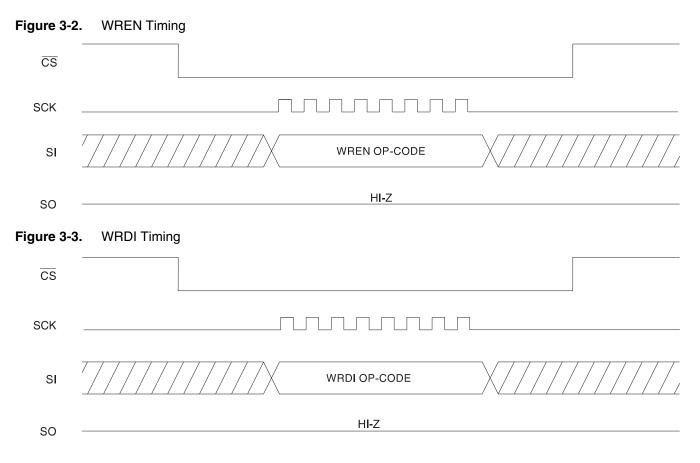

WRITE DISABLE (WRDI): To protect the device against inadvertent writes, the Write Disable instruction disables all programming modes. The WRDI instruction is independent of the status of the WP pin.

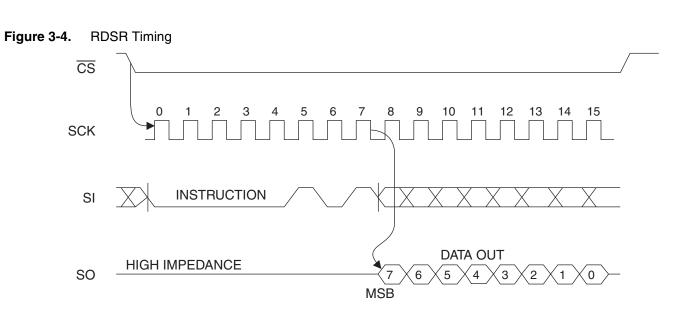

**READ STATUS REGISTER (RDSR):** The Read Status Register instruction provides access to the status register. The READY/BUSY and Write Enable status of the device can be determined by the RDSR instruction. Similarly, the Block Write Protection Bits indicate the extent of protection employed. These bits are set by using the WRSR instruction.

Table 2-2.Status Register Format

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| WPEN  | Х     | Х     | Х     | BP1   | BP0   | WEN   | RDY   |

Table 2-3.

Read Status Register Bit Definition

| Bit                                                                                                                                            | Definition                                                                                               |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--|--|

| Bit 0 ( $\overline{RDY}$ ) Bit 0 = "0" ( $\overline{RDY}$ ) indicates the device is READY. Bit 0 = "1" indicates the write cyclis in progress. |                                                                                                          |  |  |

| Bit 1 (WEN)                                                                                                                                    | Bit 1= "0" indicates the device is not WRITE ENABLED. Bit 1 = "1" indicates the device is write enabled. |  |  |

| Bit 2 (BP0)                                                                                                                                    | See Table 2-4 on page 9.                                                                                 |  |  |

| Bit 3 (BP1) See Table 2-4 on page 9.                                                                                                           |                                                                                                          |  |  |

| Bits 4–6 are "0"s when device is not in an internal write cycle.                                                                               |                                                                                                          |  |  |

| Bit 7 (WPEN) See Table 2-5 on page 9.                                                                                                          |                                                                                                          |  |  |

| Bits 0–7 are "1"s during an internal write cycle.                                                                                              |                                                                                                          |  |  |

**WRITE STATUS REGISTER (WRSR):** The WRSR instruction allows the user to select one of four levels of protection. The AT25080B/160B is divided into four array segments. One-quarter, one-half, or all of the memory segments can be protected. Any of the data within any selected segment will therefore be read only. The block write protection levels and corresponding status register control bits are shown in Table 2-4.

The three bits BP0, BP1, and WPEN are nonvolatile cells that have the same properties and functions as the regular memory cells (e.g., WREN, t<sub>WC</sub>, RDSR).

|        | Status Re | gister Bits | Array Addresses Protected |           |  |

|--------|-----------|-------------|---------------------------|-----------|--|

| Level  | BP1       | BP0         | AT25080B                  | AT25160B  |  |

| 0      | 0         | 0           | None                      | None      |  |

| 1(1/4) | 0         | 1           | 0300-03FF                 | 0600-07FF |  |

| 2(1/2) | 1         | 0           | 0200-03FF                 | 0400-07FF |  |

| 3(All) | 1         | 1           | 0000-03FF                 | 0000-07FF |  |

Table 2-4.

Block Write Protect Bits

The WRSR instruction also allows the user to enable or disable the write protect ( $\overline{WP}$ ) pin through the use of the Write Protect Enable (WPEN) bit. Hardware write protection is enabled when the  $\overline{WP}$  pin is low and the WPEN bit is "1". Hardware write protection is disabled when either the  $\overline{WP}$  pin is high or the WPEN bit is "0". When the device is hardware write protected, writes to the status register, including the block protect bits and the WPEN bit, and the block-protected sections in the memory array are disabled. Writes are only allowed to sections of the memory that are not block-protected.

**NOTE:** When the WPEN bit is hardware write protected, it cannot be changed back to "0" as long as the  $\overline{WP}$  pin is held low.

| WPEN | WP   | WEN | Protected<br>Blocks | Unprotected<br>Blocks | Status<br>Register |

|------|------|-----|---------------------|-----------------------|--------------------|

| 0    | Х    | 0   | Protected           | Protected             | Protected          |

| 0    | Х    | 1   | Protected           | Writeable             | Writeable          |

| 1    | Low  | 0   | Protected           | Protected             | Protected          |

| 1    | Low  | 1   | Protected           | Writeable             | Protected          |

| Х    | High | 0   | Protected           | Protected             | Protected          |

| Х    | High | 1   | Protected           | Writeable             | Writeable          |

Table 2-5.WPEN Operation

**READ SEQUENCE (READ):** Reading the AT25080B/160B via the Serial Output (SO) pin requires the following sequence. After the  $\overline{CS}$  line is pulled low to select a device, the read opcode is transmitted via the SI line followed by the byte address to be read (A15–A0, see Table 2-6). Upon completion, any data on the SI line will be ignored. The data (D7–D0) at the specified address is then shifted out onto the SO line. If only one byte is to be read, the  $\overline{CS}$  line should be driven high after the data comes out. The read sequence can be continued since the byte address is automatically incremented and data will continue to be shifted out. When the highest address is reached, the address counter will roll over to the lowest address allowing the entire memory to be read in one continuous read cycle.

**WRITE SEQUENCE (WRITE):** In order to program the AT25080B/160B, two separate instructions must be executed. First, the device *must be write enabled* via the WREN instruction. Then a write (WRITE) instruction may be executed. Also, the address of the memory location(s) to be programmed must be outside the protected address field location selected by the block write protection level. During an internal write cycle, all commands will be ignored except the RDSR instruction.

A write instruction requires the following sequence. After the  $\overline{CS}$  line is pulled low to select the device, the WRITE op-code is transmitted via the SI line followed by the byte address (A15–A0) and the data (D7–D0) to be programmed (see Table 2-6). Programming will start after the  $\overline{CS}$  pin is brought high. The low-to-high transition of the  $\overline{CS}$  pin must occur during the SCK low-time immediately after clocking in the D0 (LSB) data bit.

The READY/BUSY status of the device can be determined by initiating a read status register (RDSR) instruction. If Bit 0 = "1", the write cycle is still in progress. If Bit 0 = "0", the write cycle has ended. Only the RDSR instruction is enabled during the write programming cycle.

The AT25080B/160B is capable of a 32-byte page write operation. After each byte of data is received, the five low-order address bits are internally incremented by one; the high-order bits of the address will remain constant. If more than 32 bytes of data are transmitted, the address counter will roll over and the previously written data will be overwritten. The AT25080B/160B is automatically returned to the write disable state at the completion of a write cycle.

**NOTE:** If the device is not write-enabled (WREN), the device will ignore the write instruction and will return to the standby state, when  $\overline{CS}$  is brought high. A new  $\overline{CS}$  falling edge is required to reinitiate the serial communication.

| Address         | AT25080B                         | AT25160B                         |

|-----------------|----------------------------------|----------------------------------|

| A <sub>N</sub>  | A <sub>9</sub> –A <sub>0</sub>   | A <sub>10</sub> -A <sub>0</sub>  |

| Don't Care Bits | A <sub>15</sub> -A <sub>10</sub> | A <sub>15</sub> –A <sub>11</sub> |

### 3. Timing Diagrams

### 4. AT25080B Ordering Information

| Ordering Code                                       | Voltage | Package  | <b>Operation Range</b>                            |

|-----------------------------------------------------|---------|----------|---------------------------------------------------|

| AT25080B-PU (Bulk form only)                        | 1.8     | 8P3      |                                                   |

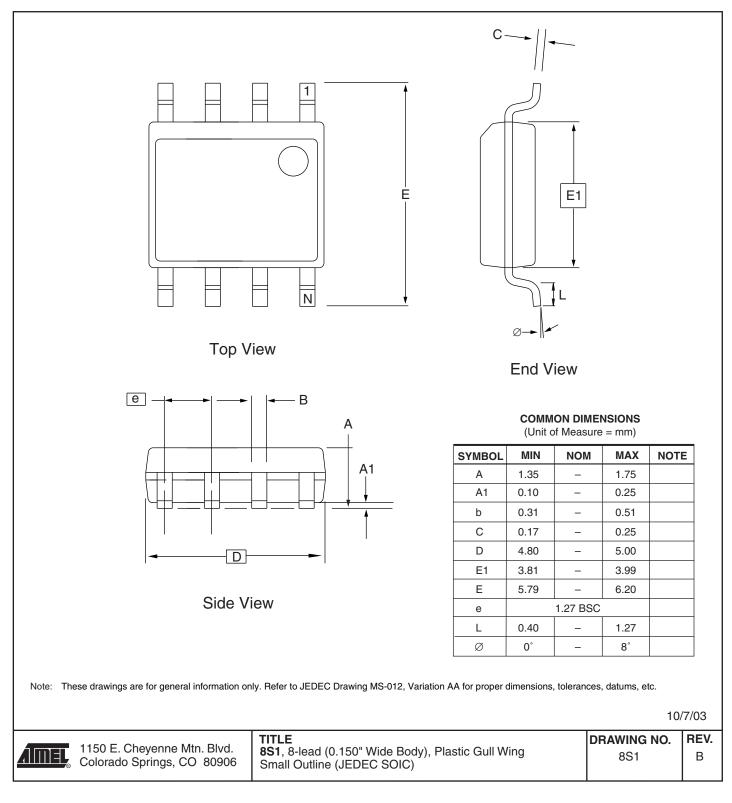

| AT25080BN-SH-B <sup>(1)</sup> (NiPdAu Lead Finish)  | 1.8     | 8S1      |                                                   |

| AT25080BN-SH-T <sup>(2)</sup> (NiPdAu Lead Finish)  | 1.8     | 8S1      |                                                   |

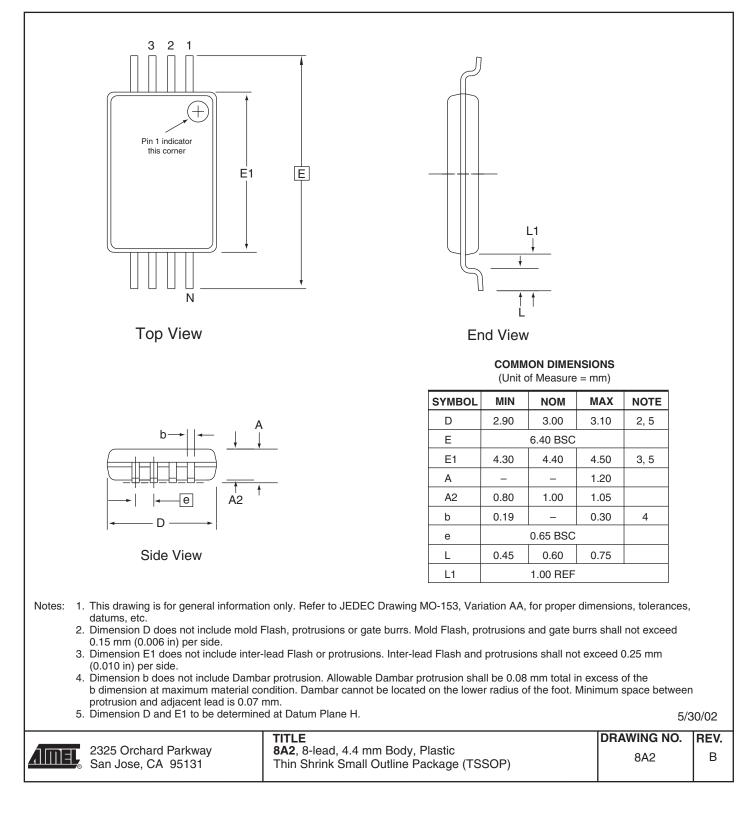

| AT25080B-TH-B <sup>(1)</sup> (NiPdAu Lead Finish)   | 1.8     | 8A2      | Lead-free/Halogen-free/<br>Industrial Temperature |

| AT25080B-TH-T <sup>(2)</sup> (NiPdAu Lead Finish)   | 1.8     | 8A2      | (–40 to 85°C)                                     |

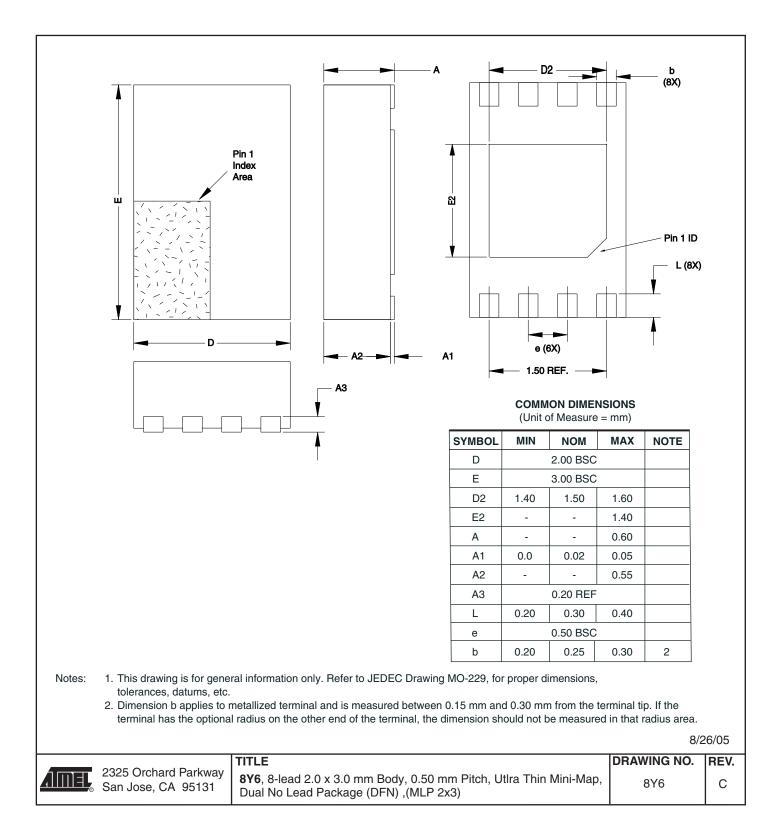

| AT25080BY6-YH-T <sup>(2)</sup> (NiPdAu Lead Finish) | 1.8     | 8Y6      |                                                   |

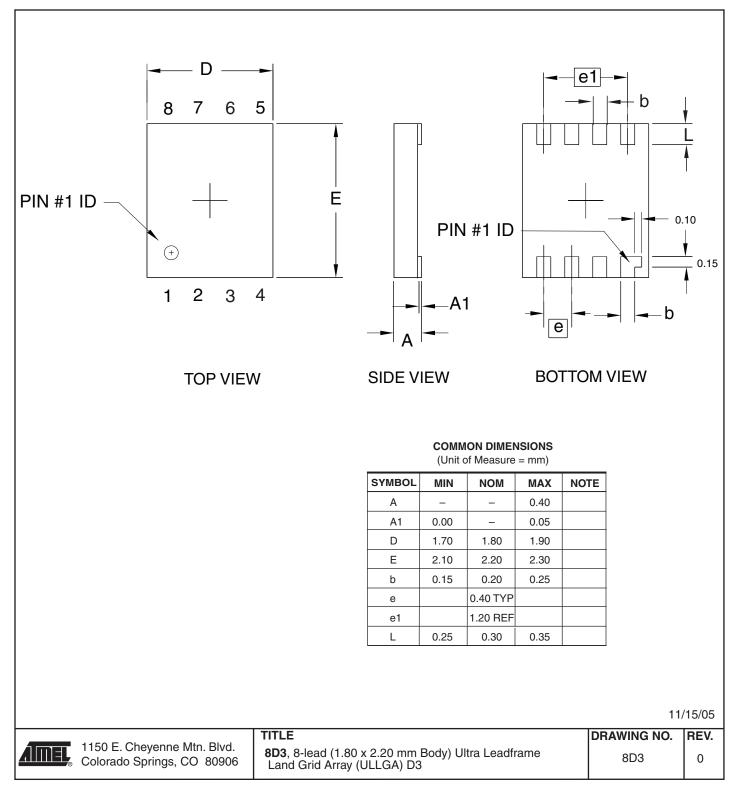

| AT25080BD3-DH-T <sup>(2)</sup>                      | 1.8     | 8D3      |                                                   |

| AT25080BU3-UU-T <sup>(2)</sup> (NiPdAu Lead Finish) | 1.8     | 8U3-1    |                                                   |

| AT25080B-W-11 <sup>(3)</sup>                        | 1.8     | Die Sale | Industrial Temperature<br>(-40 to 85°C)           |

Notes: 1. "B" denotes bulk.

2. "-T" deontes tape and reel. SOIC = 4K per reel. TSSOP, Ultra Thin Mini-MAP, SOT23, and dBGA2 = 5K per reel.

3. Available in waffle pack, tape and reel, and wafer form; order as SL788 for inkless wafer form. Bumped die available upon request. Please contact Serial Interface Marketing.

|       | Package Type                                                                                                 |  |  |  |  |  |

|-------|--------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 8P3   | 8-lead, 0.300" Wide, Plastic Dual Inline Package (PDIP)                                                      |  |  |  |  |  |

| 8S1   | 8-lead, 0.150" Wide, Plastic Gull Wing Small Outline (JEDEC SOIC)                                            |  |  |  |  |  |

| 8A2   | 8-lead, 4.4 mm Body, Plastic Thin Shrink Small Outline Package (TSSOP)                                       |  |  |  |  |  |

| 8Y6   | 8-lead, 2.00 mm x 3.00 mm Body, 0.50 mm Pitch, Ultra Thin Mini-MAP, Dual No Lead Package (DFN), (MLP 2x3 mm) |  |  |  |  |  |

| 8D3   | 8-lead, 1.8 mm x 2.2 mm Body, Ultra axLanda Grid Array (ULLGA)                                               |  |  |  |  |  |

| 8U3-1 | 8-ball, die Ball Grid Array Package (dBGA2)                                                                  |  |  |  |  |  |

|       | Options                                                                                                      |  |  |  |  |  |

| -1.8  | Low Voltage (1.8 to 5.5V)                                                                                    |  |  |  |  |  |

## 5. AT25160B Ordering Information

| Ordering Code                                       | Voltage | Package  | Operation Range                         |

|-----------------------------------------------------|---------|----------|-----------------------------------------|

| AT25160B-PU (Bulk form only)                        | 1.8     | 8P3      |                                         |

| AT25160BN-SH-B <sup>(1)</sup> (NiPdAu Lead Finish)  | 1.8     | 8S1      |                                         |

| AT25160BN-SH-T <sup>(2)</sup> (NiPdAu Lead Finish)  | 1.8     | 8S1      |                                         |

| AT25160B-TH-B <sup>(1)</sup> (NiPdAu Lead Finish)   | 1.8     | 8A2      | Lead-free/Halogen-free/                 |

| AT25160B-TH-T <sup>(2)</sup> (NiPdAu Lead Finish)   | 1.8     | 8A2      | Industrial Temperature<br>(-40 to 85°C) |

| AT25160BY6-YH-T <sup>(2)</sup> (NiPdAu Lead Finish) | 1.8     | 8Y6      | ( +0 10 00 0)                           |

| AT25160BD3-DH-T <sup>(2)</sup>                      | 1.8     | 8D3      |                                         |

| AT25160BU3-UU-T <sup>(2)</sup>                      | 1.8     | 8U3-1    |                                         |

| AT25160B-W-11 <sup>(3)</sup>                        | 1.8     | Die Sale | Industrial Temperature<br>(–40 to 85°C) |

Notes: 1. "B" denotes bulk.

2. "-T" deontes tape and reel. SOIC = 4K per reel. TSSOP, Ultra Thin Mini-MAP, SOT23, and dBGA2 = 5K per reel.

3. Available in tape and reel and wafer form; order as SL788 for inkless wafer form. Bumped die available upon request. Please contact Serial Interface Marketing.

| Package Type |                                                                                                             |  |  |  |

|--------------|-------------------------------------------------------------------------------------------------------------|--|--|--|

| 8P3          | 8-lead, 0.300" Wide, Plastic Dual Inline Package (PDIP)                                                     |  |  |  |

| 8S1          | 8-lead, 0.150" Wide, Plastic Gull Wing Small Outline (JEDEC SOIC)                                           |  |  |  |

| 8A2          | 8-lead, 4.4 mm Body, Plastic Thin Shrink Small Outline Package (TSSOP)                                      |  |  |  |

| 8Y6          | 8-lead, 2.00 mm x 3.00 mm Body, 0.50 mm Pitch, Ultra Thin Mini-MAP, Dual No Lead Package (DFN), (MLP 2x3mm) |  |  |  |

| 8D3          | 8-lead, 1.8 mm x 2.2 mm Body, Ultra axLanda Grid Array (ULLGA)                                              |  |  |  |

| 8U3-1        | 8U3-1 8-ball, die Ball Grid Array Package (dBGA2)                                                           |  |  |  |

| Options      |                                                                                                             |  |  |  |

| -1.8         | Low Voltage (1.8 to 5.5V)                                                                                   |  |  |  |

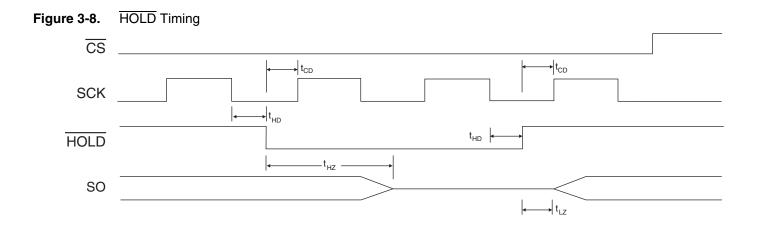

### 6. Packaging Information

### 8P3 – PDIP

### 8S1 – JEDEC SOIC

### 8A2 – TSSOP

### 8Y6 – Mini MAP

### 8D3 - ULLGA

## 7. Revision History

| Lit No. | Date   | Comments                                |

|---------|--------|-----------------------------------------|

| 5228B   | 7/2008 | Changed 'Endurance' parameter on page 6 |

| 5228A   | 9/2007 | Initial document release.               |

#### Headquarters

*Atmel Corporation* 2325 Orchard Parkway San Jose, CA 95131 USA Tel: 1(408) 441-0311 Fax: 1(408) 487-2600

#### International

Atmel Asia Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon Hong Kong Tel: (852) 2721-9778 Fax: (852) 2722-1369 Atmel Europe Le Krebs 8, Rue Jean-Pierre Timbaud BP 309 78054 Saint-Quentin-en-Yvelines Cedex France Tel: (33) 1-30-60-70-00 Fax: (33) 1-30-60-71-11

#### Atmel Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan Tel: (81) 3-3523-3551 Fax: (81) 3-3523-7581

#### **Product Contact**

Web Site www.atmel.com *Technical Support* s\_eeprom@atmel.com Sales Contact www.atmel.com/contacts

Literature Requests www.atmel.com/literature

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL'S TERMS AND CONDI-TIONS OF SALE LOCATED ON ATMEL'S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDEN-TAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel's products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.

© 2008 Atmel Corporation. All rights reserved. Atmel<sup>®</sup>, logo and combinations thereof, and others, are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.