# **Features**

- Designed in Accordance with CAN Specification 2.0B

- CAN 2.0B Protocol Functions

- · 4 Different Data Rates Using an Internal Programmable Prescaler

- 1 Mbit/s, 500 kbit/s, 250 kbit/s, 125 kbit/s

- 16 MHz Cycle Frequency

- · Power-down: Sleep Mode

- CAN Bus Line Arbitration

- All Required CAN Functions:

- Error Handling:

- Stuff Bit Generation

- CRC Generation

- Acknowledge Generation

- Remote Frame

- · 1 TX Buffer and 3 RX Buffer

- 3 Individual Acceptance Filtering

- Interrupt Outputs Can be Generated for the Following Events

- Telegram Sent Successfully

- Telegram Received Successfully

- Receive Buffer Overflow

- Bus Off Condition

- Error Passive Condition

- Technology: Atmel MG2RTP Radiation Hardened Sea of Gate 0.5 um

- Type: Semi-Custom Digital 5V

- Operating Frequency: 16 MHz (Test Frequency is 10MHz)

- Maximum Frequency: 18 MHz

- No Single Event Latch-up below a LET Threshold of 80 MeV/mg/cm<sup>2</sup>

- Tested up to a Total Dose of 300 Krads(si) According to MIL STD 883 Method 1019

- QML-Q and V with SMD 5962-03A06

- · Package: MLCC 44 pins

# **Description**

The AT7908E is a CAN controller stand-alone device for space application. Redundant structures and special techniques are implemented in order to make the device SEU tolerant. The AT7908E CAN core provides all CAN 2.0B protocol functions except the overload frame generation. It includes the acceptance filtering. The core incorporates error-handling capabilities, the stuff bit generation, CRC, multiple sample points and remote frame generation. The AT7908E provides a programmable MCU 8-bit general-purpose interface to connect receive and transmit buffer, control register and status register to CPU.

The AT7908E was designed by Aurelia Microelettronica S.p.A., Italy, and the chip is known as CASA (CAN ASIC for Space Application).

# CAN Controller for Space Application

# AT7908E

4268D-AERO-11/09

# **Signal Pins Description**

| Pin Number                        | Signal<br>Name | Туре      | Note | Description                                                           |

|-----------------------------------|----------------|-----------|------|-----------------------------------------------------------------------|

| 9                                 | Mode           | I - CMOS  |      | Interface operational mode                                            |

| 8                                 | Cs             | I - CMOS  | AH   | Chip select signal                                                    |

| 11                                | Wr             | I - CMOS  | AL   | Write signal                                                          |

| 13                                | Rd             | I - CMOS  | AL   | Read signal                                                           |

| 10                                | ALE            | I - CMOS  | AH   | Address latch enable                                                  |

| 23                                | Xtalin         | I - CMOS  |      | Input to internal oscillators or clock input from external oscillator |

| 22                                | Xtalout        | IO - CMOS |      | Output from internal oscillator                                       |

| 16                                | Reset          | I - CMOS  | AL   | reset signal                                                          |

| 5, 4, 3, 2, 44, 43,<br>42, 41     | addr<7:0>      | I - CMOS  |      | Input address(mode1) or output address(mode 0)                        |

| 38, 37, 36, 35, 33,<br>32, 31, 30 | Data<7:0>      | IO - CMOS |      | Address data bus                                                      |

| 25                                | Int            | O - CMOS  | AL   | interrupt request                                                     |

| 27                                | Can_tx         | O - CMOS  |      | tx signal                                                             |

| 19                                | Can_rx         | I - CMOS  |      | rx signal                                                             |

| 14                                | sena           | I - CMOS  | AH   | scan enable                                                           |

| 15                                | test           | I - CMOS  | AH   | input signal to increase testability                                  |

| 26                                | hatrig         | O - CMOS  | АН   | Output signal to trigger the message matching                         |

| 20                                | hasync         | O - CMOS  | AH   | Output synchronization signal                                         |

Note: Abbreviations: O = output, I = input, IO = bi-directional I/O, AL = Active Low, AH = Active High.

# **Oscillator**

Xtalin and Xtalout are IOs of an internal inverting oscillator. To use the internal oscillator, the quartz must be connected between Xtalin and Xtalout pins.

To drive the device with an external clock source, Xtalin must be driven by clock signal and Xtalout must be left unconnected. The maximum operating frequency of the oscillator, in open-loop mode(without crystal) with 6 pF load on Xtalout at worst condition (Process slow, temperature = 145°C, Power supply = 4.5V) is 60 MHz.

The IO level of Xtalin and Xtalout are CMOS levels.

The internal clock could be put on off condition with external pins SENA = logical value 1 and TEST = logical value 0.

# **Reset Specification**

The reset pin must be driven low for at least 3 clock cycles (190 ns at 16 MHz).

The reset signal must be driven low at power on of the AT7908E for at least 200 ns to avoid abnormal start condition of the AT7908E device.

\*NOTICE:

# **Electrical Characteristics**

# **Absolute Maximum Ratings**

Stresses above those listed may cause permanent damages to the device. Exposure to absolute maximum rating conditions for extended period may affect device reliability.

# **DC Characteristics**

Specified at VDD = +5V +/- 10%

| Symbol | Parameter                                | Min    | Тур   | Max      | Unit     | Conditions                         |

|--------|------------------------------------------|--------|-------|----------|----------|------------------------------------|

| VIL    | Input LOW voltage<br>CMOS input          | 0      |       | 0.3VDD   | V        |                                    |

| VIH    | Input HIGH voltage<br>CMOS input         | 0.7VDD |       | VDD      | V        |                                    |

| VOL    | Output LOW voltage<br>CMOS Output        |        |       | 0.4      | V        | IOL = +6 mA <sup>(1)</sup>         |

| VOH    | Output HIGH voltage<br>CMOS Output       | 3.9    |       |          | V        | IOH = -6 mA <sup>(1)</sup>         |

| IL     | Input Leakage current<br>NO Pull up/down |        | +/- 1 | +/- 5    | mA       |                                    |

| IOZ    | 3-State Output Leakage current           |        | +/-1  | +/-5     | mA       |                                    |

| IOS    | Output Short circuit current IOSN IOSP   |        |       | 24<br>18 | mA<br>mA | BOUT6<br>VOUT = 4.5V<br>VOUT = VSS |

Note: 1. According to the following buffers: BOUT6, BIOC6 @ VDD = 4.5V

# **AC Characteristics**

Tj = 125 °C, Process typical (all values in ns)

| Output Signals                             | Buffer Description                         | Load  | Tp<br>Xtalin to Output High | Tp<br>Xtalin to Output Low | Set Up<br>or Hold |

|--------------------------------------------|--------------------------------------------|-------|-----------------------------|----------------------------|-------------------|

| Can_tx<br>Int                              | BOUT6: Output buffer with 6                |       | 29                          |                            |                   |

| Hasync<br>Hatrig                           | mA drive                                   | 75 pF | 25<br>26                    | 19                         |                   |

| Set up Data<7:0>/Ale<br>Hold Data<7:0>/Ale | BIOC6: Bi-directional Buffer<br>CMOS input | 75 pF |                             |                            | 5<br>6            |

# **Power Consumption**

| Parameter                | Max        | Min | Note                   |

|--------------------------|------------|-----|------------------------|

| DC Curent<br>Dissipation | 50 mA @ 5V | -   | CLK frequency = 16 MHz |

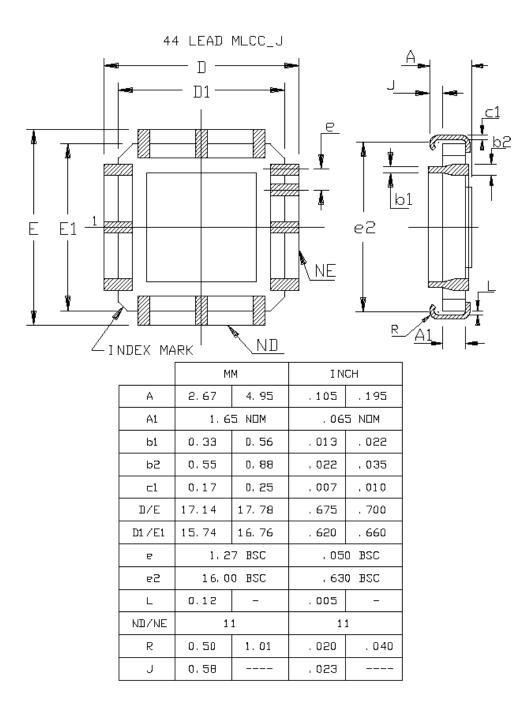

**Technology**

MG2RTP 0.5 mm 3 Metal Layers Sea of Gate.

Matrix: MG2 -044: 33K usable gates.

Package: MLCC\_J44: Ceramic Multi layer Package

**Application**

The core architecture has been implemented taking into account the typical constraints of a space application:

- No Single Event Latch-up below a LET Threshold of 80 MeV/mg/cm<sup>2</sup>

- Tested up to a Total Dose of 300 Krads(si) According to MIL STD 883 Method 1019

- Design using the SEU hardened flip flops

- Sleep mode for low power consumption

- Insertion of test structures (internal scan chain) to reach a fault coverage > 95% according to ESA specification

# Functional Description

The AT7908E is an integrated device that performs serial communications according to the CAN protocol. The CAN protocol uses a multi-master bus configuration to transfer data packets between nodes on a network. It supports both, standard and extended, message frame formats as CAN Specification 2.0B. It can transmit and receive with 29 identifier bits and it can filter the first eleven bits of the receiving message (the filtering function is performed only on eleven bits).

The AT7908E has one transmit buffer and three receiving buffers. The filtering function is individual for every RX message buffer. Every RX message buffer is formed by an identifier (29 bits long), by the data and by the status register that store the status of the receiver buffer. The identifier permits to filter the receiving message together with the global mask that implements the don't care condition. A message is accepted and stored in the RX message buffer only if the identifier of the incoming message (first eleven bits) matches the identifier in the RX message buffer. If the receiving message matches more than one identifier, the message is stored in the lowest numbered message buffer.

The AT7908E implements a global acceptance-masking feature for the message filtering.

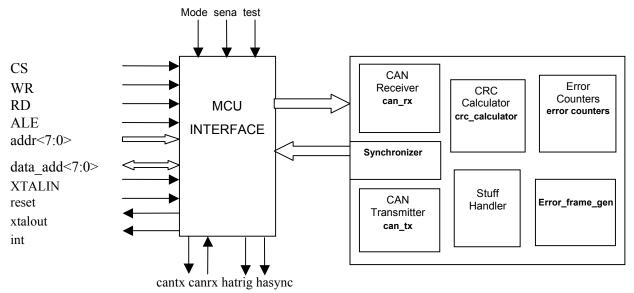

The AT7908E was developed to have a programmable general-purpose MCU interface. The MCU interface permits to program the internal register of the AT7908E and to read out the status of the controller and the received messages. The schematic representation of the AT7908E is shown in Fig. 1.

Figure 1. Block Schematic of AT7908E

To transmit a CAN message, the MCU must write in the interface internal registers the data and the configuration signals. The message bus (0 to 101) goes to **can\_tx** that generates the output signal to the transceiver **can\_tx** and the signals for **crc\_calculator** and for **error counters**.

The crc\_calculator block calculates the CRC on the received message and, if the CAN is in Transmission State, sends the CRC to can\_tx. If the CAN is receiving the message, the CRC is sent to can\_rx (CRC<0:14>) that checks if the calculated CRC matches the received CRC.

The **error\_counters** block is a counter that receives signals from **can\_tx** and **can\_rx** to calculate the error state of the CAN. If the number of errors is higher than 127, the AT7908E will be on the error passive state. If error counters is higher than 255, the AT7908E will be on the bus-off state.

The **synchronizer** block synchronizes the controller with the **can\_rx** incoming signal and generates the internal clock and reset signals for the other blocks of the controller.

The stuff handler block handles the stuff bit generation, compliant with the standard BOSCH 2.0B specification. **error\_frame\_gen** block generates the error frame on the bus.

In the next sections, the interface block, the internal registers and the operational modes of the AT7908E will be described.

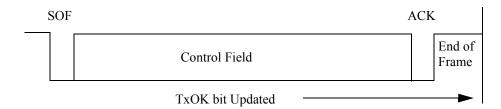

#### **Transmission of Message**

To transmit a message on the bus, the controller must program the configuration registers of the AT7908E (interrupt generator configuration, data rate, bit timing configuration, message length) and the transmit buffer. After this, the controller must write in the internal register the bit (Txreq=1) to start the transmission. At this point, the Transmit message buffer is sent to the bus line. At every moment the external MCU can readout the status of the controller (error condition, bus-off condition, transmission active or transmission OK).

### **Incoming Message**

The incoming message passes through the global mask and is checked with the identifier of the first receiver message buffer. If the message is accepted, the data will be stored in the first message buffer and the status of the receiver message objects will be updated with the information of the received message: length of message, extended or standard frame message, reception OK or overrun condition. The incoming message is stored in the message buffer at the end of the END of FRAME field (7 recessive bits).

If the incoming message is a remote frame request from another CAN node, the incoming remote request will not be stored on the RX message buffer.

#### Remote Frame

The AT7908E supports remote frame features. To send on the bus a remote frame request, the MCU must write two internal bits of SETUP register (TMRMR=1 and TXRM=0). The arbitration registers of the transmitter message buffer must have the identifier for the remote frame request. The start of the remote frame request will be performed when the transmission request is set by the MCU on the AT7908E. The AT7908E that receives a REMOTE FRAME request (RTR bit =recessive) that matches the identifier stored on own TX\_arbitration register (filtering functionality with don't care feature) send on the bus the TX message buffer as an answer to the remote frame request. To answer the remote frame request, the AT7908E must be pre-programmed with two bits of the internal register: TMRMR=0 and TXRM=1. The TX arbitration register must be initialized with the message identifier to which to answer and the transmitter data buffer must be loaded with the data to be sent as the answer to the remote frame request. The transmission request must be set as:

Answer to remote request if

for i = 28 down to 18

("MsgID(i)" XOR" TX\_arbitration (i) )AND "Accept. Mask(i)" = 0

# Filtering of Message

The filtering function is implemented with a global mask and the arbitration register of the receiver message buffers. The Global Mask permits to define the don't care bit on the filtering operation. The incoming message ID (msg\_ID(28:18) is checked (xor) with

the identifier stored in the message buffers (RXn\_ARB0, RXn\_ARB1). The result is masker able (logic **AND** operation) with global mask (FILTER\_AM\_0, FILTER\_AM\_1).

# Message Valid if

for i = 28 downto 18

("MsgID(i)" XOR" RXn\_arbitration (i) )AND "Accept. Mask(i)" = 0

If the incoming message is filtered out from the first message buffer, the arbitration field of the incoming message is checked with the identifier of the second message buffer, and if filtered out, with the identifier of the third message buffer. The global mask feature (used to accept a set of incoming messages) permits that the incoming message could match with all the three-messages buffers but the received message is stored on the lowest numbered message buffer.

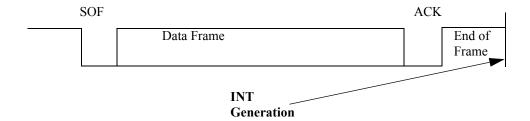

#### **Interrupt Generation**

The interrupt generation on the INT pin can be programmed by the external MCU writing the internal configuration register. Interrupt can be generated for:

- Either message correctly transmitted

- Or message correctly received ( data frame, not remote frame reception).

- Or overrun condition on the rx message buffer

- · Or bus-off condition

- Or error passive condition

In the SETUP register, it is possible to configure which kind of interrupt will be generated by the AT7908E device.

# Fault Confinement and Error Counters

The two internal error counters are readable from the external MCU to check the error status of the CAN controller. The error counter operates according to the Fault Confinement rules of the CAN Specification 2.0B, exception included. This means that if there is only one node of the AT7908E connected on the BUS and this node starts to transmit message, it meets the error passive condition but not the bus-off condition, because the transmitter error counter will no longer be incremented for acknowledge error when it is in error passive state.

### **Trigger Match Function**

The trigger match function is a feature implemented to generate the HATRIG signal (a pulse for a clock cycle) if the Identifier of the incoming message matches the TRIGGER\_MATCH register value. The incoming message identifier(msg\_id28 down to msg\_id18) is checked with the TM28 down to the TM18 bits of the TRIGGER\_MATCH registers. This function is independent from the filtration of message and from the interrupt generation. The HATRIG signal, together with the CAN node, regularly generating the appropriate frame, could be used to force the bus switching in a system with two physical bus used as nominal and redundant.

# **Detailed Pin Description**

|           | Input pin to select the operational mode of the interface:                                                                                                                                                                                                                                                                                                                                  |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | mode = 0 : 8 bits of the data bus multiplexed with the lowest 8 bits of the address(register mapped between 8000Hex and 804Chex)                                                                                                                                                                                                                                                            |

| MODE      | mode = 1 : 8 bits not multiplexed with the address data bus ( register mapped between 00 Hex and 4C Hex)                                                                                                                                                                                                                                                                                    |

| cs        | Chip select pin to write or read the internal register. A high level on this pin enables the CPU to access the AT7908E.                                                                                                                                                                                                                                                                     |

| WR        | Pin to write the internal register. A low level on this pin enables the writing of the AT7908E register (if CS signal is HIGH).                                                                                                                                                                                                                                                             |

| RD        | Pin to read the internal register. A low level on this pin enables the readout of the AT7908E register (if CS signal is HIGH).                                                                                                                                                                                                                                                              |

| ALE       | Address-latch-enable. Used in mode=0.                                                                                                                                                                                                                                                                                                                                                       |

| XTALIN    | Input pin for the clock. XTALIN, with XTALOUT, are the crystal connections for the internal oscillator.                                                                                                                                                                                                                                                                                     |

| XTALOUT   | Input output pin. This pin could be used as the input, together with XTALIN, for the internal oscillator or as the clock output to drive the CPU.                                                                                                                                                                                                                                           |

| RESET     | Reset signal for the AT7908E. To reset the AT7908E, this signal must be set low.                                                                                                                                                                                                                                                                                                            |

| DATA<7:0> | Bi-directional bus: Multiplexed data/address bus in the mode 0 or data bus in the mode1.                                                                                                                                                                                                                                                                                                    |

| ADDR<7:0> | Highest input address in the mode0 or lowest input address in the mode 1.                                                                                                                                                                                                                                                                                                                   |

| INT       | Output pin for the interrupt request to the MCU. This pin is active low (interrupt generation) and will be kept low until the MCU clears the interrupt request on AT7908E.                                                                                                                                                                                                                  |

| CAN_TX    | Serial output pin to the CAN transceiver (dominant='0', recessive='1')                                                                                                                                                                                                                                                                                                                      |

| CAN_RX    | Serial input from the CAN transceiver (dominant='0', recessive='1').                                                                                                                                                                                                                                                                                                                        |

| SENA      | Input signal to enable the scan-test (with test = 1) or to put the AT7908E on power down mode (with test signal = 0). To use the AT7908E in normal functional mode, this signal must be logical 0.                                                                                                                                                                                          |

| TEST      | Input signal to increase the testability. This pin will be used in the test modality. Test = 1 => test mode (used by the manufacturer that executes the test of the device. Test = 0 => functional mode ( if SENA =0) or power down mode ( if SENA =1).                                                                                                                                     |

| HATRIG    | Output signal that will be set high (duration of the pulse = 13 clock cycles) if the received message arbitration matches the TRIGGER_MATCH register (independently from the matching between the arbitration of the incoming message and the identifier of the message buffers). This pin could be used for the bus switching in a system with two physical buses (nominal and redundant). |

| HASYNC    | Output signal that could be used to advise that the node started to transmit a message or started to receive a message (duration of the pulse = 13 clock cycles).                                                                                                                                                                                                                           |

# Internal Register Description

| Register Name | Type R = read R/W = read/write | Address<br>Hex |          |          | R             | egister fund  | ction ( bit7 | bit0)   |        |        |

|---------------|--------------------------------|----------------|----------|----------|---------------|---------------|--------------|---------|--------|--------|

| SETUP_0       | R/W                            | 00             | BPR1     | BPR0     | Gensync<br>Tx | Gensync<br>Rx | Errint       | Overint | Rxint  | Txint  |

| SETUP_1       | R/W                            | 01             | Disabled | TXRM     | TXEM          | TMRMR         | TXDLC3       | TXDLC1  | TXDLC1 | TXDLC0 |

| SETUP_2       | R/W                            | 02             | PS2_3    | PS2_2    | PS2_1         | PS2_0         | PS1_3        | PS1_2   | PS1_1  | PS1_0  |

| SETUP_3       | R/W                            | 03             | RxClr    | Reset    | IntClr        | AbortTx       | Txreq        | RSJ2    | RSJ1   | RSJ0   |

| SETUP_RX      | R/W                            | 04             | reserved | reserved | reserved      | Reserved      | reserved     | Rxclr3  | Rxclr2 | Rxclr1 |

| CTATUC        |     | O.F. | CumaTv                                                             | CunaDy                                                   | Dybuf1           | DybufO        | TyOK             | Ty A etiye  | CrrDoos     | DueOff      |

|---------------|-----|------|--------------------------------------------------------------------|----------------------------------------------------------|------------------|---------------|------------------|-------------|-------------|-------------|

| STATUS        | R   | 05   | SyncTx                                                             | SyncRx                                                   | Rxbuf1           | Rxbuf0        | TxOK             | TxActive    | ErrPass     | BusOff      |

| STATUS_RX     | R   | 06   |                                                                    | reserved Rxovr3 Rxovr2 Rxovr1 reserved RXOK3 RXOK2 RXOK1 |                  |               |                  |             |             |             |

| FILTER_AM_0   | R/W | 07   |                                                                    | AM28:AM21                                                |                  |               |                  |             |             |             |

| FILTER_AM_1   | R/W | 08   |                                                                    |                                                          | & 3 reserved bit | <u> </u>      |                  |             |             |             |

| ERR_COUNT_TX  | R   | 09   |                                                                    | error counter                                            |                  |               |                  |             |             |             |

| ERR_COUNT_RX  | R   | 0A   | Receiver en                                                        |                                                          |                  |               |                  |             |             |             |

| TRIG_MATCH_0  | R/W | 0B   | Trigger mate                                                       | ch register TM                                           | l28TM21          |               |                  |             |             |             |

| TRIG_MATCH_1  | R/W | 0C   | Trigger mate                                                       | ch register TM                                           | l20, TM19, TM1   | 8 & 5 reserv  | ed bit           |             |             |             |

| TX_ARB_0      | R/W | 10   | Tx Arbitration                                                     | n register – T.                                          | XARB28:TXAR      | B21           |                  |             |             |             |

| TX_ARB_1      | R/W | 11   | Tx Arbitration                                                     | n register – T                                           | XARB20:TXAR      | B13           |                  |             |             |             |

| TX_ARB_2      | R/W | 12   | Tx Arbitration                                                     | n register – T                                           | XARB12:TXAR      | B5            |                  |             |             |             |

| TX_ARB_3      | R/W | 13   | Tx Arbitration                                                     | n register - T                                           | XARB4: TXARI     | 30 & 3 reserv | ved bit          |             |             |             |

| TX_MESSAGE_0  | R/W | 14   | Tx Data byte                                                       | e 0                                                      |                  |               |                  |             |             |             |

| TX_MESSAGE_1  | R/W | 15   | Tx Data byte                                                       | e 1                                                      |                  |               |                  |             |             |             |

| TX_MESSAGE_2  | R/W | 16   | Tx Data byte                                                       | e 2                                                      |                  |               |                  |             |             |             |

| TX_MESSAGE_3  | R/W | 17   | Tx Data byte                                                       | e 3                                                      |                  |               |                  |             |             |             |

| TX_MESSAGE_4  | R/W | 18   | Tx Data byte                                                       | e 4                                                      |                  |               |                  |             |             |             |

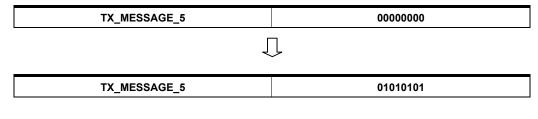

| TX_MESSAGE_5  | R/W | 19   | Tx Data byte                                                       | e 5                                                      |                  |               |                  |             |             |             |

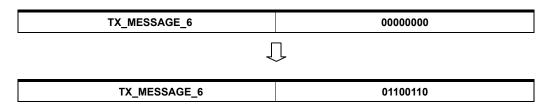

| TX_MESSAGE_6  | R/W | 1A   | Tx Data byte                                                       | e 6                                                      |                  |               |                  |             |             |             |

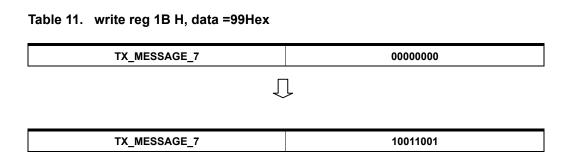

| TX_MESSAGE_7  | R/W | 1B   | Tx Data byte                                                       | e 7                                                      |                  |               |                  |             |             |             |

| RX1_ARB_0     | R/W | 20   | Rx1 buffer A                                                       | Arbitration regi                                         | ster – RX1ARB    | 28:RX1ARB     | 21               |             |             |             |

| RX1_ARB_1     | R/W | 21   | Rx1 buffer A                                                       | Arbitration regi                                         | ster – RX1ARB    | 20:RX1ARB     | 13               |             |             |             |

| RX1_ARB_2     | R   | 22   | Rx1 buffer A                                                       | Arbitration regi                                         | ster – RX1ARB    | 12:RX1ARB     | 5                |             |             |             |

| RX1_ARB_3     | R   | 23   | Rx1 buffer A                                                       | Arbitration regi                                         | ster- RX1ARB4    | :RX1ARB0 8    | & 3 reserved bit |             |             |             |

| RX1_MESSAGE_0 | R   | 24   | Rx1 buffer [                                                       | Data byte 0                                              |                  |               |                  |             |             |             |

| RX1_MESSAGE_1 | R   | 25   | Rx1 buffer [                                                       | Data byte 1                                              |                  |               |                  |             |             |             |

| RX1_MESSAGE_2 | R   | 26   | Rx1 buffer [                                                       | Data byte 2                                              |                  |               |                  |             |             |             |

| RX1_MESSAGE_3 | R   | 27   | Rx1 buffer [                                                       | Data byte 3                                              |                  |               |                  |             |             |             |

| RX1_MESSAGE_4 | R   | 28   | Rx1 buffer [                                                       | Data byte 4                                              |                  |               |                  |             |             |             |

| RX1_MESSAGE_5 | R   | 29   | Rx1 buffer [                                                       | Data byte 5                                              |                  |               |                  |             |             |             |

| RX1_MESSAGE_6 | R   | 2A   | Rx1 buffer [                                                       | Data byte 6                                              |                  |               |                  |             |             |             |

| RX1_MESSAGE_7 | R   | 2B   | Rx1 buffer [                                                       | Data byte 7                                              |                  |               |                  |             |             |             |

| RX1_STATUS    | R   | 2C   | RX1<br>reserved                                                    | RX1<br>reserved                                          | RX1<br>reserved  | RX1<br>Extfr  | Rx1<br>DLC3      | Rx1<br>DLC2 | Rx1<br>DLC1 | Rx1<br>DLC0 |

| RX2_ARB_0     | R/W | 30   | Rx2 buffer A                                                       | Arbitration regi                                         | ster – RX2ARB    | 28:RX2ARB     | 21               |             |             |             |

| RX2_ARB_1     | R/W | 31   | Rx2 buffer A                                                       | Arbitration regi                                         | ster – RX2ARB    | 20:RX2ARB     | 13               |             |             |             |

| RX2_ARB_2     | R   | 32   | Rx2 buffer Arbitration register – RX2ARB12:RX2ARB5                 |                                                          |                  |               |                  |             |             |             |

| RX2_ARB_3     | R   | 33   | Rx2 buffer Arbitration register- RX2ARB4: RX2ARB0 & 3 reserved bit |                                                          |                  |               |                  |             |             |             |

| RX2_MESSAGE_0 | R   | 34   | Rx2 buffer Data byte 0                                             |                                                          |                  |               |                  |             |             |             |

| RX2_MESSAGE_1 | R   | 35   | Rx2 buffer Data byte 1                                             |                                                          |                  |               |                  |             |             |             |

| RX2_MESSAGE_2 | R   | 36   | Rx2 buffer [                                                       | Data byte 2                                              |                  |               |                  |             |             |             |

| RX2_MESSAGE_3 | R   | 37   | Rx2 buffer D                                                       | Data byte 3                                              |                  |               |                  |             |             |             |

| RX2_MESSAGE_4 | R   | 38   | Rx2 buffer [                                                       | Data byte 4                                              |                  |               |                  |             |             |             |

| RX2_MESSAGE_5 | R   | 39 | Rx2 buffer [    | Rx2 buffer Data byte 5                                            |                   |              |             |             |             |             |

|---------------|-----|----|-----------------|-------------------------------------------------------------------|-------------------|--------------|-------------|-------------|-------------|-------------|

| RX2_MESSAGE_6 | R   | 3A | Rx2 buffer [    | Rx2 buffer Data byte 6                                            |                   |              |             |             |             |             |

| RX2_MESSAGE_7 | R   | 3B | Rx2 buffer [    | Data byte 7                                                       |                   |              |             |             |             |             |

| RX2_STATUS    | R   | 3C | RX2<br>reserved | RX3<br>reserved                                                   | RX3<br>Reserved   | RX2<br>Extfr | Rx2<br>DLC3 | Rx2<br>DLC2 | Rx2<br>DLC1 | Rx2<br>DLC0 |

| RX3_ARB_0     | R/W | 40 | Rx3 buffer A    | Arbitration regi                                                  | ster – RX3ARB28:  | RX3ARB       | 21          |             |             |             |

| RX3_ARB_1     | R/W | 41 | Rx3 buffer A    | Arbitration regi                                                  | ister – RX3ARB20: | RX3ARB       | 13          |             |             |             |

| RX3_ARB_2     | R   | 42 | Rx3 buffer A    | Arbitration regi                                                  | ister – RX3ARB12: | RX3ARB       | 5           |             |             |             |

| RX3_ARB_3     | R   | 43 | Rx3 buffer A    | Rx3 buffer Arbitration register- RX3ARB4:RX3ARB0 & 3 reserved bit |                   |              |             |             |             |             |

| RX3_MESSAGE_0 | R   | 44 | Rx3 buffer [    | Rx3 buffer Data byte 0                                            |                   |              |             |             |             |             |

| RX3_MESSAGE_1 | R   | 45 | Rx3 buffer [    | Data byte 1                                                       |                   |              |             |             |             |             |

| RX3_MESSAGE_2 | R   | 46 | Rx3 buffer [    | Data byte 2                                                       |                   |              |             |             |             |             |

| RX3_MESSAGE_3 | R   | 47 | Rx3 buffer [    | Data byte 3                                                       |                   |              |             |             |             |             |

| RX3_MESSAGE_4 | R   | 48 | Rx3 buffer [    | Data byte 4                                                       |                   |              |             |             |             |             |

| RX3_MESSAGE_5 | R   | 49 | Rx3 buffer [    | Data byte 5                                                       |                   |              |             |             |             |             |

| RX3_MESSAGE_6 | R   | 4A | Rx3 buffer [    | Rx3 buffer Data byte 6                                            |                   |              |             |             |             |             |

| RX3_MESSAGE_7 | R   | 4B | Rx3 buffer [    | Rx3 buffer Data byte 7                                            |                   |              |             |             |             |             |

| RX3_STATUS    | R   | 4C | RX3<br>reserved | RX3<br>reserved                                                   | RX3<br>reserved   | RX3<br>Extfr | Rx3<br>DLC3 | Rx3<br>DLC2 | Rx3<br>DLC1 | Rx3<br>DLC0 |

### **Setup Registers**

The five 8 bits SETUP registers are used to set specific CAN configurations. The 5 bits shown in grey on SETUP\_3 register and the 3 bits on SETUP\_RX register are not written directly inside the interface but are used to perform reset or other actions.

SETUP 0:

*Txint*: active high, the AT7908E generates the interrupt on the INT line after a successful transmission.

**Rxint:** active high, the AT7908E generates one interrupt on the INT line after a successful data frame reception.

**Overint:** active high, the AT7908E generates the interrupt on the INT line if the receiver buffer (number n) has not been cleared(with RxClr) before the next valid message for the same receiver buffer.

**Errint:** active high, the AT7908E generates the interrupt on the INT line if there's an error condition on the CAN Controller (bus-off or error-passive).

**GensyncRx**: the AT7908E generates a pulse on the hasync output signal when a receiving message is detected.

**GensyncTx**: the AT7908E generates a pulse on the hasync output signal when a sync pulse on the transmitting message is detected.

**BPR0-BPR1**: 2 bits to program the CAN clock pre-scaler (4 different system clocks of the CAN Core). In the next table, it is possible to see the different values of the system clock depending on the bits BPR0 and BPR1.

| BPR0 | BPR1 | System clock frequency |

|------|------|------------------------|

| 0    | 0    | f <sub>osc</sub>       |

| 0    | 1    | f <sub>osc</sub> /2    |

| 1    | 0    | f <sub>osc</sub> /4    |

| 1    | 1    | f <sub>osc</sub> /8    |

SETUP 1:

TXDLC<3:0>: length of the transmitted message.

**TMRMR:** Active High, establishes if the transmitted message is a remote frame (if TXRM=0).

**TXEM:** active high, it establishes if the transmitted message is an extended frame.

**TXRM**: Active high, it establishes if the controller answers to the remote frame request (if TMRMR=0).

**Disabled:** active high, by setting this bit, the CAN controller is disabled and disconnected from the bus. This condition could be used to set the other registers safely. The error counter values, when this bit is active, will be frozen at the last value.

SETUP\_2:

**PS1\_3** ... **PS1\_0**: these 4 bits are the phase segment length 1 (acceptable value 1:15). The default value of this register (value after reset) is 9 decimal.

**PS2\_3** ... **PS2\_0**: these 4 bits are the phase segment length 2 (acceptable value 1:8). The default value of this register (value after reset) is 5 decimal.

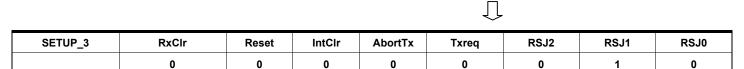

SETUP 3:

**RSJ\_2** ... **RSJ\_0**: 3 bits for the re-synchronization jump (correct value 1:4). The default value is 2.

**Txreq:** when this bit is set high, the AT7908E sends on the CAN bus the message contained in the TX buffer. This bit must be written from the MCU to start the transmission.

**AbortTx:** this bit must be set to inform the interface that the transmission request has to be aborted. The error counter values are not reset when this bit is set.

*IntCIr:* this bit resets the INT signal of the device and clears the SyncTx and SyncRx bits of the STATUS register.

**Reset:** active high, this signal must be set to reset the CAN controller. The error condition is cleared and also the counter values.

**RxCIr:** active high, this bit is set to clear all RXOKn and RXOVRn bits on the status register of the receiver message buffers (STATUS\_RX).

SETUP\_RX Register

**RxCIr3:** active high, this bit is set to clear the RXOK3 and RXOVR3 bits on the status register of the receiver message buffer (STATUS\_RX). This bit must be set after the read out operation of the received message otherwise, at the next reception on the same RX message buffer, an overrun condition is raised.

**RxCIr2:** active high, this bit is set to clear the RXOK2 and RXOVR2 bits on the status register of the receiver message buffers. This bit must be set after the read out operation of the received message otherwise, at the next reception on the same RX message buffer, an overrun condition is raised.

**RxCIr1:** active high, this bit is set to clear the RXOK1 and RXOVR1 bits on the status register of the receiver message buffers. This bit must be set after the read out operation of the received message otherwise, at the next reception on the same RX message buffer, an overrun condition is raised.

### **Status Registers**

STATUS\_0

BusOff: this bit indicates that the CAN controller has reached a bus off condition.

**ErrPass:** this bit indicates that the CAN controller has reached an error passive condition.

*TxActive:* this bit signals that there is an active transmission.

**TXOK:** this bit indicates that the transmission has been successfully terminated. This bit is reset automatically when the TXREQ bit on the SETUP\_3 register is set.

**Rxbuf1:Rxbuf0:** these bits indicate which receiver buffer received a message:

00: message filtered out

01: message received by RX1 buffer10: message received by RX2 buffer11: message received by RX3 buffer

**SyncRx:** this bit indicates that a pulse on the sync bit of the received message has been generated.

**SyncTx:** this bit indicates that a pulse on the sync bit of the transmitted message has been generated.

STATUS\_RX:

**RXOVR3:** This bit indicates an overrun condition (a new message received on the message buffer 3 with RXOK3 not cleared).

**RXOVR2:** This bit indicates an overrun condition (a new message received on the message buffer 2 with RXOK2 not cleared).

**RXOVR1:** This bit indicates an overrun condition (a new message received on the message buffer 1 with RXOK1 not cleared).

**RXOK3:** This bit indicates (active high) that the data frame message has been received correctly by the third message buffer.

**RXOK2:** This bit indicates (active high) that the data frame message has been received correctly by the second message buffer.

**RXOK1:** This bit indicates (active high) that the data frame message has been received correctly by the first message buffer.

#### Filter Registers

The 2 filter registers are used (together with the arbitration register of the receiver buffers or the arbitration registers of the transmit buffer to answer to the remote request) to filter out the messages that are not interesting for the receiving software. The filtering function is implemented only on 11 bits of the identifier (message\_id28 downto message\_id18) but works for both, extended and standard messages. The filtering function is:

Message Valid if:

for i = 28 downto 18

("MsgID(i)" XOR "RXnARB(i)")AND "AM(i)" = 0

The Message ID bits that are checked with the arbitration of the receiver buffer bits are the corresponding bits on the Acceptance Mask only if set to 1.

This filtering function is implemented for every message buffer.

#### TX Message Buffer

The AT7908E CAN controller has one transmitter buffer. The transmitter buffer is composed of 12 registers of 8 bits. The firsts 4 registers are used for the arbitration part that could be of 11 or 29 bits. If the message to transmit is a standard message, the AT7908E will send on the bus the identifier from ARB28 to ARB18. The other 8 registers contain the data byte of the message:

**TX\_ARB0**: bits 28 down to 21 of the arbitration of the transmitter buffer(TXARB28:TXARB21)

**TX\_ARB1**: bits 20 down to 13 of the arbitration of the transmitter buffer(TXARB20:TXARB13)

**TX\_ARB2**: bits 12 down to 5 of the arbitration of the transmitter buffer (TXARB12:TXARB5)

**TX\_ARB3**: bits 4 down to 0 of the arbitration of the transmitter buffer (TXARB4:TXARB0)

**TX\_Message\_0**: first 8 bits data of the transmitter buffer

**TX\_Message\_1**: second 8 bits data of the transmitter buffer

**TX\_Message\_2**: third 8 bits data of the transmitter buffer

**TX\_Message\_3**: fourth 8 bits data of the transmitter buffer

**TX\_Message\_4**: fifth 8 bits data of the transmitter buffer

**TX\_Message\_5**: sixth 8 bits data of the transmitter buffer

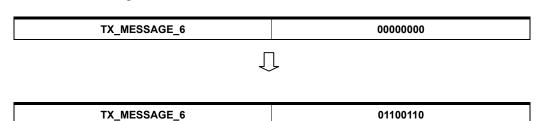

**TX Message 6**: seventh 8 bits data of the transmitter buffer

TX\_Message\_7: eighth 8 bits data of the transmitter buffer

### **RX Message Buffers**

The AT7908E CAN controller has three receiver message buffers. The incoming data frame message will be stored on the message object that matches the incoming ID ( see filtering functionality). If the incoming ID matches more than one ID of the message object, the message will be stored in the lowest numbered message object. The incoming remote request is not stored on the message buffer.

The structure of the message buffer is:

**RXn\_STATUS**: Status register of the message object n

RXn\_ARB0: bits 28 down to 21 of the arbitration of the message object n

**RXn\_ARB1**: bits 20 down to 13 of the arbitration of the message object n

**RXn** ARB2: bits 12 down to 5 of the arbitration of the message object n

**RXn\_ARB3**: bits 4 down to 0 of the arbitration of the message object n

RXn\_Message\_0: first 8 bits data of the message object n

RXn Message 1: second 8 bits data of the message object n

RXn Message 2: third 8 bits data of the message object n

RXn\_Message\_3: fourth 8 bits data of the message object n

RXn\_Message\_4: fifth 8 bits data of the message object n

**RXn Message 5**: sixth 8 bits data of the message object n

RXn\_Message\_6: seventh 8 bits data of the message object n

RXn\_Message\_7: eighth 8 bits data of the message object n

The following bit composes the **RXn\_STATUS** register of the message buffer:

RXn\_DLC3:RXn\_DLC0: length of the received message

(length = RXn\_DLC0 +2 x RXn\_DLC1 + 4 x RXn\_DLC2 + 8 x RXn\_DLC3)

**RXn\_extfr**: if this bit is high, the received message has an extended identifier.

#### **Error Counters Registers**

The AT7908E has two internal counters for the RX and TX errors. The values of these counters are stored into two registers that can be read from the MCU.

### **Trigger Match Registers**

The Trigger Match registers are implemented to generate a pulse on the HATRIG output signal when the received message arbitration match the Trigger Match registers (see the trigger match functionality).

# **Bit Timing**

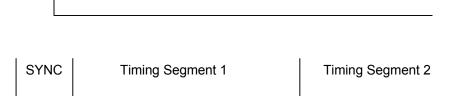

A bit period is composed of the following three segments:

Synchronization segment

Timing segment 1

Timing segment 2

The sampling point is at the end of time segment 1.

Input signal

Figure 2. Bit Time Segments

During the **Sync segment** (1 system clock cycle =  $t_{scl}$ ) the edge of the input signal is expected.

The **Timing segment 1** is programmable from 2 to 16  $t_{scl}$  (see register SETUP\_2: PS1\_3:PS1\_0: **TSEG1 =PS1+1**) and the end of this segment indicates the sample point.

The **Timing segment 2** is programmable from 1 to 8  $t_{scl}$  (register SETUP\_2: PS2\_3:PS2\_0) and this period is used to have extra time for the internal processing after the sample point.

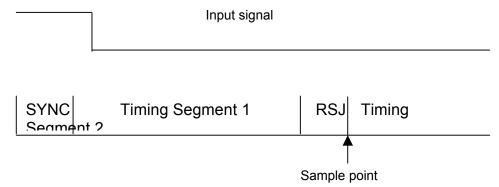

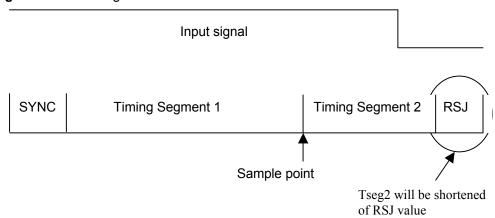

The **resynchronization Jump Width** is used to compensate phase shifts between the oscillator frequency of the different CAN nodes on the network. This value is programmable (see register SETUP\_3: RSJ\_2:RSJ\_0) from 1 to 4  $t_{scl}$  and the value indicates the number of system clock pulses by which the bit period must be shortened or lengthened for resynchronization. If the falling edge of the incoming signal is on the TIMING segment 1, then the Bit period is lengthened (the sample point will be at TSEG1 +RSJ). If the falling edge of the incoming signal is on the Timing segment 2, then the bit period

will be shortened (TSEG2 is shortened of RSJ value). The resynchronization mechanism is shown in fig. 3 and fig. 4.

Figure 3. Lengthening a Bit Period

Figure 4. Shortening a Bit Period

The Bit rate of the message on the bus will be:

f<sub>osc</sub>/(BPR(baud rate prescaler)x(TSEG1 +TSEG2+1)) =

= f<sub>osc</sub> /(BPR(baud rate prescaler) x( PS1 +PS2 +2))

The TSEG1 and TSEG2 lengths must be programmed to respect these conditions:

TSEG1 3 TSEG2 => PS1 +1 3 PS2

TSEG2 3 RSJ => PS2 3 RSJ

# Interface Block Description

The AT7908E provides a programmable (with external pin) MCU interface. Two modes can be selected. The first operational mode is an interface with 8-bit multiplexed address data bus (mode = 0) and an internal register addressable with 16-bit of address. In this operational mode, the AT7908E registers are mapped between 8000Hex and 804CHex.

The second operational mode (mode =1) is implemented with 8 bit not multiplexed address and data buses. In this mode the internal registers are accessible with 8-bit and are mapped between 00Hex and 4C Hex.

The pins for the interface block are:

| Mode       | Selection of the interface modality. This pin must be <b>0</b> to use 8 bits multiplexed data address (lowest) to map the AT7908E on the highest address space (8000Hex to 804C Hex). If MODE = 1, the data and addresses are not multiplexed and the registers are mapped on the lowest address space. |  |  |  |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Data <7:0> | bi-directional 8-bit address (low address in mode 0) data bus                                                                                                                                                                                                                                           |  |  |  |

| ALE        | Input Address Latch Enable used for mode 0.                                                                                                                                                                                                                                                             |  |  |  |

| cs         | Input Chip select to enable the internal registers access (active high).                                                                                                                                                                                                                                |  |  |  |

| WR         | Input Write signal to write the internal registers (active low).                                                                                                                                                                                                                                        |  |  |  |

| RD         | Input Read signal to readout the internal registers (active low).                                                                                                                                                                                                                                       |  |  |  |

| Addr <7:0> | Input highest address in <b>mode 0</b> (used with low address to map the AT7908E register between 8000Hex and 804Chex address space) or input lowest address in <b>mode 1</b>                                                                                                                           |  |  |  |

# **Operational Mode 0**

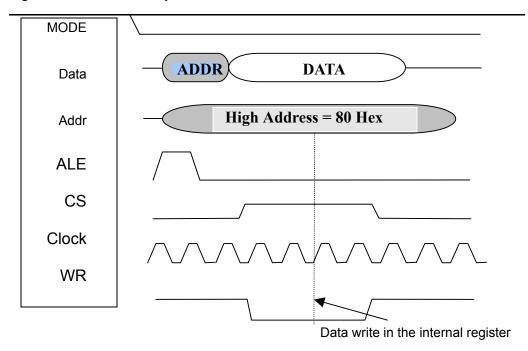

This operational mode is selected with **MODE** pin = 0.

The bus Data\_addr <7:0> must be connected to the data/address bus of the MCU. The ALE signal is used to latch the address. This latched address will be the address of the AT7908E internal registers. The bus addr (7:0) will contain the highest address generated by the MCU. The internal AT7908E registers will be accessed only if the 16-bit address generated by the MCU is between 8000 Hex and 804C Hex (the internal Chip Select will be generated). Moreover, to write in the register or to read from the register, the micro-controller must generate the CS (active high), WR, RD and ALE signals and must drive the Data\_addr and addr buses. The signal WR must be low for, at least, 3 clock cycles. The data is latched at the rising edge of the clock when CS = 1, WR = 0 and RD = 1.

A write cycle is reported in Fig. 5.

Figure 5. Mode 0 Write Cycle

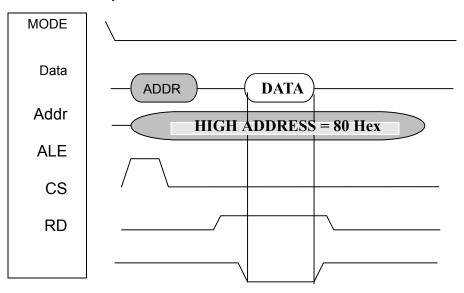

In Fig. 6 are represented the signals to readout the internal register of AT7908E in mode 0

Figure 6. Mode 0 Read Cycle

In mode 0, the internal registers of the AT7908E are mapped between 8000 Hex and 804C Hex and the lowest 8-bit address are multiplexed with the data.

# **Operational Mode 1**

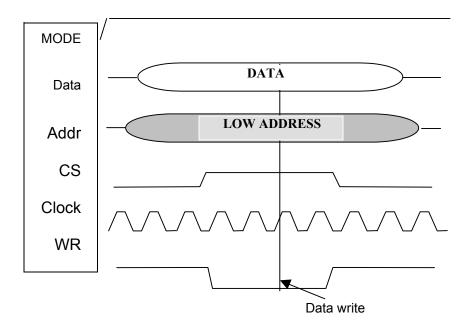

This operational mode is selected with mode pin = 1.

This interface operational mode is used to write the AT7908E registers and to readout from the AT7908E with two different 8-bit data and address buses. The ALE input pin is not used and the internal registers are mapped between 00Hex and 4C Hex. The Addr bus will be used as the 8 bits address for the internal registers. To write data on the internal registers, the MCU must control the CS, WR and RD signals of the AT7908E and must drive the addr and data buses. The signal WR must be low for, at least, 3 clock cycles. The data is latched at the rising edge of the clock when CS = 1, WR = 0 and RD = 1. The fig. 7 shows the write cycle in the operational mode 1.

Figure 7. Mode 1 Write Cycle

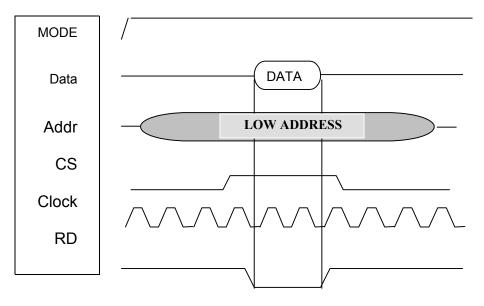

Fig. 8 shows a read cycle. To readout the data from the AT7908E internal registers, the MCU must drive CS=1, RD=0, WR=1.

Figure 8. Mode 1 Read Cycle

# **Timing**

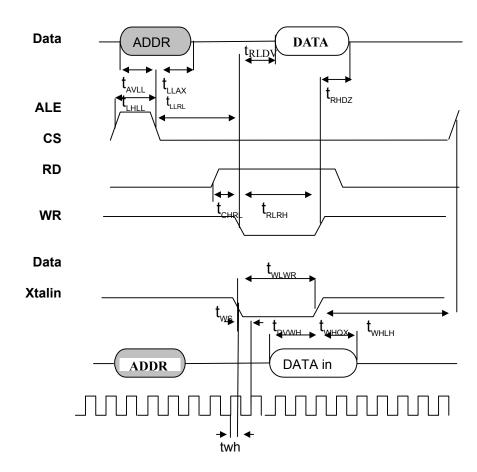

In this paragraph are provided the AC specification for the AT7908E interface signals in both operational modes.

AC Specification for 8 bit Multiplexed Mode (mode =0) Conditions: VCC = 5V  $\pm 10\%$ , VSS = 0V, Ta = -55°C to +125 °C, Cl = 80 pF , Tclk = 100 ns

| Symbol                 | Parameter                     | Min    | Max   | Note           |

|------------------------|-------------------------------|--------|-------|----------------|

| t <sub>AVLL</sub>      | Address valid to ALE low      | 4 ns   |       | Mode 0         |

| t <sub>LLAX</sub>      | Address Hold after ALE low    | 4 ns   |       | Mode 0         |

| t <sub>LHLL (*)</sub>  | ALE HIGH Time                 | Tclk   |       | Mode 0         |

| t <sub>LLRL (*)</sub>  | ALE low to RD low             | 2 Tclk |       | Mode 0         |

| t <sub>CHRL</sub>      | CS high to RD low             | 100 ns |       | Mode 0         |

| t <sub>DVWH] (*)</sub> | Input Data valid to WR High   | 3 Tclk |       | Mode 0, mode 1 |

| t <sub>WHQX (*)</sub>  | Input data hold after WR high | 10 ns  |       | Mode 0, mode 1 |

| t <sub>WLWH (*)</sub>  | WR pulse width                | 3 Tclk |       | Mode 0, mode 1 |

| t <sub>WHLH (*)</sub>  | WR high to next ALE high      | Tclk   |       |                |

| t <sub>ws</sub>        | WR setup time before clock    | -3 ns  |       | Mode 0, mode 1 |

| t <sub>WH (*)</sub>    | WR hold time after clock      | 7 ns   |       | Mode 0, mode 1 |

| t <sub>RLRH (*)</sub>  | RD pulse width                | 3 Tclk |       | Mode 0, mode 1 |

| t <sub>RLDV (*)</sub>  | RD low to data valid          | 6 ns   | 82 ns | Mode 0, mode 1 |

| t <sub>RHDZ (*)</sub>  | Data float after RD High      | 4 ns   | 20 ns | Mode 0, mode 1 |

Note: 1. Guaranteed, not tested.

Figure 9. Timing information for interface signals

# Interface Internal Structure

This paragraph is intended to explain the implementation of the interface internal structure.

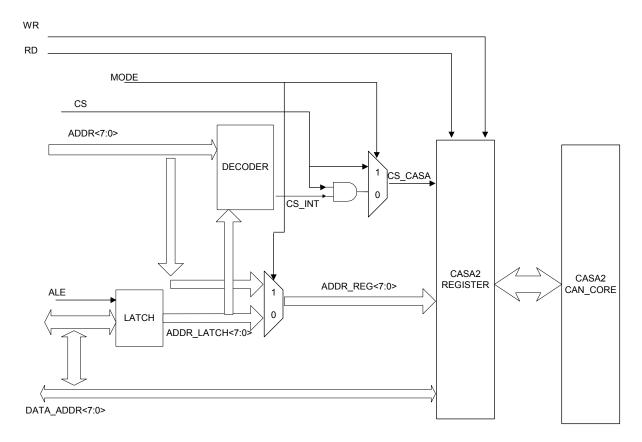

In the Figure 10, one can see the realization of the two operational modes and the access to the AT7908E internal registers.

Figure 10. Interface Block Scheme

The MCU 80C32 generates **DATA<7:0>**, **ADDR<7:0>** (highest 8-bit address for the 16-bit external data access), **and ALE to latch** the **lowest address**, **WR**, **CS** and **RD** signals.

The external data bus is connected to the internal latch block of the AT7908E. The **ALE** signal latches and extracts the **ADDR\_LATCH** (lowest 8-bit address). The **ADDR\_LATCH** is used to address the internal registers in mode 0 and to generate, with **ADDR<7:0>** (highest 8-bit address), the internal chip select signal (**CS\_INT**). In mode 0, the access to the internal registers is selected by CS\_INT and CS; in mode 1, the access is selected by **CS**. In mode 1, moreover, the address of the internal register is **ADDR<7:0>**. The two different operational modes are established by the **mode** pin that is the selector for the two multiplexers in Figure 5. In Figure 5 are reported, in addition, the other two blocks of the AT7908E device: the AT7908E registers and the AT7908E CAN\_CORE.

# **Address Table**

In the next table, one can see how the MCU can address the RAM or the internal register of the AT7908E in the operational mode 0.

| ADDRESS Generated by the MCU (15 down to 0) | Device                                                                    |

|---------------------------------------------|---------------------------------------------------------------------------|

| 0000 – 7FFF Hex                             | 32 Kword of External RAM                                                  |

| 8000 - 800C Hex                             | AT7908E internal register 00 – 0C Hex (Configuration and status register) |

| 8010 - 801B Hex                             | AT7908E internal register 10 – 1B Hex<br>Transmitter message buffer       |

| 8020 – 802C Hex                             | AT7908E internal register 20 – 2C Hex First receiver message object       |

| 8030 – 803C Hex                             | AT7908E internal register 30 – 3C Hex<br>Second receiver message object   |

| 8040 – 804C Hex                             | AT7908E internal register 40 – 4C Hex<br>Third receiver message object    |

# **Optional Features**

**Internal Clock Frequency**

The actual internal system clock can be the external clock divided by 1, 2, 4, or 8. If the bit time length is (default configuration) 16 system clock pulses (see PS1, PS2 programmable bit timing registers), it is possible to have four different data rates by the prescaler programming.

AT7908E Operational Mode

The AT7908E device could be put on three different operational modes:

- Functional Mode

- Test mode

- Power down mode

Functional Mode

This mode is the normal operational mode for the AT7908E device. The two input pins **test** and **sena** must be put on logical value 0.

**Test Mode**

This mode is used by the chip manufacturer to test the AT7908E. The input pin **test** must be logical value 1 and **sena** input pin could be logical values 0 or 1 according to the execution of the scan chain test or not.

**Power Down Mode**

This mode could be used to put the AT7908E device on the sleep mode (internal clock is off). To put the AT7908E in this mode, the **test** input pin must be 0 and **sena** input pin must be 1.

# **Application Notes**

# Registers Value After Reset

In the next table are reported the registers value after reset of the AT7908E device:

| Register Name | Address<br>Hex | Reset Val | ue ( bit7 b | it0)      |           |          |          |         |        |  |

|---------------|----------------|-----------|-------------|-----------|-----------|----------|----------|---------|--------|--|

|               |                | BPR1      | BPR0        | GensyncTx | GensyncRx | Errint   | Overint  | Rxint   | Txint  |  |

| SETUP_0       | 00             | 0         | 0           | 0         | 0         | 0        | 0        | 0       | 0      |  |

| 0FTUD 4       |                | Disabled  | TXRM        | TXEM      | TMRMR     | TXDLC3   | TXDLC1   | TXDLC1  | TXDLC0 |  |

| SETUP_1       | 01             | 1         | 0           | 0         | 0         | 0        | 0        | 0       | 0      |  |

| CETUD 2       | 00             | PS2_3     | PS2_2       | PS2_1     | PS2_0     | PS1_3    | PS1_2    | PS1_1   | PS1_0  |  |

| SETUP_2       | 02             | 0         | 1           | 0         | 1         | 1        | 0        | 0       | 1      |  |

| SETUP_3       | 03             | RxClr     | Reset       | IntClr    | AbortTx   | Txreq    | RSJ2     | RSJ1    | RSJ0   |  |

| 3E1UF_3       | 03             | 0         | 0           | 0         | 0         | 0        | 0        | 1       | 0      |  |

| SETUP_RX      | 04             | Reserved  | Reserved    | Reserved  | Reserved  | Reserved | Rxclr3   | Rxclr2  | Rxclr1 |  |

| SETOF_KX      | 04             | Х         | Х           | Х         | Х         | Х        | 0        | 0       | 0      |  |

| STATUS        | 05             | SyncTx    | SyncRx      | Rxbuf1    | Rxbuf0    | TxOK     | TxActive | ErrPass | BusOff |  |

| OIAIOO        | 00             | 0         | 0           | 0         | 0         | 0        | 0        | 0       | 0      |  |

| STATUS_RX     | 06             | reserved  | Rxovr3      | Rxovr2    | Rxovr1    | Reserved | RXOK3    | RXOK2   | RXOK1  |  |

| 01A100_100    | 00             | 0         | 0           | 0         | 0         | 0        | 0        | 0       | 0      |  |

| FILTER_AM_0   | 07             | 00000000  |             |           |           |          |          |         |        |  |

| FILTER_AM_1   | 08             | 00000000  | 00000000    |           |           |          |          |         |        |  |

| ERR_COUNT_TX  | 09             | 00000000  | 0000000     |           |           |          |          |         |        |  |

| ERR_COUNT_RX  | 0A             | 00000000  | 00000000    |           |           |          |          |         |        |  |

| TRIG_MATCH_0  | 0B             | 00000000  | 0000000     |           |           |          |          |         |        |  |

| TRIG_MATCH_1  | 0C             | 00000000  |             |           |           |          |          |         |        |  |

| TX_ARB_0      | 10             | 00000000  |             |           |           |          |          |         |        |  |

| TX_ARB_1      | 11             | 00000000  |             |           |           |          |          |         |        |  |

| TX_ARB_2      | 12             | 00000000  |             |           |           |          |          |         |        |  |

| TX_ARB_3      | 13             | 00000000  |             |           |           |          |          |         |        |  |

| TX_MESSAGE_0  | 14             | 00000000  |             |           |           |          |          |         |        |  |

| TX_MESSAGE_1  | 15             | 00000000  |             |           |           |          |          |         |        |  |

| TX_MESSAGE_2  | 16             | 00000000  |             |           |           |          |          |         |        |  |

| TX_MESSAGE_3  | 17             | 00000000  |             |           |           |          |          |         |        |  |

| TX_MESSAGE_4  | 18             | 00000000  |             |           |           |          |          |         |        |  |

| TX_MESSAGE_5  | 19             | 00000000  |             |           |           |          |          |         |        |  |

| TX_MESSAGE_6  | 1A             | 00000000  |             |           |           |          |          |         |        |  |

| TX_MESSAGE_7  | 1B             | 0000000   |             |           |           |          |          |         |        |  |

| RX1_ARB_0     | 20             | 00000000  |             |           |           |          |          |         |        |  |

| RX1_ARB_1     | 21             | 00000000  |             |           |           |          |          |         |        |  |

| RX1_ARB_2     | 22             | 0000000   |             |           |           |          |          |         |        |  |

| Register Name | Address<br>Hex | Reset Valu | ue ( bit7 bi | it0)     |               |          |          |          |          |  |

|---------------|----------------|------------|--------------|----------|---------------|----------|----------|----------|----------|--|

| RX1_ARB_3     | 23             | 00000000   | 0000000      |          |               |          |          |          |          |  |

| RX1_MESSAGE_0 | 24             | 00000000   | 0000000      |          |               |          |          |          |          |  |

| RX1_MESSAGE_1 | 25             | 00000000   |              |          |               |          |          |          |          |  |

| RX1_MESSAGE_2 | 26             | 00000000   |              |          |               |          |          |          |          |  |

| RX1_MESSAGE_3 | 27             | 00000000   |              |          |               |          |          |          |          |  |

| RX1_MESSAGE_4 | 28             | 00000000   |              |          |               |          |          |          |          |  |

| RX1_MESSAGE_5 | 29             | 00000000   |              |          |               |          |          |          |          |  |

| RX1_MESSAGE_6 | 2A             | 00000000   |              |          |               |          |          |          |          |  |

| RX1_MESSAGE_7 | 2B             | 00000000   |              |          |               |          |          |          |          |  |

| RX1_STATUS    | 2C             | reserved   | reserved     | Reserved | RX1_e<br>xtfr | Rx1_DLC3 | Rx1_DLC2 | Rx1_DLC1 | Rx1_DLC0 |  |

|               |                | Х          | Х            | Х        | 0             | 0        | 0        | 0        | 0        |  |

| RX2_ARB_0     | 30             | 00000000   |              |          |               |          |          |          |          |  |

| RX2_ARB_1     | 31             | 00000000   | 0000000      |          |               |          |          |          |          |  |

| RX2_ARB_2     | 32             | 00000000   | 0000000      |          |               |          |          |          |          |  |

| RX2_ARB_3     | 33             | 00000000   | 00000000     |          |               |          |          |          |          |  |

| RX2_MESSAGE_0 | 34             | 00000000   |              |          |               |          |          |          |          |  |

| RX2_MESSAGE_1 | 35             | 00000000   |              |          |               |          |          |          |          |  |

| RX2_MESSAGE_2 | 36             | 00000000   |              |          |               |          |          |          |          |  |

| RX2_MESSAGE_3 | 37             | 00000000   |              |          |               |          |          |          |          |  |

| RX2_MESSAGE_4 | 38             | 00000000   |              |          |               |          |          |          |          |  |

| RX2_MESSAGE_5 | 39             | 00000000   |              |          |               |          |          |          |          |  |

| RX2_MESSAGE_6 | 3A             | 00000000   |              |          |               |          |          |          |          |  |

| RX2_MESSAGE_7 | 3B             | 00000000   | 1            | 1        |               | I        | T        | 1        |          |  |

| RX2_STATUS    | 3C             | reserved   | reserved     | Reserved | RX2_e<br>xtfr | Rx2_DLC3 | Rx2_DLC2 | Rx2_DLC1 | Rx2_DLC0 |  |

|               |                | X          | Х            | X        | 0             | 0        | 0        | 0        | 0        |  |

| RX3_ARB_0     | 40             | 00000000   |              |          |               |          |          |          |          |  |

| RX3_ARB_1     | 41             | 00000000   |              |          |               |          |          |          |          |  |

| RX3_ARB_2     | 42             | 00000000   |              |          |               |          |          |          |          |  |

| RX3_ARB_3     | 43             | 00000000   |              |          |               |          |          |          |          |  |

| RX3_MESSAGE_0 | 44             |            | 0000000      |          |               |          |          |          |          |  |

| RX3_MESSAGE_1 | 45             |            | 0000000      |          |               |          |          |          |          |  |

| RX3_MESSAGE_2 | 46             |            | 0000000      |          |               |          |          |          |          |  |

| RX3_MESSAGE_3 | 47             |            | 0000000      |          |               |          |          |          |          |  |

| RX3_MESSAGE_4 | 48             | 00000000   |              |          |               |          |          |          |          |  |

| RX3_MESSAGE_5 | 49             | 00000000   |              |          |               |          |          |          |          |  |

| RX3_MESSAGE_6 | 4A             | 00000000   | 0000000      |          |               |          |          |          |          |  |

| Register Name | Address<br>Hex | Reset Value ( bit7 bit0) |          |          |               |          |          |          |          |

|---------------|----------------|--------------------------|----------|----------|---------------|----------|----------|----------|----------|

| RX3_MESSAGE_7 | 4B             | 0000000                  |          |          |               |          |          |          |          |

| RX3 STATUS    | 4C             | reserved                 | reserved | Reserved | RX3_e<br>xtfr | Rx3_DLC3 | Rx3_DLC2 | Rx3_DLC1 | Rx3_DLC0 |

|               |                | Х                        | Х        | Х        | 0             | 0        | 0        | 0        | 0        |

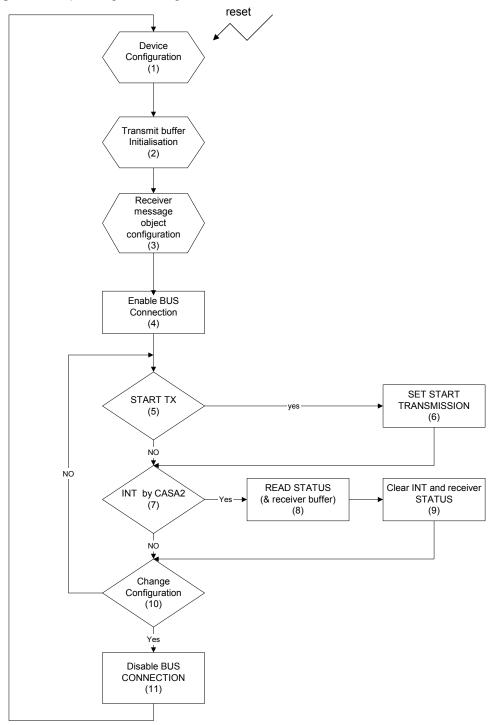

# **Configuration Flow**

The following flow diagram explains the action that the MCU must perform to program the AT7908E CAN controller to send or to receive CAN message.

Figure 11. Operating Flow Diagram

In the examples of the followings paragraph the different operations are referred to the number reported on flow diagram. After the commands, the old register and the new register values are reported.

# Initialization and Transmission of the Data Frame with the INT Generation and Behavior of the MCU After the Interrupt is Received

Configuration of all the setup registers after the RESET signal.

# Operation 1

# Table 1. write reg 00 H, data =01Hex

(SETUP\_0 register) system clock = external clock, enable transmission completed interrupt

|         | BPR1 | BPR0 | Gens<br>yncTx | Gens<br>yncRx | Errint | Overint | Rxint | Txint |

|---------|------|------|---------------|---------------|--------|---------|-------|-------|

| SETUP_0 | 0    | 0    | 0             | 0             | 0      | 0       | 0     | 0     |

|         | BPR1 | BPR0 | Gens<br>yncTx | Gens<br>yncRx | Errint | Overint | Rxint | Txint |

|---------|------|------|---------------|---------------|--------|---------|-------|-------|

| SETUP_0 | 0    | 0    | 0             | 0             | 0      | 0       | 0     | 1     |

# Table 2. write reg 02 H, data =69Hex

(SETUP\_2 register) Time segment 2 = 6 pulse of system clock; Time segment 1 = 8 pulse of system clock.

| SETUP_2 | PS2_3 | PS2_2 | PS2_1 | PS2_0 | PS1_3 | PS1_2 | PS1_1 | PS1_0 |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|

|         | 0     | 1     | 0     | 1     | 1     | 0     | 0     | 1     |

| SETUP_2 | PS2_3 | PS2_2 | PS2_1 | PS2_0 | PS1_3 | PS1_2 | PS1_1 | PS1_0 |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|

|         | 0     | 1     | 1     | 0     | 1     | 0     | 0     | 1     |

### SETUP\_3 register will be not written ( default configuration)

### **Operation 2**

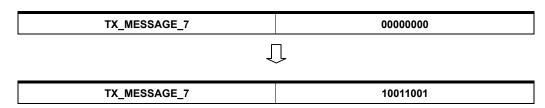

After SETUP registers is necessary to configure TX message object: