# Fractional-N Clock Multiplier with Internal LCO

#### **Features**

- ♦ Clock Multiplier / Jitter Reduction

- Generates a Low Jitter 6 75 MHz Clock from a Jittery or Intermittent 50 Hz to 30 MHz Clock Source

- ♦ Internal LC Oscillator for Timing Reference

- ♦ Highly Accurate PLL Multiplication Factor

- Maximum Error less than 1 PPM in High-Resolution Mode

- ♦ I<sup>2</sup>C<sup>®</sup> / SPI<sup>TM</sup> Control Port

- ♦ Configurable Auxiliary Output

- Minimal Board Space Required

- No External Analog Loop-filter Components

#### **General Description**

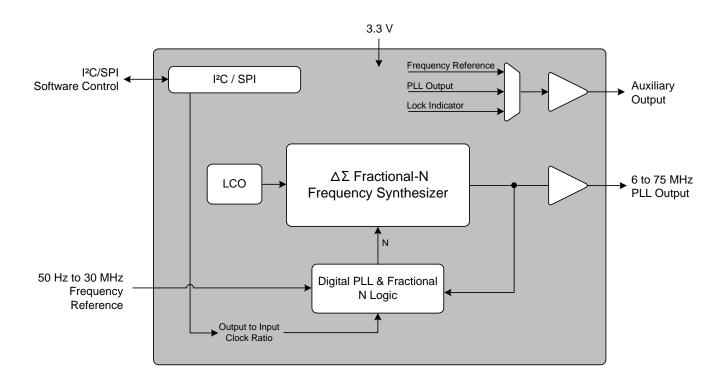

The CS2300-CP is an extremely versatile system clocking device that utilizes a programmable phase lock loop. The CS2300-CP is based on a hybrid analog-digital PLL architecture comprised of a unique combination of a Delta-Sigma Fractional-N Frequency Synthesizer and a Digital PLL. This architecture allows for generation of a low-jitter clock relative to an external noisy synchronization clock at frequencies as low as 50 Hz. The CS2300-CP supports both I<sup>2</sup>C and SPI for full software control.

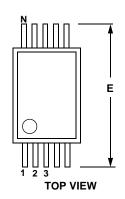

The CS2300-CP is available in a 10-pin MSOP package in Commercial (-10°C to +70°C) grade. Customer development kits are also available for device evaluation. Please see "Ordering Information" on page 31 for complete details.

Preliminary Product Information

This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

# TABLE OF CONTENTS

| 1. PIN DESCRIPTION                                              |    |

|-----------------------------------------------------------------|----|

| 2. TYPICAL CONNECTION DIAGRAM                                   |    |

| 3. CHARACTERISTICS AND SPECIFICATIONS                           |    |

| RECOMMENDED OPERATING CONDITIONS                                |    |

| ABSOLUTE MAXIMUM RATINGS                                        |    |

| DC ELECTRICAL CHARACTERISTICS                                   |    |

| AC ELECTRICAL CHARACTERISTICS                                   |    |

| CONTROL PORT SWITCHING CHARACTERISTICS- I <sup>2</sup> C FORMAT |    |

| CONTROL PORT SWITCHING CHARACTERISTICS - SPI FORMAT             |    |

| 4. ARCHITECTURE OVERVIEW                                        | 10 |

| 4.1 Delta-Sigma Fractional-N Frequency Synthesizer              |    |

| 4.2 Hybrid Analog-Digital Phase Locked Loop                     |    |

| 5. APPLICATIONS                                                 |    |

| 5.1 Timing Reference Clock                                      |    |

| 5.2 Frequency Reference Clock Input, CLK_IN                     |    |

| 5.2.1 CLK_IN Frequency Detector                                 |    |

| 5.2.2 CLK_IN Skipping Mode                                      |    |

| 5.2.3 Adjusting the Minimum Loop Bandwidth for CLK_IN           |    |

| 5.3 Output to Input Frequency Ratio Configuration               |    |

| 5.3.1 User Defined Ratio (RUD)                                  |    |

| 5.3.2 Manual Ratio Modifier (R-Mod)                             |    |

| 5.3.3 Automatic Ratio Modifier (Auto R-Mod)                     |    |

| 5.3.4 Effective Ratio (REFF)                                    |    |

| 5.3.5 Ratio Configuration Summary                               |    |

| 5.4 PLL Clock Output                                            |    |

| 5.5 Auxiliary Output                                            |    |

| 5.6 Clock Output Stability Considerations                       |    |

| 5.6.1 Output Switching                                          |    |

| 5.6.2 PLL Unlock Conditions                                     |    |

| 6. SPI / I <sup>2</sup> C CONTROL PORT                          |    |

| 6.1 SPI Control                                                 |    |

| 6.2 I <sup>2</sup> C Control                                    |    |

| 6.3 Memory Address Pointer                                      |    |

| 6.3.1 Map Auto Increment                                        |    |

| 7. REGISTER QUICK REFERENCE                                     |    |

| 8. REGISTER DESCRIPTIONS                                        |    |

| 8.1 Device I.D. and Revision (Address 01h)                      |    |

| 8.1.1 Device Identification (Device[4:0]) - Read Only           |    |

| 8.1.2 Device Revision (Revision[2:0]) - Read Only               |    |

| 8.2 Device Control (Address 02h)                                |    |

| 8.2.1 Unlock Indicator (Unlock) - Read Only                     |    |

| 8.2.2 PLL Input Sample Rate Indicator (FsDet[1:0]) - Read Only  |    |

| 8.2.3 Auto R-Modifier Enable (AutoRMod)                         |    |

| 8.2.4 Auxiliary Output Disable (AuxOutDis)                      |    |

| 8.2.5 PLL Clock Output Disable (ClkOutDis)                      |    |

| 8.3 Device Configuration 1 (Address 03h)                        |    |

| 8.3.1 R-Mod Selection (RModSel[2:0])                            |    |

| 8.3.2 Auxiliary Output Source Selection (AuxOutSrc[1:0])        |    |

| 8.3.3 Enable Device Configuration Registers 1 (EnDevCfg1)       |    |

| 8.4 Global Configuration (Address 05h)                          |    |

| 8.4.1 Device Configuration Freeze (Freeze)                      |    |

| 8.4.2 Enable Device Configuration Registers 2 (EnDevCfg2)       | 26 |

|      | 8.5 Ratio (Address 06h - 09h)                                                   | 27 |

|------|---------------------------------------------------------------------------------|----|

|      | 8.6 Function Configuration 1 (Address 16h)                                      | 27 |

|      | 8.6.1 Clock Skip Enable (ClkSkipEn)                                             |    |

|      | 8.6.2 AUX PLL Lock Output Configuration (AuxLockCfg)                            | 27 |

|      | 8.6.3 Enable Device Configuration Registers 3 (EnDevCfg3)                       | 27 |

|      | 8.7 Function Configuration 2 (Address 17h)                                      | 28 |

|      | 8.7.1 Enable PLL Clock Output on Unlock (ClkOutUnl)                             | 28 |

|      | 8.7.2 Low-Frequency Ratio Configuration (LFRatioCfg)                            | 28 |

|      | 8.8 Function Configuration 3 (Address 1Eh)                                      | 28 |

|      | 8.8.1 Clock Input Bandwidth (ClkIn_BW[2:0])                                     | 28 |

|      | 9. CALCULATING THE USER DEFINED RATIO                                           | 29 |

|      | 9.1 High Resolution 12.20 Format                                                | 29 |

|      | 9.2 High Multiplication 20.12 Format                                            |    |

|      | 10. PACKAGE DIMENSIONS                                                          |    |

|      | THERMAL CHARACTERISTICS                                                         |    |

|      | 11. ORDERING INFORMATION                                                        |    |

|      | 12. REFERENCES                                                                  |    |

|      | 13. REVISION HISTORY                                                            | 31 |

| LIST | OF FIGURES                                                                      |    |

| LIGI |                                                                                 |    |

|      | Figure 1. Typical Connection Diagram                                            |    |

|      | Figure 2. Control Port Timing - I <sup>2</sup> C Format                         |    |

|      | Figure 3. Control Port Timing - SPI Format (Write Only)                         |    |

|      | Figure 4. Delta-Sigma Fractional-N Frequency Synthesizer                        |    |

|      | Figure 5. Hybrid Analog-Digital PLL                                             |    |

|      | Figure 6. External Component Requirements for LCO                               | 12 |

|      | Figure 7. CLK_IN removed for > 2 <sup>23</sup> LCO cycles                       | 13 |

|      | Figure 8. CLK_IN removed for < 2 <sup>23</sup> LCO cycles but > t <sub>CS</sub> |    |

|      | Figure 9. CLK_IN removed for < t <sub>CS</sub>                                  |    |

|      | Figure 10. Low bandwidth and new clock domain                                   |    |

|      | Figure 11. High bandwidth with CLK_IN domain re-use                             |    |

|      | Figure 12. Ratio Feature Summary                                                |    |

|      | Figure 13. PLL Clock Output Options                                             |    |

|      | Figure 14. Auxiliary Output Selection                                           |    |

|      | Figure 15. Control Port Timing in SPI Mode                                      |    |

|      | Figure 16. Control Port Timing, I <sup>2</sup> C Write                          |    |

|      | Figure 17. Control Port Timing, I <sup>2</sup> C Aborted Write + Read           | 22 |

| LIST | OF TABLES                                                                       |    |

|      | Table 1. PLL Input Clock Range Indicator                                        | 12 |

|      | Table 2. Ratio Modifier                                                         |    |

|      | Table 3. Automatic Ratio Modifier                                               |    |

|      | Table 4. Example Audio Oversampling Clock Generation from CLK_IN                |    |

|      | Table 5. Example 12.20 R-Values                                                 |    |

|      | Table 6 Example 20.12 R-Values                                                  | 20 |

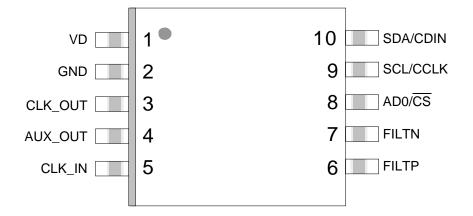

# 1. PIN DESCRIPTION

| Pin Name       | #      | Pin Description                                                                                                                                                                        |

|----------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VD             | 1      | Digital Power (Input) - Positive power supply for the digital and analog sections.                                                                                                     |

| GND            | 2      | Ground (Input) - Ground reference.                                                                                                                                                     |

| CLK_OUT        | 3      | PLL Clock Output (Output) - PLL clock output.                                                                                                                                          |

| AUX_OUT        | 4      | <b>Auxiliary Output</b> ( <i>Output</i> ) - This pin outputs a buffered version of one of the input or output clocks, or a status signal, depending on register configuration.         |

| CLK_IN         | 5      | Frequency Reference Clock Input (Input) - Clock input for the Digital PLL frequency reference.                                                                                         |

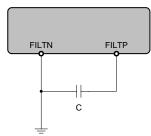

| FILTP<br>FILTN | 6<br>7 | <b>LCO Filter Connections</b> ( <i>Input/Output</i> ) - These pins provide external supply filtering for the internal LC Oscillator.                                                   |

| AD0/CS         | 8      | Address Bit 0 (I <sup>2</sup> C) / Control Port Chip Select (SPI) (Input) - AD0 is a chip address pin in I <sup>2</sup> C Mode. $\overline{CS}$ is the chip select signal in SPI Mode. |

| SCL/CCLK       | 9      | <b>Control Port Clock</b> ( <i>Input</i> ) - SCL/CCLK is the serial clock for the serial control port in I <sup>2</sup> C and SPI mode.                                                |

| SDA/CDIN       | 10     | <b>Serial Control Data</b> ( <i>Input/Output</i> ) - SDA is the data I/O line in I <sup>2</sup> C Mode. CDIN is the input data line for the control port interface in SPI Mode.        |

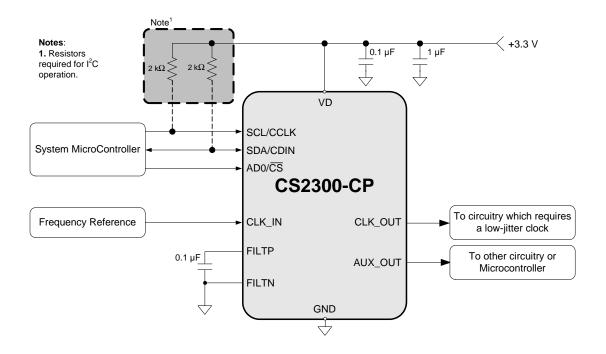

# 2. TYPICAL CONNECTION DIAGRAM

Figure 1. Typical Connection Diagram

#### 3. CHARACTERISTICS AND SPECIFICATIONS

#### RECOMMENDED OPERATING CONDITIONS

GND = 0 V; all voltages with respect to ground. (Note 1)

| Parameters                                    | Symbol   | Min | Тур | Max | Units |

|-----------------------------------------------|----------|-----|-----|-----|-------|

| DC Power Supply                               | VD       | 3.1 | 3.3 | 3.5 | V     |

| Ambient Operating Temperature (Power Applied) |          |     |     |     |       |

| Commercial Grade                              | $T_{AC}$ | -10 | -   | +70 | °C    |

**Notes:** 1. Device functional operation is guaranteed within these limits. Functionality is not guaranteed or implied outside of these limits. Operation outside of these limits may adversely affect device reliability.

#### ABSOLUTE MAXIMUM RATINGS

GND = 0 V; all voltages with respect to ground.

| Parameters                                    | Symbol           | Min  | Max      | Units |

|-----------------------------------------------|------------------|------|----------|-------|

| DC Power Supply                               | VD               | -0.3 | 6.0      | V     |

| Input Current                                 | I <sub>IN</sub>  | -    | ±10      | mA    |

| Digital Input Voltage (Note 1)                | V <sub>IN</sub>  | -0.3 | VD + 0.4 | V     |

| Ambient Operating Temperature (Power Applied) | T <sub>A</sub>   | -55  | 125      | °C    |

| Storage Temperature                           | T <sub>stg</sub> | -65  | 150      | °C    |

**WARNING:** Operation at or beyond these limits may result in permanent damage to the device.

Notes: 1. The maximum over/under voltage is limited by the input current except on the power supply pin.

# DC ELECTRICAL CHARACTERISTICS

Test Conditions (unless otherwise specified): VD = 3.1 V to 3.5 V;  $T_A = -10^{\circ}\text{C}$  to  $+70^{\circ}\text{C}$  (Commercial Grade).

| Parameters                                            | Symbol          | Min | Тур | Max | Units |

|-------------------------------------------------------|-----------------|-----|-----|-----|-------|

| Power Supply Current - Unloaded (Note 2)              | I <sub>D</sub>  | -   | 18  | 23  | mA    |

| Power Dissipation - Unloaded (Note 2)                 | $P_{D}$         | -   | 59  | 76  | mW    |

| Input Leakage Current                                 | I <sub>IN</sub> | -   | -   | ±10 | μA    |

| Input Capacitance                                     | I <sub>C</sub>  | -   | 8   | -   | pF    |

| High-Level Input Voltage                              | V <sub>IH</sub> | 70% | -   | -   | VD    |

| Low-Level Input Voltage                               | $V_{IL}$        | -   | -   | 30% | VD    |

| High-Level Output Voltage (I <sub>OH</sub> = -1.2 mA) | V <sub>OH</sub> | 80% | -   | -   | VD    |

| Low-Level Output Voltage (I <sub>OH</sub> = 1.2 mA)   | $V_{OL}$        | -   | -   | 20% | VD    |

Notes: 2. To calculate the additional current consumption due to loading (per output pin), multiply clock output frequency by load capacitance and power supply voltage.

For example, f<sub>CLK\_OUT</sub> (49.152 MHz) \* C<sub>L</sub>(15 pF) \* VD (3.3 V) = 2.4 mA of additional current due to these loading conditions on CLK\_OUT.

# **AC ELECTRICAL CHARACTERISTICS**

Test Conditions (unless otherwise specified): VD = 3.1 V to 3.5 V;  $T_A = -10^{\circ}\text{C}$  to  $+70^{\circ}\text{C}$  (Commercial Grade);  $C_1 = 15 \text{ pF}$ .

| Parameters                                  | Symbol                | Conditions                    | Min   | Тур | Max | Units  |

|---------------------------------------------|-----------------------|-------------------------------|-------|-----|-----|--------|

| Clock Input Frequency (Auto R-Mod Disabled) | f <sub>CLK_IN</sub>   |                               | 50 Hz | -   | 30  | MHz    |

| Clock Input Frequency (Auto R-mod Enabled)  | f <sub>CLK_IN</sub>   | Auto R Modifier = 1           | 4     | -   | 59  | kHz    |

|                                             |                       | Auto R Modifier = 0.5         | 72    | -   | 138 | kHz    |

|                                             |                       | Auto R Modifier = 0.25        | 168   | -   | 256 | kHz    |

| Clock Input Pulse Width                     | pw <sub>CLK_IN</sub>  | f <sub>CLK_IN</sub> < 175 kHz | 140   | -   | -   | ns     |

|                                             |                       | f <sub>CLK_IN</sub> > 175 kHz | 10    | -   | -   | ns     |

| Clock Skipping Timeout                      | t <sub>CS</sub>       | (Notes 3, 4)                  | 20    | -   | -   | ms     |

| Clock Skipping Input Frequency              | f <sub>CLK_SKIP</sub> | (Note 4)                      | 50 Hz | -   | 80  | kHz    |

| PLL Clock Output Frequency                  | f <sub>CLK_OUT</sub>  |                               | 6     | -   | 75  | MHz    |

| PLL Clock Output Duty Cycle                 | t <sub>OD</sub>       | Measured at VD/2              | 48    | 50  | 52  | %      |

| Clock Output Rise Time                      | t <sub>OR</sub>       | 20% to 80% of VD              | -     | 1.7 | 3.0 | ns     |

| Clock Output Fall Time                      | t <sub>OF</sub>       | 80% to 20% of VD              | -     | 1.7 | 3.0 | ns     |

| Period Jitter                               | t <sub>JIT</sub>      | (Note 5)                      | -     | 35  | 110 | ps rms |

| Base Band Jitter (100 Hz to 40 kHz)         |                       | (Notes 5, 6)                  | -     | 50  | -   | ps rms |

| Wide Band JItter (100 Hz Corner)            |                       | (Notes 5, 7)                  | -     | 150 | -   | ps rms |

| PLL Lock Time - CLK_IN (Note 8)             | t <sub>LC</sub>       | f <sub>CLK_IN</sub> < 200 kHz | -     | 100 | 200 | UI     |

|                                             |                       | f <sub>CLK_IN</sub> > 200 kHz | -     | 1   | 3   | ms     |

- **Notes:** 3. t<sub>CS</sub> represents the time from the removal of CLK\_IN by which CLK\_IN must be re-applied to ensure that PLL\_OUT continues while the PLL re-acquires lock. This timeout is based on the internal VCO frequency, with the minimum timeout occurring at the maximum VCO frequency. Lower VCO frequencies will result in larger values of t<sub>CS</sub>.

- 4. Only valid in clock skipping mode; See "CLK\_IN Skipping Mode" on page 13 for more information.

- 5. f<sub>CLK\_OUT</sub> = 24.576 MHz; Sample size = 10,000 points; AuxOutSrc[1:0] = 11.

- 6. In accordance with AES-12id-2006 section 3.4.2. Measurements are Time Interval Error taken with 3rd order 100 Hz to 40 kHz bandpass filter.

- 7. In accordance with AES-12id-2006 section 3.4.1. Measurements are Time Interval Error taken with 3rd order 100 Hz Highpass filter.

- 8. 1 UI (unit interval) corresponds to t<sub>CLK IN</sub> or 1/f<sub>CLK IN</sub>.

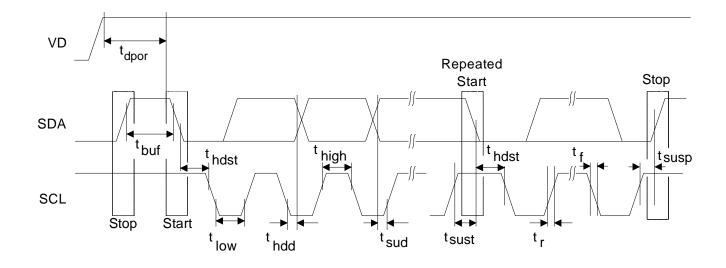

# CONTROL PORT SWITCHING CHARACTERISTICS- I2C FORMAT

Inputs: Logic 0 = GND; Logic 1 = VD;  $C_L = 20 pF$ .

| Parameter                                              | Symbol            | Min | Max  | Unit |

|--------------------------------------------------------|-------------------|-----|------|------|

| SCL Clock Frequency                                    | f <sub>scl</sub>  | -   | 100  | kHz  |

| Bus Free-Time Between Transmissions                    | t <sub>buf</sub>  | 4.7 | -    | μs   |

| Start Condition Hold Time (prior to first clock pulse) | t <sub>hdst</sub> | 4.0 | -    | μs   |

| Clock Low Time                                         | t <sub>low</sub>  | 4.7 | -    | μs   |

| Clock High Time                                        | t <sub>high</sub> | 4.0 | -    | μs   |

| Setup Time for Repeated Start Condition                | t <sub>sust</sub> | 4.7 | -    | μs   |

| SDA Hold Time from SCL Falling (Note 9)                | t <sub>hdd</sub>  | 0   | -    | μs   |

| SDA Setup Time to SCL Rising                           | t <sub>sud</sub>  | 250 | -    | ns   |

| Rise Time of SCL and SDA                               | t <sub>r</sub>    | -   | 1    | μs   |

| Fall Time SCL and SDA                                  | t <sub>f</sub>    | -   | 300  | ns   |

| Setup Time for Stop Condition                          | t <sub>susp</sub> | 4.7 | -    | μs   |

| Acknowledge Delay from SCL Falling                     | t <sub>ack</sub>  | 300 | 1000 | ns   |

| Delay from Supply Voltage Stable to Control Port Ready | t <sub>dpor</sub> | 100 | -    | μs   |

**Notes:** 9. Data must be held for sufficient time to bridge the transition time,  $t_f$ , of SCL.

Figure 2. Control Port Timing - I<sup>2</sup>C Format

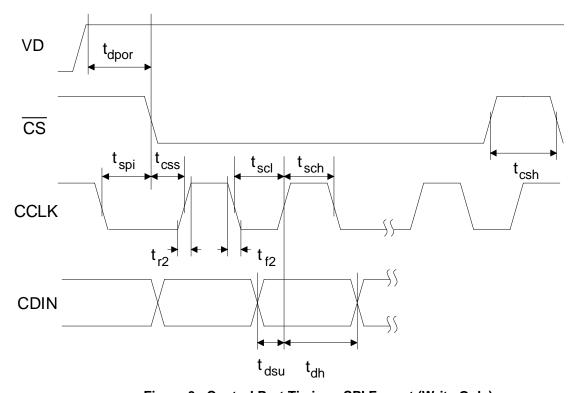

# **CONTROL PORT SWITCHING CHARACTERISTICS - SPI FORMAT**

Inputs: Logic 0 = GND; Logic 1 = VD;  $C_L = 20 \text{ pF}.$

| Parameter                                              |           | Symbol             | Min | Max | Unit |

|--------------------------------------------------------|-----------|--------------------|-----|-----|------|

| CCLK Clock Frequency                                   |           | f <sub>ccllk</sub> | -   | 6   | MHz  |

| CCLK Edge to CS Falling                                | (Note 10) | t <sub>spi</sub>   | 500 | -   | ns   |

| CS High Time Between Transmissions                     |           | t <sub>csh</sub>   | 1.0 | -   | μs   |

| CS Falling to CCLK Edge                                |           | t <sub>css</sub>   | 20  | -   | ns   |

| CCLK Low Time                                          |           | t <sub>scl</sub>   | 66  | -   | ns   |

| CCLK High Time                                         |           | t <sub>sch</sub>   | 66  | -   | ns   |

| CDIN to CCLK Rising Setup Time                         |           | t <sub>dsu</sub>   | 40  | -   | ns   |

| CCLK Rising to DATA Hold Time                          | (Note 11) | t <sub>dh</sub>    | 15  | -   | ns   |

| Rise Time of CCLK and CDIN                             | (Note 12) | t <sub>r2</sub>    | -   | 100 | ns   |

| Fall Time of CCLK and CDIN                             | (Note 12) | t <sub>f2</sub>    | -   | 100 | ns   |

| Delay from Supply Voltage Stable to Control Port Ready |           | t <sub>dpor</sub>  | 100 | -   | μs   |

**Notes:** 10.  $t_{spi}$  is only needed before first falling edge of  $\overline{CS}$  after power is applied.  $t_{spi} = 0$  at all other times.

- 11. Data must be held for sufficient time to bridge the transition time of CCLK.

- 12. For  $f_{cclk} < 1$  MHz.

Figure 3. Control Port Timing - SPI Format (Write Only)

#### 4. ARCHITECTURE OVERVIEW

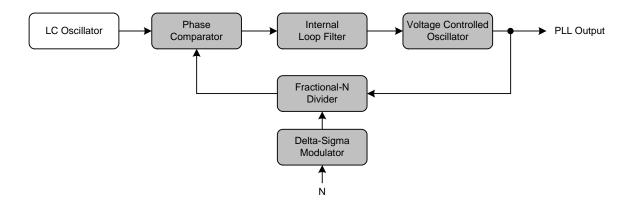

#### 4.1 Delta-Sigma Fractional-N Frequency Synthesizer

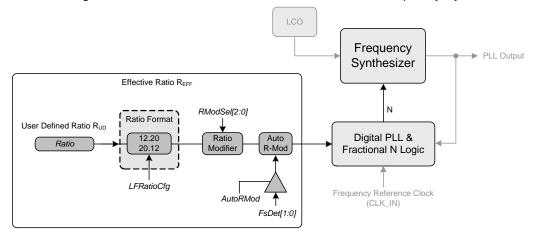

The core of the CS2300 is a Delta-Sigma Fractional-N Frequency Synthesizer which has very high-resolution for Input/Output clock ratios, low phase noise, very wide range of output frequencies and the ability to quickly tune to a new frequency. The reference for the synthesizer is an on chip LC Oscillator (LCO) which generates the necessary internal stable clocks. In very simplistic terms, the Fractional-N Frequency Synthesizer multiplies the LC Oscillator by the value of N to generate the PLL output clock. The desired output to input clock ratio is the value of N that is applied to the delta-sigma modulator (see Figure 4).

The analog PLL based frequency synthesizer uses a low-jitter timing reference clock, the LCO, as a time and phase reference for the internal voltage controlled oscillator (VCO). The phase comparator compares the fractional-N divided clock with the original timing reference and generates a control signal. The control signal is filtered by the internal loop filter to generate the VCO's control voltage which sets its output frequency. The delta-sigma modulator modulates the loop integer divide ratio to get the desired fractional ratio between the reference clock and the VCO output (thus the one's density of the modulator sets the fractional value). This allows the design to be optimized for very fast lock times for a wide range of output frequencies without the need for external filter components.

Figure 4. Delta-Sigma Fractional-N Frequency Synthesizer

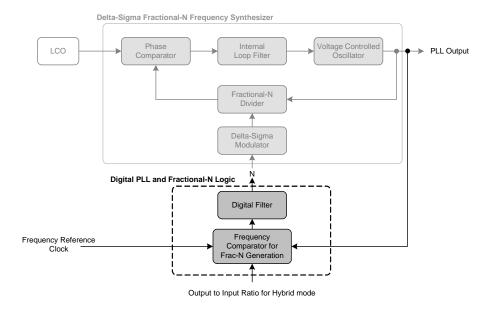

### 4.2 Hybrid Analog-Digital Phase Locked Loop

The addition of the Digital PLL and Fractional-N Logic (shown in Figure 5) to the Fractional-N Frequency Synthesizer creates the Hybrid Analog-Digital Phase Locked Loop with many advantages over classical analog PLL techniques. These advantages include the ability to operate over extremely wide frequency ranges without the need to change external loop filter components while maintaining impressive jitter reduction performance. In the Hybrid architecture, the Digital PLL calculates the ratio of the PLL output clock to the frequency reference and compares that to the desired ratio. The digital logic generates a value of N which is then applied to the Fractional-N frequency synthesizer to generate the desired PLL output frequency. Notice that the frequency and phase of the LCO does not affect the output of the PLL since the digital control loop will correct for the PLL output. A major advantage of the Digital PLL is the ease with which the loop filter bandwidth can be altered. The PLL bandwidth is automatically set to a wide-bandwidth mode to quickly achieve lock and then reduced for optimal jitter rejection.

Figure 5. Hybrid Analog-Digital PLL

#### 5. APPLICATIONS

#### 5.1 Timing Reference Clock

The internal LC oscillator is used to generate the internal timing reference clock (see section 4 "Architecture Overview" on page 10 for information on how this internal clock is used by the CS2300). A single 0.1 µF cap must be connected between the FILTP and FILTN pins and the FILTN pin must be connected to ground as shown in Figure 6.

Figure 6. External Component Requirements for LCO

#### 5.2 Frequency Reference Clock Input, CLK\_IN

The frequency reference clock input (CLK\_IN) is used by the Digital PLL and Fractional-N Logic block to dynamically generate a fractional-N value for the Frequency Synthesizer (see "Hybrid Analog-Digital PLL" on page 11). The Digital PLL first compares the CLK\_IN frequency to the PLL output. The Fractional-N logic block then translates the desired ratio based off of CLK\_IN to one based off of the internal LCO. This allows the low-jitter internal LCO to be used as the clock which the Frequency Synthesizer multiplies while maintaining synchronicity with the frequency reference clock through the Digital PLL. The allowable frequency range for CLK\_IN is found in the "AC Electrical Characteristics" on page 7.

#### 5.2.1 CLK IN Frequency Detector

The CLK\_IN frequency range detector determines and indicates the ratio between the frequency of the internal LCO and the CLK\_IN input signal.

The result of the ratio measurement is available in the read-only *FsDet[1:0]* bits and is also used by the device to determine the Auto R-Mod value.

| FsDetect[1:0] | f <sub>LCO</sub> / f <sub>CLK_IN</sub> Ratio |

|---------------|----------------------------------------------|

| 00            | > 224                                        |

| 01            | 96 - 224                                     |

| 10            | < 96                                         |

| 11            | Reserved                                     |

Table 1. PLL Input Clock Range Indicator

Because f<sub>LCO</sub> is known, *FsDet[1:0]* can then be interpreted as a range for f<sub>CLK\_IN</sub>. This feature is particularly useful when used in conjunction with the Auto R-Mod feature (see section 5.3.3 on page 16).

| Referenced Control | Register Location                                                             |

|--------------------|-------------------------------------------------------------------------------|

| FsDet[1:0]         | "PLL Input Sample Rate Indicator (FsDet[1:0]) - Read Only" section on page 24 |

#### 5.2.2 CLK\_IN Skipping Mode

CLK\_IN skipping mode allows the PLL to maintain lock even when the CLK\_IN signal has missing pulses for up to 20 ms (t<sub>CS</sub>) at a time (see "AC Electrical Characteristics" on page 7 for specifications). CLK\_IN skipping mode can only be used when the CLK\_IN frequency is below 80 kHz. The *ClkSkipEn* bit enables this function.

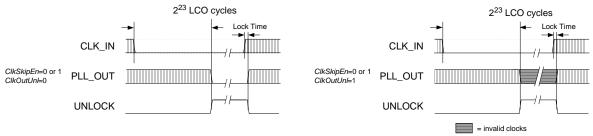

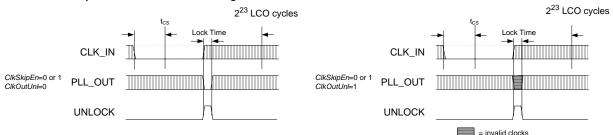

Regardless of the setting of the *ClkSkipEn* bit the PLL output will continue for 2<sup>23</sup> LCO cycles (518 ms to 634 ms) after CLK\_IN is removed (see Figure 7). This is true as long as CLK\_IN does not glitch or have an effective change in period as the clock source is removed, otherwise the PLL will interpret this as a change in frequency causing clock skipping and the 2<sup>23</sup> LCO cycle time-out to be bypassed and the PLL to immediately unlock. If the prior conditions are met while CLK\_IN is removed and 2<sup>23</sup> LCO cycles pass, the PLL will unlock and the PLL\_OUT state will be determined by the *ClkOutUnl* bit; See "PLL Clock Output" on page 19. If CLK\_IN is re-applied after such time, the PLL will remain unlocked for the specified time listed in the "AC Electrical Characteristics" on page 7 after which lock will be acquired and the PLL output will resume.

Figure 7. CLK\_IN removed for  $> 2^{23}$  LCO cycles

If CLK\_IN is removed and then reapplied within  $2^{23}$  LCO cycles but later than  $t_{CS}$ , the *ClkSkipEn* bit will have no effect and the PLL output will continue until CLK\_IN is re-applied (see Figure 8). Once CLK\_IN is re-applied, the PLL will go unlocked only for the time it takes to acquire lock; the PLL\_OUT state will be determined by the *ClkOutUnl* bit during this time.

Figure 8. CLK\_IN removed for  $< 2^{23}$  LCO cycles but  $> t_{CS}$

If CLK\_IN is removed and then re-applied within  $t_{CS}$ , the  $\mathit{ClkSkipEn}$  bit determines whether PLL\_OUT continues while the PLL re-acquires lock (see Figure 9). When  $\mathit{ClkSkipEn}$  is disabled and CLK\_IN is removed the PLL output will continue until CLK\_IN is re-applied at which point the PLL will go unlocked only for the time it takes to acquire lock; the PLL\_OUT state will be determined by the  $\mathit{ClkOutUnl}$  bit during this

time. When *ClkSkipEn* is enabled and CLK\_IN is removed the PLL output clock will remain continuous throughout the missing CLK\_IN period including the time while the PLL re-acquires lock.

Figure 9. CLK\_IN removed for < t<sub>CS</sub>

| Referenced Control | Register Location                                                                                        |

|--------------------|----------------------------------------------------------------------------------------------------------|

| ClkSkipEnClkOutUnl | "Clock Skip Enable (ClkSkipEn)" on page 27<br>"Enable PLL Clock Output on Unlock (ClkOutUnl)" on page 28 |

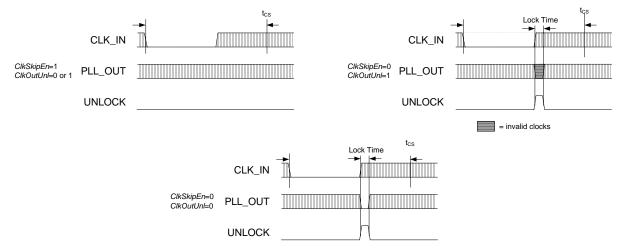

## 5.2.3 Adjusting the Minimum Loop Bandwidth for CLK\_IN

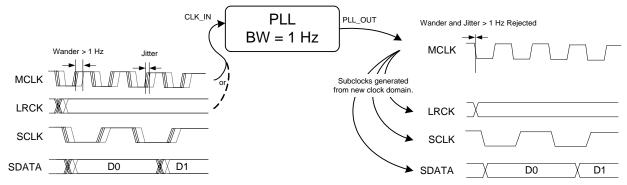

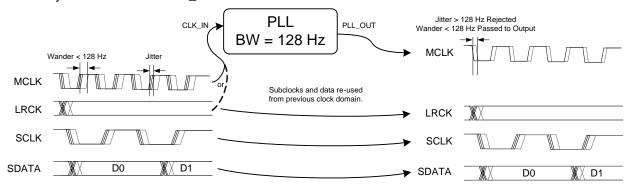

The CS2000 allows the minimum loop bandwidth of the Digital PLL to be adjusted between 1 Hz and 128 Hz using the *ClkIn\_BW[2:0]* bits. The minimum loop bandwidth of the Digital PLL directly affects the jitter transfer function; specifically, jitter frequencies below the loop bandwidth corner are passed from the PLL input directly to the PLL output without attenuation. In some applications it is desirable to have a very low minimum loop bandwidth to reject very low jitter frequencies, commonly referred to as wander. In others it may be preferable to remove only higher frequency jitter, allowing the input wander to pass through the PLL without attenuation.

Typically, applications in which the PLL\_OUT signal creates a new clock domain from which all other system clocks and associated data are derived will benefit from the maximum jitter and wander rejection of the lowest PLL bandwidth setting. See Figure 10.

Figure 10. Low bandwidth and new clock domain

Systems in which some clocks and data are derived from the PLL\_OUT signal while other clocks and data are derived from the CLK\_IN signal will often require phase alignment of all the clocks and data in the system. See Figure 11. If there is substantial wander on the CLK\_IN signal in these applications, it may be necessary to increase the minimum loop bandwidth allowing this wander to pass through to the

CLK\_OUT signal in order to maintain phase alignment. For these applications, it is advised to experiment with the loop bandwidth settings and choose the lowest bandwidth setting that does not produce system timing errors due to wandering between the clocks and data synchronous to the CLK\_IN domain and those synchronous to the PLL OUT domain.

Figure 11. High bandwidth with CLK\_IN domain re-use

It should be noted that manual adjustment of the minimum loop bandwidth is not necessary to acquire lock; this adjustment is made automatically by the Digital PLL. While acquiring lock, the digital loop bandwidth is automatically set to a large value. Once lock is achieved, the digital loop bandwidth will settle to the minimum value selected by the *ClkIn\_BW[2:0]* bits.

| Referenced Control | Register Location                                  |

|--------------------|----------------------------------------------------|

| ClkIn_BW[2:0]      | "Clock Input Bandwidth (ClkIn_BW[2:0])" on page 28 |

### 5.3 Output to Input Frequency Ratio Configuration

# 5.3.1 User Defined Ratio (R<sub>UD</sub>)

The User Defined Ratio,  $R_{UD}$ , is a 32-bit un-signed fixed-point number, stored in the *Ratio* register set, which determines the basis for the desired input to output clock ratio. The 32-bit  $R_{UD}$  can be expressed in either a high resolution (12.20) or high multiplication (20.12) format selectable by the *LFRatioCfg* bit, with 20.12 being the default.

The  $R_{UD}$  for high resolution (12.20) format is encoded with 12 MSBs representing the integer binary portion with the remaining 20 LSBs representing the fractional binary portion. The maximum multiplication factor is approximately 4096 with a resolution of 0.954 PPM in this configuration. See "Calculating the User Defined Ratio" on page 29 for more information.

The  $R_{UD}$  for high multiplication (20.12) format is encoded with 20 MSBs representing the integer binary portion with the remaining 12 LSBs representing the fractional binary portion. In this configuration, the maximum multiplication factor is approximately 1,048,575 with a resolution of 244 PPM. It is recommended that the 12.20 High-Resolution format be utilized whenever the desired ratio is less than 4096 since the output frequency accuracy of the PLL is directly proportional to the accuracy of the timing reference clock and the resolution of the  $R_{UD}$ .

| Referenced Control | Register Location                                           |

|--------------------|-------------------------------------------------------------|

| Ratio              |                                                             |

| LFRatioCfg         | "Low-Frequency Ratio Configuration (LFRatioCfg)" on page 28 |

#### 5.3.2 Manual Ratio Modifier (R-Mod)

The manual Ratio Modifier is used to internally multiply/divide the  $R_{UD}$  (the *Ratio* stored in the register space remains unchanged). The available options for  $R_{MOD}$  are summarized in Table 2 on page 16.

The R-Mod value selected by *RModSel[2:0]* is always used in the calculation for the Effective Ratio (R<sub>EFF</sub>), see "Effective Ratio (REFF)" on page 17. If R-Mod is not desired, *RModSel[2:0]* should be left at its default value of '000', which corresponds to an R-Mod value of 1, thereby effectively disabling the ratio modifier.

| RModSel[2:0] | Ratio Modifier |

|--------------|----------------|

| 000          | 1              |

| 001          | 2              |

| 010          | 4              |

| 011          | 8              |

| 100          | 0.5            |

| 101          | 0.25           |

| 110          | 0.125          |

| 111          | 0.0625         |

**Table 2. Ratio Modifier**

| Referenced Control | Register Location                                   |

|--------------------|-----------------------------------------------------|

| Ratio              | "Ratio (Address 06h - 09h)" on page 27              |

| RModSel[2:0]       | "R-Mod Selection (RModSel[2:0])" section on page 25 |

#### 5.3.3 Automatic Ratio Modifier (Auto R-Mod)

The Automatic R-Modifier uses the status of the CLK\_IN Frequency Range Indicator (see section 5.2.1 on page 12) to implement a frequency dependent multiply of the currently addressed R<sub>UD</sub> as shown in Table 3.

Like with R-Mod, the *Ratio* stored in the register space remain unchanged. The Automatic Ratio-Modifier is enabled by the *AutoRMod* bit.

| FsDetect[1:0] | f <sub>LCO</sub> / f <sub>CLK_IN</sub> | Auto R Modifier |

|---------------|----------------------------------------|-----------------|

| 00            | > 224                                  | 1               |

| 01            | 96 - 224                               | 0.5             |

| 10            | < 96                                   | 0.25            |

**Table 3. Automatic Ratio Modifier**

It is important to note that Auto R-Mod (if enabled) is applied in addition to any R-Mod already selected by the *RModSel[2:0]* bits and is used to calculate the Effective Ratio (see Section 5.3.4 on page 17).

Auto R-Mod can be used to generate the appropriate oversampling clock (MCLK) for audio A/D and D/A converters. For example, when the clock applied to CLK\_IN is the audio sample rate, Fs (also known as the word, frame or Left/Right clock), and the internal LCO is known to be between 13.23 MHz and 16.17

MHz, then FsDetect[1:0] reflects the frequency range of the audio sample rate. An R<sub>UD</sub> of 512 generates the audio oversampling clocks as shown in Table 4.

| FsDetect[1:0] | Inferred Audio Sample Rate                  | Speed Mode (used for audio converters) | Audio Oversampling<br>Clock |

|---------------|---------------------------------------------|----------------------------------------|-----------------------------|

| 00            | < [59 to 72] kHz                            | Single Speed                           | 512 x                       |

| 01            | >[59 to 72] kHz<br>and<br><[138 to 168] kHz | Double Speed                           | 256 x                       |

| 10            | > [138 to 168] kHz                          | Quad Speed                             | 128 x                       |

Table 4. Example Audio Oversampling Clock Generation from CLK\_IN

| Referenced Control | Register Location                              |

|--------------------|------------------------------------------------|

| Ratio              | "Ratio (Address 06h - 09h)" on page 27         |

| RModSel[2:0]       |                                                |

| AutoRMod           | "Auto R-Modifier Enable (AutoRMod)" on page 25 |

## 5.3.4 Effective Ratio (R<sub>EFF</sub>)

The Effective Ratio ( $R_{EFF}$ ) is an internal calculation comprised of  $R_{UD}$  and the appropriate modifiers, as previously described.  $R_{EFF}$  is calculated as follows:

$$R_{EFF} = R_{UD} \bullet R_{MOD} \bullet Auto R-Mod$$

Ratio modifiers which would produce an overflow or truncation of  $R_{EFF}$  should not be used; For example if  $R_{UD}$  is 1024 an  $R_{MOD}$  of 8 would produce an  $R_{EFF}$  value of 8192 which exceeds the 4096 limit of the 12.20 format. In all cases, the maximum and minimum allowable values for  $R_{EFF}$  are dictated by the frequency limits for both the input and output clocks as shown in the "AC Electrical Characteristics" on page 7.

# 5.3.5 Ratio Configuration Summary

The  $R_{UD}$  is the user defined ratio stored in the register space. The resolution for the  $R_{UD}$  is selectable by setting LFRatioCfg. R-Mod is applied if selected. The user defined ratio, ratio modifier, and automatic ratio modifier make up the effective ratio  $R_{EFF}$ , the final calculation used to determine the output to input clock ratio. The conceptual diagram in Figure 12 summarizes the features involved in the calculation of the ratio values used to generate the fractional-N value which controls the Frequency Synthesizer.

Figure 12. Ratio Feature Summary

| Referenced Control | Register Location                                                             |

|--------------------|-------------------------------------------------------------------------------|

| Ratio              | "Ratio (Address 06h - 09h)" on page 27                                        |

| LFRatioCfg         | "Low-Frequency Ratio Configuration (LFRatioCfg)" on page 28                   |

|                    | "R-Mod Selection (RModSel[2:0])" section on page 25                           |

| AutoRMod           | "Auto R-Modifier Enable (AutoRMod)" on page 25                                |

| FsDet[1:0]         | "PLL Input Sample Rate Indicator (FsDet[1:0]) - Read Only" section on page 24 |

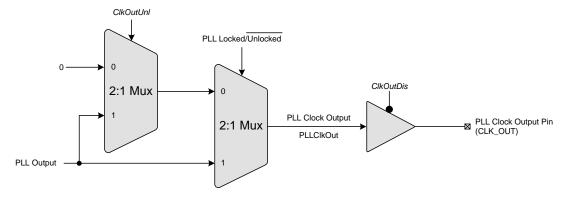

#### 5.4 PLL Clock Output

The PLL clock output pin (CLK\_OUT) provides a buffered version of the output of the frequency synthesizer. The driver can be set to high-impedance with the *ClkOutDis* bit.

The output from the PLL automatically drives a static low condition while the PLL is un-locked (when the clock may be unreliable). This feature can be disabled by setting the *ClkOutUnl* bit, however the state CLK\_OUT may then be unreliable during an unlock condition.

Figure 13. PLL Clock Output Options

| Referenced Control | Register Location                                          |

|--------------------|------------------------------------------------------------|

| ClkOutUnl          | "Enable PLL Clock Output on Unlock (ClkOutUnl)" on page 28 |

|                    | "PLL Clock Output Disable (ClkOutDis)" on page 25          |

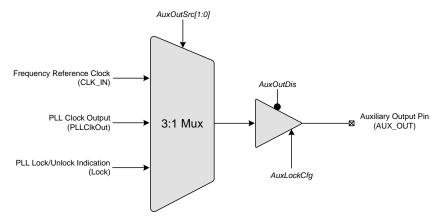

## 5.5 Auxiliary Output

The auxiliary output pin (AUX\_OUT) can be mapped, as shown in Figure 14, to one of three signals: input clock (CLK\_IN), additional PLL clock output (CLK\_OUT), or a PLL lock indicator (Lock). The mux is controlled via the *AuxOutSrc[1:0]* bits. If AUX\_OUT is set to Lock, the *AuxLockCfg* bit is then used to control the output driver type and polarity of the LOCK signal (see section 8.6.2 on page 27). If AUX\_OUT is set to CLK\_OUT the phase of the PLL Clock Output signal on AUX\_OUT may differ from the CLK\_OUT pin. The driver for the pin can be set to high-impedance using the *AuxOutDis* bit.

Figure 14. Auxiliary Output Selection

| Referenced Control | Register Location                                                   |

|--------------------|---------------------------------------------------------------------|

| AuxOutSrc[1:0]     | "Auxiliary Output Source Selection (AuxOutSrc[1:0])" on page 26     |

| AuxOutDis          | "Auxiliary Output Disable (AuxOutDis)" on page 25                   |

| AuxLockCfg         | "AUX PLL Lock Output Configuration (AuxLockCfg)" section on page 27 |

## 5.6 Clock Output Stability Considerations

#### 5.6.1 Output Switching

CS2300 is designed such that re-configuration of the clock routing functions do not result in a partial clock period on any of the active outputs (CLK\_OUT and/or AUX\_OUT). In particular, enabling or disabling an output, and the automatic disabling of the output(s) during unlock will not cause a runt or partial clock period.

The following exceptions/limitations exist:

- Enabling/disabling AUX\_OUT when AuxOutSrc = 11 (unlock indicator).

- Switching AuxOutSrc[1:0] to or from 01 (PLL clock input) and to or from 11 (unlock indicator) (Transitions between AuxOutSrc[1:0] = [00,10] will not produce a glitch).

- Changing the ClkOutUnl bit while the PLL is in operation.

When any of these exceptions occur, a partial clock period on the output may result.

#### 5.6.2 PLL Unlock Conditions

Certain changes to the clock inputs and registers can cause the PLL to lose lock which will affect the presence the clock signal on CLK\_OUT. The following outlines which conditions cause the PLL to go unlocked:

- Changes made to the registers which affect the Fraction-N value that is used by the Frequency Synthesizer. This includes all the bits shown in Figure 12 on page 18.

- · Any discontinuities on the Timing Reference Clock, REF CLK.

- Discontinuities on the Frequency Reference Clock, CLK\_IN, except when the Clock Skipping feature

is enabled and the requirements of Clock Skipping are satisfied (see "CLK\_IN Skipping Mode" on

page 13).

- Gradual changes in CLK\_IN frequency greater than ±30% from the starting frequency.

- Step changes in CLK\_IN frequency.

#### 6. SPI / I<sup>2</sup>C CONTROL PORT

The control port is used to access the registers and allows the device to be configured for the desired operational modes and formats. The operation of the control port may be completely asynchronous with respect to device inputs and outputs. However, to avoid potential interference problems, the control port pins should remain static if no operation is required.

The control port operates with either the SPI or I<sup>2</sup>C interface, with the CS2300 acting as a slave device. SPI Mode is selected if there is a high-to-low transition on the AD0/CS pin after power-up. I<sup>2</sup>C Mode is selected by connecting the AD0/CS pin through a resistor to VD or GND, thereby permanently selecting the desired AD0 bit address state. In both modes the *EnDevCfg1*, *EnDevCfg2*, *and EnDevCfg3* bits must be set to 1 for normal operation.

WARNING: All "Reserved" registers must maintain their default state to ensure proper functional operation.

| Referenced Control | Register Location                                                        |

|--------------------|--------------------------------------------------------------------------|

| EnDevCfg1          | "Enable Device Configuration Registers 1 (EnDevCfg1)" on page 26         |

| EnDevCfg2          | "Enable Device Configuration Registers 2 (EnDevCfg2)" section on page 26 |

| EnDevCfg3          | "Enable Device Configuration Registers 3 (EnDevCfg3)" section on page 27 |

#### 6.1 SPI Control

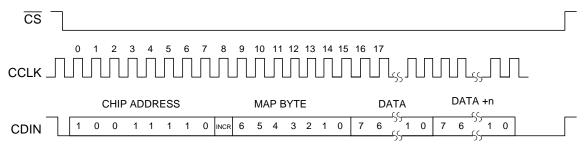

In SPI Mode,  $\overline{CS}$  is the chip select signal; CCLK is the control port bit clock (sourced from a microcontroller), and CDIN is the input data line from the microcontroller. Data is clocked in on the rising edge of CCLK. The device only supports write operations.

Figure 15 shows the operation of the control port in SPI Mode. To write to a register, bring  $\overline{\text{CS}}$  low. The first eight bits on CDIN form the chip address and must be 10011110. The next eight bits form the Memory Address Pointer (MAP), which is set to the address of the register that is to be updated. The next eight bits are the data which will be placed into the register designated by the MAP.

There is MAP auto increment capability, enabled by the INCR bit in the MAP register. If INCR is a zero, the MAP will stay constant for successive read or writes. If INCR is set to a 1, the MAP will automatically increment after each byte is read or written, allowing block writes of successive registers.

Figure 15. Control Port Timing in SPI Mode

#### 6.2 I<sup>2</sup>C Control

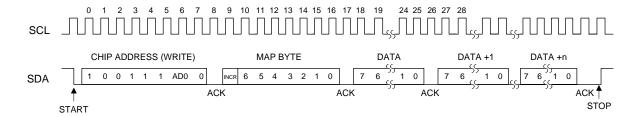

In I<sup>2</sup>C Mode, SDA is a bidirectional data line. Data is clocked into and out of the device by the clock, SCL. There is no CS pin. The AD0 pin forms the least-significant bit of the chip address and should be connected to VD or GND as appropriate. The state of the AD0 pin should be maintained throughout operation of the device.

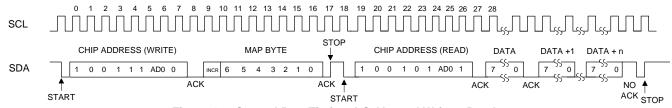

The signal timings for a read and write cycle are shown in Figure 16 and Figure 17. A Start condition is defined as a falling transition of SDA while the clock is high. A Stop condition is a rising transition while the clock is high. All other transitions of SDA occur while the clock is low. The first byte sent to the CS2300 after a Start condition consists of the 7-bit chip address field and a R/W bit (high for a read, low for a write). The

upper 6 bits of the 7-bit address field are fixed at 100111 followed by the logic state of the AD0 pin. The eighth bit of the address is the R/W bit. If the operation is a write, the next byte is the Memory Address Pointer (MAP) which selects the register to be read or written. If the operation is a read, the contents of the register pointed to by the MAP will be output. Setting the auto increment bit in MAP allows successive reads or writes of consecutive registers. Each byte is separated by an acknowledge bit. The ACK bit is output from the CS2300 after each input byte is read and is input from the microcontroller after each transmitted byte.

Figure 16. Control Port Timing, I2C Write

Figure 17. Control Port Timing, I<sup>2</sup>C Aborted Write + Read

Since the read operation cannot set the MAP, an aborted write operation is used as a preamble. As shown in Figure 16, the write operation is aborted after the acknowledge for the MAP byte by sending a stop condition. The following pseudocode illustrates an aborted write operation followed by a read operation.

Send start condition.

Send 100111x0 (chip address & write operation).

Receive acknowledge bit.

Send MAP byte, auto increment off.

Receive acknowledge bit.

Send stop condition, aborting write.

Send start condition.

Send 100111x1(chip address & read operation).

Receive acknowledge bit.

Receive byte, contents of selected register.

Send acknowledge bit.

Send stop condition.

Setting the auto increment bit in the MAP allows successive reads or writes of consecutive registers. Each byte is separated by an acknowledge bit.

#### 6.3 Memory Address Pointer

The Memory Address Pointer (MAP) byte comes after the address byte and selects the register to be read or written. Refer to the pseudocode above for implementation details.

#### 6.3.1 Map Auto Increment

The device has MAP auto increment capability enabled by the INCR bit (the MSB) of the MAP. If INCR is set to 0, MAP will stay constant for successive I<sup>2</sup>C writes or reads and SPI writes. If INCR is set to 1, MAP will auto increment after each byte is read or written, allowing block reads or writes of successive registers.

#### 7. REGISTER QUICK REFERENCE

This table shows the register and bit names with their associated default values. EnDevCfg1, EnDevCfg2, and EnDevCfg3 bits must be set to 1 for normal operation.

WARNING: All "Reserved" registers must maintain their default state to ensure proper functional operation.

| Adr  | Name         | 7         | 6          | 5         | 4         | 3          | 2          | 1          | 0         |

|------|--------------|-----------|------------|-----------|-----------|------------|------------|------------|-----------|

| 01h  | Device ID    | Device4   | Device3    | Device2   | Device1   | Device0    | Revision2  | Revision1  | Revision0 |

| p 24 |              | 0         | 0          | 0         | 0         | 0          | x          | x          | x         |

| 02h  | Device Ctrl  | Unlock    | FsDet1     | FsDet0    | Reserved  | AutoRMod   | Reserved   | AuxOutDis  | ClkOutDis |

| p 24 |              | x         | x          | X         | 0         | 0          | 0          | 0          | 0         |

| 03h  | Device Cfg 1 | RModSel2  | RModSel1   | RModSel0  | Reserved  | Reserved   | AuxOutSrc1 | AuxOutSrc0 | EnDevCfg1 |

| p 25 |              | 0         | 0          | 0         | 0         | 0          | 0          | 0          | 0         |

| 05h  | Global Cfg   | Reserved  | Reserved   | Reserved  | Reserved  | Freeze     | Reserved   | Reserved   | EnDevCfg2 |

| p 26 |              | 0         | 0          | 0         | 0         | 0          | 0          | 0          | 0         |

|      |              | MSB       |            |           |           |            |            |            | MSB-7     |

| 06h  | 32-Bit Ratio | MSB-8     |            |           |           |            |            | MSB-15     |           |

| 09h  | 32-DIL KALIU | LSB+15    |            |           |           |            |            |            | LSB+8     |

|      |              | LSB+7     |            |           |           |            |            |            | LSB       |

| 16h  | Funct Cfg 1  | ClkSkipEn | AuxLockCfg | Reserved  | EnDevCfg3 | Reserved   | Reserved   | Reserved   | Reserved  |

| p 27 |              | 0         | 0          | 0         | 0         | 0          | 0          | 0          | 0         |

| 17h  | Funct Cfg 2  | Reserved  | Reserved   | Reserved  | ClkOutUnl | LFRatioCfg | Reserved   | Reserved   | Reserved  |

| p 28 |              | 0         | 0          | 0         | 0         | 0          | 0          | 0          | 0         |

| 1Eh  | Funct Cfg 3  | Reserved  | ClkIn_BW2  | ClkIn_BW1 | ClkIn_BW0 | Reserved   | Reserved   | Reserved   | Reserved  |

| p 28 |              | 0         | 0          | 0         | 0         | 0          | 0          | 0          | 0         |

#### 8. REGISTER DESCRIPTIONS

In I<sup>2</sup>C Mode all registers are read/write unless otherwise stated. In SPI mode all registers are write only. All "Reserved" registers must maintain their default state to ensure proper functional operation. The default state of each bit after a power-up sequence or reset is indicated by the shaded row in the bit decode table and in the "Register Quick Reference" on page 23.

Control port mode is entered when the device recognizes a valid chip address input on its I<sup>2</sup>C/SPI serial control pins and the *EnDevCfg1*, *EnDevCfg2*, *and EnDevCfg3* bits are set to 1.

#### 8.1 Device I.D. and Revision (Address 01h)

| 7       | 6       | 5       | 4       | 3       | 2         | 1         | 0         |

|---------|---------|---------|---------|---------|-----------|-----------|-----------|

| Device4 | Device3 | Device2 | Device1 | Device0 | Revision2 | Revision1 | Revision0 |

#### 8.1.1 Device Identification (Device[4:0]) - Read Only

I.D. code for the CS2300.

| Device[4:0] | Device  |

|-------------|---------|

| 00000       | CS2300. |

#### 8.1.2 Device Revision (Revision[2:0]) - Read Only

CS2300 revision level.

| REVID[2:0] | Revision Level |

|------------|----------------|

| 100        | B2.            |

#### 8.2 Device Control (Address 02h)

| 7      | 6      | 5      | 4        | 3        | 2        | 1         | 0         |

|--------|--------|--------|----------|----------|----------|-----------|-----------|

| Unlock | FsDet1 | FsDet0 | Reserved | AutoRMod | Reserved | AuxOutDis | ClkOutDis |

#### 8.2.1 Unlock Indicator (Unlock) - Read Only

Indicates the lock state of the PLL.

| Unlock | PLL Lock State   |

|--------|------------------|

| 0      | PLL is Locked.   |

| 1      | PLL is Unlocked. |

#### 8.2.2 PLL Input Sample Rate Indicator (FsDet[1:0]) - Read Only

Indicates the range of the frequency of CLK\_IN relative to the frequency of the internal LCO. For audio applications, this can be used to distinguish single-, double-, and quad-speed modes.

| FsDet[1:0]   | f <sub>LCO</sub> / f <sub>CLK_IN</sub> |

|--------------|----------------------------------------|

| 00           | > 224.                                 |

| 01           | 96 to 224.                             |

| 10           | < 96.                                  |

| 11           | Reserved.                              |

| Application: | "CLK_IN Frequency Detector" on page 12 |

# 8.2.3 Auto R-Modifier Enable (AutoRMod)

Controls the automatic ratio modifier function.

| AutoRMod     | Automatic R-Mod State                              |

|--------------|----------------------------------------------------|

| 0            | Disabled.                                          |

| 1            | Enabled.                                           |

| Application: | "Automatic Ratio Modifier (Auto R-Mod)" on page 16 |

# 8.2.4 Auxiliary Output Disable (AuxOutDis)

This bit controls the output driver for the AUX\_OUT pin.

| AuxOutDis    | Output Driver State                          |

|--------------|----------------------------------------------|

| 0            | AUX_OUT output driver enabled.               |

| 1            | AUX_OUT output driver set to high-impedance. |

| Application: | "Auxiliary Output" on page 19                |

# 8.2.5 PLL Clock Output Disable (ClkOutDis)

This bit controls the output driver for the CLK\_OUT pin.

| ClkOutDis    | Output Driver State                          |  |

|--------------|----------------------------------------------|--|

| 0            | CLK_OUT output driver enabled.               |  |

| 1            | CLK_OUT output driver set to high-impedance. |  |

| Application: | "PLL Clock Output" on page 19                |  |

# 8.3 Device Configuration 1 (Address 03h)

| _ | 7        | 6        | 5        | 4        | 3        | 2          | 1          | 0         |

|---|----------|----------|----------|----------|----------|------------|------------|-----------|

|   | RModSel2 | RModSel1 | RModSel0 | Reserved | Reserved | AuxOutSrc1 | AuxOutSrc0 | EnDevCfg1 |

## 8.3.1 R-Mod Selection (RModSel[2:0])

Selects the R-Mod value, which is used as a factor in determining the PLL's Fractional N.

| RModSel[2:0] | R-Mod Selection                            |

|--------------|--------------------------------------------|

| 000          | Left-shift R-value by 0 (x 1).             |

| 001          | Left-shift R-value by 1 (x 2).             |

| 010          | Left-shift R-value by 2 (x 4).             |

| 011          | Left-shift R-value by 3 (x 8).             |

| 100          | Right-shift R-value by 1 (÷ 2).            |

| 101          | Right-shift R-value by 2 (÷ 4).            |

| 110          | Right-shift R-value by 3 (÷ 8).            |

| 111          | Right-shift R-value by 4 (÷ 16).           |

| Application: | "Manual Ratio Modifier (R-Mod)" on page 16 |

### 8.3.2 Auxiliary Output Source Selection (AuxOutSrc[1:0])

Selects the source of the AUX\_OUT signal.

| AuxOutSrc[1:0] | Auxiliary Output Source       |

|----------------|-------------------------------|

| 00             | Reserved.                     |

| 01             | CLK_IN.                       |

| 10             | CLK_OUT.                      |

| 11             | PLL Lock Status Indicator.    |

| Application:   | "Auxiliary Output" on page 19 |

**Note:** When set to 11, *AuxLckCfg* sets the polarity and driver type ("AUX PLL Lock Output Configuration (AuxLockCfg)" on page 27).

#### 8.3.3 Enable Device Configuration Registers 1 (EnDevCfg1)

This bit, in conjunction with *EnDevCfg2* and *EnDevCfg3*, enables control port mode. All three bits must be set to 1 during initialization.

| EnDevCfg1    | Register State                                   |

|--------------|--------------------------------------------------|

| 0            | Disabled.                                        |

| 1            | Enabled.                                         |

| Application: | "SPI / I <sup>2</sup> C Control Port" on page 21 |

**Note:** EnDevCfg2 and EnDevCfg3 must also be set to enable control port mode ("SPI / I<sup>2</sup>C Control Port" on page 21).

## 8.4 Global Configuration (Address 05h)

| 7        | 6        | 5        | 4        | 3      | 2        | 1        | 0         |   |

|----------|----------|----------|----------|--------|----------|----------|-----------|---|

| Reserved | Reserved | Reserved | Reserved | Freeze | Reserved | Reserved | EnDevCfg2 | ! |

## 8.4.1 Device Configuration Freeze (Freeze)

Setting this bit allows writes to the Device Control and Device Configuration registers (address 02h - 04h) but keeps them from taking effect until this bit is cleared.

| FREEZE | Device Control and Configuration Registers                                                                                                                                  |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | Register changes take effect immediately.                                                                                                                                   |

| 11     | Modifications may be made to Device Control and Device Configuration registers (registers 02h-04h) without the changes taking effect until after the FREEZE bit is cleared. |

# 8.4.2 Enable Device Configuration Registers 2 (EnDevCfg2)

This bit, in conjunction with *EnDevCfg1* and *EnDevCfg3*, enables control port mode. All three bits must be set to 1 during initialization.

| EnDevCfg2    | Register State                                   |

|--------------|--------------------------------------------------|

| 0            | Disabled.                                        |

| 1            | Enabled.                                         |

| Application: | "SPI / I <sup>2</sup> C Control Port" on page 21 |

**Note:** EnDevCfg1 and EnDevCfg3 must also be set to enable control port mode ("SPI / I²C Control Port" on page 21).

#### 8.5 Ratio (Address 06h - 09h)

| 7      | 6 | 5 | 4 | 3 | 2 | 1 | 0      |

|--------|---|---|---|---|---|---|--------|

| MSB    |   |   |   |   |   |   | MSB-7  |

| MSB-8  |   |   |   |   |   |   | MSB-15 |

| LSB+15 |   |   |   |   |   |   | LSB+8  |

| LSB+7  |   |   |   |   |   |   | LSB    |

These registers contain the User Defined Ratio as shown in the "Register Quick Reference" section on page 23. These 4 registers form a single 32-bit ratio value as shown above. See "Output to Input Frequency Ratio Configuration" on page 15 and "Calculating the User Defined Ratio" on page 29 for more details.

### 8.6 Function Configuration 1 (Address 16h)

| _ | 7         | 6          | 5        | 4         | 3        | 2        | 1        | 0        |

|---|-----------|------------|----------|-----------|----------|----------|----------|----------|

|   | ClkSkipEn | AuxLockCfg | Reserved | EnDevCfg3 | Reserved | Reserved | Reserved | Reserved |

#### 8.6.1 Clock Skip Enable (ClkSkipEn)

This bit enables clock skipping mode for the PLL and allows the PLL to maintain lock even when the CLK IN has missing pulses.

| ClkSkipEn    | PLL Clock Skipping Mode           |  |  |  |

|--------------|-----------------------------------|--|--|--|

| 0            | Disabled.                         |  |  |  |

| 1            | Enabled.                          |  |  |  |

| Application: | "CLK_IN Skipping Mode" on page 13 |  |  |  |

**Note:**  $f_{CLK \ IN}$  must be < 80 kHz to use this feature.

# 8.6.2 AUX PLL Lock Output Configuration (AuxLockCfg)

When the AUX\_OUT pin is configured as a lock indicator (AuxOutSrc[1:0] = 11), this bit configures the AUX\_OUT driver to either push-pull or open drain. It also determines the polarity of the lock signal. If AUX\_OUT is configured as a clock output, the state of this bit is disregarded.

| AuxLockCfg   | AUX_OUT Driver Configuration                                                               |

|--------------|--------------------------------------------------------------------------------------------|

| 0            | Push-Pull, Active High (output 'high' for unlocked condition, 'low' for locked condition). |

| 1            | Open Drain, Active Low (output 'low' for unlocked condition, high-Z for locked condition). |

| Application: | "Auxiliary Output" on page 19                                                              |

**Note:** AUX\_OUT is an **un**lock indicator, signalling an error condition when the PLL is unlocked. Therefore, the pin polarity is defined relative to the **un**lock condition.

# 8.6.3 Enable Device Configuration Registers 3 (EnDevCfg3)

This bit, in conjunction with *EnDevCfg1* and *EnDevCfg2*, enables control port mode. All three bits must be set to 1 during initialization.

| EnDevCfg3    | Register State                                   |

|--------------|--------------------------------------------------|

| 0            | Disabled.                                        |

| 1            | Enabled.                                         |

| Application: | "SPI / I <sup>2</sup> C Control Port" on page 21 |

**Note:** EnDevCfg1 and EnDevCfg2 must also be set to enable control port mode ("SPI / I²C Control Port" on page 21).

# 8.7 Function Configuration 2 (Address 17h)

| 7        | 6        | 5        | 4         | 3          | 2        | 1        | 0        |

|----------|----------|----------|-----------|------------|----------|----------|----------|

| Reserved | Reserved | Reserved | ClkOutUnl | LFRatioCfg | Reserved | Reserved | Reserved |

#### 8.7.1 Enable PLL Clock Output on Unlock (ClkOutUnl)

Defines the state of the PLL output during the PLL unlock condition.

| ClkOutUnl    | Clock Output Enable Status                                                               |

|--------------|------------------------------------------------------------------------------------------|

| 0            | Clock outputs are driven 'low' when PLL is unlocked.                                     |

| 1            | Clock outputs are always enabled (results in unpredictable output when PLL is unlocked). |

| Application: | "PLL Clock Output" on page 19                                                            |

# 8.7.2 Low-Frequency Ratio Configuration (LFRatioCfg)

Determines how to interpret the 32-bit User Defined Ratio.

| LFRatioCfg   | Ratio Bit Encoding Interpretation     |  |  |  |

|--------------|---------------------------------------|--|--|--|

| 0            | 20.12 - High Multiplier.              |  |  |  |

| 1            | 12.20 - High Accuracy.                |  |  |  |

| Application: | "User Defined Ratio (RUD)" on page 15 |  |  |  |

#### 8.8 Function Configuration 3 (Address 1Eh)

| 7        | 6         | 5         | 4         | 3        | 2        | 1        | 0        |

|----------|-----------|-----------|-----------|----------|----------|----------|----------|

| Reserved | ClkIn_BW2 | ClkIn_BW1 | ClkIn_BW0 | Reserved | Reserved | Reserved | Reserved |

### 8.8.1 Clock Input Bandwidth (ClkIn\_BW[2:0])

Sets the minimum loop bandwidth when locked to CLK\_IN.

| ClkIn_BW[2:0] | Minimum Loop Bandwidth                                       |

|---------------|--------------------------------------------------------------|

| 000           | 1 Hz                                                         |

| 001           | 2 Hz                                                         |

| 010           | 4 Hz                                                         |

| 011           | 8 Hz                                                         |

| 100           | 16 Hz                                                        |

| 101           | 32 Hz                                                        |

| 110           | 64 Hz                                                        |

| 111           | 128 Hz                                                       |

| Application:  | "Adjusting the Minimum Loop Bandwidth for CLK_IN" on page 14 |

**Note:** In order to guarantee that a change in minimum bandwidth takes effect, these bits must be set prior to acquiring lock (removing and re-applying CLK\_IN can provide the unlock condition necessary to initiate the setting change). In production systems these bits should be configured with the desired values prior to setting the *EnDevCfg* bits; this guarantees that the setting takes effect prior to acquiring lock.

#### 9. CALCULATING THE USER DEFINED RATIO

**Note:** The software for use with the evaluation kit has built in tools to aid in calculating and converting the User Defined Ratio. This section is for those who are not interested in the software or who are developing their systems without the aid of the evaluation kit.

Most calculators do not interpret the fixed point binary representation which the CS2300 uses to define the output to input clock ratio (see Section 5.3.1 on page 15); However, with a simple conversion we can use these tools to generate a binary or hex value which can be written to the *Ratio* register.

#### 9.1 High Resolution 12.20 Format

To calculate the User Defined Ratio ( $R_{UD}$ ) to store in the register(s), divide the desired output clock frequency by the given input clock (CLK\_IN). Then multiply the desired ratio by the scaling factor of  $2^{20}$  to get the scaled decimal representation; then use the decimal to binary/hex conversion function on a calculator and write to the register. A few examples have been provided in Table 5.

| Desired Output to Input Clock Ratio (output clock/input clock) | Scaled Decimal Representation = (output clock/input clock) • 2 <sup>20</sup> | Hex Representation of<br>Binary R <sub>UD</sub> |  |

|----------------------------------------------------------------|------------------------------------------------------------------------------|-------------------------------------------------|--|

| 12.288 MHz/10 MHz=1.2288                                       | 1288490                                                                      | 00 13 A9 2A                                     |  |

| 11.2896 MHz/44.1 kHz=256                                       | 268435456                                                                    | 10 00 00 00                                     |  |

Table 5. Example 12.20 R-Values

#### 9.2 High Multiplication 20.12 Format

To calculate the User Defined Ratio (R<sub>UD</sub>) to store in the register(s), divide the desired output clock frequency by the given input clock (CLK\_IN). Then multiply the desired ratio by the scaling factor of 2<sup>12</sup> to get the scaled decimal representation; then use the decimal to binary/hex conversion function on a calculator and write to the register. A few examples have been provided in Table 6.

| Desired Output to Input Clock Ratio (output clock/input clock) | Scaled Decimal Representation = (output clock/input clock) ● 2 <sup>12</sup> | Hex Representation of<br>Binary R <sub>UD</sub> |  |

|----------------------------------------------------------------|------------------------------------------------------------------------------|-------------------------------------------------|--|

| 12.288 MHz/60 Hz=204,800                                       | 838860800                                                                    | 32 00 00 00                                     |  |

| 11.2896 MHz/59.97 Hz =188254.127                               | 771088904                                                                    | 2D F5 E2 08                                     |  |

Table 6. Example 20.12 R-Values

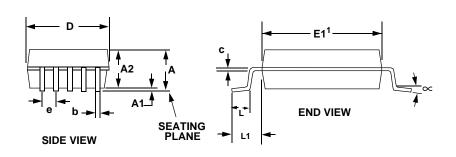

# **10.PACKAGE DIMENSIONS**

# 10L MSOP (3 mm BODY) PACKAGE DRAWING (Note 1)

|     | INCHES |            |        |      | NOTE     |      |      |

|-----|--------|------------|--------|------|----------|------|------|

| DIM | MIN    | NOM        | MAX    | MIN  | NOM      | MAX  |      |

| Α   |        |            | 0.0433 |      |          | 1.10 |      |

| A1  | 0      |            | 0.0059 | 0    |          | 0.15 |      |

| A2  | 0.0295 |            | 0.0374 | 0.75 |          | 0.95 |      |

| b   | 0.0059 |            | 0.0118 | 0.15 |          | 0.30 | 4, 5 |

| С   | 0.0031 |            | 0.0091 | 0.08 |          | 0.23 |      |

| D   |        | 0.1181 BSC |        |      | 3.00 BSC |      | 2    |

| Е   |        | 0.1929 BSC |        |      | 4.90 BSC |      |      |

| E1  |        | 0.1181 BSC |        |      | 3.00 BSC |      | 3    |

| е   |        | 0.0197 BSC |        |      | 0.50 BSC |      |      |

| L   | 0.0157 | 0.0236     | 0.0315 | 0.40 | 0.60     | 0.80 |      |

| L1  |        | 0.0374 REF |        |      | 0.95 REF |      |      |

Notes: 1. Reference document: JEDEC MO-187

- 2. D does not include mold flash or protrusions which is 0.15 mm max. per side.

- 3. E1 does not include inter-lead flash or protrusions which is 0.15 mm max per side.

- 4. Dimension b does not include a total allowable dambar protrusion of 0.08 mm max.

- 5. Exceptions to JEDEC dimension.

### THERMAL CHARACTERISTICS

| Parameter                             |               | Symbol            | Min | Тур | Max | Units |

|---------------------------------------|---------------|-------------------|-----|-----|-----|-------|

| Junction to Ambient Thermal Impedance | JEDEC 2-Layer | $\theta_{JA}$     | -   | 170 | -   | °C/W  |

|                                       | JEDEC 4-Layer | $\theta_{\sf JA}$ | -   | 100 | •   | °C/W  |

#### 11.ORDERING INFORMATION

| Product   | Description         | Package  | Pb-Free | Grade      | Temp Range    | Container        | Order#         |

|-----------|---------------------|----------|---------|------------|---------------|------------------|----------------|

| CS2300-CP | Clocking Device     | 10L-MSOP | Yes     |            | -10° to +70°C | Rail             | CS2300-CP-CZZ  |

| CS2300-CP | Clocking Device     | 10L-MSOP | Yes     | Commercial | -10° to +70°C | Tape and<br>Reel | CS2300-CP-CZZR |

| CDK2000   | Evaluation Platform | -        | Yes     | -          | -             | -                | CDK-2000-LCO   |

#### 12.REFERENCES

- 1. Audio Engineering Society AES-12id-2006: "AES Information Document for digital audio measurements Jitter performance specifications," May 2007.

- 2. Philips Semiconductor, "The I<sup>2</sup>C-Bus Specification: Version 2," Dec. 1998. http://www.semiconductors.philips.com

#### 13.REVISION HISTORY

| Release | Changes                                           |  |  |

|---------|---------------------------------------------------|--|--|

| A1      | Initial Release                                   |  |  |

| PP1     | Updated "AC Electrical Characteristics" on page 7 |  |  |

#### **Contacting Cirrus Logic Support**

For all product questions and inquiries, contact a Cirrus Logic Sales Representative.

To find one nearest you, go to www.cirrus.com

#### IMPORTANT NOTICE

"Preliminary" product information describes products that are in production, but for which full characterization data is not yet available.

Cirrus Logic, Inc. and its subsidiaries ("Cirrus") believe that the information contained in this document is accurate and reliable. However, the information is subject to change without notice and is provided "AS IS" without warranty of any kind (express or implied). Customers are advised to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, indemnification, and limitation of liability. No responsibility is assumed by Cirrus for the use of this information, including use of this information as the basis for manufacture or sale of any items, or for infringement of patents or other rights of third parties. This document is the property of Cirrus and by furnishing this information, Cirrus grants no license, express or implied under any patents, mask work rights, copyrights, trademarks, trade secrets or other intellectual property rights. Cirrus owns the copyrights associated with the information contained herein and gives consent for copies to be made of the information only for use within your organization with respect to Cirrus integrated circuits or other products of Cirrus. This consent does not extend to other copying such as copying for general distribution, advertising or promotional purposes, or for creating any work for resale.