# ISOFACE™

## ISO11813T

Isolated 8 Channel Digital Input with IEC61131-2 Type 1/2/3 Characteristics

# **Preliminary Data Sheet**

Revision 1.0, 2011-03-30

# Industrial & Multimarket

Edition 2011-03-30

Published by Infineon Technologies AG 81726 Munich, Germany © 2011 Infineon Technologies AG All Rights Reserved.

#### **Legal Disclaimer**

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

| ISO1181 | iT                                           |  |

|---------|----------------------------------------------|--|

| Revisio | History: 2011-03-30, V1.0                    |  |

| Previou | S Version:                                   |  |

| Page    | Subjects (major changes since last revision) |  |

|         | Preliminary Datasheet                        |  |

|         |                                              |  |

|         |                                              |  |

|         |                                              |  |

|         |                                              |  |

|         |                                              |  |

|         |                                              |  |

|         |                                              |  |

|         |                                              |  |

|         |                                              |  |

| <b>1</b><br>1.1<br>1.2<br>1.2.1<br>1.2.2                                                                                        | Pin Configuration and Functionality Pin Configuration Pin Functionality Pins of Sensor Interface Pins of Serial and Parallel logic Interface                                                                                                                                                                                                                                                      | PDS-8<br>PDS-10<br>PDS-10                                                                                |

|---------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| 2                                                                                                                               | Blockdiagram                                                                                                                                                                                                                                                                                                                                                                                      | PDS-13                                                                                                   |

| 3<br>3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.3<br>3.4<br>3.4.1<br>3.4.2<br>3.5<br>3.6<br>3.7<br>3.8<br>3.8.1<br>3.8.2<br>3.9 | Functional Description Introduction Power Supply Voltage Limits on VBB External Supply DC/DC Supply Internal Oscillator Sensor Input Input Type Select Wire Break Detection Common Error Output Programmable Digital Input Filter Parallel Interface Mode Serial Interface Mode SPI Modes Architecture of CRC-Engines SYNC Operation                                                              | PDS-14 PDS-14 PDS-15 PDS-16 PDS-20 PDS-21 PDS-21 PDS-23 PDS-24 PDS-26 PDS-27 PDS-29 PDS-29 PDS-30 PDS-34 |

| 4                                                                                                                               | Standard Compliance                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                          |

| <b>5</b><br>5.1<br>5.2<br>5.3<br>5.4                                                                                            | Electrical Characteristics Absolute Maximum Ratings Operating Conditions and Power Supply Electrical Characteristics Input Side Electrical Characteristics Microcontroller Interface                                                                                                                                                                                                              | PDS-37<br>PDS-38<br>PDS-40                                                                               |

| 6.1<br>6.2<br>6.2.1<br>6.2.2<br>6.2.3<br>6.3.1<br>6.3.2<br>6.3.3<br>6.3.4<br>6.3.5<br>6.3.6                                     | Registers of Microcontroller-Interface-Chip  µController Chip Registers Overview  Presentation of the Registers  Sensor Registers  Status Registers  Configuration Registers  µController Registers Description  Collective Diagnostics Register  Input Channel Data Register  Global Error Register  Filter Time of Channel 0-7 Register  Internal Error Register  Global Configuration Register | PDS-46<br>PDS-47<br>PDS-47<br>PDS-48<br>PDS-49<br>PDS-49<br>PDS-50<br>PDS-51<br>PDS-51                   |

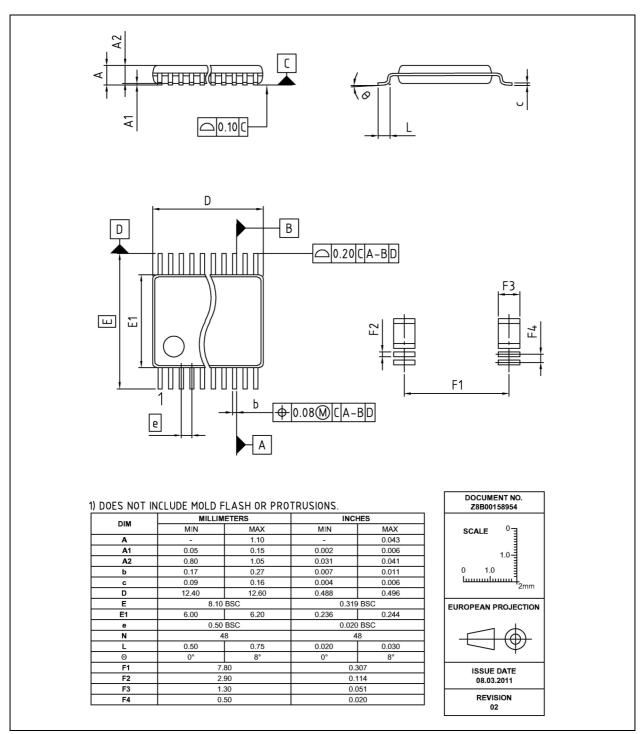

| 7                                                                                                                               | Package Outline                                                                                                                                                                                                                                                                                                                                                                                   | PDS-54                                                                                                   |

# Isolated 8 Channel Digital Input with IEC61131-2 Type 1/2/3 Characteristics

### **Product Highlights**

- Minimization of power dissipation due to constant current characteristic

- · Status LED output for each input

- Digital averaging of the input signals to suppress interference pulses

- Isolation between Input and Output using Coreless Transformer Technology

- Complete system integration (digital sensor or switch input, galvanic isolation and intelligent micro-controller or bus-ASIC interface

- 8-channel input according to IEC61131-2 (Type 1/2/3)

- Integrated galvanic isolation 500VAC (EN60664-1, UL508)

- 5/3.3V SPI and parallel micro-controller interface

- · Adjustable deglitching filters

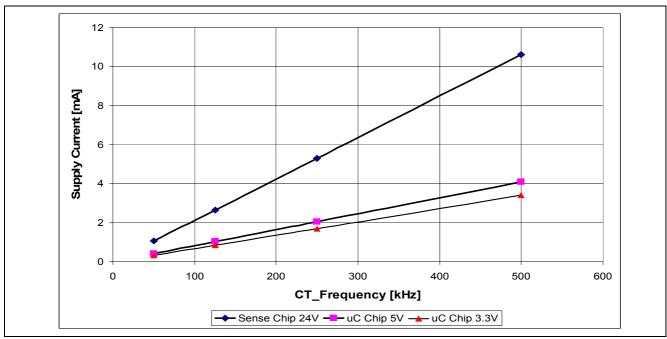

- Up to 500 kHz sampling frequency

- · Wire-break detection

- · Vbb under-voltage detection

- Package: TSSOP 8 x 12.5 mm

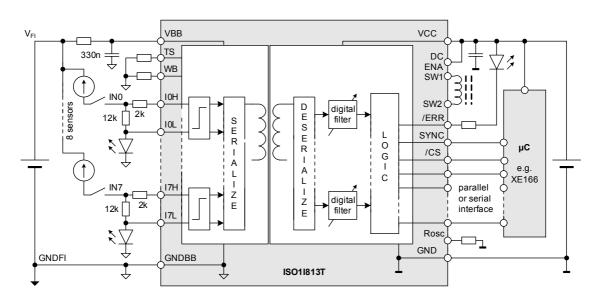

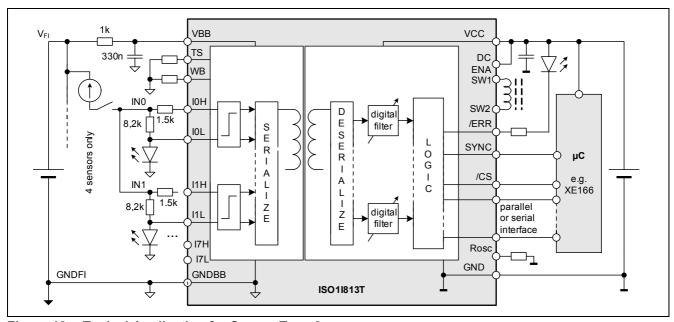

#### **Typical Application**

Programmable Logic Controllers(PLC)

Industrial PC

General Control Equipment

#### **Description**

The ISO1I813T is an electrically isolated 8 bit data input interface in TSSOP-48 package.

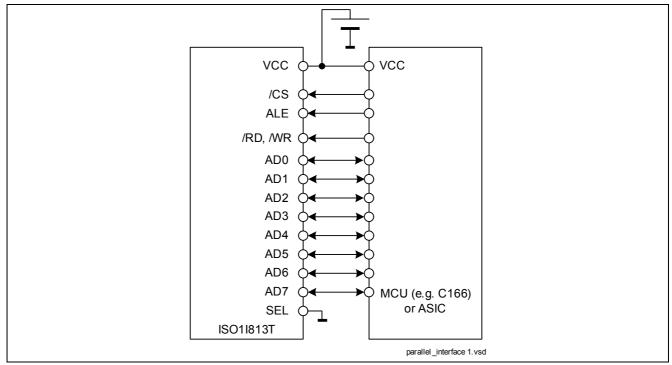

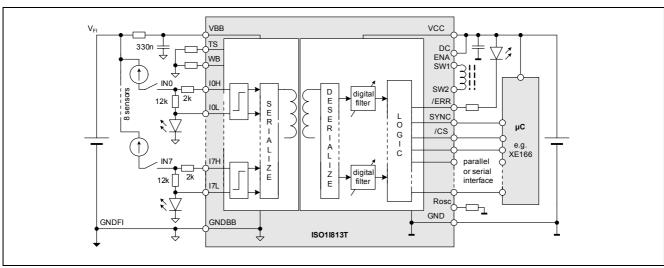

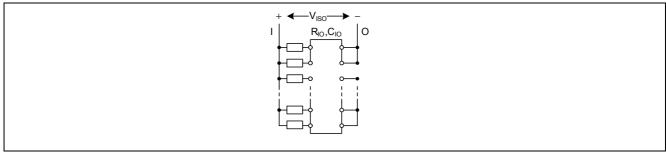

This part is used to detect the signal states of eight independent input lines according to IEC61131-2 Type 1/2/3 (e.g. two-wire proximity switches) with a common ground (GNDFI). For operating sensors of type 1/2/3 in accordance with IEC61131-2, it is necessary for the device to be wired with resistors  $R_V$  and  $R_{\text{FXT}}$  (it is recommended to use resistors with an accuracy of 2%, in any case < 5% - is mandatory, temperaturecoefficients < 200ppm are allowed). The figure below shows the typical application circuit for type 1/3. An 8 bit parallel µC compatible interface allows to connect the IC directly to a µC system. The input interface supports also a direct control mode and is designed to operate with 3.3/5V CMOS compatible levels. The data transfer from input to output side is realized by the integrated Coreless Transformer Technology.

Typical Application for Sensor of Type 1/3

### 1 Pin Configuration and Functionality

The pin configuration slightly differs for the parallel or the serial interfaces.

### 1.1 Pin Configuration

The ordering, type and functions of the IC pins are listed in the  ${\color{red}{\textbf{Table 1}}}.$

Table 1 Pin Configuration

| Pin  | Parallel Ir  | le   | Serial Interface Mode |                               |        |       |          |                       |

|------|--------------|------|-----------------------|-------------------------------|--------|-------|----------|-----------------------|

|      | Symbol       | Ctrl | Type                  | Function                      | Symbol | Ctrl. | Type     | Function              |

| ASIC | / Micro-con  | Í    | -                     | Pins                          |        |       |          |                       |

| 1    | GND          |      | A                     | Logic Ground                  | GND    |       |          |                       |

| 2    | SEL          | ı    | PD                    | Serial Parallel Mode Select   | SEL    |       |          |                       |

| 3    | SYNC         | I    | PU                    | Freeze Data & Diagnostics     | SYNC   |       |          |                       |

| 4    | Rosc         |      | Α                     | Clock Frequency Adjustment    | Rosc   |       |          |                       |

| 5    | VCC          |      | Α                     | Positive 5/3.3V logic supply  | VCC    |       |          |                       |

| 6    | ERR          | 0    | D,<br>PU              | Fault Indication output       | ERR    |       |          |                       |

| 7    | GND          |      | Α                     | Logic Ground                  | GND    |       |          |                       |

| 8    | AD0          | Ю    | PPZ                   | Data output bit0              | SDI    | I     | PD       | SPI Data input        |

| 9    | AD1          | Ю    | PPZ                   | Data output bit1              | SSO    | 0     | PPZ      | SPI Status output     |

| 10   | AD2          | Ю    | PPZ                   | Data output bit2              | GND    |       |          |                       |

| 11   | AD3          | Ю    | PPZ                   | Data output bit3              | GND    |       |          |                       |

| 12   | AD4          | Ю    | PPZ                   | Data output bit4              | CRCERR | 0     | D,<br>PU | CRC Error output      |

| 13   | AD5          | Ю    | PPZ                   | Data output bit5              | SCLK   | I     | PD       | SPI Shift Clock input |

| 14   | AD6          | Ю    | PPZ                   | Data output bit6              | SSI    | I     | PD       | SPI Status input      |

| 15   | AD7          | Ю    | PPZ                   | Data output bit7              | SDO    | 0     | PPZ      | SPI Data output       |

| 16   | CS           | I    | PU                    | Chip Select                   | CS     |       |          |                       |

| 17   | RD           | I    | PU                    | Data Read                     | n.c.   |       |          |                       |

| 18   | GND          |      | Α                     | Logic Ground                  | GND    |       |          |                       |

| 19   | WR           | I    | PU                    | Data Write                    | MS0    | I     | PD       | SPI Mode Select bit 0 |

| 20   | ALE          | I    | PD                    | Address Latch Enable          | MS1    | I     | PD       | SPI Mode Select bit 1 |

| 21   | DC_ENA       | I    | PD                    | DC-DC Supply Enable           | DC_ENA |       |          |                       |

| 22   | SW1          |      | Α                     | DC-DC Switch Output 1         | SW1    |       |          |                       |

| 23   | SW2          |      | Α                     | DC-DC Switch Output 2         | SW2    |       |          |                       |

| 24   | GND          |      | Α                     | Logic Ground                  | GND    |       |          |                       |

|      | or Side Pins | 5    | ı                     |                               | T      |       |          |                       |

| 25   | GNDBB        |      | Α                     | Input Ground                  | GNDBB  |       |          |                       |

| 26   | VBB          |      | Α                     | Positive input supply voltage | •      |       |          |                       |

| 27   | I0L          |      | Α                     | Input 0 Low, LED Out          | IOL    |       |          |                       |

| 28   | I0H          |      | Α                     | Input 0 High                  | IOH    |       |          |                       |

| 29   | I1L          |      | Α                     | Input 1 Low, LED Out          | I1L    |       |          |                       |

Table 1 Pin Configuration

| Pin | Parallel Interface Mode |      |                    |                          | Serial Interface Mode |       |      |          |  |

|-----|-------------------------|------|--------------------|--------------------------|-----------------------|-------|------|----------|--|

|     | Symbol                  | Ctrl | Type <sub>2)</sub> | Function                 | Symbol                | Ctrl. | Туре | Function |  |

| 30  | I1H                     |      | Α                  | Input 1 High             | I1H                   |       |      |          |  |

| 31  | GNDBB                   |      | Α                  | Input Ground             | GNDBB                 |       |      |          |  |

| 32  | I2L                     |      | Α                  | Input 2 Low, LED Out     | I2L                   |       |      |          |  |

| 33  | I2H                     |      | Α                  | Input 2 High             | I2H                   |       |      |          |  |

| 34  | I3L                     |      | Α                  | Input 3 Low, LED Out     | I3L                   |       |      |          |  |

| 35  | I3H                     |      | Α                  | Input 3 High             | I3H                   |       |      |          |  |

| 36  | TS                      |      | Α                  | Sensor Type 1/2/3 Select | TS                    |       |      |          |  |

| 37  | GNDBB                   |      | Α                  | Input Ground             | GNDBB                 |       |      |          |  |

| 38  | WB                      |      | Α                  | Wire Break Select        | t WB                  |       |      |          |  |

| 39  | I4L                     |      | Α                  | Input 4 Low, LED Out     | I4L                   | 14L   |      |          |  |

| 40  | I4H                     |      | Α                  | Input 4 High             | I4H                   |       |      |          |  |

| 41  | I5L                     |      | Α                  | Input 5 Low, LED Out     | I5L                   |       |      |          |  |

| 42  | I5H                     |      | Α                  | Input 5 High             | I5H                   |       |      |          |  |

| 43  | GNDBB                   |      | Α                  | Input Ground             | GNDBB                 |       |      |          |  |

| 44  | I6L                     |      | Α                  | Input 6 Low, LED Out     | I6L                   |       |      |          |  |

| 45  | 16H                     |      | Α                  | Input 6 High             |                       |       |      |          |  |

| 46  | I7L                     |      | Α                  | Input 7 Low, LED Out     | I7L                   |       |      |          |  |

| 47  | I7H                     |      | Α                  | Input 7 High             | I7H                   |       |      |          |  |

| 48  | GNDBB                   |      | Α                  | Input Ground             | GNDBB                 |       |      |          |  |

<sup>1)</sup> Direction of the pin: I = input, O = output, IO = Input/Output

<sup>2)</sup> Type of the pin: A = analog, D = Open-Drain, PU = internal Pull-Up resistor, PD = internal Pull-Down resistor, PPZ = Push-Pull pin with High-Impedance functionality

| GND   1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                      |                      |                     |               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------|---------------------|---------------|

| SYNC   3   46   17L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | GND 1 ()             | 48 GNDBB             | GND 1 O             | 48 GNDBB      |

| Rosc   4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | SEL 2                | 47 <u>17H</u>        | SEL 2               | 47 17H        |

| VCC   5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | SYNC 3               | 46 17L               | SYNC 3              | 46 17L        |

| Terr   6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Rosc 4               | 45 <u>I6H</u>        | Rosc 4              | 45 16H        |

| GND   7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | VCC 5                | 44 16L               | VCC 5               | 44   I6L      |

| ADD 8 41 15L SDI 8 41 15L SDI 8 41 15L ADI 9 40 14H SSO 9 40 14H SSO 9 40 14H ADI 10 39 14L GND 10 39 14L GND 10 39 14L GND 11 38 WB ADI 11 38 WB ADI 12 Pinout for parallel 37 GNDBB CREER 12 Pinout for serial 37 GNDBB CREER 13 Interface 36 TS SCIK 14 SCIK 15 INTERFACE 36 TS SCIK 15 INTERFACE 37 INTERFACE | /ERR 6               | 43 GNDBB             | /ERR 6              | 43 GNDBB      |

| AD1   9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | GND 7                | 42 I5H               | GND 7               | 42 15H        |

| ADZ   10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | AD0 8 4              | 41 15L               | SDI 8               | 41 I5L        |

| AD3 11 38 WB GND 11 38 WB CRCERR 12 Pinout for serial 37 CNDBB CRCERR 12 Pinout for serial 37 CNDBB CRCERR 13 Interface 36 TS SCLK 13 Interface 36 TS SCLK 13 Interface 36 TS SCLK 14 35 ISH SSI 14 35 ISH SSI 14 35 ISH SSI 14 SSI 14 SSI 15H | AD1 9                | 40 <u>14H</u>        | SSO 9               | 40 I4H        |

| ADA   12   Pinout for parallel   37   GNDBB   CRCERR   12   Pinout for serial   37   GNDBB   GRDBB   Interface   36   TS   SCIK   13   Interface   36   TS   SCIK   13   Interface   36   TS   SSI   14   35   I3H   SDO   15   34   I3L   SDO   15   34   I3L   SDO   15   34   I3L   SDO   15   34   I3L   SDO   15   SVIT   SVI   | AD2 10 3             | 39 <u>14L</u>        | GND 10              | 39 I4L        |

| AD5   13   Interface   36   TS     SCLK   13   Interface   36   TS   AD6   14   35   I3H   SSI   14   35   I3H   AD7   15   34   I3L   SDO   15   34   I3L   SDO   15   34   I3L   AD7   I7   32   I2L   Inc   17   32   I2L   Inc   17   32   I2L   Inc   I7   32   I2L   Inc   I7   I1   I1   I1   I1   I1   I1   I1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | AD3 11 3             | 38 WB                | GND 11              | 38 WB         |

| AD6 14 35 13H SSI 14 35 13H AD7 15 34 13L SDO 17 32 12L SDO 17 32 12L SDO 18 31 GNDBB GND 19 30 11H MSO 19 30 11H MSO 19 30 11H MSO 19 30 11H MSO 19 SDO 29 11L SDO 29 11L SW1 20 29 11L SW1 20 29 11L SW1 22 27 10L SW2 23 26 VBB GND 24 25 GNDBB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | i inout for paraller | GNDBB                | I illout for scriai | 37 GNDBB      |

| AD7 15 34 13L SDO 15 34 13L    (CS 16 33 12H    (RD 17 32 12L    (RD 18 31 GNDBB    (RD 19 30 I1H    (RD 19 30 IIH    (RD 19 30 I | AD5 13 Interface 3   | 36 TS                | SCLK 13 Interface   | 36 TS         |

| CS   16   33   12H     CS   16   33   12H     CS   16   33   12H     CS   16   17   32   12L     CS   16   17   32   12L     CS   16   CS   12H   CS   CS   CS   CS   CS   CS   CS   C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | AD6 14 3             | 35 <u>I3H</u>        | SSI 14              | 35 I3H        |

| RD         17         32         IZL         nc         17         32         IZL           GND         18         31         GNDBB         GND         18         31         GNDBB           MR         19         30         I1H         MSO         19         30         I1H           ALE         20         29         I1L         MS1         20         29         I1L           DC ENA         21         28         I0H         DC ENA         21         28         I0H           SW1         22         27         I0L         SW1         22         27         I0L           SW2         23         26         VBB         SW2         23         26         VBB           GND         24         25         GNDBB         GND         24         25         GNDBB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | AD7 15 3             | 34 13L               | SDO 15              | 34     3L     |

| GND 18 31 GNDBB GND 18 31 GNDBB 31 GNDBB 31 GNDBB 30 I1H MSO 19 30 I1H MSO 19 30 I1H MSO 19 30 I1H MSO 19 30 IIH MSO 19 29 IIL MSO 29 IIL MSO 29 IIL MSO 29 IIL MSO 20 20 IIL MSO 20 20 IIL MSO 20 20 III MSO 20 20  | /CS 16 3             | 33 <u>I2H</u>        | /CS 16              | 33 I2H        |

| MR     19     30     I1H     MSO     19     30     I1H       ALE     20     29     I1L     MS1     20     29     I1L       DC ENA     21     28     I0H     DC ENA     21     28     I0H       SW1     22     27     I0L     SW1     22     27     I0L       SW2     23     26     VBB     SW2     23     26     VBB       GND     24     25     GNDBB     GND     24     25     GNDBB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | /RD 17 3             | 32 <u>12L</u>        | nc 17               | 32   I2L      |

| ALE 20 29 I1L MS1 20 29 I1L  DC ENA 21 28 I0H DC ENA 21 28 I0H  SW1 22 27 I0L SW1 22 27 I0L  SW2 23 26 VBB SW2 23 26 VBB  GND 24 25 GNDBB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | GND 18 3             | 31 GNDBB             | GND 18              | 31 GNDBB      |

| DC ENA   21   28   IOH   DC ENA   21   28   IOH     SW1   22   27   IOL     SW2   23   26   VBB   SW2   23   26   VBB   SW2   24   25   GNDBB   GND   24   25   GNDBB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | WR 19 3              | 30 <u>I1H</u>        | MS0 19              | 30 I1H        |

| SW1         22         27         IOL         SW1         22         27         IOL           SW2         23         26         VBB         SW2         23         26         VBB           GND         24         25         GNDBB         GND         24         25         GNDBB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ALE 20 2             | 29 I1L               | MS1 20              | 29 I1L        |

| SW2     23     26     VBB     SW2     23     26     VBB       GND     24     25     GNDBB     GND     24     25     GNDBB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | DC ENA 21 2          | 28 10H               | DC ENA 21           | 28 <u>IOH</u> |

| GND 24 25 GNDBB GND 24 25 GNDBB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | SW1 22 2             | 27 10L               | SW1 22              | 27 IOL        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | SW2 23 2             | 26 VBB               | SW2 23              | 26 VBB        |

| n.c. = Not Connected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | GND 24 2             | 25 GNDBB             | GND 24              | 25 GNDBB      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      | n.c. = Not Connected |                     |               |

Figure 1 TSSOP-48 Pinout for Parallel and Serial Interface Modes

#### 1.2 Pin Functionality

#### 1.2.1 Pins of Sensor Interface

VBB (Positive supply 9.6-35V sensor supply)

VBB supplies the sensor input stage.

#### **GNDBB** (Ground for VBB domain)

This pin acts as the ground reference for the sensor input stage that is supplied by VBB.

#### I0H... I7H (Input channel 0 ... 7)

Sensor inputs with current sink characteristic according IEC61131-2 Type 1/2/3 which has been selected by pin TS

#### IOL... I7L (LED output channel 0 ... 7)

This pin provides the output signal to switch on the LED if the input voltage and current has been detected as "High" according to the selected Sensor Type.

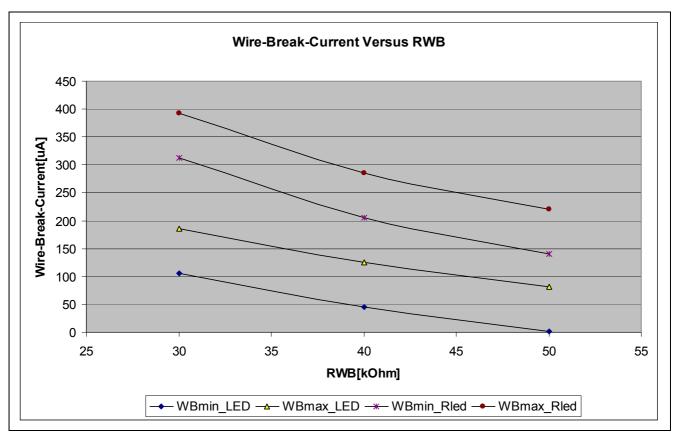

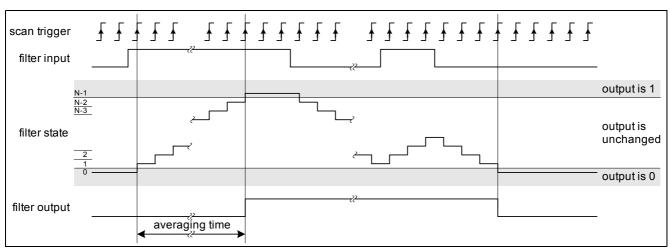

#### WB (Wire-Break Select)

By connecting a resistor between WB and GNDBB, the level for the Wire-Break detection can be adjusted (refer to **Table 10**). This pin is for static configuration (pin-strapping). The input voltage must not change during operation.

#### TS (Type Select)

By connecting a resistor between TS and GNDBB the sensor type (Type 1/2/3) can be selected (refer to **Table 10** for corresponding resistor value). This pin is for static configuration (pin-strapping). The input voltage must not change during operation.

### 1.2.2 Pins of Serial and Parallel logic Interface

Some pins are common for both interface types, some others are specific for the parallel or serial access.

#### VCC (Positive 3.3/5V logic supply)

VCC supplies the output interface that is electrically isolated from the sensor input stage. The interface can be supplied with 3.3/5V.

#### **GND (Ground for VCC domain)**

This pin acts as the ground reference for the uC-interface that is supplied by VCC.

#### **Rosc (Clock Adjustment)**

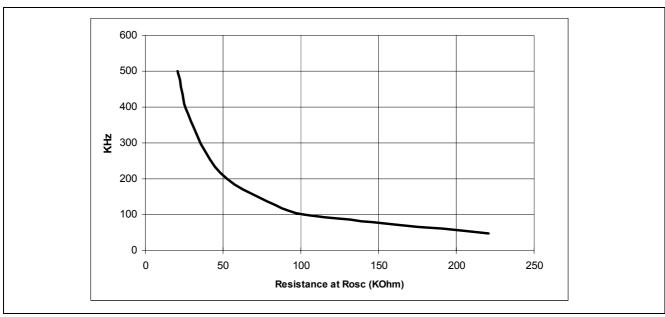

A high precision resistor has to be connected between Rosc and GND to set the frequency of the sampling clock.

#### DC\_ENA (DC-DC Converter Enable)

When the DC\_ENA pin is connected to VCC, the internal DC-DC driver is activated. When DC\_ENA is in the state Low, the switches are not driven. The input voltage must not change during operation. This pin has an internal Pull-Down resistor.

#### SW1, SW2 (DC-DC switch outputs 1/2)

When the DC\_ENA pin is connected to VCC, the outputs SW1 and SW2 switch at the clock-frequency determined by the resistor at Rosc to supply the external push-pull converter. The switching frequency can be divided by two by setting the responsible bit in the GLCFG register (see also section 6). Both outputs provide an open drain functionality.

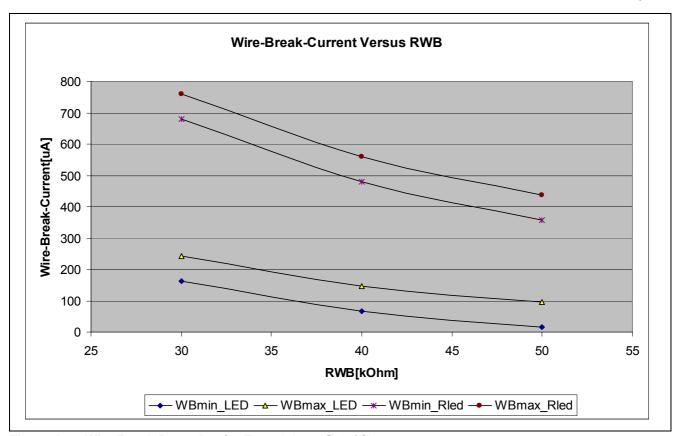

#### ERR (Error)

The low active ERR signal contains the OR-wired information of the sensor input undervoltage and missing voltage detection, the internal data transmission failure detection unit and the overcurrent fault of the DC-DC-converter. The output pin  $\overline{\mathsf{ERR}}$  provides an open drain functionality. During Start Up this pin is pulled to High state. This pin has an internal Pull-Up resistor. In normal operation the signal  $\overline{\mathsf{ERR}}$  is high. See Section 3.5 for more details.

#### **SEL (Serial or Parallel Mode Select)**

When this pin is in a logic Low state, the IC operates in Parallel Mode. For Serial Mode operation the pin has to be pulled in logic High state. During Start Up the IC is operating in Parallel Mode. This pin has an internal Pull-Down resistor. This pin must not change during operation.

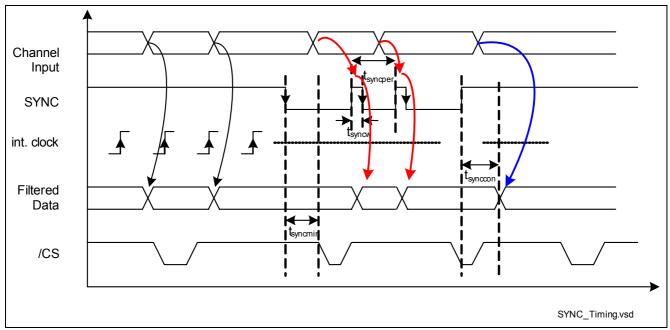

#### SYNC

When this pin is in a logic High state, the IC operates in continuous mode with the internal sampling clock. In isochronous mode, the internal data and diagnostics registers are synchronized on each falling edge detected at SYNC. In logic low state the internal data and diagnostic registers are not updated. During Start-Up this pin is pulled to high state. This pin has an internal Pull-Up resistor. (see also Section 3.9

#### **CS (Chip Select)**

When this pin is in a logic Low state, the IC interface is enabled and data can be transferred. This pin has an internal Pull-Up resistor.

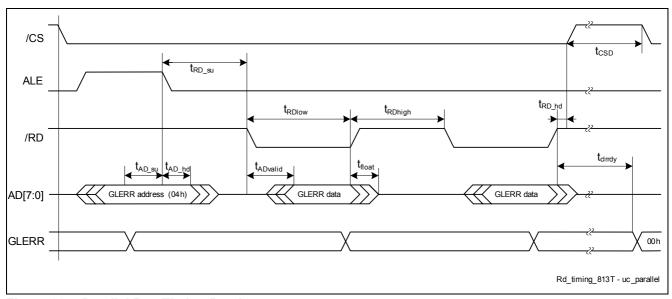

#### The following pins are provided in the parallel interface mode

#### AD7:AD0 (AddressData input / output bit7 ... bit0)

The pins AD0 .. AD7 are the bidirectional input / outputs for data write and read. Depending on the state of the ALE, RD, WR pins, register addresses or data can be transferred between the internal registers and e.g. the microcontroller.

#### RD, WR (Read / Write)

By pulling one of these pins down, a read or write transaction is initiated on the AddressData bus and the data becomes valid. These pins have internal Pull-Up resistors.

#### **ALE (Address Latch Enable)**

The pin ALE is used to select between address (ALE is in a logic High state) or data (ALE is in a logic Low state). When ALE is pulled high, addresses are transferred and latched over the bit AD0 to AD7. During the Low State of ALE all read or write transactions hit the same address. This pin has an internal Pull-Down resistor.

#### The following pins are provided in the serial interface mode

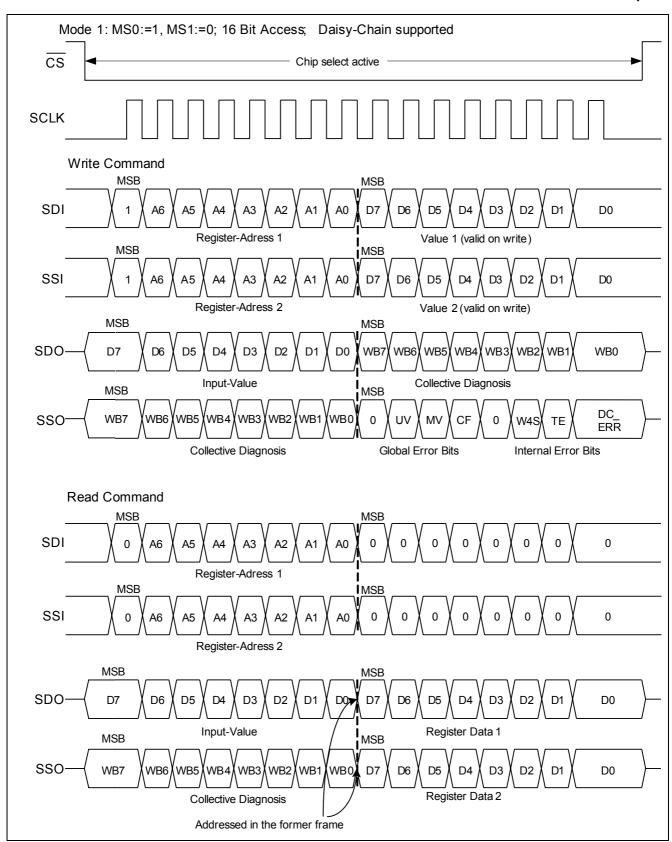

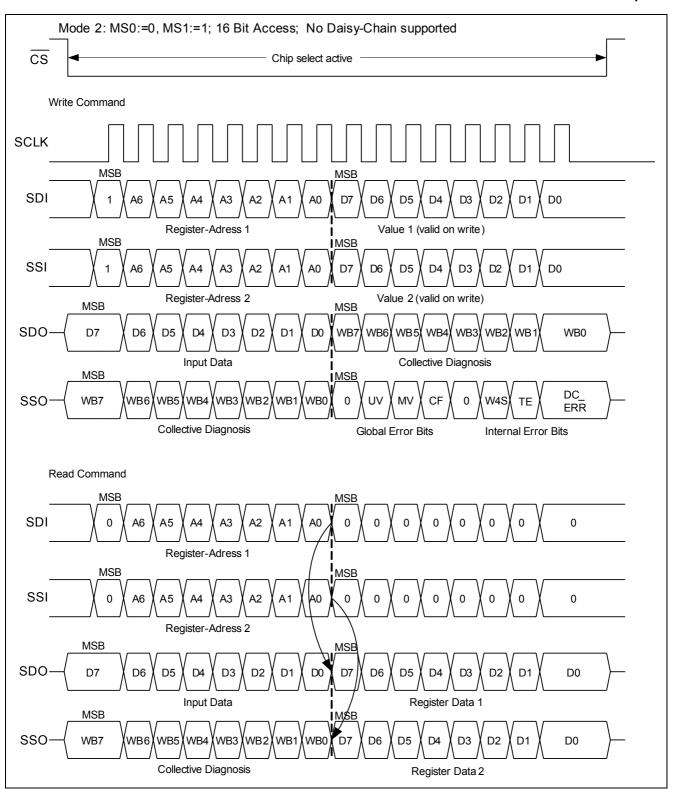

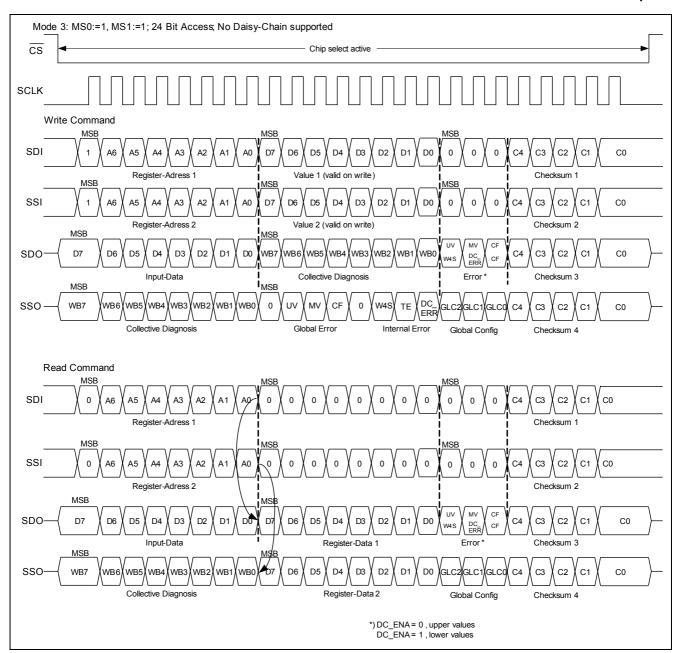

#### MS0, MS1 (Serial Mode Select)

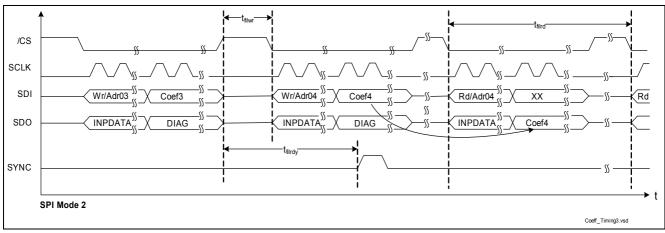

By driving these pins to Logic High or Low the Serial Interface Mode can be selected. These pins have internal Pull-Down resistors. The mode of the Serial Interface can be changed during operation.

#### SCLK (Serial interface shift clock)

Input data are sampled with the rising edge and output data are updated with the falling edge of this input clock signal. This pin has an internal Pull-Down resistor.

#### SDI, SSI (Serial interface data/status input )

SDI/SSI data is put into a dedicated FIFO to program the filtering time and mask the Wire-Break diagnostic bits of each channel (SPI Mode 2 and 3) or to program register adresses the contents of which to be read subsequently. This pin has an internal Pull-Down resistor.

#### SDO, SSO (Serial interface data/status outputs)

SDO provides typically the sensor data bits, SSO provides the sensor diagnostic bits.

#### **CRCERR (CRC Error output)**

This pin is in a logic Low state when CRC errors or Shift-Clock errors are detected internally. This pin has an internal Pull-Up resistor.

Preliminary Data Sheet 12 V1.0, 2011-03-xx

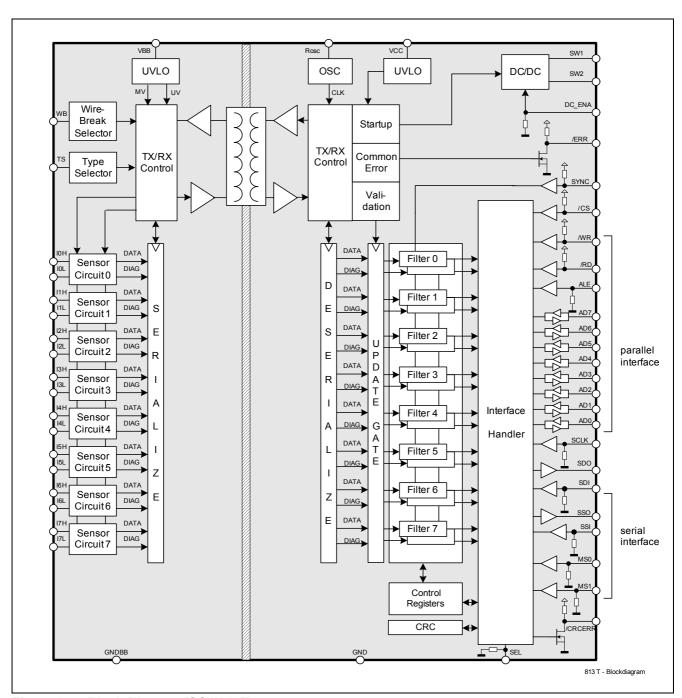

#### **Blockdiagram**

### 2 Blockdiagram

Figure 2 Block Diagram ISO1I813T

### 3 Functional Description

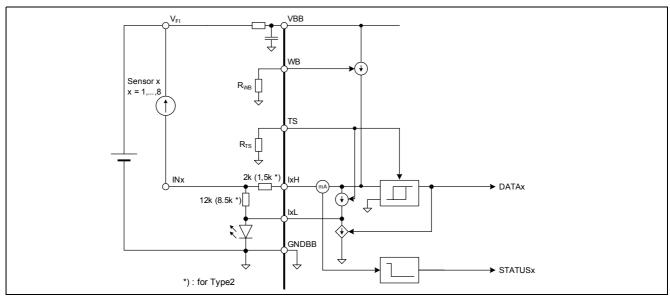

The ISO1I813T is an electrically isolated 8 bit data input interface. This part is used to detect the signal states of eight independent input lines according to IEC61131-2 Type 1/2/3 (e.g. two-wire proximity switches) with a common ground (GNDBB).

#### 3.1 Introduction

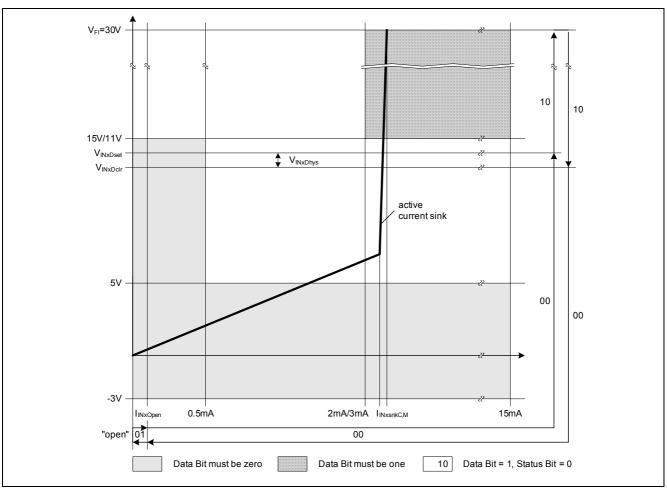

The current in the input circuit is determined by the switching element in state "0" and by characteristics of the input stage in state "1".

The octal input device is intended for a configuration comprising two specified external resistors per channel, as shown in the block diagram. As a result the power dissipation within the package is at a minimum.

The voltage dependent current through the external resistor  $R_{\text{EXT}}$  is compensated by a negative differential resistance of the current sink across pins IxH and IxL, therefore input INx behaves like a constant current sink.

The comparator assigns level 1 or 0 to the voltage present at input I. To improve interference protection, the comparator is provided with hysteresis. A status LED is connected in series with the input circuit ( $R_{\text{EXT}}$  and current sink).

If no LED is used an external resistor of 2  $k\Omega$  has to be connected between IxL and GNDBB. The specified switching thresholds may change if the LED is replaced by a resistor.

The LED drive short-circuits the status LED if the comparator detects "0". A constant current sink in parallel with the LED reduces the operating current of the LED, and a voltage limiter ensures that the input circuit remains operational if the LED is interrupted but the switching thresholds may change.

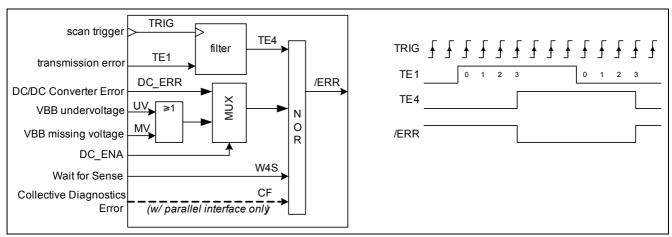

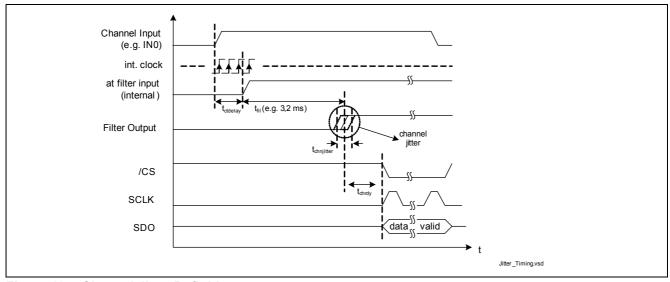

For each channel an adjustable digital filter is provided which samples the comparator signal at a rate configured by programming internal registers. The digital filter is designed to provide averaging characteristics. If the input value remains the same for the selected number of sampling values than, the output changes to the corresponding state.

The  $\mu$ C compatible interfaces allow a direct connection to the ports of a microcontroller without the need for other components. The diagnostic logic on the chip monitors the internal data transfer as well as the sensor input supply. The information is send via the internal coreless transformer to the pin  $\overline{\text{ERR}}$  at the input interface

#### 3.2 Power Supply

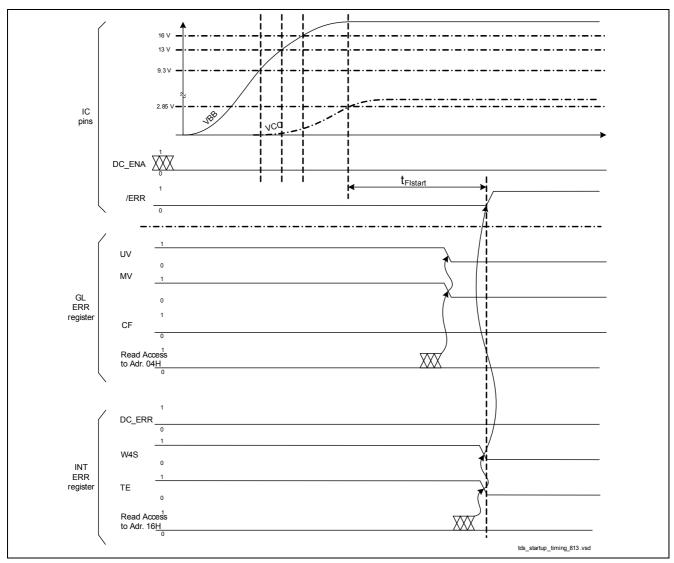

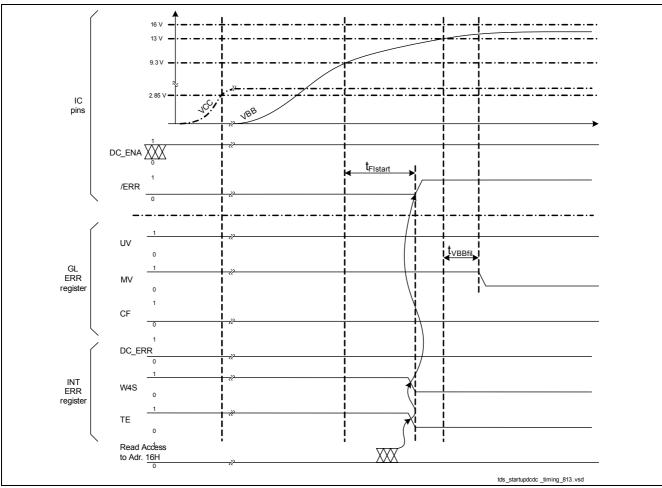

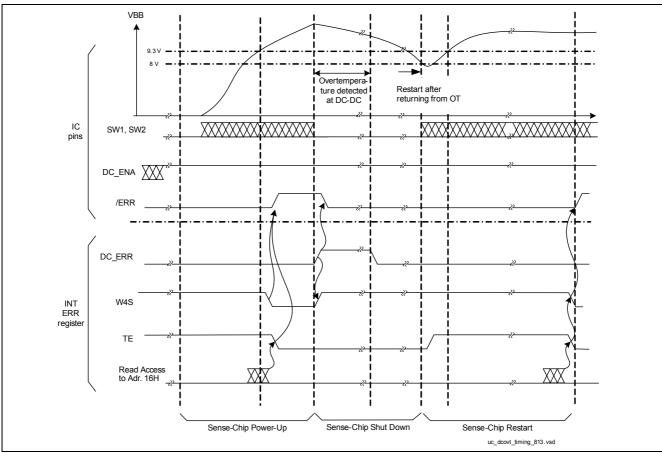

The IC contains 2 electrically isolated voltage domains that are independent from each other. The microcontroller interface is supplied via pin VCC, GND and the input stage is supplied via pin VBB, GNDBB. The different voltage domains can be switched on at different time. **Figure 4** shows the Start Up behaviour if both voltage domains are powered by an external power supply. If the VCC and VBB voltage have reached their operating range and the internal data transmission has been started successfully, the IC indicates the end of the Start Up procedure by setting the pin  $\overline{\text{ERR}}$  to logic high. In the situation of a supply voltage drop at VBB on the Sense Side - even short - the Sense Chip requires a proper restart and therefore the  $\mu$ Controller Side control unit needs to react accordingly, especially to guarantee the integrity of the sensor data provided to the filter stage.

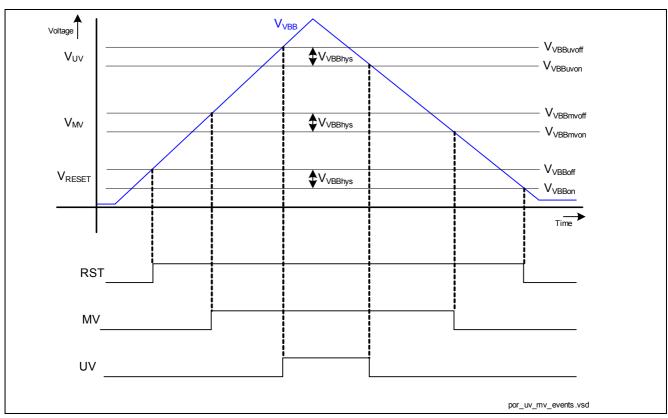

### 3.2.1 Voltage Limits on VBB

Figure 3 Start Up Procedure with external Power Supply

During UVLO, all registers are reset to their reset values as specified in the **Chapter 6.2**. As a result, the flags TE, UV as well as MV are High and the ERR pin is Low (error condition). Immediately after the reset is released, the chip is first configured by "reading" the logic level of the SEL, MS1, MS0 (when available). The IC powers up as a parallel device i.e. the AD0-7 pins are high-impedance until the IC configuration is over.

The supply voltage VBB is monitored during operation by two internal comparators (with typ. 8  $\mu$ s blanking time @ 500kHz f<sub>scantyp</sub>) detecting:

- VBB Undervoltage: If the voltage drops below the UV threshold (see Table 7), the UV-bit in the GLERR register is set High. The IC operates normally.

- VBB Missing Voltage: If the voltage further drops below the MV threshold, lower than the previous threshold, the MV-bit in the GLERR register is set, the Sense Side of the IC is turned off when reaching the V<sub>RESET</sub> threshold whereas the Micro-Controller Side remains active.

These 2 thresholds are inactive when the IC operates in Self Power Mode i.e. when the DC\_ENA pin is High.

Note: In case DC\_ENA ist high the integrated DC/DC driver is active. The driver stage is self-protected in overload condition: the internal switches will be turned off as long as the overcurrent condition is detected and the IC will automatically restart once the overload condition disappears.

Important: Since the UV and MV (as well as the TE and W4S) bits used for generating the  $\overline{ERR}$  signal are preset to High during UVLO, the  $\overline{ERR}$  pin is Low after power up. Therefore the  $\overline{ERR}$  signal requires to be explicitly cleared after power up. At least one read access to the GLERR and INTERR registers is needed to update those status bits and thus release the  $\overline{ERR}$  pin.

### 3.2.2 External Supply

**Figure 4** shows the Start Up behaviour if both voltage domains are powered by an external power supply. If the VCC and VBB voltage have reached their operating range and the internal data transmission has been started successfully, the IC indicates the end of the Start Up procedure by setting the pin ERR to logic high

Figure 4 Start Up Procedure with external Power Supply

### 3.2.3 DC/DC Supply

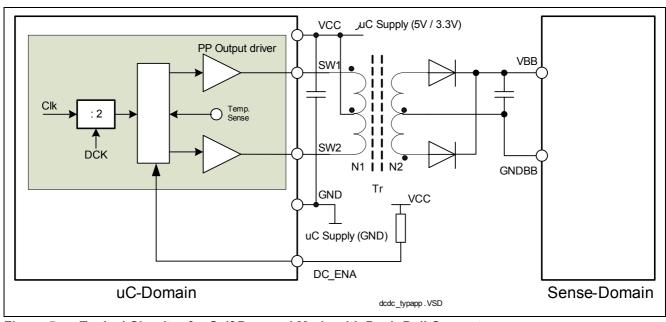

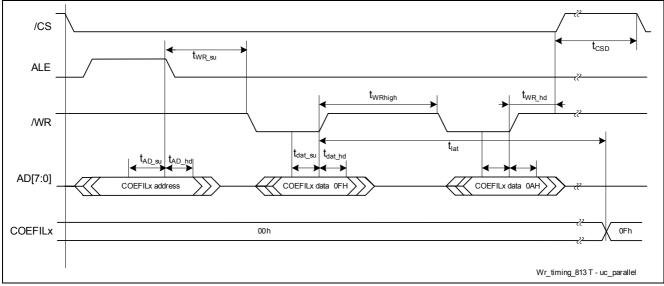

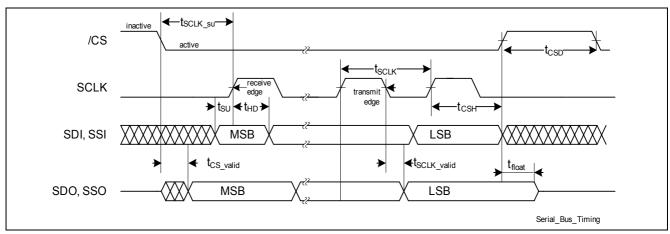

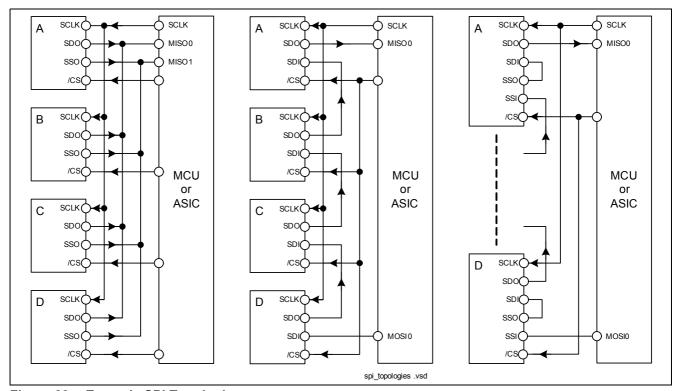

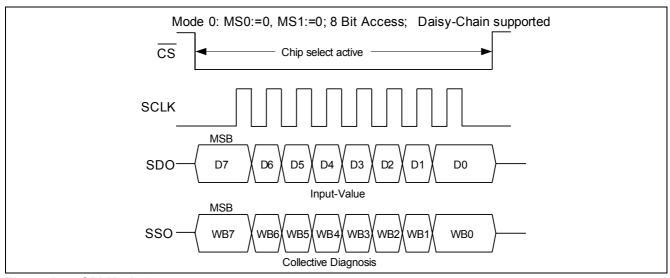

Figure 5 Typical Circuitry for Self Powered Mode with Push-Pull Converter