www.ti.com

SLVS953A-JUNE 2009-REVISED JUNE 2009

# 2-CHANNEL ESD SOLUTION FOR HIGH-SPEED (6 GBPS) DIFFERENTIAL INTERFACE

#### **FEATURES**

- 0.05-pF Matching Capacitance Between the Differential Signal Pair

- Single-Pair Differential Lines to Protect the Differential Data and Clock Lines of the LVDS, SATA, Ethernet, or USB High-Speed (HS) Interface

- Flow-Through Pin Mapping for the High-Speed Lines Ensures Zero Additional Skew Due to Board Layout While Placing ESD-Protection Chip Near the Connector

- Supports Data Rates in Excess of 6 Gbps

- ESD Protection Meets or Exceeds IEC61000-4-2 (Level 4)

- 5-A Peak Pulse Current (8/20 µs Pulse) for V<sub>BUS</sub> and D+, D-, and ID Lines

- Industrial Temperature Range: -40°C to 85°C

- Multiple Space-Saving Package Options

#### **APPLICATIONS**

- Notebooks

- Set-Top Boxes

- DVD Players

- Media Players

- Portable Computers

# DBZ/DRT PACKAGE (TOP VIEW) D+ 1 3 GND D-2 DRY PACKAGE (TOP VIEW) N.C. 1 6 D+ GND 2 5 V<sub>CC</sub> N.C. 3 4 D-

N.C. - No internal connection

#### DESCRIPTION/ORDERING INFORMATION

The TPD2E009 provides 2 ESD clamp circuits with flow-through pin mapping for ease of board layout. This device has been designed to protect sensitive components which are connected to ultra high-speed data and transmission lines. The TPD2E009 offers protection from stress caused by ESD (electrostatic discharge). This device also offers 5 A (8/20 µs) peak pulse current ratings per IEC 61000-4-5 (lightning) specification.

The monolithic silicon technology allows matching between the differential signal pairs. The less than differential 0.05-pF capacitance ensures that the differential signal distortion due to added ESD clamp remains minimal. The 0.7-pF line capacitance is suitable for high-speed data rate (in excess of 6 Gbps).

The TPD2E009 conforms to IEC61000-4-2 (Level 4) ESD protection. The DRT (1 mm  $\times$  1 mm) package is offered for space-saving portable applications. The industry standard DBZ (2.4 mm  $\times$  2.9 mm) package offers additional flexibility in the board layout for the system designer.

The TPD2E009 is characterized for operation over ambient air temperature range of -40°C to 85°C.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

#### **ORDERING INFORMATION**

| T <sub>A</sub> | PACKA     | GE <sup>(1)(2)</sup> | ORDERABLE PART NUMBER | TOP-SIDE MARKING |  |  |

|----------------|-----------|----------------------|-----------------------|------------------|--|--|

|                | SON - DRY | Tape and reel        | TPD2E009DRYR          | PREVIEW          |  |  |

| -40°C to 85°C  | SOP – DBZ | Tape and reel        | TPD2E009DBZR          | NFLR             |  |  |

|                | SOT- DRT  | Tape and reel        | TPD2E009DRTR          | 4T               |  |  |

- (1) Package drawings, thermal data, and symbolization are available at www.ti.com/packaging.

(2) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI website at www.ti.com.

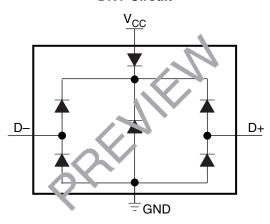

#### **CIRCUIT DIAGRAMS**

#### **DRY Circuit**

#### **DBZ/DRT Circuit**

#### **TERMINAL FUNCTIONS**

| TERMINAL        |                                               |      |          |                                                                                         |  |  |  |  |

|-----------------|-----------------------------------------------|------|----------|-----------------------------------------------------------------------------------------|--|--|--|--|

| NAME            | DBZ/DRT DRY <sup>(1)</sup><br>PIN NO. PIN NO. |      | TYPE     | DESCRIPTION                                                                             |  |  |  |  |

| D+, D-          | 1, 2                                          | 4, 6 | ESD port | High-speed ESD clamp, provides ESD protection to the high-speed differential data lines |  |  |  |  |

| V <sub>CC</sub> | _                                             | 5    | Supply   | Power supply                                                                            |  |  |  |  |

| GND             | 3                                             | 3    | GND      | Ground                                                                                  |  |  |  |  |

(1) Product Preview

www.ti.com

## **ABSOLUTE MAXIMUM RATINGS**(1)

over operating free-air temperature range (unless otherwise noted)

|                  |                                          |                                 |             | MIN | MAX | UNIT |

|------------------|------------------------------------------|---------------------------------|-------------|-----|-----|------|

|                  | IO voltage tolerance                     | D+, D- pins                     | 0           | 6   |     |      |

| T <sub>A</sub>   | Operating free-air temperate             |                                 | -40         | 85  | °C  |      |

| T <sub>stg</sub> | Storage temperature range                |                                 |             | -65 | 125 | °C   |

|                  | ESD protection                           | IEC 61000-4-2 Contact Discharge | D+, D- pins |     | ±8  | kV   |

|                  | ESD protection                           | IEC 61000-4-2 Air-Gap Discharge | D+, D- pins |     | ±8  | kV   |

|                  | Peak pulse current (t <sub>p</sub> = 8/2 | D+, D- pins                     |             | 5   | Α   |      |

|                  | Peak pulse power (t <sub>p</sub> = 8/20  | μs)                             | D+, D- pins |     | 45  | W    |

<sup>(1)</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum-rated conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

over operating free-air temperature range (unless otherwise noted)

|                  | PARAMETER                           | TEST CO                                          | TEST CONDITIONS                             |     |      |      | UNIT |

|------------------|-------------------------------------|--------------------------------------------------|---------------------------------------------|-----|------|------|------|

| $V_{RWM}$        | Reverse stand-off voltage           | D+,D- pins to ground                             |                                             |     |      | 5.5  | V    |

| $V_{clamp}$      | Clamp voltage                       | D+,D- pins to ground,                            | I <sub>IO</sub> = 1 A                       |     |      | 8    | V    |

| I <sub>IO</sub>  | Current from IO port to supply pins | $V_{IO} = 2.5 \text{ V}, I_D = 8 \text{ mA}$     |                                             |     | 0.01 | 0.1  | μΑ   |

|                  | Diode forward voltage               | D+,D- pins,<br>lower clamp diode,                | 0.6                                         | 0.8 | 0.95 |      |      |

| V <sub>D</sub>   |                                     | D+,D- pins,<br>upper clamp diode,<br>DRY package | $V_{CC} = 0 \text{ V}, I_D = -8 \text{ mA}$ | 0.6 | 0.8  | 0.95 | V    |

| R <sub>dyn</sub> | Dynamic resistance                  | D+,D- pins,                                      | I = 1 A                                     |     | 1    |      | Ω    |

|                  | IO conscitones                      | D+,D- pins, DBZ<br>Package                       | V <sub>IO</sub> = 2.5 V                     |     | 0.9  |      | pF   |

| C <sub>IO</sub>  | IO capacitance                      | D+,D- pins, DRT<br>Package                       | V <sub>IO</sub> = 2.5 V                     |     | 0.7  |      | pF   |

| $V_{BR}$         | Break-down voltage                  | I <sub>IO</sub> = 1 mA                           |                                             | 7   |      |      | V    |

Product Folder Link(s): TPD2E009

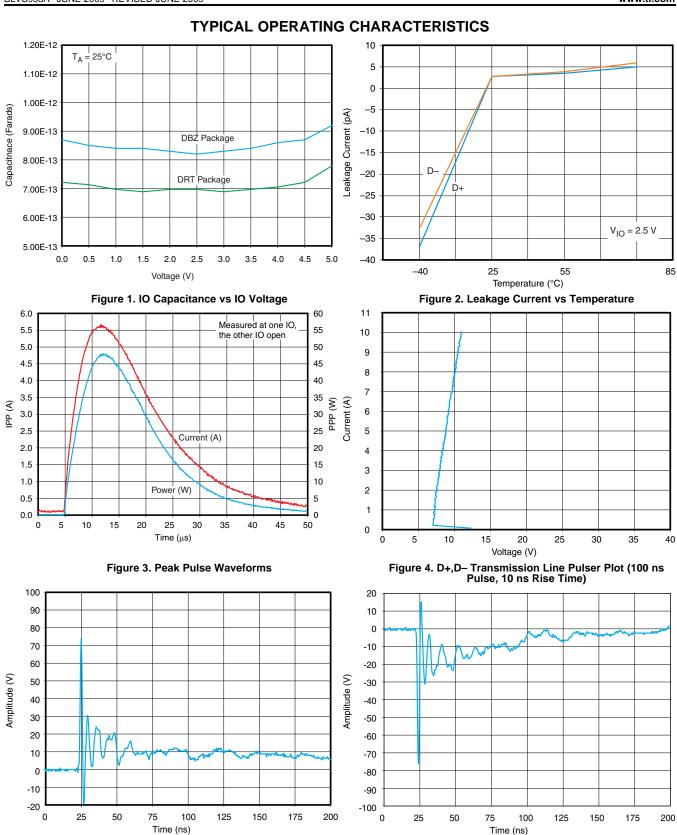

Figure 5. IEC Clamping Waveforms (8 kV Contact)

Figure 6. IEC Clamping Waveforms (-8 kV Contact)

13 May 09 15:21:32

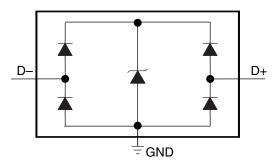

## TYPICAL OPERATING CHARACTERISTICS (continued)

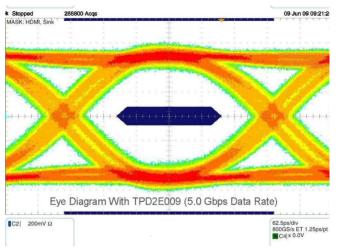

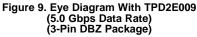

MASK: HDMI, Sink

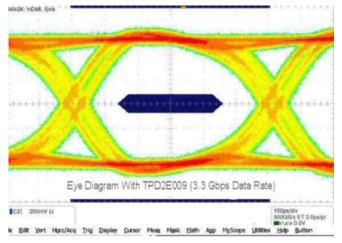

# **Eye Diagrams**

Eye Diagram Without TPD2E009 (3.3 Gbps Data Rate)

Figure 7. Eye Diagram With TPD2E009 (3.3 Gbps Data Rate) (3-Pin DBZ Package)

Figure 8. Eye Diagram Without TPD2E009 (3.3 Gbps Data Rate) (3-Pin DBZ Package)

Figure 10. Eye Diagram Without TPD2E009 (5.0 Gbps Data Rate) (3-Pin DBZ Package)

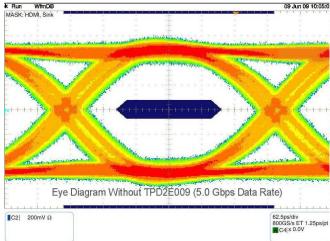

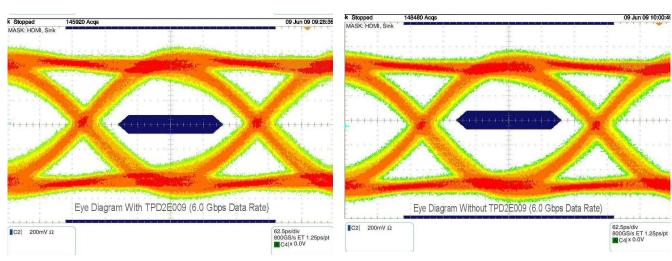

# **TYPICAL OPERATING CHARACTERISTICS (continued)**

Figure 11. Eye Diagram With TPD2E009 (6.0 Gbps Data Rate) (3-Pin DBZ Package)

Figure 12. Eye Diagram Without TPD2E009 (6.0 Gbps Data Rate) (3-Pin DBZ Package)

Submit Documentation Feedback

#### **APPLICATION INFORMATION**

## **Typical Application**

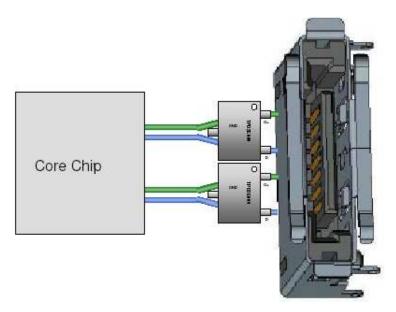

Figure 13. TPD2E009 in Differential eSATA Interface

Figure 13 shows the board layout scheme for the D+/D- lines of a single differential pair. It allows the differential signal pairs couple together right after they touch the ESD ports (pin 1 and pin 2) of the TPD2E009.

#### **Designing with High-Speed Differential Signals**

Layout considerations, such as package selection, trace routing, etc. must be taken into account while designing the ESD clamp circuit for high-speed interface. Difficult routing can lead the designer to use vias or stubs in the board traces, creating significant disruption in the line impedance in the high-speed signal path. Poor package choice can force designer to route differential traces with unequal lengths and add the skew in the signals. It is recommended to closely couple the differential traces to reduce the EMI interference.

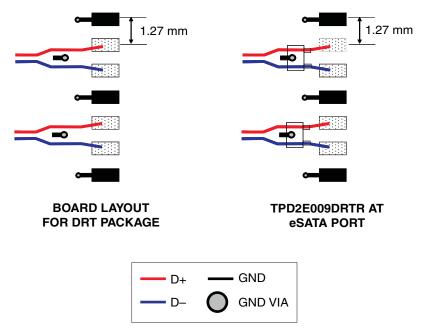

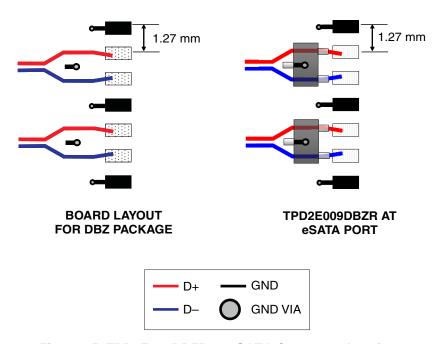

The TPD2E009 can provide system level ESD protection to the high-speed differential ports (>6 Gbps data rate). The flow-through package offers flexibility for board routing with traces up to 15 mills wide. Figure 14 and Figure 15 show the board layout scheme for the D+/D- lines of a single differential pair. It allows the differential signal pairs couple together right after they touch the ESD ports (pin 1 and pin 2) of the TPD2E009.

Copyright © 2009, Texas Instruments Incorporated

Submit Documentation Feedback

Figure 14. TPD2E009DRTR at eSATA Connector Interface

Figure 15. TPD2E009DBZR at eSATA Connector Interface

Submit Documentation Feedback

# PACKAGE MATERIALS INFORMATION

www.ti.com 7-Aug-2009

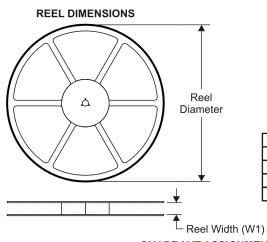

# TAPE AND REEL INFORMATION

# TAPE DIMENSIONS KO P1 BO W Cavity A0

|    | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

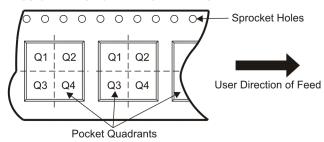

# QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device       | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TPD2E009DBZR | SOT-23          | DBZ                | 3 | 3000 | 180.0                    | 9.2                      | 3.18       | 3.28       | 1.32       | 4.0        | 8.0       | Q3               |

| TPD2E009DRTR | SOT             | DRT                | 3 | 3000 | 180.0                    | 8.4                      | 1.16       | 1.16       | 0.63       | 4.0        | 8.0       | Q3               |

www.ti.com 7-Aug-2009

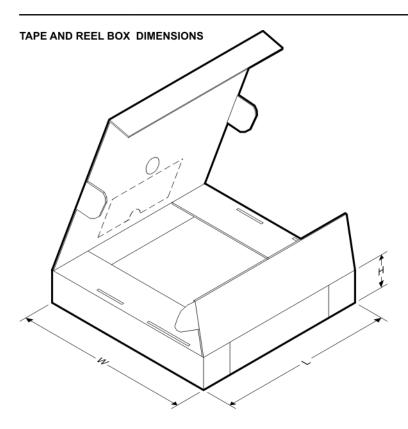

#### \*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPD2E009DBZR | SOT-23       | DBZ             | 3    | 3000 | 202.0       | 201.0      | 28.0        |

| TPD2E009DRTR | SOT          | DRT             | 3    | 3000 | 180.0       | 180.0      | 85.0        |

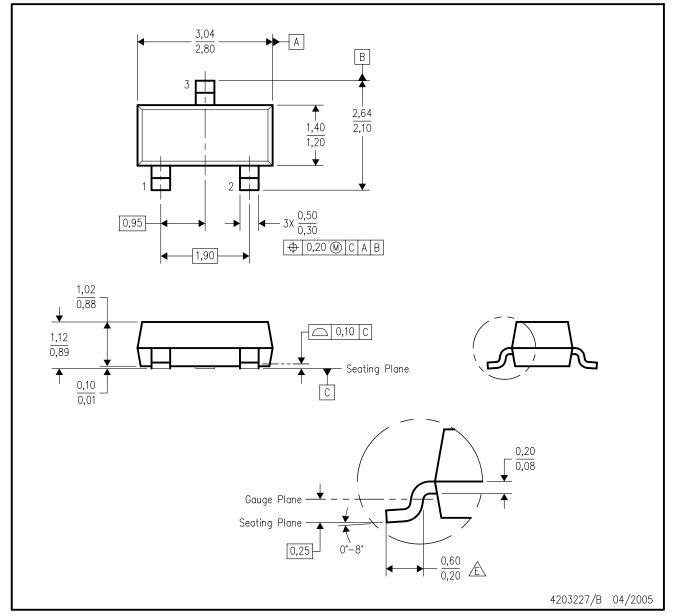

# DBZ (R-PDSO-G3)

# PLASTIC SMALL-OUTLINE

NOTES: A. All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5M-1994.

- B. This drawing is subject to change without notice.

- C. Lead dimensions are inclusive of plating.

- D. Body dimensions are exclusive of mold flash and protrusion. Mold flash and protrusion not to exceed 0.25 per side.

- Falls within JEDEC TO-236 variation AB, except minimum foot length.

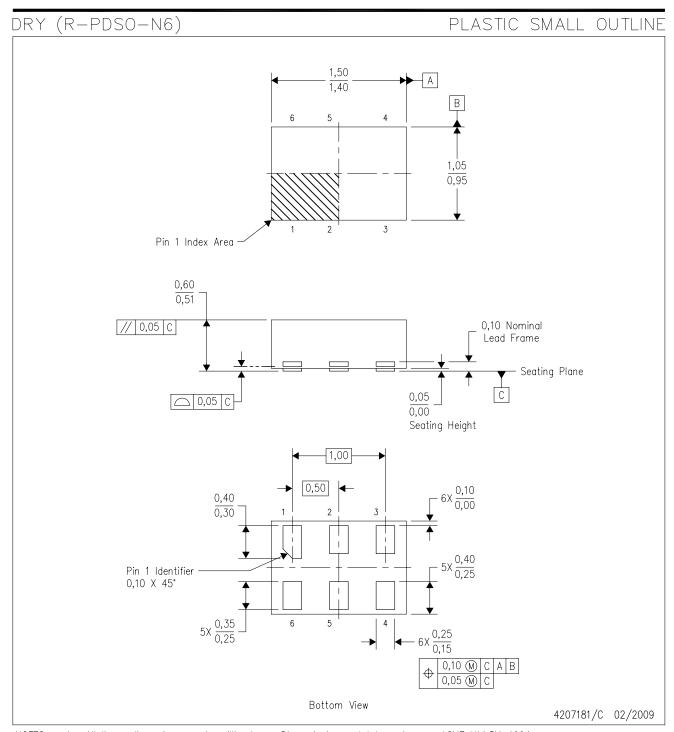

NOTES: A. All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5M-1994.

- B. This drawing is subject to change without notice.

- C. SON (Small Outline No-Lead) package configuration.

- D. This package complies to JÉDEC MO-287 variation UFAD.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

**Applications Products Amplifiers** amplifier.ti.com Audio www.ti.com/audio Data Converters Automotive www.ti.com/automotive dataconverter.ti.com DLP® Products Broadband www.dlp.com www.ti.com/broadband DSP Digital Control dsp.ti.com www.ti.com/digitalcontrol Clocks and Timers www.ti.com/clocks Medical www.ti.com/medical Military Interface www.ti.com/military interface.ti.com Optical Networking Logic logic.ti.com www.ti.com/opticalnetwork Power Mgmt power.ti.com Security www.ti.com/security Telephony Microcontrollers microcontroller.ti.com www.ti.com/telephony Video & Imaging www.ti-rfid.com www.ti.com/video RF/IF and ZigBee® Solutions www.ti.com/lprf Wireless www.ti.com/wireless

> Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2009, Texas Instruments Incorporated