# **Advanced Power Management Unit**

Check for Samples: TPS658600

### 1 INTRODUCTION

#### 1.1 MAIN FEATURES

- BATTERY CHARGER

- Complete Charge Management Solution for a Single Cell Li-lon/Li-Pol Cell With Dynamic Power Management and Thermal Foldback.

- Maximum 1.0A charge current

- Programmable Adapter and USB Charge Operation

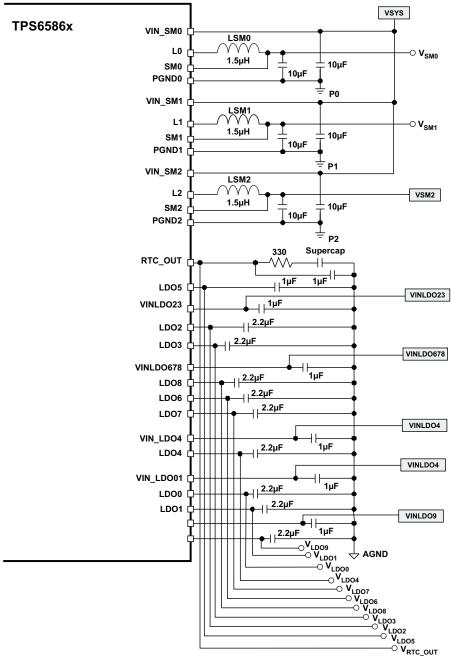

- INTEGRATED POWER SUPPLIES

- 3 Programmable Step-Down converters

- Software Controlled Enable/Forced PWM Mode

- Automatic Power Saving Mode

- Maximum 1.2A Outputs

- 11 Programmable General Purpose LDOs

- 7 With Output Voltages of 1.25V to 3.3V

- 2 With Output Voltages of 0.725V to 1.5V or 1.25V to 2.586V (factory configurable)

- 1 "Always On" With Output Voltages of 1.25V to 3.3V

- 1 With Output Voltage of 1.70V–2.475V

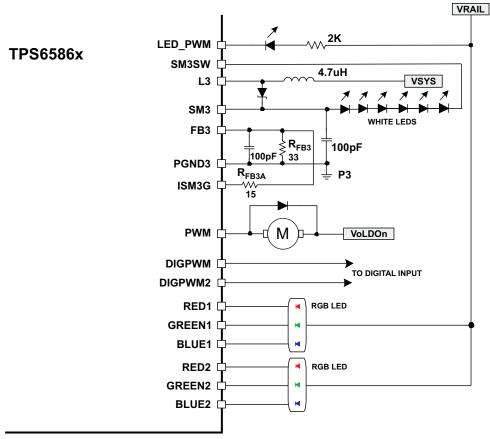

- DISPLAY SUPPORT FUNCTIONS

- 4 PWM Outputs With Programmable Frequency and Duty Cycle

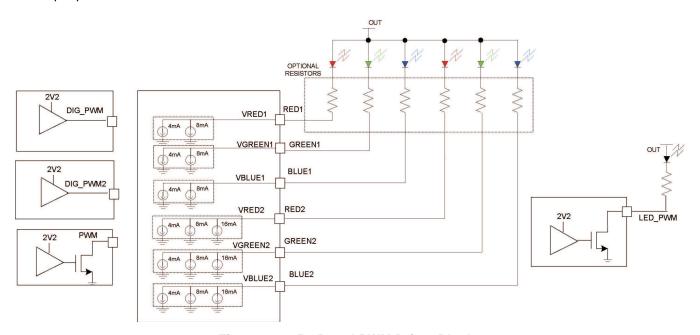

- Dual RGB LED Drivers

- Constant Current WLED Driver

- 26.5V (max) at 25mA

- Over-Voltage Protection

- Programmable Current Level and Brightness Control

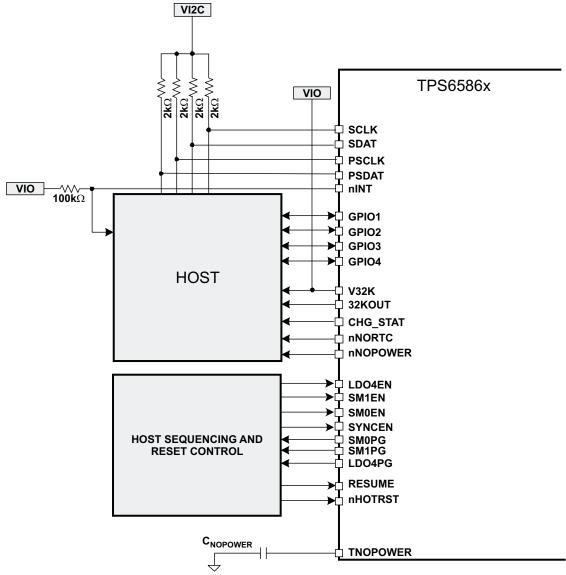

- HOST INTERFACE

- Interrupt Controller With Maskable Interrupts

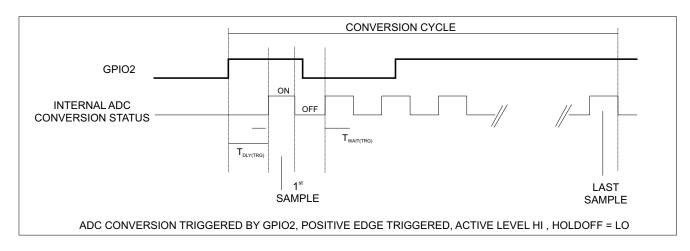

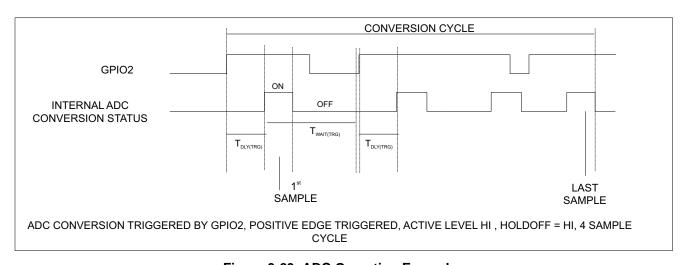

- External ADC Triggering and Step-Down Converter Mode Control

- SYSTEM MANAGEMENT

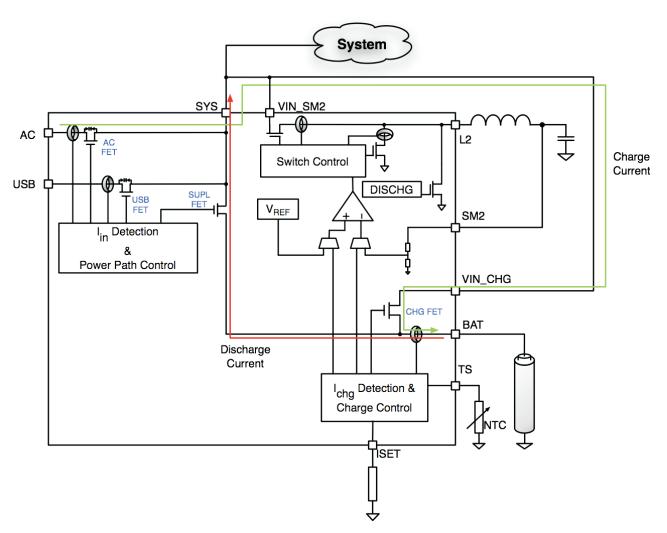

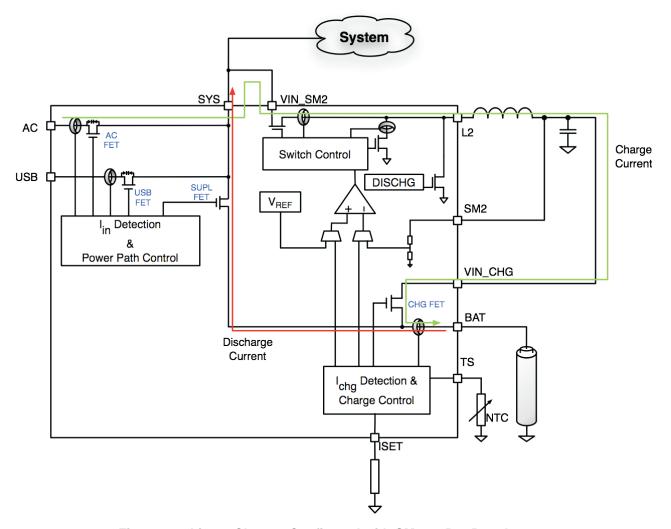

- Dual Input Power Path

- USB Current Limiting

- Max 18V Over-Voltage Protection

- Power Good Monitoring on all Supply Outputs

- Software Reset Function

- Hardware On/Off and Reboot Control

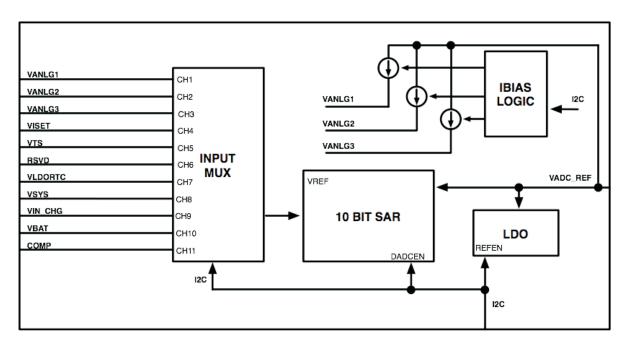

- 11 Channel ADC With 3 Operating Modes

- Single Conversion

- Peak Detection

- Averaging

#### 1.2 APPLICATIONS

- Smart Phones

- Portable Navigation Devices

- Portable Media Players

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

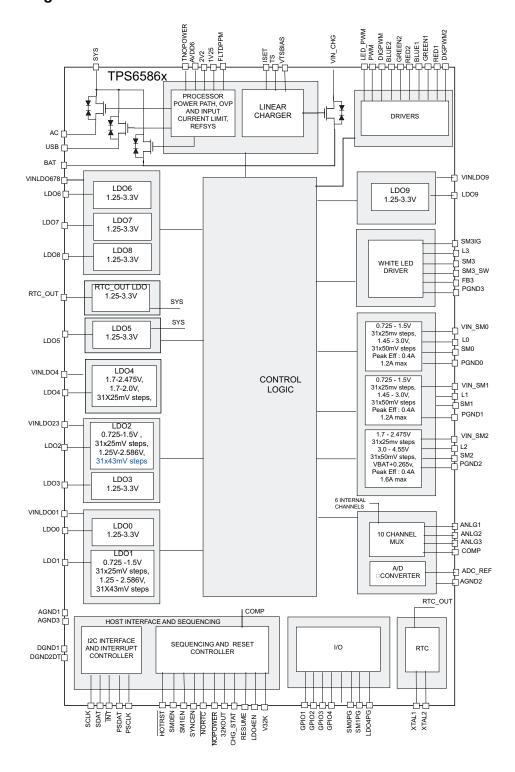

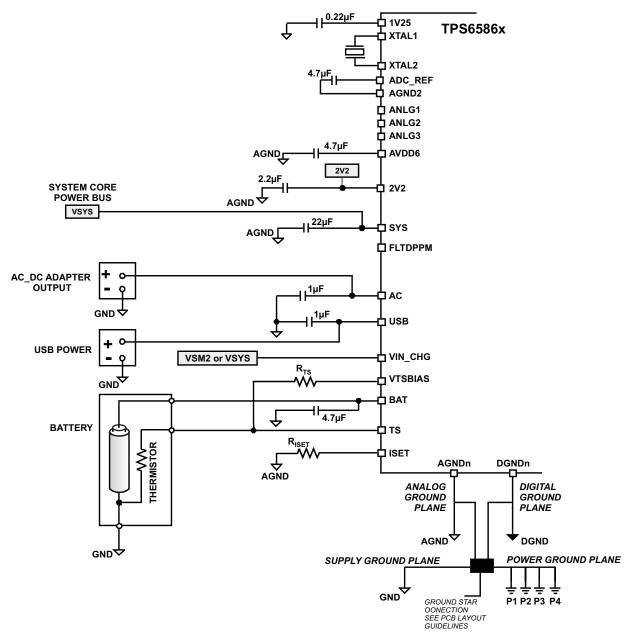

#### 1.3 OVERVIEW

The TPS658600 provides an easy to use, fully integrated solution for handheld devices, integrating charge management, multiple regulated power supplies, system management and display functions in a small 6x6 package. The I<sup>2</sup>C interface enables control of a wide range of subsystem parameters. Internal registers have a complete set of status information, enabling easy diagnostics and host-controlled handling of fault conditions.

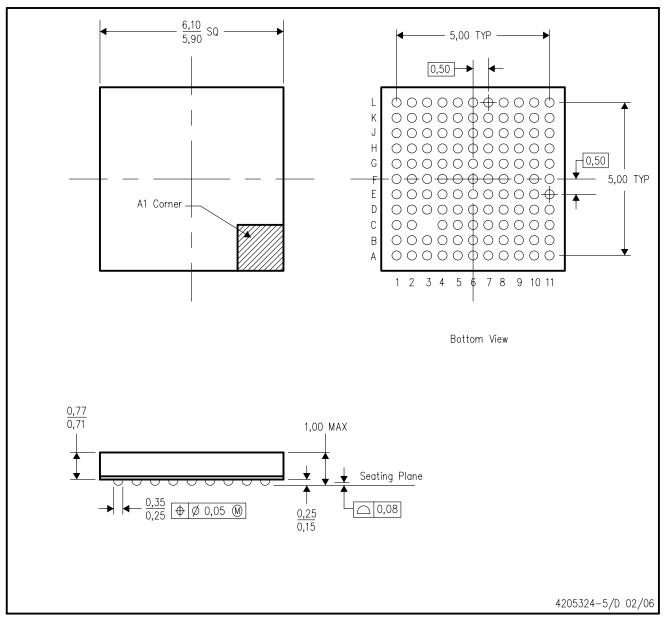

# 1.4 ORDERING INFORMATION(1)

| T <sub>A</sub> | PART NUMBER (2) (3) | PACKAGE <sup>(4)</sup> | PACKAGE DESIGNATOR | ORDERING <sup>(2)</sup> | PACKAGE MARKING |

|----------------|---------------------|------------------------|--------------------|-------------------------|-----------------|

| –40°C to 85°C  | TPS658600           | MicroStar BGA          | ZQZ                | TPS658600               | TPS658600       |

- (1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI website at www.ti.com.

- (2) The TPS658600 is only available taped and reeled. Quantities are 2,500 devices per reel.

- (3) Devices with distinct part numbers have unique factory configurations for supply defaults, sequencing and other functions. Consult the factor for configuration information for each part number.

- (4) This product is RoHS compatible, including a lead concentration that does not exceed 0.1% of total product weight, and is suitable for use in specified lead-free soldering processes. In addition, this product uses package materials that do not contain halogens, including bromine (Br) or antimony (Sb) above 0.1% of total product weight.

# 2 ELECTRICAL SPECIFICATIONS

#### 2.1 ABSOLUTE MAXIMUM RATINGS

over operating free-air temperature range (unless otherwise noted) (1)

|                                                                                               | VALUE / UNITS    |

|-----------------------------------------------------------------------------------------------|------------------|

| AC and USB with respect to AGND1                                                              | –0.3 V to 18 V   |

| ANLG1, ANLG2, ANLG3 with respect to AGND2                                                     | –0.3 V to 6.5 V  |

| V(SYS), V(VIN_CHG) with respect to AGND1                                                      | –0.3 V to 6.5 V  |

| VIN_LDO01, VIN_LDO23, VIN_LDO4, VIN_LDO678, VIN_LDO9 with respect to AGND1                    | –0.3 V to 6.5 V  |

| ADC_REF with respect to AGND2                                                                 | -0.3 V to 3.6 V  |

| RTC_OUT with respect to V(SYS)                                                                | –5.5 V to 3.6 V  |

| RTC_OUT with respect to AGND1                                                                 | –0.3 V to 3.6 V  |

| LDO0, LDO1, LDO2, LDO3, LDO4, LDO5, LDO6, LDO7, LDO8, LDO9, V2V2 and TS with respect to AGND1 | -0.3 V to 3.6 V  |

| V32K with respect to AGND1                                                                    | -0.3 V to 3.6 V  |

| TS with respect to V2V2                                                                       | –2.3 V to 0.3 V  |

| SM0, L0, VIN_SM0 with respect to PGND0                                                        | –0.3 V to 6.5 V  |

| SM1, L1, VIN_SM1 with respect to PGND1                                                        | –0.3 V to 6.5 V  |

| SM2, L2, VIN_SM2 with respect to PGND2                                                        | –0.3 V to 6.5 V  |

| SM3 , L3 with respect to PGND3                                                                | –0.3 V to 29 V   |

| SM3SW with respect to PGND3                                                                   | -0.3 V to 29 V   |

| FB3 with respect to PGND3                                                                     | -0.3 V to 0.5 V  |

| V(BAT) with respect to AGND1, Battery power only                                              | -0.3 V to 4.6 V  |

| All other pins (except AGNDn and PGNDn) with respect to AGND1                                 | –0.3 V to 6.5 V  |

| AGND2, AGND3, , DGND1, DGND2DT, PGND0, PGND1, PGND2, PGND3 with respect to AGND1              | -0.3 V to +0.3 V |

| Input Current, AC pin                                                                         | Defined by ILIM  |

| Input Current, USB pin                                                                        | Defined by ILIM  |

| Output continuous current, SYS, VIN_CHG pins                                                  | 2500 mA          |

| Output continuous current, BAT pin                                                            | -3000 mA         |

| Continuous Current at L0, PGND0, L1, PGND1                                                    | 1500 mA          |

| Continuous Current at L3, PGND3                                                               | 1000 mA          |

| Continuous Current at L2, PGND2                                                               | 2000 mA          |

| Operating free-air temperature, T <sub>A</sub>                                                | -40°C to 85°C    |

| Maximum junction temperature, T <sub>J</sub>                                                  | 125°C            |

| Storage temperature, T <sub>STG</sub>                                                         | -65°C to 150°C   |

| Lead temperature 1,6 mm (1/16-inch) from case for 10 seconds                                  | 260°C            |

| HBM rating , all pins                                                                         | 2 kV             |

| MM rating, all pins                                                                           | 100 V            |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 2.2 DISSIPATION RATINGS

| PACKAGE | Psi_Jb | T <sub>A</sub> ≤ 25°C<br>POWER RATING | DERATING FACTOR<br>ABOVE T <sub>A</sub> = 25°C | T <sub>A</sub> = 55°C<br>POWER RATING | T <sub>A</sub> = 70°C<br>POWER RATING | T <sub>A</sub> = 85°C<br>POWER RATING |

|---------|--------|---------------------------------------|------------------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|

| ZQZ     | 25°C/W | 4000 mW                               | 40.0°C/W                                       | 2800 mW                               | 2200 mW                               | 1600 mW                               |

# 2.3 RECOMMENDED OPERATING CONDITIONS

|                                                                                                        | MIN                                                                                                                                            | MAX                 | UNIT |

|--------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|

| AC and USB with respect to AGND1                                                                       | 4.30                                                                                                                                           | 16.5 <sup>(1)</sup> | V    |

| V(SYS) with respect to AGND1                                                                           | 2.9                                                                                                                                            | 5.5                 | V    |

| V(BAT) with respect to AGND1, battery power only                                                       | 2.9                                                                                                                                            | 4.6                 | V    |

| V(BAT) with respect to AGND1, battery connected, AC or USB power selected, Selected power source >2.9V | 2.15                                                                                                                                           | 4.6                 | V    |

| ANLG1,ANLG2, ANLG3 with respect to AGND2                                                               | 0                                                                                                                                              | 2.6                 | V    |

| VIN_LDO01, VIN_LDO23, VIN_LDO678, VIN_LDO4, VIN_LDO9 with respect to AGND1                             | Greater of : 1.7V OR Minimum input voltage required for LDO/Converter operation outside dropout region                                         | 5.5                 | V    |

| VIN_SM0 with respect to PGND0                                                                          | Greater of: 2.3V OR Minimum input voltage required for LDO/Converter operation outside dropout region. 2.9V to meet parametric specifications. | 5.5                 | V    |

| VIN_SM1 with respect to PGND1                                                                          |                                                                                                                                                | 28                  | V    |

| VIN_SM2 with respect to PGND2                                                                          |                                                                                                                                                | 28                  | V    |

| VIN_SM4 with respect to PGND4                                                                          |                                                                                                                                                | 28                  | V    |

| SM3 with respect to PGND3                                                                              |                                                                                                                                                | 28                  | V    |

| GPIOx with respect to AGND1                                                                            | 0                                                                                                                                              | 5.5                 | V    |

| All other pins (except AGNDn and PGNDn) with respect to AGND1                                          | 0                                                                                                                                              | 5.5                 | V    |

| Operating free-air temperature, T <sub>A</sub>                                                         | -40                                                                                                                                            | 85                  | °C   |

| Maximum junction temperature, T <sub>J</sub> , functional operation                                    | -40                                                                                                                                            | 125                 | °C   |

| Maximum junction temperature, T <sub>J</sub> , electrical characteristics                              | 0                                                                                                                                              | 125                 | °C   |

| External supply ramp rate, AC or USB pins                                                              | 1 V/mSec                                                                                                                                       | 1 V/µSec            |      |

<sup>(1)</sup> Thermal operating restrictions are reduced or avoided if input voltage does not exceed 5V.

#### 2.4 **ELECTRICAL CHARACTERISTICS**

|                         | PARAMETER                                                                                   | TEST CONDITIONS                                                                                                                                          | MIN  | TYP | MAX | UNIT |

|-------------------------|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-----|------|

| QUIESCENT (             | CURRENT - V(BAT) = 4.2V NO EXTERNAL LOADS A                                                 | T SYS PIN OR SUPPLY OUTPUTS                                                                                                                              |      |     |     |      |

| Q(ON)                   | Quiescent current, 6586x in normal or sleep mode. All supplies, peripherals and charger off | Power path active, control logic in low power mode <sup>(1)</sup>                                                                                        |      |     | 375 | μΑ   |

| Q(DIGITAL)              | Quiescent current, control logic                                                            | Control logic in high power mode <sup>(2)</sup>                                                                                                          | 584  | 716 | 870 | μΑ   |

|                         |                                                                                             | SM0, SM1: enabled, PFM mode, from SYS pin                                                                                                                |      | 14  | 25  | μΑ   |

|                         | ONO ONA ONO secretical existence of secret                                                  | SM2: enabled, PFM mode, from SYS pin                                                                                                                     |      | 19  | 32  | μΑ   |

| Q(SMn)                  | SM0, SM1, SM2 operating quiescent current                                                   | SM0, SM1, SM2: enabled, PWM mode, from VINSMn pin                                                                                                        |      | 6   |     | mA   |

|                         |                                                                                             | disabled via I <sup>2</sup> C                                                                                                                            |      | 1   |     | μΑ   |

|                         |                                                                                             | I(LDOx) = no external load                                                                                                                               |      | 24  | 29  | μΑ   |

|                         | LDO quiescent current, All but one LDOx                                                     | I(LDOx) = -1  mA                                                                                                                                         |      | 24  | 150 | μΑ   |

| Q(LDOx)                 | disabled                                                                                    | I(LDOx) = -50  mA                                                                                                                                        |      | 160 |     | μΑ   |

|                         |                                                                                             | LDO disabled, T <sub>J</sub> = 85°C                                                                                                                      |      | 1   | 3   | μΑ   |

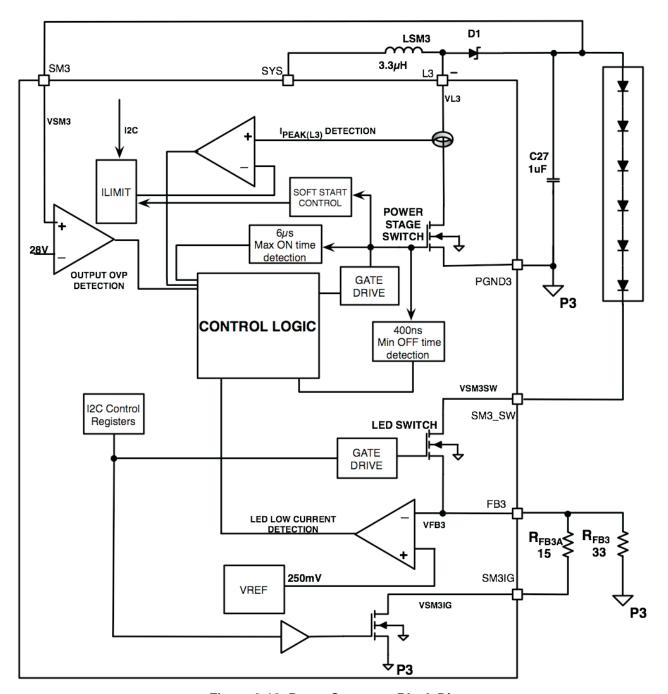

|                         |                                                                                             | SM3 enabled, not switching                                                                                                                               |      | 15  | 30  | μΑ   |

| Q(SM3)                  | SM3 operating quiescent current <sup>(3)</sup>                                              | Enabled, switching                                                                                                                                       |      |     | 200 | μΑ   |

|                         |                                                                                             | Disabled via I <sup>2</sup> C                                                                                                                            |      | 1   |     | μΑ   |

|                         |                                                                                             | Conversion active                                                                                                                                        |      | 1   |     | mA   |

| I <sub>Q(ADC)</sub>     | ADC operating quiescent current                                                             | Not converting, waiting for trigger                                                                                                                      |      | 170 |     | μΑ   |

|                         |                                                                                             | ADC disabled via I <sup>2</sup> C                                                                                                                        |      | 1   |     | μA   |

|                         |                                                                                             | RTC_OUT LDO enabled                                                                                                                                      |      | 27  | 45  | μA   |

| I <sub>Q(RTC)</sub>     | RTC_OUT pin quiescent current                                                               | RTC_OUT disabled via $I^2$ C, $T_J$ = 85°C . Externally applied <sup>(4)</sup> $V(RTC\_OUT)$ = 2 V supplies real time clock counters and xtal oscillator |      |     | 15  | μΑ   |

|                         |                                                                                             | 32k buffer enabled, 100 pF external load                                                                                                                 |      |     | 24  | μA   |

| Q(V32K)                 | V32K supply bias current , 32k buffer enabled                                               | Disabled via I <sup>2</sup> C                                                                                                                            |      |     | 8   | μA   |

|                         |                                                                                             | Charger enabled, termination detected                                                                                                                    |      | 40  | 50  | μA   |

| I <sub>Q(CHG)</sub>     | Charger quiescent current                                                                   | Charger enabled, termination disabled, charge current=0 <sup>(3)</sup>                                                                                   |      |     | 2   | mA   |

| .,                      |                                                                                             | Charger disabled                                                                                                                                         |      | 10  | 20  | μA   |

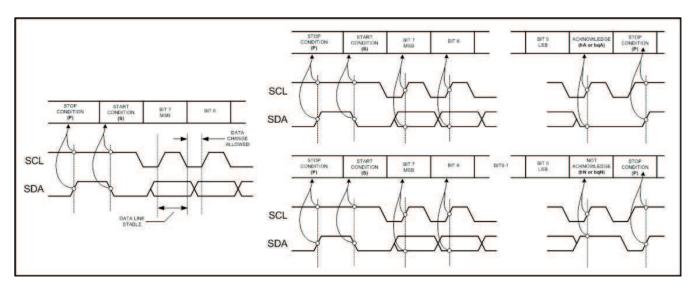

| <sup>2</sup> C INTERFAC | E TIMING – SDA, PSDA, PSCLK, SCLK <sup>(3)</sup>                                            |                                                                                                                                                          |      |     |     | -    |

| T <sub>R</sub>          | SCLK/SDATA rise time                                                                        |                                                                                                                                                          |      |     | 300 | ns   |

| T <sub>F</sub>          | SCLK/SDATA fall time                                                                        |                                                                                                                                                          |      |     | 300 | ns   |

| T <sub>W(H)</sub>       | SCLK pulse width high                                                                       |                                                                                                                                                          | 600  |     |     | ns   |

| T <sub>W(L)</sub>       | SCLK Pulse Width Low                                                                        |                                                                                                                                                          | 1.3  |     |     | μs   |

| T <sub>SU(STA)</sub>    | Setup time for START condition                                                              |                                                                                                                                                          | 600  |     |     | ns   |

| T <sub>H(STA)</sub>     | START condition hold time after which first clock pulse is generated                        | Pull-up resistors connected to 2.2V                                                                                                                      | 600  |     |     | ns   |

| T <sub>SU(DAT)</sub>    | Data setup time                                                                             |                                                                                                                                                          | 100  |     |     | ns   |

| T <sub>H(DAT)</sub>     | Data hold time                                                                              |                                                                                                                                                          | 0    |     |     | ns   |

| T <sub>SU(STOP)</sub>   | Setup time for STOP condition                                                               |                                                                                                                                                          | 600  |     |     | ns   |

| $T_{(BUF)}$             | Bus free time between START and STOP condition                                              |                                                                                                                                                          | 1.3  |     |     | μs   |

| F <sub>SCL</sub>        | Clock Frequency                                                                             |                                                                                                                                                          |      |     | 400 | kHz  |

| <sup>2</sup> C BUFFERS  | – SDA, PSDA, PSCLK, SCLK                                                                    |                                                                                                                                                          |      |     |     |      |

| V <sub>IL(I2C)</sub>    | Low level input voltage                                                                     |                                                                                                                                                          |      |     | 0.4 | V    |

| V <sub>IH(I2C)</sub>    | High level input voltage                                                                    |                                                                                                                                                          | 1.15 |     |     | V    |

| V <sub>OL(I2C)</sub>    | Low level output voltage                                                                    | SDA, PSDA configured as output, I <sub>OL</sub> =3mA                                                                                                     |      |     | 0.4 | V    |

| I <sub>O(I2C)</sub>     | Maximum load current <sup>(3)</sup>                                                         | SDA, PSDA configured as output                                                                                                                           |      |     | 8   | mA   |

| I <sub>LKG(I2C)</sub>   | Input current                                                                               | V(pin)=5V or 0V                                                                                                                                          |      |     | 1.0 | μΑ   |

| C <sub>I2C</sub>        | Input pin capacitance                                                                       | SDAT, SCLK, PSDAT, PSCLK pins                                                                                                                            |      | 10  |     | pF   |

| C <sub>I2CBUS</sub>     | I <sup>2</sup> C bus capacitance                                                            | SDAT, SCLK, PSDAT, PSCLK                                                                                                                                 |      | 400 |     | pF   |

- (1) Control logic in low power mode when all functions are off and no I<sup>2</sup>C communication is on going

(2) Control logic in high power mode when one of the following events happen: 6586x in power-up/rtc/rtc\_on/supplyseq states, any converter in PWM mode, SM3 enabled, PWM driver enabled, ADC conversion on-going, I<sup>2</sup>C communication on-going, voltage transition for DVM supplies on-going, charger on, AC or USB supply detected, initial power-up cycle.

- Not production tested.

- External voltage supplied by supercap or coin cell connected to RTC\_OUT pin, see application diagram for details.

# **ELECTRICAL CHARACTERISTICS (continued)**

|                                       | PARAMETER                                                     | TEST CONDITIONS                                                 | MIN       | TYP    | MAX  | UNIT |

|---------------------------------------|---------------------------------------------------------------|-----------------------------------------------------------------|-----------|--------|------|------|

| DIGITAL INPU                          | T BUFFERS: RESUME, SM0EN, SM1EN, HOTRST, L                    | LDO4EN, SYNCEN                                                  |           |        |      |      |

| V <sub>IL(DIG)</sub>                  | Low level input voltage                                       |                                                                 |           |        | 0.4  | V    |

| / <sub>IH(DIG)</sub>                  | High level input voltage                                      |                                                                 | 1.15      |        |      | V    |

| LKG(DIG)                              | Input current                                                 | V(pin)=5V                                                       |           |        | 0.1  | μΑ   |

|                                       | Internal recistor                                             | RESUME pin , pull-down to AGND                                  | 55        | 100    | 150  | kΩ   |

| R <sub>DIG</sub>                      | Internal resistor                                             | HOTRST pin, pull-up to V2V2                                     | 55        | 100    | 150  | K12  |

| PUSH-PULL C                           | OUTPUT BUFFERS, USER SELECTABLE OUTPUT V                      | OLTAGE – NORTC, NOPOWER                                         | •         |        | -    |      |

| V <sub>BFRPWR</sub>                   | Buffer positive supply                                        | Internally connected to V32K pin                                | 1.1       | to 3.3 |      | V    |

| .,                                    | Law law Law tank with an                                      | I <sub>OL</sub> = 3 mA, V32K = 1.5 V                            |           |        | 0.6  |      |

| V <sub>OL(OBFR)</sub>                 | Low level output voltage                                      | I <sub>OL</sub> = 10 μA, V32K > 1.1 V                           |           |        | 0.1  | V    |

| · · · · · · · · · · · · · · · · · · · | High level output voltage, referenced to output               | I <sub>OH</sub> = 1.4 mA, V32K = 1.5 V                          | V32K-0.6  |        |      | V    |

| V <sub>OH(OBFR)</sub>                 | buffer supply, NORTC                                          | I <sub>OH</sub> = -10 μA, V32K = 1.1 V                          | V32K-0.11 |        |      | V    |

| V                                     | High level output voltage, referenced to output               | I <sub>OH</sub> = 1.4 mA, V32K = 1.5 V                          | V32K-0.6  |        |      |      |

| V <sub>OH(OBFR)</sub>                 | buffer supply,NOPOWER                                         | I <sub>OH</sub> = -10 μA, V32K = 1.1 V                          | V32K-0.11 |        |      | V    |

| I <sub>OL(OBFR)</sub>                 | Maximum low level sink current load <sup>(1)</sup>            | V(pin) = 2.5 V                                                  |           |        | 5    | mA   |

| I <sub>OH(OBFR)</sub>                 | Maximum high level source current load <sup>(1)</sup>         | V(pin) = 0 V                                                    | -5        |        |      | mA   |

|                                       | OUTPUT BUFFERS – INT                                          |                                                                 | •         |        |      |      |

|                                       | Landard colored and                                           | I <sub>OL</sub> = 3 mA, V32K = 1.5 V                            |           |        | 0.6  |      |

| $V_{OL(OBFR)}$                        | Low level output voltage                                      | I <sub>OL</sub> = 10 μA, V32K > 1.1 V                           |           |        | 0.1  | V    |

| I <sub>LKG(OBFR)</sub>                | Output leakage current                                        | Output buffer, open-drain mode, V(pin)=5.5V                     |           |        | 0.1  | μΑ   |

|                                       | OUTPUT BUFFERS - LDO4PG, SM0PG, SM1PG, CH0                    | GSTAT                                                           |           |        |      |      |

|                                       |                                                               | I <sub>OL</sub> = 3 mA                                          |           |        | 0.6  |      |

| V <sub>OL(DBFR)</sub>                 | Low level output voltage                                      | I <sub>OL</sub> = 10 μA                                         |           |        | 0.1  | V    |

|                                       | High level output voltage , buffer configured as              | I <sub>OH</sub> = 3 mA                                          | 1.5       |        |      |      |

| $V_{OH(DBFR)}$                        | push-pull via I <sup>2</sup> C                                | I <sub>OH</sub> = -10 μA                                        | 1.8       |        |      | V    |

| I <sub>OL(DBFR)</sub>                 | Maximum low level sink current load <sup>(1)</sup>            | V(pin) = 2.5 V                                                  |           |        | 5    | mA   |

| I <sub>OH(DBFR)</sub>                 | Maximum high level source current load <sup>(1)</sup>         | V(pin) = 0 V                                                    | -5        |        |      | mA   |

|                                       | T BUFFER , V(32K)=1.7V (min), UNLESS OTHERWI                  | SE STATED                                                       | 1         |        |      |      |

| V <sub>32B</sub>                      | Externally applied bias rail for output driver <sup>(1)</sup> | Buffer supply voltage                                           | 1.0       |        | 3.6  | V    |

|                                       |                                                               | V(32K) = 1.1 V, I <sub>OL</sub> = 100 μA                        |           |        | 0.05 |      |

| V <sub>OL</sub>                       | Output low level                                              | V(32K) = 1.1 V, I <sub>OL</sub> = 1 mA                          |           |        | 0.2  | V    |

| 02                                    | ·                                                             | V(32K) = 1.5 V, I <sub>OL</sub> = 5 mA                          |           |        | 0.5  |      |

|                                       |                                                               | V(32K) = 1.1 V, I <sub>OH</sub> = -1 μA                         | V32K-0.05 |        |      |      |

| V <sub>OH</sub>                       | Normal operation                                              | V(32K) = 1.5 V, I <sub>OH</sub> = 5 mA                          | V32K-0.5  |        |      | V    |

| T <sub>F</sub> , T <sub>R</sub>       | Rise/fall time                                                | 32 kHz clock driving 50pF load cap                              |           | 15     |      | ns   |

| r - 1X                                |                                                               | Peak to peak                                                    |           | 15     |      |      |

| $V_{\text{JITTER}}$                   | Output jitter                                                 | RMS                                                             | <u> </u>  | 15     |      | ns   |

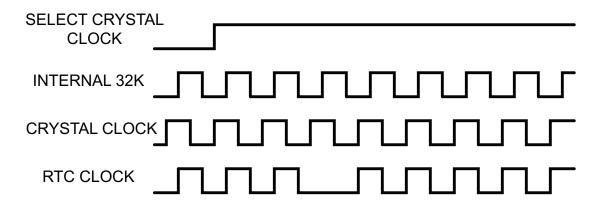

| 32kHz CLOCK                           | AND 32K SWITCHING TIMING                                      | <u> </u>                                                        | 1         |        |      |      |

| -                                     |                                                               | Frequency within 2% of typical value, frequency defined by XTAL |           |        | ٦    | _    |

| I <sub>XTAL</sub>                     | XTAL oscillator stabilization time <sup>(1)</sup>             | characteristics                                                 |           |        | 2    | S    |

| F <sub>32K</sub>                      | Internal 32 kHz clock                                         | Frequency                                                       | 28        | 32     | 36   | kHz  |

| INTERNAL RE                           | FERENCES AND POR                                              |                                                                 |           |        |      |      |

| V <sub>UVLO</sub>                     | Internal UVLO detection threshold                             | V(2V2) decreasing                                               | -3%       | 1.85   | 3%   | V    |

| V <sub>UVLO_HYS</sub>                 | UVLO detection hysteresis                                     | V(2V2) increasing from decreasing trigger point                 |           | 120    |      | mV   |

| V <sub>O(2V2)</sub>                   | Output Voltage                                                | Always on,                                                      | 2.1       | 2.2    | 2.3  | V    |

| I <sub>SH2V2</sub>                    | Short Circuit current limit                                   | V(2V2)=0v                                                       | 18        |        |      | mA   |

<sup>(1)</sup> Not production tested.

#### **ELECTRICAL CHARACTERISTICS** 2.5

over operating free-air temperature range (unless otherwise noted)

|                           | PARAMETER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | TEST CONDITIONS                                                             | MIN                                  | TYP                          | MAX       | UNIT         |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|--------------------------------------|------------------------------|-----------|--------------|

| RTC_OUT LDO               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                             |                                      |                              |           |              |

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Output Voltage, Selectable via I <sup>2</sup> C <sup>(1)</sup>              | V <sub>O(RTC_OUT)</sub> TYP<br>2.7,2 | =1.25, 1.50,<br>.85,3.1,3.3  | 1.8, 2.5, | V            |

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Dropout voltage, I(RTC_OUT) = -15 mA<br>V(SYS) = 2.8 V                      |                                      |                              | 600       | mV           |

| V <sub>O(RTC_OUT)</sub>   | RTC_OUT output voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Total accuracy, V(AC):2V to 4.7V, -15mA load, V(BAT1)=V(BAT2)=V(USB)=0V     | -5%                                  |                              | 5%        |              |

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Load regulation, V(AC)=3.5V, load: $1mA \rightarrow -15mA$                  |                                      | 1%                           |           |              |

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Line regulation, 5mA load,V(AC): 3.5V→18V, V(BAT1) =V(BAT2) =V(USB) =0V     |                                      | 1%                           |           |              |

| SHRTC                     | Short Circuit current limit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                             | 20                                   |                              |           | mA           |

| V <sub>(RTCGOOD)</sub>    | RTC_OUT power good fault detection threshold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Falling RTC_OUT pin voltage, set via I <sup>2</sup> C                       | 2.3                                  | 2.35<br>1.90                 | 2.45      | ٧            |

| V <sub>HYS(RTC)</sub>     | Power good fault detection hysteresis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Rising RTC_OUT pin voltage (Referenced to V <sub>(RTCGOOD)</sub> threshold) | 50                                   | 75                           | 131       | mV           |

| V <sub>UVLO_RTC</sub>     | Internal RTC UVLO detection threshold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | VRTC Decreasing                                                             | -10%                                 | 1.5                          | 10%       | V            |

| V <sub>UVLO_RTC_HYS</sub> | UVLO detection hysteresis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | VRTC Increasing                                                             | 100                                  | 150                          | 200       | mV           |

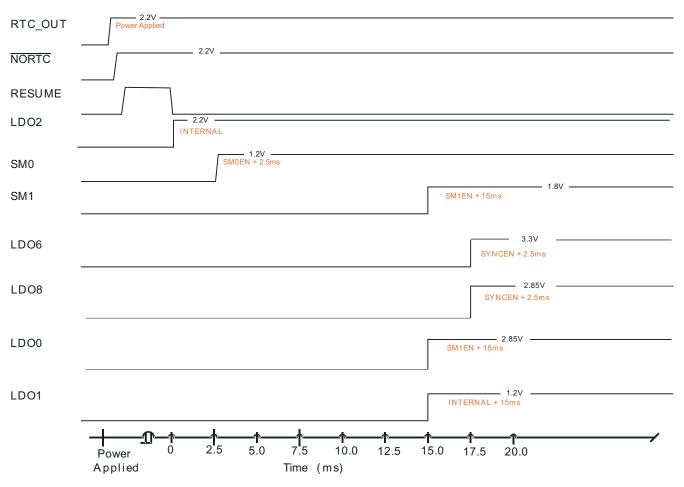

| BOOT-UP TIMIN             | <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | The moreasing                                                               | 100                                  |                              | 200       |              |

| T <sub>POR</sub>          | Power-on-reset delay <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Fixed time, measured from 2V2>UVLO                                          | 7.2                                  | 8                            | 8.8       | ms           |

| TOK                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Fixed time                                                                  |                                      | 500                          |           |              |

| T <sub>BOOT</sub>         | Boot-up time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Accuracy, referenced to T <sub>BOOT((TYP)</sub>                             | -10%                                 |                              | 10%       | ms           |