# LH4118/LH4118A/LH4118C Low Gain Wide Band RF Amplifier

### **General Description**

The LH4118 is a wideband amplifier optimized for high speed, low gain applications. It is an ideal alternative to low precision amplifiers. It features a closed loop -3 dB unity gain bandwidth in excess of 200 MHz. Unlike conventional op-amps, the bandwidth is relatively independent of closed loop gain between 1 and 5. A high current output stage is also incorporated, allowing the LH4118 to drive  $50\Omega$  terminated lines directly. It is an ideal choice for video distribution, flash converter input buffering and ATE pin driver.

#### **Features**

- 250 MHz bandwidth

- 15 ns settling time to 0.1%

- 2.5 ns rise and fall times

- Output current to 100 mA

- 2 mV offset voltage

- 2500 V/µs slew rate (100Ω load)

- $\pm 0.5$  dB gain flatness (AV = 5)

### **Applications**

- Unity gain buffers

- Low gain op amp

- High speed peak detectors

- Video amplifier

- Flash converter driver

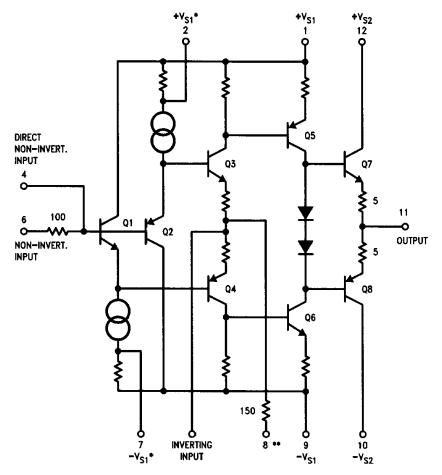

### Simplified Schematic

TL/K/9768-1

<sup>\*</sup>Pins 2 and 7 can also be left disconnected (floating)

<sup>\*\*</sup>The built-in 150 $\Omega$  can be used as feedback resistor for A<sub>V</sub> = 1. For details see applications section.

## **Absolute Maximum Ratings**

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Supply Voltage, VS ±18V 1.65W Power Dissipation, PD (See Graph)

Output Current Non-Inverting Input Voltage Range,

$V_{CM}$  (For  $V_S \le +15V$ ) (Note 1) ±٧s Operating Temperature Range, T<sub>A</sub> LH4118CG

-25°C to +85°C -55°C to +125°C LH4118G, LH4118AG

Storage Temperature Range, TSTG -65°C to +150°C

175°C

Maximum Junction Temperature, T<sub>J</sub> Lead Temperature (Soldering, < 10 sec.)

300°C

ESD Tolerance (Note 2)

650V

## DC Electrical Characteristics

Unless otherwise noted,  $R_S = 50\Omega$ ,  $T_A = T_C = 25^{\circ}C$ ,  $V_S = \pm 15V$  (Notes 3, 4)

125 mA

| Symbol                           | Parameter                             |                                                      |         | Units                       |                             |                                    |

|----------------------------------|---------------------------------------|------------------------------------------------------|---------|-----------------------------|-----------------------------|------------------------------------|

|                                  |                                       | Conditions                                           | Typical | Tested<br>Limit<br>(Note 5) | Design<br>Limit<br>(Note 6) | (Max Unless<br>Otherwise<br>Noted) |

| Vos                              | Non-Inverting Input<br>Offset Voltage | V <sub>IN</sub> = 0V                                 | ±2      | ±2<br>± <b>5</b>            |                             | m∨                                 |

| $\frac{\Delta V_{OS}}{\Delta T}$ | Offset Voltage Drift                  |                                                      | 10      |                             |                             | μV/°C                              |

| l <sub>B</sub>                   | Non-Inverting Input<br>Bias Current   |                                                      | ±5      | ±25<br>±30                  |                             | μΑ                                 |

| V <sub>O</sub>                   | Output Voltage Swing                  | $R_L = 500\Omega$                                    | ±13     | ±11<br>±10.5                |                             | V (Min)                            |

| V <sub>O</sub>                   | Output Voltage Swing                  | $R_L = \infty$                                       | ±14     | ±12<br>± <b>11.5</b>        |                             | V (Min)                            |

| lo                               | Output Current Swing                  | $R_L = 50\Omega$ (Note 7)                            |         | ± 100                       |                             | mA (Min)                           |

| CMRR                             | Common Mode<br>Rejection Ratio        | $V_{IN} = -11V \text{ to } + 11V,$ $V_{S} = \pm 18V$ | 54      | 50                          |                             | dB (Min)                           |

| PSRR                             | Power Supply<br>Rejection Ratio       | $\pm V_S = 9V \text{ to } 15V$<br>$\Delta V = 6V$    | 72      | 62                          |                             | dB (Min)                           |

| Is                               | Quiescent Supply Current              | V <sub>IN</sub> = 0V                                 | 20      | 25                          | ,                           | mA                                 |

| P <sub>D</sub>                   | Quiescent Power Dissipation           | (Note 7)                                             | 600     | 750                         |                             | mW                                 |

| C <sub>IN</sub>                  | Input Capacitance                     |                                                      | 1.5     |                             |                             | pF                                 |

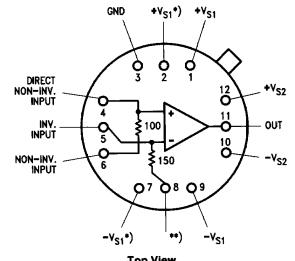

## **Connection Diagram**

TL/K/9768-2

\*Pins 2 and 7 can also be left disconnected (floating)

\*\*The built-in 150 $\Omega$  can be used as feedback resistor for A<sub>V</sub> = 1. For details see applications section.

Order Number LH4118G, LH4118AG or LH4118CG See NS Package Number H12B

DC Electrical Characteristics Unless otherwise noted,  $R_S=50\Omega$ ,  $T_A=T_C=25^{\circ}$ C,  $V_S=\pm15V$  (Notes 3, 4)

| Symbol                 | Parameter                           |                                                     |         | Units                       |                             |                                    |

|------------------------|-------------------------------------|-----------------------------------------------------|---------|-----------------------------|-----------------------------|------------------------------------|

|                        |                                     | Conditions                                          | Typical | Tested<br>Limit<br>(Note 5) | Design<br>Limit<br>(Note 6) | (Max Unless<br>Otherwise<br>Noted) |

| Vos                    | Non-Inverting Input Offset Voltage  | V <sub>IN</sub> = 0V                                | ±2      | ±5                          |                             | mV                                 |

| ΔV <sub>OS</sub><br>ΔT | Offset Voltage Drift                |                                                     | 10      |                             |                             | μV/°C                              |

| l <sub>B</sub>         | Non-Inverting Input<br>Bias Current |                                                     | ±5      | ±25<br>±30                  |                             | μΑ                                 |

| v <sub>o</sub>         | Output Voltage<br>Swing             | $R_L = 500\Omega$                                   | ±13     | ±11<br>±10.5                |                             | V<br>(Min)                         |

| v <sub>o</sub>         | Output Voltage Swing                | R <sub>L</sub> = ∞                                  | ±14     | ±12<br>± <b>11.5</b>        |                             | V (Min)                            |

| Ю                      | Output Current Swing                | $R_L = 50\Omega$ (Note 7)                           |         | ± 100                       |                             | mA (Min)                           |

| CMRR                   | Common Mode<br>Rejection Ratio      | $V_{IN} = -11V \text{ to } +11V,$ $V_{S} = \pm 18V$ | 54      | 50                          |                             | dB (Min)                           |

| PSRR                   | Power Supply<br>Rejection Ratio     | $\pm V_S = 9V \text{ to } 15V$<br>$\Delta V = 6V$   | 72      | 62                          |                             | dB (Min)                           |

| ls                     | Quiescent Supply Current            | V <sub>IN</sub> = 0V                                | 20      | 25                          |                             | mA                                 |

| PD                     | Quiescent Power Dissipation         | (Note 7)                                            | 600     | 750                         |                             | mW                                 |

| CIN                    | Input Capacitance                   |                                                     | 1.5     |                             |                             | pF                                 |

DC Electrical Characteristics Unless otherwise noted,  $R_S=50\Omega$ ,  $T_A=T_C=25^{\circ}C$ ,  $V_S=\pm15V$  (Notes 3, 4)

| Symbol                           | Parameter                             |                                                        |         | Units                       |                             |                                    |

|----------------------------------|---------------------------------------|--------------------------------------------------------|---------|-----------------------------|-----------------------------|------------------------------------|

|                                  |                                       | Conditions                                             | Typical | Tested<br>Limit<br>(Note 5) | Design<br>Limit<br>(Note 6) | (Max Unless<br>Otherwise<br>Noted) |

| V <sub>OS</sub>                  | Non-Inverting Input<br>Offset Voltage | $V_{IN} = 0V$                                          | ±2      | ±5                          | ± 5                         | mV                                 |

| $\frac{\Delta V_{OS}}{\Delta T}$ | Offset Voltage Drift                  |                                                        | 10      |                             |                             | μV/°C                              |

| l <sub>B</sub>                   | Non-Inverting Input Bias Current      |                                                        | ±5      | ± 25                        | ± 30                        | μΑ                                 |

| v <sub>o</sub>                   | Output Voltage Swing                  | $R_L = 500\Omega$                                      | ±13     | ±11                         | ± 10.5                      | ٧                                  |

| V <sub>O</sub>                   | Output Voltage Swing                  | R <sub>L</sub> = ∞                                     | ±14     | ± 12                        | ± 11.5                      | V (Min)                            |

| lo                               | Output Current Swing                  | $R_L = 50\Omega$ (Note 7)                              |         | ±100                        | ± 100                       | mA                                 |

| CMRR                             | Common Mode<br>Rejection Ratio        | $V_{IN} = -11V \text{ to } +11V,$<br>$V_{S} = \pm 18V$ | 54      | 50                          | 50                          | dB                                 |

| PSRR                             | Power Supply<br>Rejection Ratio       | $\pm V_S = 9V \text{ to } 15V$<br>$\Delta V = 6V$      | 72      | 62                          | 62                          | dΒ                                 |

| Is                               | Quiescent Supply Current              | V <sub>IN</sub> = 0V                                   | 20      | 25                          | 25                          | mA                                 |

| P <sub>D</sub>                   | Quiescent Power Dissipation           | (Note 7)                                               | 600     | 750                         | 750                         | mW                                 |

| CIN                              | Input Capacitance                     |                                                        | 1.5     |                             |                             | pF                                 |

#### **AC Electrical Characteristics**

Unless otherwise noted, Av  $=~+2,\, R_S=~50\Omega,\, R_L=~100\Omega,\, V_S=~\pm\,15V,\, T_A=~25^{\circ}C$

| Symbol          | Parameter                                    | Conditions $V_{OUT} = 0.2  V_{P-P}$                                |                                       | LH4118CG, LH4118AG<br>and LH4118G |                      |                 | Units<br>(Max Unless |

|-----------------|----------------------------------------------|--------------------------------------------------------------------|---------------------------------------|-----------------------------------|----------------------|-----------------|----------------------|

| Symbol          |                                              |                                                                    |                                       | Typical                           | Tested<br>Limit      | Design<br>Limit | Otherwise<br>Noted)  |

| SSBW<br>-3 dB   | Small Signal<br>Bandwidth                    |                                                                    |                                       | 250                               | 200                  |                 | MHz (Min)            |

| PBW -3 dB       | Power Bandwidth                              | V <sub>OUT</sub> = 10 V                                            | P-P                                   | 68                                | 55                   |                 | MHz (Min)            |

| GF              | Gain Flatness                                | V <sub>OUT</sub> =<br>0.2 V <sub>P-P</sub>                         | 0.5 MHz, -50 MHz<br>0.5 MHz, -100 MHz | ±0.3                              |                      |                 | dB (Max)             |

| SR              | Slew Rate<br>LH4118AG<br>LH4118G<br>LH4118CG | V <sub>OUT</sub> = 15 V <sub>P-P</sub><br>20%-80%                  |                                       |                                   | 2400<br>2000<br>1800 |                 | V/μS (Min)           |

| t <sub>r</sub>  | Rise Time                                    | V <sub>OUT</sub> = 10 V <sub>P-P</sub><br>10%-90%                  |                                       | 2.5                               |                      |                 | ns                   |

| V <sub>GC</sub> | -1 dB Gain<br>Compression                    | f = 50 MHz                                                         |                                       | 23.5                              |                      |                 | dBm                  |

| e <sub>n</sub>  | Input Noise<br>Voltage                       | $A_V = 5$ , $R_S = 50\Omega$ ,<br>f = 10 MHz                       |                                       | 1.3                               |                      |                 | nV/√Hz               |

| HD <sub>2</sub> | Second Harmonic<br>Distortion                | V <sub>OC</sub> = 1.27 V <sub>P-P</sub><br>F <sub>C</sub> = 14 MHz |                                       | -58                               |                      |                 | dBc                  |

| HD <sub>3</sub> | Third Harmonic<br>Distortion                 | V <sub>OC</sub> = 1.27 V <sub>P-P</sub><br>F <sub>C</sub> = 14 MHz |                                       | -40                               |                      |                 | dBc                  |

| t <sub>s</sub>  | Settling Time                                | $A_V = -1$<br>$V_{IN} = +5 V_{P-P} \text{ to } 0.1\%$              |                                       | 15                                |                      |                 | ns                   |

| LVBW<br>-3 dB   | Low Supply<br>Voltage Bandwidth              | $V_{OUT} = 0.2 V_{P-P}$ $V_S = \pm 5V$                             |                                       | 230                               |                      |                 | MHz                  |

| LVSR            | Low Supply<br>Voltage Slew Rate              | $V_S = \pm 5V, V_{OUT} = 5 V_{P-P}$<br>20%-80%                     |                                       | 1400                              |                      |                 | V/µs                 |

| DG              | Differential<br>Gain                         | $V_{IN} = \pm 4 V_{DC}$ $0.4 V_{P-P} AC$ $f = 4 MHz$               |                                       | <0.01                             |                      |                 | dB                   |

| PL              | Phase Linearity                              | $V_{IN} = \pm 4 V_{DC}$<br>0.4 $V_{P-P}$ AC, f = 4 MHz             |                                       | <0.1                              |                      |                 | DEG                  |

Note 1: The input signal should be within the supply rails. Also, the input signal as well as the output signal should not be more than 30V from any supply voltage.

Note 2: The average voltage that the weakest pin combinations can withstand and still conform to the datasheet limits. The test circuit used consists of the human body model of 100 pF in series with 1500 $\Omega$ .

Note 3: Boldface limits are guaranteed over full temperature range. Operating ambient temperature range of LH4118CG is -25°C to +85°C, for LH4118G and LH4118AG it is -55°C to 125°C.

Note 4: Specifications are at 25°C junction temperature due to requirements of high speed automatic testing. Actual values at operating temperature will exceed value at T<sub>J</sub> = 25°C.

Note 5: Tested limits are guaranteed and 100% production tested.

Note 6: Design limits are guaranteed (but not production tested) over the indicated temperature or temperature range. These limits are not used to calculate outgoing quality level.

Note 7: When the LH4118 is operated at elevated temperature (such as 125°C), some form of heat sinking or forced air cooling is required. The quiescent power with  $V_S = \pm 15V$  is 750 mW, whereas the package can only handle 550 mW without a heatsink at 125°C.

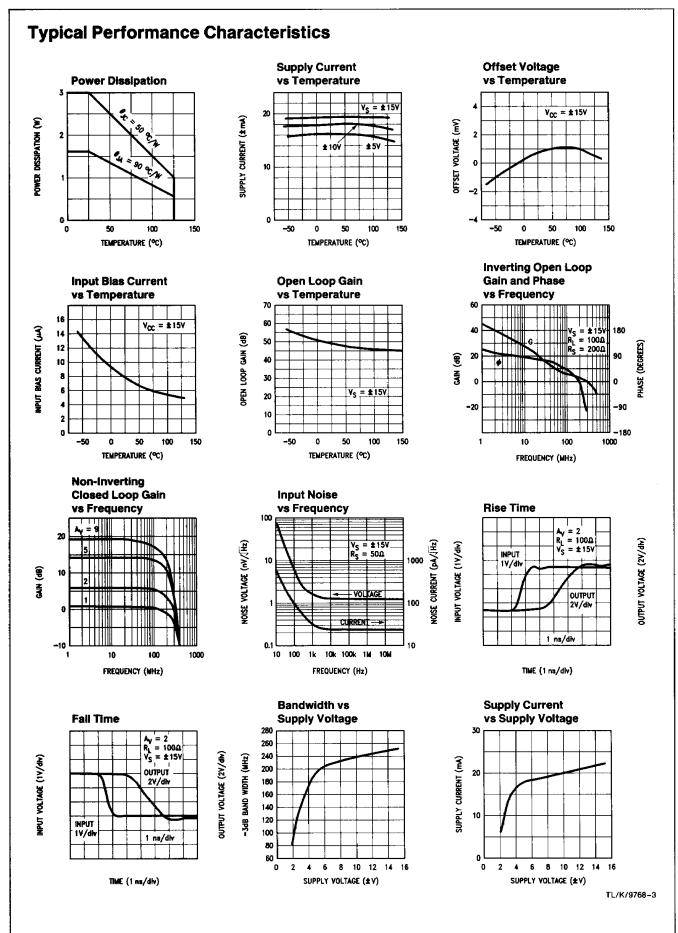

## **Typical Performance Characteristics (Continued)**

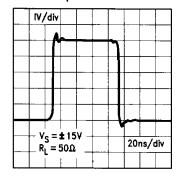

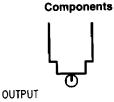

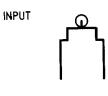

#### **Pulse Response**

OUTPUT VOLTAGE (1V/div)

TIME (20 ns/div)

TL/K/9768-4

## **Applications Information**

#### **LAYOUT**

Breadboards should have a solid ground plane and short point-to-point wiring. Do not use wirewrap boards or techniques. PC boards should have short connections and as much ground plane as possible.

The inputs (Pins 4, 5 & 6) should have low capacitance and, therefore, the ground plane should be taken out around these pins. The body of RG should be close to Pin 5 for the same reason.

It is best to have a layout without sockets, but sockets with short pins and receptacles do not degrade the performance much.

Input and output should be led by coax or microstrip if the distances are more than a few inches to avoid impedance shifts and resulting reflections.

Power supplies need to be bypassed with 0.01  $\mu$ F to 0.1  $\mu$ F as close as 0.15" to the pins and additional 1  $\mu$ F tantalum a maximum 1" distant. Please make sure that the return current from the ground end of R<sub>L</sub> does not flow across the input: the grounding point of R<sub>L</sub> should be close to the grounding points of the power supply bypass capacitors. On the LH4118, this comes almost natural because of the layout of the pins.

The direct non-inverting input on pin 4, if used, should not see impedances of less than  $100\,\Omega.$

The built-in feedback resistor (pin 8) is limited to a maximum dissipation of 150 mW. It can be used for unity gain and for higher gains at lower amplitudes.

#### Input-to-Output Offset Zero Adjust

TL/K/9768-5

This circuit lets the V $_{OS}$  between non-inverting input (pin 6) and output (pin 11) be adjusted. For  $R_G=15\Omega$  the range of adjustment is  $\pm\,11$  mV, for higher  $R_G$  proportionately more. For higher  $R_G$  it is recommended to increase  $R_2$  to decrease the range and make trimming less sensitive.

There is also an offset between inverting and non-inverting input which cannot be trimmed out.

## **Typical Applications**

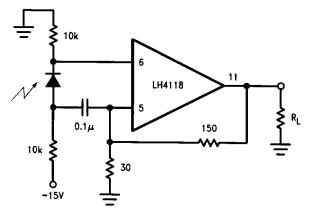

FIGURE 1. Bootstrapped Fiber Optic Receiver

TL/K/9768-6

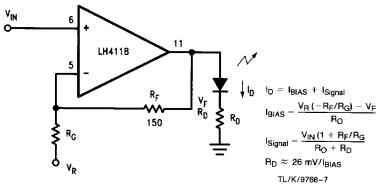

FIGURE 2. Fiber Optic Transmitter

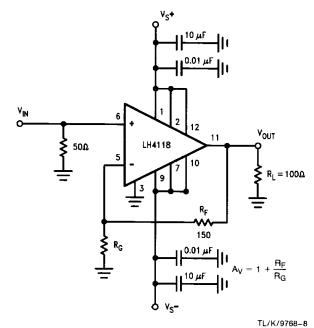

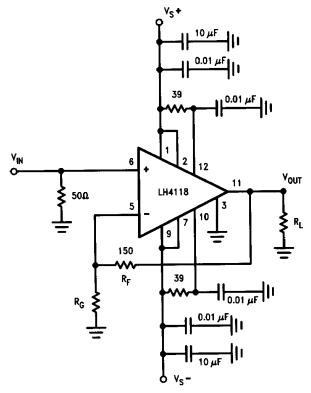

FIGURE 3. Non-Inverting Gain Circuit

$R_i$  is selected so that  $R_i \parallel R_G$  matches the line impedance (e.g., 50 $\Omega$ )

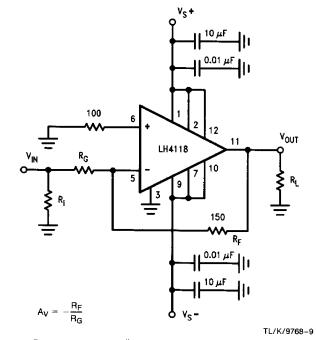

FIGURE 4. Inverting Gain Circuit

# Typical Applications (Continued)

FIGURE 5. Current Limiting Using Resistor

TL/K/9768-10

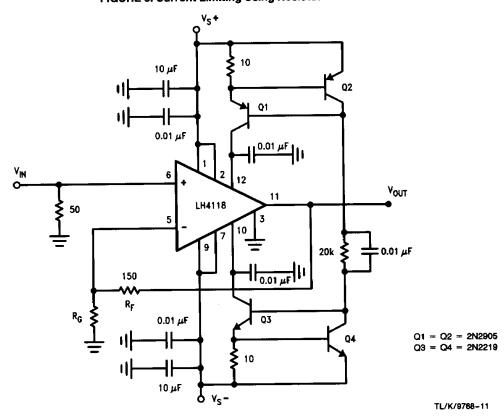

The current cutoff is set to I =  $\frac{\text{VBE}}{\text{R}} = \frac{600 \text{ mV}}{10\Omega} = 60 \text{ mA}$ . Higher current peaks are sustained by the 0.01  $\mu\text{F}$  Capacitors.

FIGURE 6. Current Limiting Using Transistor Current Source

# **Typical Applications (Continued)**

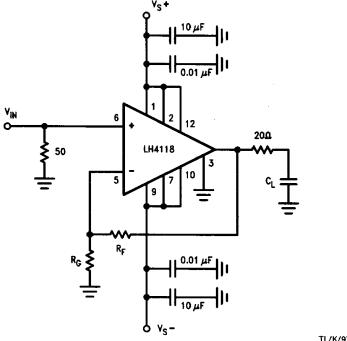

TL/K/9768-12

A series resistor between  $5\Omega$  and  $50\Omega$  helps to stabilize capacitive loads. There is, however, a corresponding drop in bandwidth.

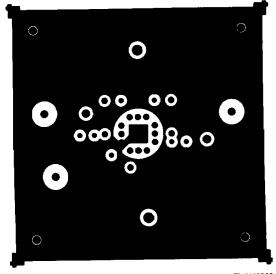

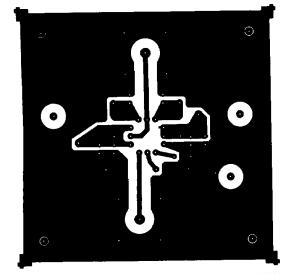

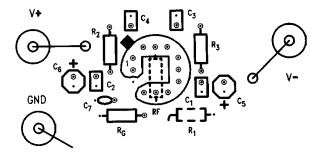

## **Evaluation Board**

(3" x 3", not to scale)

TL/K/9768-13

TL/K/9768--14 **Bottom**

\_

LH4118 DEMO BOARD

TL/K/9768-15

**Top View**

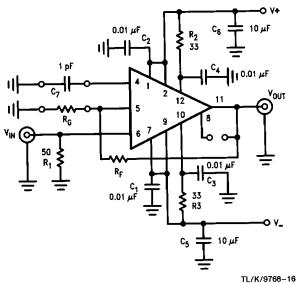

**Schematic Diagram**

16/10/3100-1

Input and output connections are made through BNC connectors. When the indicated cut-outs are made, the connectors can be placed in-line. As an alternative, Amphenol No. 31-4758 connectors can be used soldered upright into the board

R1 is the termination resistor of the input line. It is mounted on the bottom of the board, with one side soldered flat to the center of the input strip-line. The LH4118 can be soldered directly into the board or Holetight pins can be used (Augat part No. 8134-HC-5P2). These pins need plated through holes with a finished inner diameter of 41  $\pm 2$  Mil. For  $A_V=1$  the built-in  $R_F$  (150 $\Omega$ ) can be utilized by bridging the trace between pins 8 and 11. In this case no external  $R_F$  should be used.