# LR38620

### DESCRIPTION

The LR38620 is a CMOS timing generator IC which generates timing pulses for driving 4 200 k-pixel CCD area sensor and processing pulses.

## FEATURES

- Designed for 1/1.8-type 4 200 k-pixel CCD area sensor

- Frequency of driving horizontal CCD : 24.54545 MHz

- In monitoring mode, it can be obtained 30 fields/s

- External shutter control function with serial data input is possible

- +3.3 V and +4.5 V power supplies

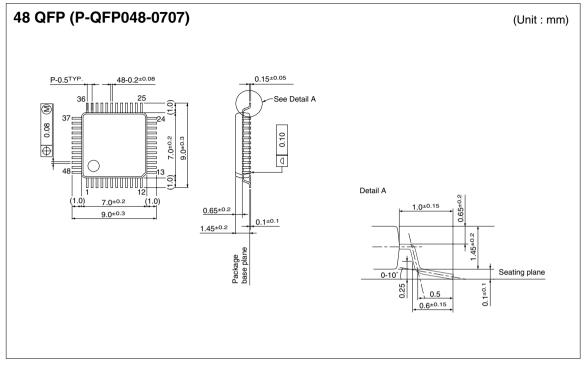

- Package :

48-pin QFP (P-QFP048-0707) 0.5 mm pin-pitch

# Timing Generator IC for 4 200 k-pixel CCD

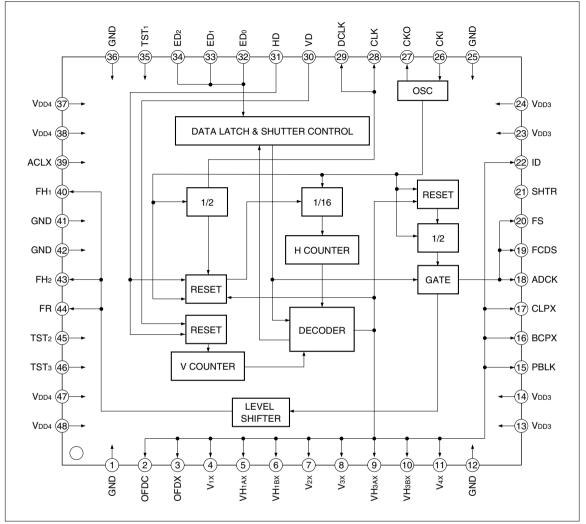

## **PIN CONNECTIONS**

In the absence of confirmation by device specification sheets, SHARP takes no responsibility for any defects that may occur in equipment using any SHARP devices shown in catalogs, data books, etc. Contact SHARP in order to obtain the latest device specification sheets before using any SHARP device.

### **BLOCK DIAGRAM**

## **PIN DESCRIPTION**

| PIN NO. | SYMBOL | IO SYMBOL | POLARITY | PIN NAME                                              | IE DESCRIPTION                                                                                                                                                                                                                                               |  |  |

|---------|--------|-----------|----------|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1       | GND    | _         | _        | Ground                                                | A grounding pin.                                                                                                                                                                                                                                             |  |  |

| 2       | OFDC   | O3MR1     | Л        | Control pulse output for OFD voltage                  | A pulse to control OFD voltage.                                                                                                                                                                                                                              |  |  |

| 3       | OFDX   | O3MR1     | Ţ        | OFD pulse output                                      | A pulse that sweeps the charge of the photo-diode for<br>the electronic shutter. Connect to OFD pin of the CCD<br>through the vertical driver IC and DC offset circuit.<br>Held at H level in normal mode.                                                   |  |  |

| 4       | V1X    | O3MR1     | ſL       | Vertical transfer pulse output 1                      | A vertical transfer pulse for the CCD.<br>Connect to V1x pin of vertical driver IC.                                                                                                                                                                          |  |  |

| 5       | VH1AX  | O3MR1     | T        | Readout pulse<br>output 1A                            | A pulse that transfers the charge of the photo-diode to<br>the vertical shift register.<br>Connect to VH1AX pin of vertical driver IC.                                                                                                                       |  |  |

| 6       | VH1BX  | O3MR1     | Ţ        | Readout pulse<br>output 1B                            | A pulse that transfers the charge of the photo-diode to<br>the vertical shift register.<br>Connect to VH1BX pin of vertical driver IC.                                                                                                                       |  |  |

| 7       | V2X    | O3MR1     | ſL       | Vertical transfer                                     | A vertical transfer pulse for the CCD.                                                                                                                                                                                                                       |  |  |

| 8       | Vзх    | O3MR1     | IJ       | Pulse output 2<br>Vertical transfer<br>pulse output 3 | Connect to V2x pin of vertical driver IC.<br>A vertical transfer pulse for the CCD.<br>Connect to V3x pin of vertical driver IC.                                                                                                                             |  |  |

| 9       | VHзах  | O3MR1     | T        | Readout pulse<br>output 3A                            | A pulse that transfers the charge of the photo-diode to<br>the vertical shift register.<br>Connect to VH3AX pin of vertical driver IC.                                                                                                                       |  |  |

| 10      | VНзвх  | O3MR1     | T        | Readout pulse<br>output 3B                            | A pulse that transfers the charge of the photo-diode to<br>the vertical shift register.<br>Connect to VH3BX pin of vertical driver IC.                                                                                                                       |  |  |

| 11      | V4X    | O3MR1     | U        | Vertical transfer pulse output 4                      | A vertical transfer pulse for the CCD.<br>Connect to V4x pin of vertical driver IC.                                                                                                                                                                          |  |  |

| 12      | GND    | _         | _        | Ground                                                | A grounding pin.                                                                                                                                                                                                                                             |  |  |

| 13      | Vdd3   | _         | -        | Power supply                                          | Supply of +3.3 V power.                                                                                                                                                                                                                                      |  |  |

| 14      | Vdd3   | _         | -        | Power supply                                          | Supply of +3.3 V power.                                                                                                                                                                                                                                      |  |  |

| 15      | PBLK   | ОЗMR1 ]   | Ţ        | Pre-blanking pulse<br>output                          | A pulse for pre-blanking. This pulse is controlled by<br>serial data BLKCNT.<br>BLKCNT = H; This pulse stays low during the<br>absence of effective pixels within the<br>vertical blanking or during the<br>sweepout signal.<br>BLKCNT = L; Continuous pulse |  |  |

|         |        |           |          |                                                       | The output phase of PBLK is selected by serial data.                                                                                                                                                                                                         |  |  |

| PIN NO. | SYMBOL         | IO SYMBOL | POLARITY           | PIN NAME                                                | DESCRIPTION                                                  |                                             |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                          |

|---------|----------------|-----------|--------------------|---------------------------------------------------------|--------------------------------------------------------------|---------------------------------------------|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|----------------------------------------------------------|

|         |                |           |                    |                                                         | A pulse to clamp the optical black signal.                   |                                             |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                          |

|         |                |           |                    |                                                         | This pulse is controlled by serial data BCPCNT.              |                                             |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                          |

|         |                |           |                    |                                                         | BCPCNT = H; This pulse stays high during the                 |                                             |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                          |

|         |                |           |                    | Optical black clamp                                     | absence of effective pixels within the                       |                                             |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                          |

| 16      | BCPX           | O3MR1     | T                  | pulse output                                            | vertical blanking or during the                              |                                             |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                          |

|         |                |           |                    |                                                         | sweepout signal.                                             |                                             |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                          |

|         |                |           |                    |                                                         | BCPCNT = L; This pulse stays high during the                 |                                             |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                          |

|         |                |           |                    |                                                         | sweepout signal.                                             |                                             |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                          |

|         |                |           |                    |                                                         | A pulse to clamp the dummy outputs of the CCD signal.        |                                             |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                          |

| 17      | CLPX           | O3MR1     | T                  | Clamp pulse output                                      | This pulse stays high during the sweepout period.            |                                             |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                          |

|         |                |           |                    |                                                         | An output pin for AD converter. The output phase of          |                                             |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                          |

| 18      | ADCK           | O6M32     | ГЛ                 | AD clock output                                         | ADCK is selected by serial data in 90° steps.                |                                             |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                          |

|         |                |           | П                  |                                                         | A pulse to clamp the feed-through level for the CCD.         |                                             |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                          |

| 19      | FCDS           | O6M32     |                    | CDS pulse output 1                                      | The output phase and output polarity of FCDS are             |                                             |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                          |

|         |                |           | T                  |                                                         | selected by serial data.                                     |                                             |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                          |

|         |                |           | L                  |                                                         | A pulse to sample-hold the signal for the CCD.               |                                             |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                          |

| 20      | FS             | O6M32     |                    | CDS pulse output 2                                      |                                                              |                                             |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                          |

|         | -              |           | T                  |                                                         | by serial data.                                              |                                             |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                          |

| 21      | SHTR           | O3MR1     | Π                  | Trigger output                                          | A trigger pulse for effective signal period.                 |                                             |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                          |

|         |                |           |                    | Line index pulse                                        | The pulse is used in the color separator.                    |                                             |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                          |

| 22      | ID O3MR1 ]]    |           | output             | The signal switches between high and low at every line. |                                                              |                                             |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                          |

| 23      | Vdd3           | _         | _                  | Power supply                                            | Supply of +3.3 V power.                                      |                                             |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                          |

| 24      | Vdd3           | _         | _                  | Power supply                                            | Supply of +3.3 V power.                                      |                                             |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                          |

| 25      | GND            | -         | _                  | Ground                                                  | A grounding pin.                                             |                                             |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                          |

|         | 0.4            | 00010     |                    | <b>0</b> , , , , ,                                      | An input pin for reference clock oscillation.                |                                             |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                          |

| 26      | CKI            | OSCI3     | -                  | Clock input                                             | The frequency is 49.0909 MHz.                                |                                             |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                          |

| 07      | 01/0           | 00000     |                    |                                                         | An output pin for reference oscillation.                     |                                             |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                          |

| 27      | СКО            | OSCO3     | -                  | Clock output                                            | The output is the inverse of CKI (pin 26).                   |                                             |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                          |

| 00      |                | 001400    | 0.01400            | пг                                                      |                                                              | An output pin to generate HD and VD pulses. |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                          |

| 28      | CLK            | O6M32     | Л                  | Clock output                                            | The frequency is 24.54545 MHz.                               |                                             |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                          |

|         |                |           |                    |                                                         |                                                              |                                             |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  | An output pin for DSP IC. The frequency is 24.54545 MHz. |

| 29      | DCLK           | O6M32     | Л                  | Clock output                                            | The output phase of DCLK is selected by serial data in       |                                             |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                          |

|         |                |           |                    |                                                         | 90° steps.                                                   |                                             |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                          |

| 00      |                | 100       |                    | Vertical reference                                      | An input pin for reference of vertical pulse.                |                                             |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                          |

| 30      | VD             |           |                    | pulse input                                             | Connect to VD pin of DSP IC.                                 |                                             |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                          |

| 0.1     |                | 100       |                    | Horizontal drive                                        | An input pin for reference of horizontal pulse.              |                                             |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                          |

| 31      | HD             | IC3       |                    | pulse input                                             | Connect to HD pin of DSP IC.                                 |                                             |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                          |

| 20      | EDa            | 10000     |                    | Strobo pulso input                                      | An input pin for the strobe pulse, to control the functions  |                                             |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                          |

| 32      | 32 ED0 ICSD3 - |           | Strobe pulse input | of LR38620. For details, see "Serial Data Control".     |                                                              |                                             |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                          |

|         | ED1            |           |                    | Shift register cleak                                    | An input pin for the clock of the shift register, to control |                                             |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                          |

| 33      |                | ICSD3     | 93 –               | Shift register clock                                    | the functions of LR38620. For details, see "Serial Data      |                                             |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                          |

|         |                |           |                    | input                                                   | Control".                                                    |                                             |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                                          |

| Pin No.     | SYMBOL           | IO SYMBOL | POLARITY | PIN NAME                              | DESCRIPTION                                                                                                                           |  |  |

|-------------|------------------|-----------|----------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 34          | ED2              | ICSD3     | _        | Shift register data input             | An input pin for the data of the shift register, to control the functions of LR38620. For details, see <b>"Serial Data Control"</b> . |  |  |

| 35          | TST1             | ICD3      | -        | Test pin 1                            | A test pin. Set open or to L level in normal mode.                                                                                    |  |  |

| 36          | GND              | -         | Ι        | Ground                                | A grounding pin.                                                                                                                      |  |  |

| 37          | Vdd4             | -         | Ι        | Power supply                          | Supply of +4.5 V power.                                                                                                               |  |  |

| 38          | Vdd4             | -         | -        | Power supply                          | Supply of +4.5 V power.                                                                                                               |  |  |

| 39          | ACLX             | ICU4      | -        | All clear input                       | An input pin for resetting all internal circuit at power-on.<br>Connect to VDD3 through the diode and GND through<br>the capacitor.   |  |  |

| 40          | FH1              | O8M43     | $\prod$  | Horizontal transfer<br>pulse output 1 | A horizontal transfer pulse for the CCD.<br>Connect to $\phi_{H1}$ pin of the CCD.                                                    |  |  |

| 41          | GND              | _         | -        | Ground                                | A grounding pin.                                                                                                                      |  |  |

| 42          | GND              | _         | -        | Ground                                | A grounding pin.                                                                                                                      |  |  |

| 43          | FH2              | O8M43     | N        | Horizontal transfer pulse output 2    | A horizontal transfer pulse for the CCD.<br>Connect to $\phi_{H2}$ pin of the CCD.                                                    |  |  |

| 44          | FR               | O8M43     | L        | Reset pulse output                    | A pulse to reset the charge of output circuit.<br>The output phase of FR is selected by serial data.                                  |  |  |

| 45          | TST <sub>2</sub> | ICD4      | -        | Test pin 2                            | A test pin. Set open or to L level in normal mode.                                                                                    |  |  |

| 46          | TST3             | ICD4      | -        | Test pin 3                            | A test pin. Set open or to L level in normal mode.                                                                                    |  |  |

| 47          | VDD4             | -         | -        | Power supply                          | Supply of +4.5 V power.                                                                                                               |  |  |

| 48          | Vdd4             | _         | Ι        | Power supply                          | Supply of +4.5 V power.                                                                                                               |  |  |

| IC3<br>ICD3 |                  |           |          |                                       |                                                                                                                                       |  |  |

O8M43

OSCI3

: Output pin (output high level is VDD4.)

: Input pin for oscillation

OSCO3 : Output pin for oscillation

ICSD3 : Input pin (CMOS schmitt-trigger level with pulldown resistor)

ICD4 : Input pin (CMOS level with pull-down resistor)

ICU4 : Input pin (CMOS level with pull-up resistor)

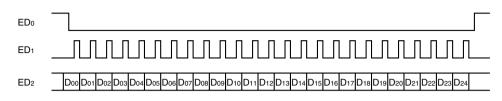

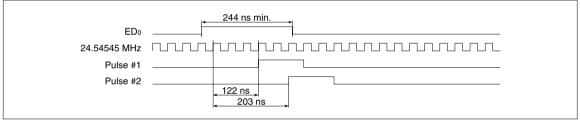

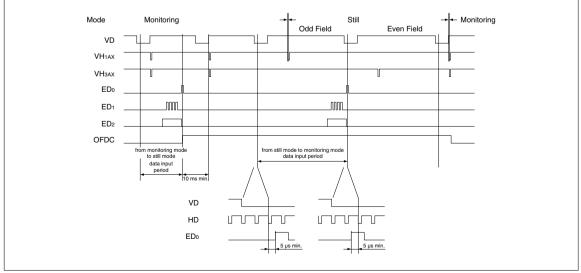

#### Serial Data Control SERIAL DATA INPUT TIMING

ED2 is shifted by the rising edge of ED1, and is latched by the pulse #1 which is generated after 122 to 162 ns delay from the rising edge of ED0. (See **Fig. 2**.)

The latched serial data are divided into two types by the data of Doo, and are relatched by the pulse #2 which is generated after 203 to 243 ns delay from the rising edge of EDo. (See **Fig. 1**.) INMD is effective at the start of #3 horizontal line, and shutter control data are effective at the start of #11 horizontal line in monitoring mode and #93 horizontal line in still mode, and other data are effective at pulse #2.

ED<sub>0</sub> should be at low level during data inputs of ED<sub>1</sub> and ED<sub>2</sub> or while ACLX is at low level.

Fig. 1 Data Latch Timing

#### SERIAL DATA INPUTS

| D00 = | L |

|-------|---|

|-------|---|

| DATA    | NAME                               | FUNCTION                          | DATA = L                         | DATA = H        | AT ACLX = L |

|---------|------------------------------------|-----------------------------------|----------------------------------|-----------------|-------------|

| D01-D09 | SDV0-SDV8                          | Integration time control in field |                                  | All L           |             |

| D01-D09 | 500-5008                           | period step by horizontal period. | eriod step by horizontal period. |                 |             |

| D10-D15 | SDH <sub>0</sub> -SDH <sub>5</sub> | Dummy                             | Fix to                           | All L           |             |

| D16     | SDF0                               | Integration time control by field |                                  |                 |             |

| D17     | SDF1                               | Integration time control by field | -                                | All L           |             |

| D18     | SDF2                               | period.                           |                                  |                 |             |

| D19     | SMD                                | Electronic shutter mode control   | -                                | L               |             |

| D20     | PWSA                               | Power save control                | Normal                           | Power save      | L           |

| D21     | INMD                               | Integration mode control          | Monitoring                       | Still           | L           |

| D22     | Dummy                              | Dummy                             | Fix to L level                   |                 | L           |

| D23     | Dummy                              | Dummy                             | Fix to L level                   |                 | L           |

| D24     | VHCNT                              | VH1AX to VH3BX control            | Output                           | Held at H level | L           |

| Doo = H<br>DATA | NAME   | FUNCTION                               | DATA = L   | DATA = H      | AT ACLX = L |  |

|-----------------|--------|----------------------------------------|------------|---------------|-------------|--|

| D01             | ML1    |                                        |            |               |             |  |

| D02             | ML2    |                                        | · ·        | All L         |             |  |

| D03             | MR1    |                                        |            |               |             |  |

| D04             | MR2    |                                        |            | All L         |             |  |

| D05             | MR3    |                                        |            |               |             |  |

| D06             | MC1    |                                        |            |               |             |  |

| D07             | MC2    |                                        |            | All L         |             |  |

| D08             | MC3    |                                        |            |               |             |  |

| D09             | MS1    | Phase control                          |            |               |             |  |

| D10             | MS2    |                                        |            | All L         |             |  |

| D11             | MS3    | _                                      |            |               |             |  |

| D12             | MD1    | _                                      |            |               |             |  |

| D13             | MD2    | _                                      |            | All L         |             |  |

| D14             | MD3    |                                        |            |               |             |  |

| D15             | MA1    |                                        |            | A II 1        |             |  |

| D16             | MA2    |                                        |            | All L         |             |  |

| D17             | Dummy  |                                        |            | All L         |             |  |

| D18             | Dummy  | Dummy                                  | Fix to     |               |             |  |

| D19             | Dummy  |                                        |            |               |             |  |

| D20             | MP1    | Dhana control                          |            |               | A II 1      |  |

| D21             | MP2    | Phase control                          |            | All L         |             |  |

| D22             | PLCH   | Polarity control of FCDS and FS pulses | Negative   | Positive      | L           |  |

| D23             | BLKCNT | PBLK control                           | Continuous | Discontinuous | L           |  |

| D24             | BCPCNT | BCPX control                           | Continuous | Discontinuous | L           |  |

#### **ABSOLUTE MAXIMUM RATINGS**

| PARAMETER             | SYMBOL     | RATING             | UNIT |

|-----------------------|------------|--------------------|------|

| Supply voltage        | Vdd3, Vdd4 | -0.3 to +5.5       | V    |

| Input voltage         | Vıз        | -0.3 to VDD3 + 0.3 | V    |

| input voltage         | VI4        | -0.3 to VDD4 + 0.3 | V    |

| Output voltage        | Vo3        | -0.3 to VDD3 + 0.3 | V    |

| Output voltage        | VO4        | -0.3 to VDD4 + 0.3 | V    |

| Operating temperature | TOPR       | -20 to +70         | °C   |

| Storage temperature   | Tstg       | -55 to +150        | °C   |

# **ELECTRICAL CHARACTERISTICS**

#### **DC Characteristics**

$(VDD3 = 3.3 \pm 10\%, VDD4 = 4.5 \pm 10\%, TOPR = -20 \text{ to } +70^{\circ}\text{C})$

| PARAMETER             | SYMBOL    | CONDITIONS     | MIN.       | TYP. | MAX.     | UNIT | NOTE |

|-----------------------|-----------|----------------|------------|------|----------|------|------|

| Input "Low" voltage   | VIL3-1    |                |            |      | 0.2VDD3  | V    | 1.0  |

| Input "High" voltage  | VIH3-1    |                | 0.8VDD3    |      |          | V    | 1, 2 |

| Input "Low" voltage   | VIL3-2    |                | 0.2VDD3    |      |          | V    |      |

| Input "High" voltage  | VIH3-2    | Schmitt-buffer |            |      | 0.75Vdd3 | V    | 3    |

| Hysteresis voltage    | Vt+ – Vt- |                | 0.14Vdd3   |      |          | V    |      |

| Input "Low" voltage   | VIL4      |                |            |      | 0.2VDD4  | V    | 4 5  |

| Input "High" voltage  | VIH4      |                | 0.8VDD4    |      |          | V    | 4, 5 |

| Input "Low" current   | IIL3-1    | VI = 0 V       |            |      | 1.0      | μA   | -    |

| Input "High" current  | IIH3-1    | VI = VDD3      |            |      | 1.0      | μA   | 1    |

| Input "Low" current   | IIL3-2    | VI = 0 V       |            |      | 3.0      | μA   | 0.0  |

| Input "High" current  | Іінз-2    | VI = VDD3      | 8.0        |      | 100      | μA   | 2, 3 |

| Input "Low" current   | IIL4-1    | VI = 0 V       | 20         |      | 300      | μA   | - 4  |

| Input "High" current  | IIH4-1    | VI = VDD4      |            |      | 5.0      | μA   | 4    |

| Input "Low" current   | IIL4-2    | VI = 0 V       |            |      | 5.0      | μA   | - 5  |

| Input "High" current  | IIH4-2    | VI = VDD4      | 20         |      | 300      | μA   | 5    |

| Output "Low" voltage  | VOL3-1    | IOL = 3 mA     |            |      | 0.4      | V    | 6    |

| Output "High" voltage | Vонз-1    | Іон = -2.5 mA  | VDD3 - 0.5 |      |          | V    | 6    |

| Output "Low" voltage  | VOL3-2    | IoL = 12 mA    |            |      | 0.4      | V    | 7    |

| Output "High" voltage | Vонз-2    | Iон = -10 mA   | Vdd3 - 0.5 |      |          | V    | ] /  |

| Output "Low" voltage  | VOL4      | IoL = 20 mA    |            |      | 0.4      | ٧    | 0    |

| Output "High" voltage | Vон4      | Іон = –20 mA   | VDD4 - 0.5 |      |          | V    | 8    |

#### NOTES :

- 1. Applied to inputs (IC3, OSCI3).

- 2. Applied to input (ICD3).

- 3. Applied to input (ICSD3).

- 4. Applied to input (ICU4).

- 5. Applied to input (ICD4).

- Applied to outputs (OSCO3, O3MR1). (Output (OSCO3) measures on condition that input (OSCI3) level is 0 V or VDD3.)

- 7. Applied to output (O6M32).

- 8. Applied to output (O8M43).

## PACKAGE OUTLINES