T-52-33-13

# DESCRIPTION

The M5M82C59AP,-2 is a programmable LSI for interrupt control. It is fabricated using sflicon-gate CMOS technology and is designed to be used easily in connection with an 8085A, 8086 or 8088.

## **FEATURES**

- Single 5V supply voltage

- TTL compatible

- Having internal anti-noise circuit on IR<sub>2</sub>~IR<sub>7</sub> pins

- M5M82C59AP,-2 is compatible with M5L8259AP in pin connection.

- CALL instruction to the CPU is generated automatically

- Priority, interrupt mask and vectored address for each interrupt request input are programmable

- Up to 64 levels of interrupt requests can be controlled by cascading with M5M82C59AP,-2

- Polling functions

## APPLICATION

The M5M82C59AP,-2 can be used as an interrupt controller for CPUs 8085A, 8086 and 8088

## FUNCTION

The M5M82C59AP,-2 is a device specifically designed for use in real time, interrupt driven microcomputer systems. It manages eight level requests and has built-in features for expandability to other M5M82C59AP,-2's. The priority and interrupt mask can be changed or reconfigured at any time by

the main program.

When an interrupt is generated because of an interrupt request at 1 of the pins, the M5M82C59AP,-2 based on the mask and priority will output an INT to the CPU. After that, when an INTA signal is received from the CPU or the system controller, a CALL instruction and a programmed vector address is released onto the data bus.

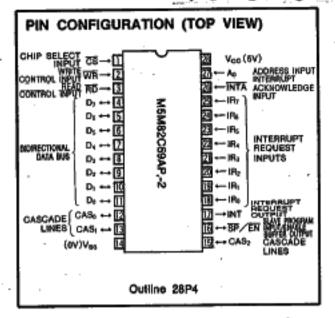

# PIN DESCRIPTION

T-62-33-13

| Symbol                           | Pin name                                     | Input or output  | . Functional significance                                                                                                                                                                                                                                                                                                                                                |

|----------------------------------|----------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CS                               | Chip select input                            | Input            | This input is active at low-level, but may be at high-level during interrupt request input and interrupt processing.                                                                                                                                                                                                                                                     |

| WA                               | Write control input                          | input            | Command write control input from the CPU                                                                                                                                                                                                                                                                                                                                 |

| RD                               | Read control input                           | Isput            | Data read control legat for the CPU                                                                                                                                                                                                                                                                                                                                      |

| Dy~Do                            | Bidirectional data bus                       | Input/<br>output | Date and commands are transmitted through this bidirectional data bus to and from the CPU,                                                                                                                                                                                                                                                                               |

| CAS <sub>2</sub> ~               | Osscade lines                                | imput/<br>oviput | These pins are outputs for a master and inputs for a slave. And those pins of the master will be able to address each individual slave. The master will anable the corresponding slave to release the device routine address during bytes 2 and 3 of INTA.                                                                                                               |

| 8P/EN                            | Slave program input/<br>Enable buffer output | Input/<br>output | SP: In normal mode, a master is designated when SP/EN=1 and a slave is designated when SP/EN=0.  EN: In the buffered mode, whenever the M5M82CS9AP,-2's data bus output is enabled, its SP/EN pie will go low.                                                                                                                                                           |

| INT                              | Inferrupt request output                     | Output           | This pin goes high whenever a voild interrupt is assetted.                                                                                                                                                                                                                                                                                                               |

| iR <sub>7</sub> ∼iR <sub>0</sub> | leterrupt request input                      | Input            | The asynchronous interrupt inputs are solive at high-level. The interrupt mask and priority of each interrupt input can be changed at any time. When using edge triggered mode, the rising edge (low to high) of the interrupt request and the high-level must be held until the first INTA. For level triggered mode, the high-level must be held until the first INTA. |

| INTA                             | Interrupt acknowledge<br>Input               | Input            | When an interrupt acknowledge (INTA) from the CPU is received, the M5M82C59AP releases a CALL in-<br>struction or vectored address onto the data bus.                                                                                                                                                                                                                    |

| A <sub>0</sub>                   | A <sub>0</sub> address isput                 | Input            | This pin is normally connected to one of the address lines and sets in conjunction with the CS, WR and RD when writing commands or reading states registers.                                                                                                                                                                                                             |

# **OPERATION**

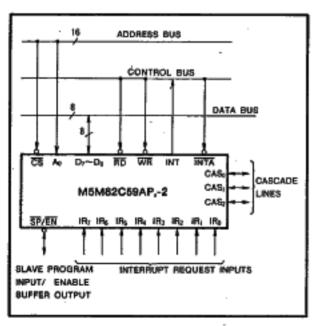

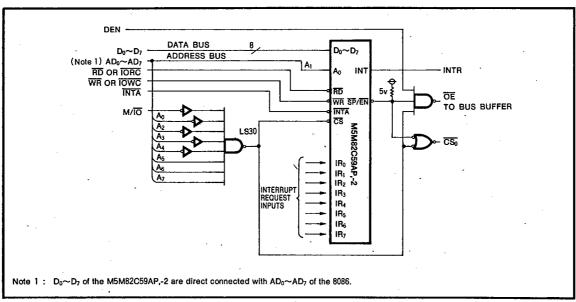

The M5M82C59AP,-2 is interfaced with a standard system bus as shown in Fig. 1 and operates as an interrupt controller.

Fig. 1 The M5M82C59AP,-2 Interfaces to standard system bus.

## Table 1 M5M82C59AP,-2 basic operation

| Αo   | D4 | D3 | RD  | WR | C8 | . Input operation (read)                |

|------|----|----|-----|----|----|-----------------------------------------|

| 0    |    |    | 0   | 1  | 0  | IRR, ISR or interrupting level-data bus |

| 1    |    |    | 0   | 1  | 0  | IMR-Data bus                            |

|      |    |    |     |    |    | Output operation (write)                |

| 0    | 0  | ٥  | 1   | 0  | 0  | Data bus→OCW2                           |

| 0    | 0  | 1  | 1   | 0  | 0  | Data bus→OCW3                           |

| 0    | 1  | ×  | 1   | ٥  | ۰  | Data bus→tCW1                           |

| Li I | x  | ×  | 1   | 0  | 0. | Data bas→OCW1, ICW2, ICW3, ICW4         |

|      |    |    |     |    |    | Disable function                        |

| х    | х  | ×  | 1 - | 1  | 0  | Date bus→High-Impedance                 |

| x    | х  | х  | х   | x  | 1  | Data bus-High-impedance                 |

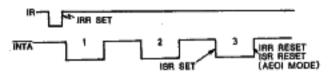

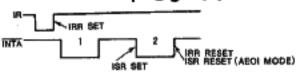

Interrupt Sequence

# 1. When the CPU is an 8085A:

- When one or more of the interrupt request inputs are raised high, the corresponding IRR bit(s) for the highlevel inputs will be set.

- (2) Mask state and priority levels are considered and, if appropriate, the M5M82C59AP,-2 sends an INT signal to the CPU.

- (3) The acknowledgement of the CPU to the INT signal, the CPU issues an INTA pulse to the M5M82C59AP,-2.

- (4) Upon receiving the first INTA pulse from the CPU, a CALL instruction is released onto the data bus.

- (5) A CALL is a 3-byte instruction, so additional two INTA pulses are issued to the M5M82C59AP,-2 from the CPU.

- (6) These two INTA pulses allow the M5M82C59AP,-2 to release the program address onto the data bus. The low-order 8-bit vectored address is released at the second INTA pulse and the high-order 8-bit vectored address is released at the third INTA pulse. The ISR bit corresponding to the interrupt request input is set upon receiving the third INTA pulse from the CPU, and the corresponding IRR bit is reset.

- (7) This completes the 3-byte CALL instruction and the interrupt routine will be serviced. The ISR bit is reset at the trailing edge of the third INTA pulse in the AEOI mode. In the other modes the ISR bit is not reset until an EOI command is issued.

# 2. When the CPU is an 8085 or 8088;

- When one or more of the interrupt request inputs are raised high, the corresponding IRR bit(s) for the highlevel inputs will be set.

- (2) Mask state and priority levels are considered and if appropriated, the M5M82C59AP,-2 sends an INT signal to the CPU.

- (3) As an acknowledgement to the INT signal, the CPU Issues an INTA pulse to the M5M82O59AP,-2.

- (4) Upon receiving the first INTA pulse from the CPU, the M5M82C59AP,-2 does not drive the data bus, and the data bus keeps high-impedance state.

- (5) When the second INTA pulse is issued from the CPU, an 8-bit pointer is released onto the data bus.

- (6) This completes the interrupt cycle and the interrupt routine will be serviced. The ISR bit is reset at the trailing edge of the second INTA pulse in the AEOI mode. In the other modes the ISR bit is not reset until an EOI command is issued from the CPU.

T-52-33-13

The interrupt request input must be held at high-level until the first INTA pulse is issued. If it is allowed to return to low-level before the first INTA pulse is issued, an interrupt request in IR<sub>7</sub> is executed. However, in this case the ISR bit is not set.

This is a function for a noise countermeasure of interrupt request inputs. In the interrupt routine of IR<sub>7</sub>, if ISR is checked by software either the interrupt by noise or real interrupt can be acknowledged. In the state of edge trigger mode normally the interrupt request inputs hold high-level and its input low-level pulse in the case of interrupt.

# Interrupt sequence outputs

# 1. When the CPU is an 8085A:

A CALL instruction is released onto the data bus when the first INTA pulse is issued. The low-order 8 bits of the vectored address are released when the second INTA pulse is issued, and the high-order 8 bits are released when the third INTA pulse is issued. The format of these three outputs is shown in Table 2.

Table 2 Formats of Interrupt CALL instruction and vectored address

First INTA pulse (CALL Instruction)

| D, | De | Da | $D_4$ | D <sub>3</sub> | $D_2$ | Dı | D <sub>0</sub> |

|----|----|----|-------|----------------|-------|----|----------------|

| 1  | 1  | 0  | 0     | 1              | 1     | 0  | . 1            |

Second INTA pulse (low-order 8-bit of vectored address)

| IR              |                |                |                | Interv | si= 4          |                |                |    |

|-----------------|----------------|----------------|----------------|--------|----------------|----------------|----------------|----|

|                 | D <sub>7</sub> | D <sub>6</sub> | D <sub>5</sub> | D4     | D <sub>3</sub> | D <sub>2</sub> | D <sub>1</sub> | Do |

| IR <sub>0</sub> | A <sub>7</sub> | A <sub>6</sub> | As             | 0      | . 0            | 0              | 0              | 0  |

| IR.             | , Az           | As             | - As           | 0      | 0              | 1              | 0              | 0  |

| IR <sub>4</sub> | Ar             | 4              | A <sub>6</sub> | 0      | 1              | 0              | 0              | 0  |

| IP <sub>0</sub> | A <sub>7</sub> | ٨.             | Α,             | 0      | 1              | 1              | 0              | 0  |

| IR <sub>4</sub> | A7             | Ac             | A <sub>5</sub> | 1      | 0              | 0              | 0              | 0  |

| IR <sub>6</sub> | A <sub>7</sub> | Ao             | A <sub>5</sub> | 1      | 0              | 1              | 0              | 0  |

| IR₀             | Ay             | As             | As             | 1      | 1              | 0              | 0              | 0  |

| IR <sub>2</sub> | A <sub>7</sub> | As             | Α.             | 1      | 1              | 1              | 0              | ò  |

T-52-33-13

| IR              |                |    |    | Inter | t=lov |    |                |     |

|-----------------|----------------|----|----|-------|-------|----|----------------|-----|

|                 | D <sub>7</sub> | Dq | Ds | D4    | Da    | D₂ | D <sub>1</sub> | Do  |

| IP <sub>0</sub> | A <sub>7</sub> | As | 0  | 0     | .0    | 0  | 0              | 0   |

| IH.             | A7             | As | 0  | 0     | 1     | 0  | 0              | . 0 |

| IR <sub>2</sub> | A7             | As | 0  | 1     | 0     | 0  | 0              | 0   |

| IR <sub>3</sub> | A7             | As | 0  | 1     | 1     | 0  | 0              | 0   |

| IR <sub>4</sub> | A <sub>7</sub> | As | 1  | 0     | 0     | 0  | 0              | 0   |

| IR <sub>s</sub> | Α,             | Ac | 1  | 0     | 1     | 0  | 0              | 0   |

| IR <sub>o</sub> | A <sub>7</sub> | As | 1  | 1     | 0     | 0  | . 0            | 0   |

| IR <sub>7</sub> | Ag             | As | 1  | 1     | 1     | 0  | 0              | . 0 |

Third INTA pulse (high-order 8 bits of vectored address)

|   | D <sub>7</sub>  | D <sub>6</sub> | D <sub>6</sub> | D <sub>4</sub> | D <sub>1</sub> | D <sub>2</sub> | Di | Do |

|---|-----------------|----------------|----------------|----------------|----------------|----------------|----|----|

| 1 | A <sub>15</sub> | Au             | Aia            | Ana            | Ais            | Ato            | ۸, | Ae |

### 2. When the CPU is an 8086 or 8088;

The data bus keeps a high-impedance state when the first  $\overline{\text{INTA}}$  pulse is issued. Then the pointer  $T_2 \sim T_0$  is released when the next  $\overline{\text{INTA}}$  pulse is issued. The content of the pointer  $T_2 \sim T_0$  is shown in Table 3. The  $T_2 \sim T_0$  are a binary code corresponding to the interrupt request level,  $A_{10} \sim A_6$  are unused and ADI mode control is ignored.

Table 3 Contents of interrupt pointer Second INTA pulse (8-bit pointer)

|                 | D <sub>7</sub>        | D <sub>6</sub> | Do             | D4             | D <sub>3</sub> | D <sub>2</sub> | Dı  | Do    |

|-----------------|-----------------------|----------------|----------------|----------------|----------------|----------------|-----|-------|

| IR <sub>P</sub> | <b>T</b> 7            | T <sub>6</sub> | Ts             | T4             | Ta             | 0              | 0   | 0     |

| IRI             | T <sub>7</sub>        | To             | T <sub>5</sub> | T <sub>4</sub> | Ta             | 0              | 0   | 1     |

| IR₂             | Ty                    | T <sub>6</sub> | T <sub>5</sub> | Te             | Ta             | 0              | - 1 | 0     |

| IR <sub>3</sub> | <b>T</b> <sub>7</sub> | Te             | Te             | T <sub>4</sub> | T <sub>3</sub> | 0              | 1   | i     |

| IR <sub>4</sub> | T <sub>7</sub>        | Te             | Тв             | T4             | Tı             | 1              | 0   | 0     |

| IR <sub>5</sub> | Т7                    | Тв             | Τg             | T4             | T <sub>3</sub> | 1              | 0   | . 1 . |

| IR <sub>s</sub> | T <sub>7</sub>        | Τs             | T <sub>6</sub> | T4             | Tı             | 1              | 1   | 0     |

| IR <sub>2</sub> | T <sub>7</sub>        | T <sub>6</sub> | T <sub>S</sub> | T <sub>4</sub> | Ts             | 1              | 1   | 1     |

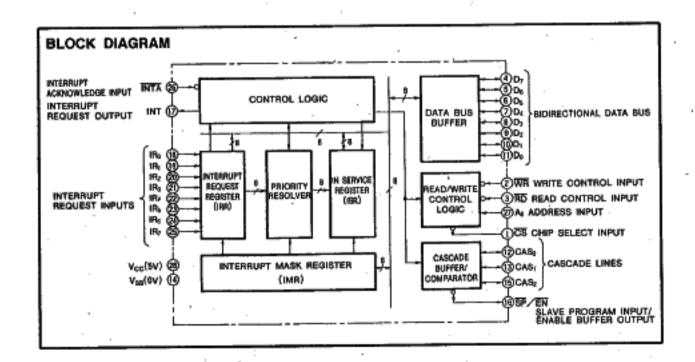

# Interrupt Request Register (IRR), In-service Register (ISR)

As interrpt requests are received at inputs IR<sub>2</sub>~IR<sub>0</sub>, the corresponding bits of IRR are set and as an interrupt request is serviced the corresponding bit of ISR is set. The IRR is used to store all the interrupt levels which are requesting service, and the ISR is used to store all the interrupt levels which are being serviced. The status of these two registers can be read. These two registers are connected through the priority resolver.

An interrupt requet received by IRn is acknowledged on the leading edge when in the edge triggered mode or it is acknowledged on the level when in the level triggered mode. After that an INT signal is released and the interrupt request

signal is latched in the corresponding IRR bit if the highlevel is held until the first INTA pulse is issued. It is important to remember that the interrupt request signal must be held at high-level until the first INTA pulse is issued.

The interrupt request latching in the IRR causes a signal to be sent to the priority resolver unless it is masked out. When the priority resolver receives the signals it selects the highest priority interrupt request latched in IRR. The ISR is set when the last INTA pulse is issued while the corresponding bit of IRR is reset and the other bits of IRR are unaffected.

The bit of ISR that was set is not reset during the interrupt routine, but is reset at the end of the routine by the EOI command (end of interrupt) or by the trailing edge of the last INTA pulse in AEOI mode.

### Priority Resolver

The priority resolver examines all of the interrupt requests set in IRR to determine and selects the highest priority. The ISR bit corresponding to the selected (highest priority) request is set by the last INTA pulse.

### Interrupt Mask Register (IMR)

The contents of the interrupt mask register are used to mask out (disable) interrupt requests of selected interrupt request pins. Each terminal is independently masked so that masking a high priority interrupt does not influence the lower or higher priority interrupts. Therefore the contents of IMR selectively enable reading.

### Interrupt Request Output (INT)

The interrupt request output connects directly to the interrupt input of the CPU. The output level is compatible with the input level required for the CPUs.

The INT output is set to low after the Interrupt sequence ends, irrespective of the current mode. When the power is turned on, the INT output (high output) may appear but is reset to low by executing ICWI.

# Interrupt Acknowledge Input (INTA)

The CALL instruction and vectored address are released onto the data bus by the INTA pulse.

### Data Bus Buffer

The data bus buffer is a 3-state bidirectional data bus buffer that is used to interface with the system bus. Write commands to the M5M82C59AP,-2, CALL instructions, vectored addresses, status information, etc. are transferred through the data bus buffer.

### Read/Write Control Logic

The read/write control logic is used to control functions such as receiving commands from the CPU and supplying status information to the data bus.

### Chip Select (CS)

The M5M82C59AP,-2 is selected (enabled) when CS is at lowlevel, but during interrupt request input or interrupt processing it may be high-level.

# Write Control Input (WR)

When WR goes to low-level the M5M82C59AP,-2 can be written.

# T-52-33-13

# Read Control Input (RD)

When RD goes low status information in the internal register of the M5M82C59AP,-2 can be read through the data bus.

## Address Input (A<sub>e</sub>)

The address input is normally connected with one of the address lines and is used along with  $\overline{WR}$  and  $\overline{RD}$  to control write commands and reading status information.

### Cascade Buffer/Comparator

The cascade buffer/comparator stores or compares identification codes. The three cascade lines are cutput when the M5M82C59AP,-2 is a master or input when it is a slave. The identification code on the cascade lines select it as master or slave.

## PROGRAMMING THE M5M82C59AP,-2

The M5M82C59AP,-2 is programmed through the initialization Command Word (ICW) and the operation command word (OCW). The following explains the functions of these two commands.

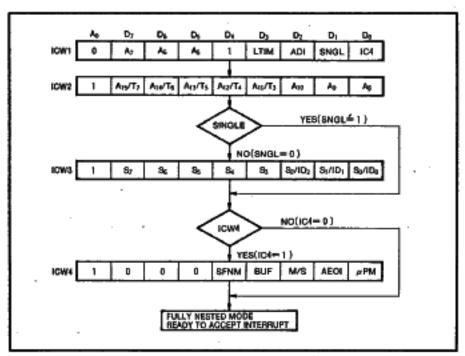

### Initialization Command Words (ICWs)

The initialization command word is used for the initial setting of the M5M82C59AP,-2. There are four commands in this group and the following explains the details of these four commands.

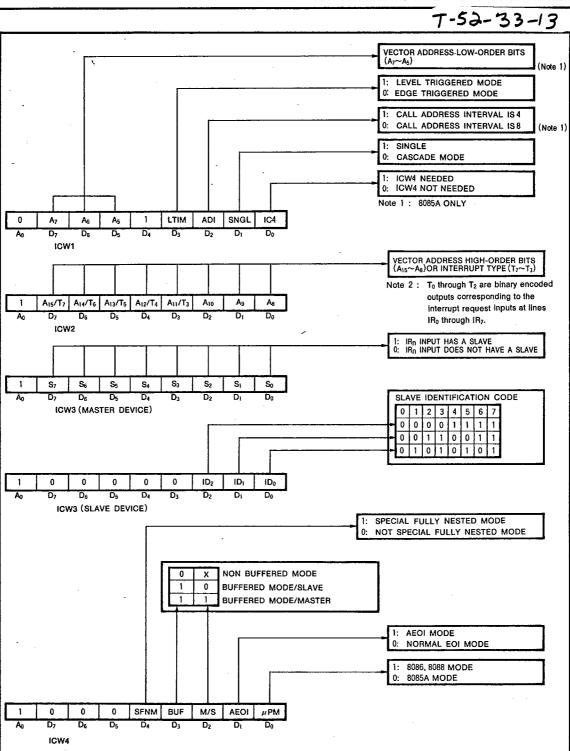

### ICW1

The meaning of the bits of ICWI is explained in Fig. 3 along with the functions. ICWI contains vectored address bits A<sub>7</sub>~ A<sub>8</sub>, a flag indicating whether interrupt input is edge triggered or level triggered, CALL address interval, whether a single M5M82C59AP,-2 or the cascade mode is used, and whether ICW4 is required or not.

Whenever a command is issued with  $A_0=0$  and  $D_4=1$ , this is interpreted as ICWI and the following will automatically occur.

- (a) The interrupt mask register (IMR) is cleared.

- (b) The interrupt request input IR<sub>7</sub> is assigned the lowest priority.

- (c) The special mask mode is cleared and the status read is set to the interrupt request register (IRR).

- (d) When IC4=0 all bits in ICW4 are set to zero.

# ICW2

ICW2 contains vectored address bits  $A_{15} \sim A_{8}$  or interrupt type  $T_{7} \sim T_{3}$ , and the format is shown in Fig. 3.

### ICW3

When SNGL=1 it indicates that only a single M5M82C59AP,-2 is used in the system, in which case ICW3 is not valid. When SNGL=0, ICW3 is valid and indicates cascade connections with other M5M82C59AP,-2 devices. In the master mode, a "1" is set for each slave.

When the CPU is an 8065A the CALL instruction is released from the master at the first INTA pulse and the vectored address is released onto the data bus from the slave at the second and third INTA pulses.

When the CPU is a 8085 the master and slave are in highimpedance at the first INTA pulse and the pointer is released onto the data bus from the slave at the second INTA pulse.

The master mode is specified when  $\overline{SP/EN}$  pin is highlevel or BUF=1 and M/S=1 in ICW4, and slave mode is specified when  $\overline{SP/EN}$  pin is low-level or BUF=1 and M/S=0 in ICW4. In the slave mode, three bits  $ID_2 \sim ID_2$  identify the

Fig. 2 Initialization sequence

6249828 MITSUBISHI(MICMPTR/MIPRC)

91D 12017

# CMOS PROGRAMMABLE INTERRUPT CONTROLLER

Fig. 3 Initialization command word format

6249828 MITSUBISHI (MICMPTR/MIPRC)

91D 12018

# CMOS PROGRAMMABLE INTERRUPT CONTROLLER

T-52-33-13

slave. And then when the slave code released on the cascade lines from the master, matches the assigned ID code, the vectored address is released by it onto the data bus at the next INTA pulse.

### ICW4

Only when IC4=1 in ICW1 is ICW4 valid. Otherwise all bits are set to zero. When ICW4 is valid it specifies special fully nested mode, buffer mode master/slave, automatic EOI and microprocessor mode. The format of ICW4 is shown in Fig. 3.

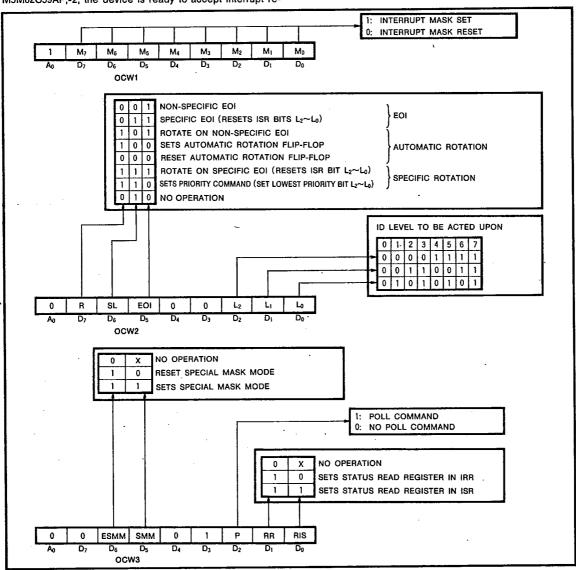

#### Operation Command Words (OCWs)

The operation command words are used to change the contents of IMR, the priority of interrupt request inputs and the special mask. After the ICW are programmed into the M5M82C59AP,-2, the device is ready to accept interrupt re-

quests. There are three types of  $OCW_S$ ; explanation of each follows, and the format of  $OCW_S$  is shown in Fig. 4.

#### OCW1

The meaning of the bits of OCW1 are explained in Fig. 4 along with their functions. Each bit of IMR can be independently changed (set or reset) by OCW1.

#### OCW2

The OCW2 is used for issuing EOI commands to the M5M82C59AP and for changing the priority of the interrupt request inputs.

### OCW3

The OCW3 is used for specifying special mask mode, poll mode and status register read.

Fig. 4 Operation command word format

6249828 MITSUBISHI(MICMPTR/MIPRC)

91D 12019

# CMOS PROGRAMMABLE INTERRUPT CONTROLLER

T-52-33-17

### **FUNCTION OF COMMAND**

#### Interrupt masks

The mask register contains a mask for each individual interrupt request. These interrupt masks can be changed by programming using OCW1.

#### Special mask mode

When an interrupt request is acknowledged and the ISR bit corresponding to the interrupt request is not reset by EOI command (which means an interrupt service routine is executing) lower priority interrupt requests are ignored.

In special mask mode interrupt requests received at interrupt request inputs which are masked by OCW1 are disabled, but interrupts at all levels that are not masked are possible. This means that in the mask mode all level of interrupts are possible or individual inputs can be selectively programmed so all interrupts at the selected inputs are disabled. The masks are stored in IMR and special mask is set/reset by executing OCW3.

#### **Buffered** mode

The buffered mode will structure the M5M82C59AP,-2 to send an enable signal on SP/EN to enable the data bus buffer, when the data bus requires the data bus buffer or when cascading mode is used. In this mode, when data bus output of the M5M82C59AP,-2 is enabled, the SP/EN output becomes low-level. This allows the M5M82C59AP,-2 to be programmed whether it is a master or a slave by software. The buffered mode is set/reset by executing ICW4.

### Fully nested mode

The fully nested mode is the mode when no mode is specified and is the usual operational mode. In this mode, the priority of interrupt request terminals is fixed from the lowest IR7 to the highest IR0. When an interrupt request is acknowledged the CALL instruction and vectored address are released onto the data bus. At the same time the ISR bit corresponding to the accepted interrupt request is set. This ISR bit remains set until it is reset by the input of an EOI command or until the trailing edge of last INTA pulse in AEOI mode. While an interrupt service routine is being executed, interrupt requests of same or lower priority are disabled while the bit of ISR remains set. The priorities can be changed by OCW2.

### Special fully nested mode

The special fully nested mode will be used when cascading is used and this mode will be programmed to the master by ICW4. The special fully nested mode is the same as the fully nested mode with the following two exceptions.

1. When an interrupt from a certain slave is being serviced, this slave is not locked out from the master priority logic. Higher priority interrupts within the slave will be recognized by the master and the master will initiate an interrupt request to the CPU. In general in the normal fully nested mode, a serviced slave is locked out from the master's priority, and so higher priority interrupts from the same slave are not serviced.

2. When an interrupt from a certain slave is being serviced the software must check ISR to determine if there are additional interrupts requests to be serviced. If the ISR bit is 0 the EOI command may be sent to the master too. But if it is not 0 the EOI command should not be sent to the master.

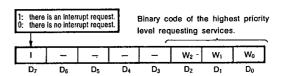

#### Poll mode

The poll mode is useful when the internal enable flip-flop of the microprocessor is reset, and interrupt input is disabled. Service to the device is achieved by a programmer initiative using a poll command. In the poll mode the M5M82C59AP,-2 at the next RD pulse puts 8 bits on the data bus which indicates whether there is an interrupt request and reads the priority level. The format of the information on the data bus is as shown below.

When I=0 (no interrupt request),  $W_2 \sim W_0$  is 111. The poll is valid from WR to RD and interrupt is frozen. This mode can be used for processing common service routines for interrupts from more than one line and does not require any INTA sequence. Poll command is issued by setting P=1 in OCW3.

#### End of Interrupt (EOI) and specific EOI (SEOI)

An EOI command is required by the M5M82C59AP,-2 to reset the ISR bit. So an EOI command must be issued to the M5M82C59AP,-2 before returning from an interrupt service routine.

When AEOI is selected in ICW4, the ISR bit can be reset at the trailing edge of the last INTA pulse. When AEOI is not selected the ISR bit is reset by the EOI command issued to the M5M82C59AP,-2 before returning from an interrupt service routine. When programmed in the cascade mode the EOI command must be issued to the master once and to corresponding slave once.

There are two forms of EOI command, specific EOI and nonspecific EOI. When the M5M82C59AP,-2 is used in the fully nested mode, the ISR bit being serviced is reset by the EOI command. When the non-specific EOI is issued the M5M82C59AP,-2 will automatically reset the highest ISR bit of those that are set. Other ISR bits are reset by a specific EOI and the bit to be reset is specified in the EOI by the program. The SEOI is useful in modes other than fully nested mode. When the M5M82C59AP,-2 is in special mask mode ISR bits masked in IMR are not reset by EOI. EOI and SEOI are selected when OCW2 is executed.

6249828 MITSUBISHI (MICMPTR/MIPRC)

91D 12020

# CMOS PROGRAMMABLE INTERRUPT CONTROLLER

T-52-33-13

#### Automatic EOI (AEOI)

In the AEOI mode the M5M82C59AP,-2 executes nonspecific EOI command automatically at the trailing edge of the last  $\overline{\text{INTA}}$  pulse. When AEOI = 1 in ICW4, the M5M82C59AP,-2 is put in AEOI mode continuously until reprogrammed in ICW4.

#### **Automatic rotation**

The automatic rotation mode is used in applications where many interrupt requests of the same level are expected such as multichannel communication systems. In this mode when an interrupt request is serviced, that request is assigned the lowest priority so that if there are other interrupt requests they will have higher priorities. This means that the next request on the interrupt request being serviced must wait until the other interrupt requests are serviced (worst case is waiting for all 7 of the other controllers to be serviced). The priority and serving status are rotated as shown in Fig. 5.

Fig. 5 An example of priority rotation

In the non-specific EOI command automatic rotation mode is selected when R=1, EOI=1, SL=0 in OCW2. The internal priority status is changed by EOI or AEOI commands. The rotation priority A flip-flop is set by R=1, EOI=0 and SL=0 which is useful when the M5M82C59AP,-2 is used in the AEOI mode.

### Specific rotation

Specific rotation gives the user versatile capabilities in interrupt controlled operations. It serves in those applications in which a specific device's interrupt priority must be altered. As opposed to automatic rotation which automatically sets priorities, specific rotation is completely user controlled. That is, the user selects the interrupt level that is to receive

lowest or highest priority. Priority changes can be executed during an EOI command.

# Level triggered mode/Edge triggered mode

Selection of level or edge triggered mode of the M5M82C59AP,-2 is made by ICW1, When using edge triggered mode not only is a transition from low to high required, but the high-level must be held until the first INTA. If the high-level is not held until the first INTA, the interrupt request will be treated as if it were input on iR7, except that the ISR bit is not set. When level triggered mode is used the functions are the same as edge triggered mode except that the transition from low to high is not required to trigger the interrupt request.

In the level triggered mode and using AEOI mode together, if the high-level is held too long the interrupt will occur immediately. To avoid this situation interrupts should be kept disabled until the end of the service routine or until the IR input returns low. In the edge triggered mode this type of mistake is not possible because the interrupt request is edge triggered.

# Reading the M5M82C59AP,-2 internal status

The contents of IRR and ISR can be read by the CPU with status read. When an OCW3 is issued to the M5M82C59AP,-2 and an RD pulse issued the contents of IRR or ISR can be released onto the data bus. A special command is not required to read the contents of IMR. The contents of IMR can be released onto the data bus by issuing an RD pulse when  $A_0 = 1$ . There is no need to issue a read register command every time the IRR or ISR is to be read. Once a read register command is received by the M5M82C59AP,-2, it remains valid until it is changed. Remember that the programmer must issue a poll command every time to check whether there is an interrupt request and read the priority level. Polling overrides status read when P=1, RR=1 in OCW3.

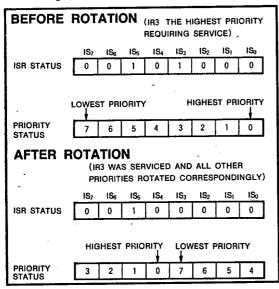

# CASCADING

The M5M82C59AP,-2 can be interconnected in a system of one master with up to eight slaves to handle up to 64 priority levels. A system of three units that can be used with the 8085A is shown in Fig. 6.

The master can select a slave by outputting its identification code through the three cascade lines. The INT output of each slave is connected to the master interrupt request inputs. When an interrupt request of one of the slaves is to be serviced the master outputs the identification code of the slave through the cascade lines, so the slave will release the vectored address on the next INTA pulse.

The cascade lines of the master are nomally low, and will contain the slave identification code from the leading edge of the first INTA pulse to the trailing edge of the last INTA pulse. The master and slave can be programmed to work in different modes. ICWs must be issued for each device, and EOI commands must be issued twice: once for the master and once for the corresponding slave. Each CS of the M5M82C59AP,-2 requires an address decoder.

6249828 MITSUBISHI(MICMPTR/MIPRC)

91D 12021

# CMOS PROGRAMMABLE INTERRUPT CONTROLLER

Fig. 6 Cascading the M5M82C59AP,-2

Fig. 7 Example of interface with the 8086

6249828 MITSUBISHI(MICMPTR/MIPRC)

91D 12022

# CMOS PROGRAMMABLE INTERRUPT CONTROLLER

# T-52-33-13

# INSTRUCTION SET

| Item                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         |                                                                      |                                                                                             | Insti                                                                                       | uction c                                                                                    | ode                                                                                              |                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                  |                                                       | Func                                                                              | tion                                                                                             |                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-------------------------------------------------------|-----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|----------------------------------------|

| Number                                                                                                                                                                                                                                                         | Mnemonic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Ao                                      | D <sub>7</sub>                                                       | D <sub>6</sub>                                                                              | D <sub>5</sub>                                                                              | D <sub>4</sub>                                                                              | D <sub>3</sub>                                                                                   | D <sub>2</sub>                                                                                   | D <sub>1</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Do                                                                                               | iCW4 required?                                        | Intervel                                                                          | Single                                                                                           | Trigger                                |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16                                                                                                                                                                            | ICWI A ICWI B ICWI C ICWI D ICWI E ICWI F ICWI G ICWI H ICWI I ICWI J ICWI K ICWI L ICWI M ICWI N ICWI N ICWI O ICWI P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 000000000000000000000000000000000000000 | A7<br>A7<br>A7<br>A7<br>A7<br>A7<br>A7<br>A7<br>A7<br>A7<br>A7<br>A7 | A6<br>A6<br>A6<br>A6<br>A6<br>A6<br>A6<br>A6<br>A6<br>A6<br>A6<br>A6<br>A6<br>A             | A5<br>A5<br>A5<br>O<br>O<br>O<br>O<br>A5<br>A5<br>O<br>O<br>O<br>O<br>O<br>O<br>O<br>O<br>O | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                                     | 0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1                               | 1<br>1<br>1<br>0<br>0<br>0<br>0<br>1<br>1<br>1<br>1<br>0<br>0<br>0                               | 1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>1<br>1<br>1<br>1<br>1                                         | 2222222777777                                         | 4<br>4<br>4<br>8<br>8<br>8<br>8<br>4<br>4<br>4<br>4<br>4<br>8<br>8<br>8<br>8<br>8 | Y<br>Y<br>N<br>N<br>Y<br>Y<br>N<br>N<br>Y<br>Y<br>N<br>N<br>N<br>Y<br>Y<br>N<br>N<br>N<br>N<br>N | 8181818181818181                       |

| 17<br>18<br>19                                                                                                                                                                                                                                                 | ICW2<br>ICW3 M<br>ICW3 S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1                                       | A <sub>15</sub><br>S <sub>7</sub><br>0                               | S <sub>6</sub>                                                                              | A <sub>13</sub><br>S <sub>5</sub><br>0                                                      | A <sub>12</sub><br>S <sub>4</sub><br>0                                                      | S <sub>3</sub>                                                                                   | S <sub>2</sub>                                                                                   | S <sub>1</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | S₀<br>ID₀                                                                                        |                                                       | Stave connection                                                                  | ns (master mode<br>tion code (slave                                                              | mode)                                  |

|                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         |                                                                      |                                                                                             |                                                                                             |                                                                                             |                                                                                                  |                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                  | SFNM                                                  | BUF                                                                               | AEOI                                                                                             | 8086                                   |

| 20<br>21<br>22<br>23<br>24<br>25<br>26<br>27<br>28<br>29<br>30<br>31<br>32<br>33<br>34<br>35<br>36<br>37<br>38<br>39<br>40<br>41<br>42<br>43<br>44<br>45<br>46<br>47<br>48<br>49<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50 | ICW4 A ICW4 B ICW4 C ICW4 C ICW4 C ICW4 F ICW4 F ICW4 G ICW4 I ICW4 I ICW4 I ICW4 N ICW5 N IC | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | 000000000000000000000000000000000000000                              | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | 0<br>0<br>0<br>0<br>1<br>1<br>1<br>1<br>1<br>0<br>0<br>0<br>0<br>0<br>0<br>1<br>1<br>1<br>1<br>1 | 0<br>0<br>1<br>1<br>0<br>0<br>0<br>1<br>1<br>1<br>0<br>0<br>0<br>1<br>1<br>1<br>0<br>0<br>0<br>1<br>1<br>1<br>0<br>0<br>0<br>1<br>1<br>1<br>0<br>0<br>0<br>0<br>1<br>1<br>0<br>0<br>0<br>0<br>1<br>1<br>0<br>0<br>0<br>0<br>1<br>1<br>0<br>0<br>0<br>0<br>1<br>0<br>0<br>0<br>0<br>1<br>0<br>0<br>0<br>0<br>1<br>0<br>0<br>0<br>1<br>0<br>0<br>0<br>0<br>1<br>0<br>0<br>0<br>0<br>0<br>0<br>1<br>0<br>0<br>0<br>0<br>1<br>0<br>0<br>0<br>0<br>0<br>1<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>1<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | 0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1 | N N N N N N N N N N N N N N N N N N N                 | N N N N N N N N N N N N N N N N N N N                                             | 2277227722772277227722772277                                                                     | 27272727272727272727272727272727272727 |

| 53<br>54<br>55<br>56<br>57<br>58<br>59<br>60<br>61<br>62<br>63<br>64                                                                                                                                                                                           | OCW2 E OCW2 SE OCW2 RE OCW2 RSE OCW2 RS OCW2 RS OCW3 P OCW3 RS OCW3 RS OCW3 RS OCW3 RS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 000000000000000000000000000000000000000 | 0<br>0<br>1<br>1<br>1<br>0<br>0<br>0                                 | 0<br>1<br>0<br>1<br>0<br>0<br>1<br>0<br>0                                                   | 1<br>1<br>1<br>1<br>0<br>0<br>0<br>0<br>0                                                   | 000000000000                                                                                | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>1<br>1<br>1                                              | 0<br>L <sub>2</sub><br>0<br>L <sub>2</sub><br>0<br>0<br>L <sub>2</sub><br>1<br>0<br>0            | 0 L <sub>1</sub> 0 L <sub>1</sub> 0 0 1 1 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 010100101000                                                                                     | EOI<br>SEOI<br>Rotate d<br>Rotate<br>Rotate<br>Rotate | on Non-Specific E                                                                 |                                                                                                  | omatic rotation)<br>lific rotation)    |

Note: Y: yes, N: no, E: edge, L: level, M: master, S: slave

6249828 MITSUBISHI(MICMPTR/MIPRC)

91D 12023

# CMOS PROGRAMMABLE INTERRUPT CONTROLLER

# ABSOLUTE MAXIMUM RATINGS

T-52-33-13

| Symbol | Parameter                            | Conditions          | Ratings                   | Unit |

|--------|--------------------------------------|---------------------|---------------------------|------|

| Vcc    | Supply voltage                       |                     | -0.3~7                    | V    |

| Vı     | input voitage                        | With respect to Vss | -0.3~V <sub>GG</sub> +0.3 | v    |

| Vo     | Output voltage                       |                     | -0.3~V <sub>cc</sub> +0.3 | V    |

| Topr   | Operating free-air temperature range |                     | -20~75                    | ΰ    |

| Tstg   | Storage temperature range            | ;                   | <b>−65~150</b>            | τ    |

# **RECOMMENDED OPERATING CONDITIONS** $(T_a = -20 \sim 75 \degree C$ , unless otherwise noted)

| Symbol          | Parameter      |     | Limits |     | 11-14 |

|-----------------|----------------|-----|--------|-----|-------|

|                 | Falallietei    | Min | Nom    | Max | Unit  |

| V <sub>CC</sub> | Supply voltage | 4.5 | 5      | 5.5 | V     |

| Vss             | Supply voltage |     | 0      |     | V     |

# **ELECTRICAL CHARACTERISTICS** ( $\tau_a = -20 \sim 75 \degree$ , $v_{cc} = 5 \lor \pm 10 \%$ , $v_{ss} = 0 \lor$ , unless otherwise noted)

| Symbol               | Parameter                                           | Test conditions                                                                       |      | Limits      |                      |      |

|----------------------|-----------------------------------------------------|---------------------------------------------------------------------------------------|------|-------------|----------------------|------|

|                      | Faianeter                                           | rest conditions                                                                       | Min  | Тур         | Max                  | Unit |

| ViH                  | High-level input voltage                            | •                                                                                     | 2    |             | V <sub>cc</sub> +0.3 | ٧    |

| VIL                  | Low-level input voltage                             |                                                                                       | -0.3 |             | 0.8                  | ٧    |

| V <sub>OH</sub>      | High-level output voltage                           | I <sub>OH</sub> =-400μA                                                               | 2.4  |             |                      |      |

| ▼он                  | nigh-level output voltage                           | I <sub>OH</sub> =−20μA                                                                | 4.4  | · · · · · · |                      | ٧    |

|                      |                                                     | I <sub>OH</sub> =-400μA                                                               | 2.4  |             |                      |      |

| V <sub>OH(INT)</sub> | High-level output voltage, interrupt request output | I <sub>OH</sub> =-100μA                                                               | 3.5  |             |                      | v    |

|                      |                                                     | I <sub>OH</sub> =−20μA                                                                | 4.4  |             |                      |      |

| VoL                  | Low-level output voltage                            | I <sub>OL</sub> =2. 2mA                                                               |      |             | 0. 45                | ٧    |

| Icc                  | Standby supply current from V <sub>CC</sub>         | V <sub>CC</sub> =5, 5V, V <sub>I</sub> =V <sub>CC</sub> or GND output open            |      |             | 10                   | μΑ   |

| I <sub>IH</sub>      | High-level input current                            | V <sub>I</sub> =V <sub>CC</sub>                                                       | -10  |             | 10                   | μA   |

| I <sub>IL</sub>      | Low-level input current                             | V <sub>I</sub> =0V                                                                    | -10  |             | 10                   | μA   |

| loz                  | Off-state output current                            | V <sub>SS</sub> =0, V <sub>I</sub> =0~V <sub>CC</sub>                                 | -10  | <u>`</u>    | 10                   | μA   |

| I <sub>LIR1</sub>    | IR pin input current                                | V <sub>i</sub> =0V                                                                    | -300 | "           |                      | μA   |

| I <sub>LIR2</sub>    | IR pin input current                                | v <sub>i</sub> =v <sub>cc</sub>                                                       |      |             | 10                   | μА   |

| Ci                   | Input capacitance                                   | V <sub>CC</sub> =V <sub>SS</sub> , f=1MH <sub>z</sub> , 25mVrms, T <sub>6</sub> =25°C |      |             | 10                   | pF   |

| Ci/o                 | Input/output capacitance                            | V <sub>CC</sub> =V <sub>SS</sub> , f=1MH <sub>Z</sub> , 25mVrms, T <sub>a</sub> =25℃  |      |             | 20                   | pF   |

6249828 MITSUBISHI (MICMPTR/MIPRC)

91D 12024

D

# CMOS PROGRAMMABLE INTERRUPT CONTROLLER

T-52-33

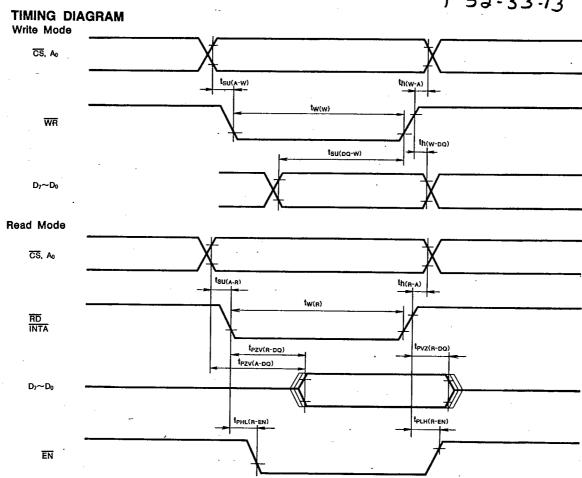

TIMING REQUIREMENTS ( $\tau_a = -20 \sim 75 \text{ C}$ ,  $V_{co} = 5 \text{ V} \pm 10 \text{ W}$ ,  $V_{ss} = 0 \text{ V}$ , unless otherwise noted)

|                       |                                                                    | Alternative       | L         | Lir   | nits      | ]      |      |

|-----------------------|--------------------------------------------------------------------|-------------------|-----------|-------|-----------|--------|------|

| Symbol                | Parameter                                                          | •                 | M5M82     | C59AP | M5M820    | 59AP-2 | Unit |

|                       |                                                                    | symbol            | Min       | Max   | Min       | Max    |      |

| t <sub>W(w)</sub>     | Write pulse width                                                  | twwn              | 290 (200) |       | 190 (120) |        | ns   |

| tsu(A-W)              | Address setup time before write                                    | t <sub>AHWL</sub> | 0         |       | 0         |        | ns   |

| th(w-A)               | Address hold time after write                                      | twhax             | 0         |       | 0         |        | ns   |

| T <sub>SU(DQ-W)</sub> | - Data setup time before write                                     | tovwh             | 240(100)  |       | 160(100)  |        | ns   |

| th(w-pa)              | Data hold time after write                                         | t <sub>WHDX</sub> | . 0       |       | 0         |        | ns   |

| t <sub>W(R)</sub>     | Read pulse width                                                   | t <sub>RLRH</sub> | 235 (200) |       | 160       |        | ns   |

| tsu(A-R)              | Address setup time before read                                     | t <sub>AHRL</sub> | 0         |       | 0         |        | ns   |

| th(R-A)               | Address hold time after read                                       | t <sub>RHAX</sub> | 0         |       | 0         |        | ns   |

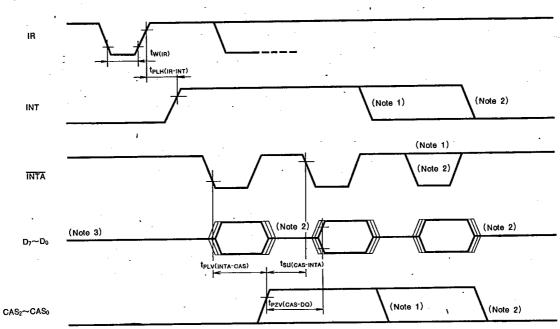

| t <sub>W(IR)</sub>    | Interrupt request input width, low-level time, edge triggered mode | tıшн              | 100       |       | 100       |        | ns   |

| tsu(cas-inta)         | Cascade setup time after INTA (slave)                              | tovial            | 55        |       | 40        |        | ns   |

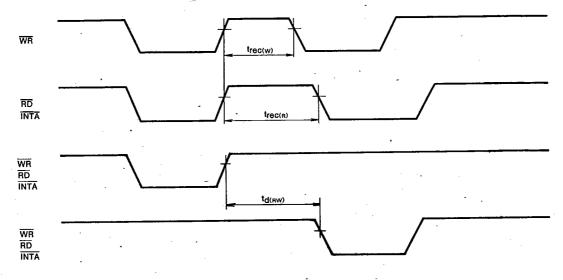

| t <sub>rec(w)</sub>   | Write recovery time                                                | twhwL             | 190       |       | 190       |        | ns   |

| trec(R)               | Read recovery time                                                 | t <sub>RHAL</sub> | 160       |       | 160       |        | ns   |

|                       | End of Command to next Command (Not same Command type)             |                   | 500       |       | 400       |        | ns   |

| td(RW)                | End of INTA sequence to next INTA sequence.                        | t <sub>OHOL</sub> | 300       | }     | 700       |        | 113  |

# **SWITCHING CHARACTERISTICS** $(T_a = -20 \sim 75 \degree C, V_{CC} = 5 \lor \pm 10\%, V_{SS} = 0 \lor, unless otherwise noted) (Note 2)$

| Symbol                    | Parameter                                                                 | Alternative<br>symbol | Limits     |           |              |           |      |

|---------------------------|---------------------------------------------------------------------------|-----------------------|------------|-----------|--------------|-----------|------|

|                           |                                                                           |                       | M5M82C59AP |           | M5M82C59AP-2 |           | Unit |

|                           |                                                                           |                       | Min        | Max       | Min          | Max       |      |

| t <sub>PZV(R-DQ)</sub>    | Data output enable time after read                                        | t <sub>RLDV</sub>     |            | 200(170)  | -            | 120       | ns   |

| t <sub>PVZ(R-DQ)</sub>    | Data output disable time after read                                       | t <sub>RHDZ</sub>     | 10         | 100       | 10           | 85        | กร   |

| t <sub>PZV(A-DQ)</sub>    | Data output enable time after address                                     | t <sub>AHDV</sub>     |            | 200 (170) |              | 200 (170) | ns   |

| t <sub>PHL(R-EN)</sub>    | Propagation time from read to enable signal output                        | t <sub>RLEL</sub>     |            | 125       |              | 100       | ns   |

| t <sub>PLH(R-EN)</sub>    | Propagation time from read to disable signal output                       | <b>!</b> янен         |            | 150       |              | 150       | ns   |

| t <sub>PLH</sub> (IR-INT) | Propagation time from interrupt request input to interrupt request output | <b>t</b> інін         |            | 350       |              | 300       | ns   |

| tplv(inta-cas)            | Propagation time from INTA to cascade output (master)                     | tIALCV                |            | 565       |              | 360       | ns   |

| tpzy(cas-pg)              | Data output enable time after cascade output (slave)                      | tcvpv                 |            | 300       |              | 200       | ns   |

M5M82C59AP, 2 is also invested with the extended specification showed in the brackets. INTA signal is considered read signal CS signal is considered address signal input pulse level 0. 45~2.4V Input pulse rise time 10ns 10ns 0. 45 Input pulse rise time input pulse fall time Reference level input Output

Load capacitance

V<sub>IH</sub>=2V, V<sub>IL</sub>=0.8V V<sub>OH</sub>=2V, V<sub>OL</sub>=0.8V C<sub>L</sub>=100pF, where SP/EN pln is 15pF

6249828 MITSUBISHI(MICMPTR/MIPRC)

91D 12025

CMOS PROGRAMMABLE INTERRUPT CONTROLLER

T-52-33-13

6249828 MITSUBISHI(MICMPTR/MIPRC)

91D 12026

CMOS PROGRAMMABLE INTERRUPT CONTROLLER

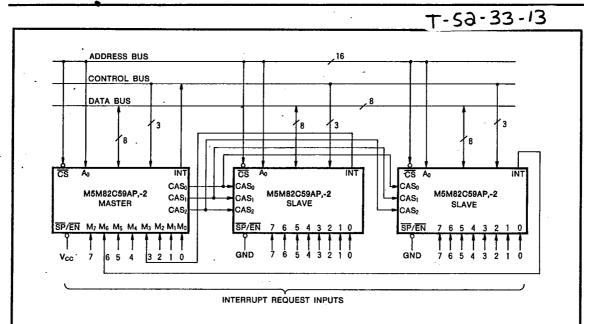

### Interrupt Sequence

### Other Timing

8086, 8088 mode 8085A mode 8086, 8088 mode is in high-impedance state, pointer is released during the next INTA. When in single 8085A mode, data is released by all INTAs. When master, CALL instruction is released during the first INTA, high impedance state during the second and third INTA. When slave, high impedance state during the first INTA, vectored address is released during the second and third INTA.