# TP3020, TP3020-1, TP3021, TP3021-1 **Monolithic CODECs**

## **General Description**

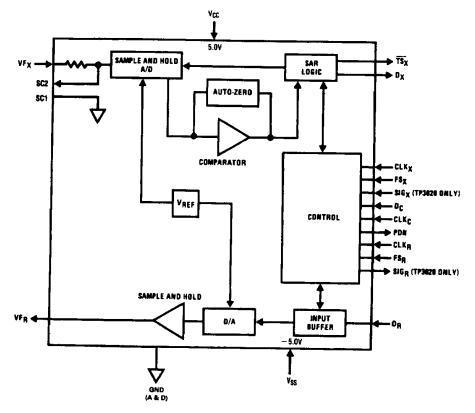

The TP3020 and TP3021 are monolithic PCM CODECs implemented with double-poly CMOS technology. The TP3020 is intended for  $\mu$ -law applications and contains logic for  $\mu$ law signaling insertion and extraction. The TP3021 is intended for A-law applications.

Each device contains separate D/A and A/D circuitry, all necessary sample and hold capacitors, a precision voltage reference and internal auto-zero circuit. A serial control port allows an external controller to individually assign the PCM input and output ports to one of up to 32 time slots or to place the CODEC into a power-down mode. Alternately, the TP3020/TP3021 may be operated in a fixed time slot mode. Both devices are intended to be used with the TP3040 monolithic PCM filter which provides the input anti-aliasing function for the encoder and smoothes the output of the decoder and corrects for the sin x/x distortion introduced by the decoder sample and hold output.

### **Features**

- Low operation power—45 mW typical

- Low standby power—1 mW typical

- ±5V operation

- TTL compatible digital interface

- Time slot assignment or alternate fixed time slot modes

- Internal precision reference

- Internal sample and hold capacitors

- Internal auto-zero circuit

- TP3020—µ-law coding with signaling capabilities

- TP3021—A-law coding

- Synchronous or asynchronous operation

# **Simplified Block Diagram**

TL/H/5538-1

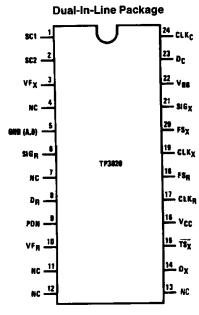

# **Connection Diagrams**

TL/H/5538-3

**Top View**

Order Number TP3020J or TP3020J-1 See NS Package Number J24A

## **Description of Pin Functions**

| Description of Fill Functions |                                                                                                                                                                                                                                                                                         |  |  |  |  |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Symbol                        | Function                                                                                                                                                                                                                                                                                |  |  |  |  |

| SC1                           | Internally connected to GNDA.                                                                                                                                                                                                                                                           |  |  |  |  |

| SC2                           | Connects $VF_X$ to an external sample/hold capacitor if fitted for use with pin-compatible NMOS CODECs. Ensures gain compatibility.                                                                                                                                                     |  |  |  |  |

| VF <sub>X</sub>               | Analog input to the encoder. This signal will be sampled at the end of the encoder time slot and the resulting PCM code will be shifted out during the subsequent encode time slot.                                                                                                     |  |  |  |  |

| GND                           | Analog and digital ground. All analog and digital signals are referenced to this pin.                                                                                                                                                                                                   |  |  |  |  |

| SIGR                          | Receive signaling bit output. During receive signaling frames the least significant (last) bit shifted into DR is internally latched and appears at this output—SIGR will then remain valid until changed during a subsequent receive signaling frame or reset by a power-down command. |  |  |  |  |

| D <sub>R</sub>                | Serial PCM data input to the decoder. During the decoder time slot, PCM data is shifted into $D_R$ , most significant bit first, on the falling edge of $CLK_R$ .                                                                                                                       |  |  |  |  |

| PDN                           | TTL output level which goes high when the CO-<br>DEC is in the power-down mode. May be used to<br>power-down other circuits associated with the<br>PCM channel.                                                                                                                         |  |  |  |  |

| VF <sub>R</sub>               | Analog output from the decoder. The decoder sample and hold amplifier is updated approximately 15 $\mu$ S after the end of the decode time slot.                                                                                                                                        |  |  |  |  |

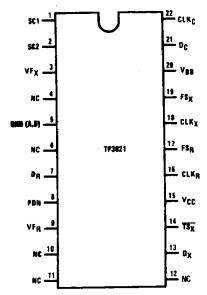

#### Dual-In-Line Package

TL/H/5538-4 **Top View**

Order Number TP3021J or TP3021J-1 See NS Package Number J22A

| Symbol           | Function                                                                                                                                                                                                                                                 |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NC               | Unused                                                                                                                                                                                                                                                   |

| D <sub>X</sub>   | Serial PCM TRI-STATE® output from the encoder. During the encoder time slot, the PCM code for the previous sample of VF <sub>X</sub> is shifted out, most significant bit first, on the rising edge of CLK <sub>X</sub> .                                |

| ₹S <sub>X</sub>  | Time slot output. This TTL compatible open-drain output pulses low during the encoder time slot. May be used to enable external TRI-STATE bus drivers if highly capacitive loads must be driven. Can be wire ANDed with other $\overline{TS}_X$ outputs. |

| $V_{CC}$         | 5V (±5%) Power Supply.                                                                                                                                                                                                                                   |

| CLK <sub>R</sub> | Master decoder clock input used to shift in the PCM data on $D_R$ and to operate the decoder sequencer. May operate at 1.536 MHz, 1.544 MHz or 2048 MHz. May be asynchronous with CLK $_X$ or CLK $_C$ .                                                 |

| FS <sub>R</sub>  | Decoder frame sync pulse. Normally occurring at an 8 kHz rate, this pulse is nominally one CLK <sub>R</sub> cycle wide. Extending the width of FS <sub>R</sub> to two or more cycles of CLK <sub>R</sub> signifies a receive signaling frame.            |

| CLK <sub>X</sub> | Master encoder clock input used to shift out the PCM data on $D_X$ and to operate the encoder sequencer. May operate at 1.536 MHz, 1.544 MHz or 2.048 MHz. May be asynchronous with CLK $_{\rm R}$ or CLK $_{\rm C}$ .                                   |

| FS <sub>X</sub>  | Encoder frame sync pulse. Normally occurring at an 8 kHz rate, this pulse is nominally one $\text{CLK}_X$ cycle wide. Extending the width of $\text{FS}_X$ to two or more cycles of $\text{CLK}_X$ signifies a transmit signaling                        |

frame.

## **Description of Pin Functions (Continued)**

**Symbol** SIGX Transmit signaling input. During a transmit signaling frame, the signal at SIGX is shifted out of DX in place of the least significant (last) bit of PCM data.

-5V (±5%) input. V<sub>BB</sub>  $D_{C}$

ESD rating is to be determined.

Serial control data input. Serial data on D<sub>C</sub> is shifted into the CODEC on the falling edge of CLKc. In the fixed time slot mode, DC doubles as a powerdown input.

**Symbol Function** CLKC

Control clock input used to shift serial control data into D<sub>C</sub>. CLK<sub>C</sub> must pulse 8 times during a period of time less than or equal to one frame time, although the 8 pulses may overlap a frame boundary.  $CLK_C$  need not be synchronous with  $CLK_X$  or CLK<sub>R</sub>. Connecting CLK<sub>C</sub> continuously high places the TP3020/TP3021 into the fixed time slot mode.

## **Absolute Maximum Ratings**

Operating Temperature -25°C to + 125°C Storage Temperature -65°C to + 150°C

V<sub>CC</sub> with Respect to GND 7V V<sub>BB</sub> with Respect to GND -7V

Input or Output Voltage at Any Digital Input or Output

Voltage at Any Analog

$V_{BB}$  = 0.3V to  $V_{CC}$  + 0.3V GND-0.3V to  $V_{CC} + 0.3V$

Lead Temperature

(Soldering, 10 seconds)

300°C

## **DC Electrical Characteristics**

Unless otherwise noted, limits printed in **BOLD** characters are guaranteed for  $V_{CC} = +5.0V \pm 5\%$ ,  $V_{BB} = -5.0V \pm 5\%$ ;  $T_A = -5.0V \pm 5\%$ 0°C to 70°C by correlation with 100% electrical testing at TA = 25°C. All other limits are assured by correlation with other production tests and/or product design and characterization. All signals referenced to GND. Typicals specified at V<sub>CC</sub> = +5.0V,  $V_{BB} = -5.0V$  and  $T_A = 25$ °C.

| Symbol           | Parameter                                                                                     | Conditions                                                                                                                              | Min        | Тур      | Max                      | Unit     |

|------------------|-----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|------------|----------|--------------------------|----------|

| DIGITAL IN       | ITERFACE                                                                                      |                                                                                                                                         |            |          |                          | <u> </u> |

| կ                | Input Current                                                                                 | 0 < V <sub>IN</sub> < V <sub>CC</sub>                                                                                                   | - 10       |          | 10                       | μА       |

| V <sub>IL</sub>  | Input Low Voltage                                                                             |                                                                                                                                         |            |          | 0.6                      | ٧        |

| V <sub>IH</sub>  | Input High Voltage                                                                            |                                                                                                                                         | 2.2        |          |                          | ٧        |

| V <sub>OL</sub>  | Output Low Voltage                                                                            | $D_X$ , $I_{OL}$ = 4.0 mA<br>$SIG_R$ , $I_{OL}$ = 0.5 mA<br>$\overline{TS}_X$ , $I_{OL}$ = 3.2 mA, Open Drain<br>PDN, $I_{OL}$ = 1.6 mA |            |          | 0.4<br>0.4<br>0.4<br>0.4 | >>>>     |

| V <sub>OH</sub>  | Output High Voltage                                                                           | D <sub>x</sub> , I <sub>OH</sub> = 6 mA<br>SIG <sub>R</sub> , I <sub>OH</sub> = 0.6 mA                                                  | 2.4<br>2.4 |          |                          | V<br>V   |

| ANALOG II        | NTERFACE                                                                                      |                                                                                                                                         |            |          |                          |          |

| Z <sub>I</sub>   | VF <sub>x</sub> Input Impedance when Resistance in Series with 2 Sampling Approximately 70 pF |                                                                                                                                         | 2.0        |          |                          | kΩ       |

| Z <sub>O</sub>   | Output impedance at VFR                                                                       | -3.1V <vf<sub>R&lt;3.1V</vf<sub>                                                                                                        |            | 10       | 20                       | Ω        |

| Vos              | Output Offset Voltage at VFR                                                                  | D <sub>R</sub> =PCM Zero Code (TP3020)<br>or Alternating ± 1 Code (TP3021)                                                              | 25         |          | 25                       | m∨       |

| I <sub>IN</sub>  | Analog Input Bias Current                                                                     | V <sub>IN</sub> =0V                                                                                                                     | -0.1       |          | 0.1                      | μΑ       |

| R1 × C1          | DC Blocking Time Constant                                                                     |                                                                                                                                         | 4.0        |          |                          | ms       |

| C1               | DC Blocking Capacitor                                                                         |                                                                                                                                         | 0.1        |          |                          | μF       |

| R1               | Input Bias Resistor                                                                           |                                                                                                                                         |            |          | 160                      | kΩ       |

| POWER DI         | SSIPATION                                                                                     |                                                                                                                                         |            | <u>-</u> |                          |          |

| Icco             | Standby Current, V <sub>CC</sub>                                                              |                                                                                                                                         |            | 0.1      | 0.4                      | mA       |

| I <sub>BB0</sub> | Standby Current, V <sub>BB</sub>                                                              |                                                                                                                                         |            | 0.03     | 0.1                      | mA       |

| loc <sub>1</sub> | Operating Current, V <sub>CC</sub>                                                            |                                                                                                                                         |            | 4.5      | 8.0                      | mA       |

| I <sub>BB1</sub> | Operating Current, V <sub>BB</sub>                                                            |                                                                                                                                         |            | 4.5      | 8.0                      | mA       |

## **AC Electrical Characteristics**

Unless otherwise noted, the analog input is a 0 dBm0, 1.02 kHz sine wave. The digital input is a PCM bit stream generated by passing a 0 dBm0, 1.02 kHz sine wave through an ideal encoder. All output levels are sin x/x corrected. Limits printed in **BOLD** characters are guaranteed for  $V_{CC} = +5V \pm 5\%$ ,  $V_{BB} = -5V \pm 5\%$ ;  $T_A = 0^{\circ}C$  to  $+70^{\circ}C$  by correlation with 100% electrical testing at  $T_A = 25^{\circ}C$ . All other limits are assured by correlation with other production tests and/or product design and characterization. All signals referenced to GND. Typicals specified at  $V_{CC} = +5V$ ,  $V_{BB} = -5V$ ,  $T_A = 25^{\circ}C$ .

| Symbol           | Parameter                                                       | Conditions                                                                                                                                                                                                                                                                                                                              | MIn                          | Тур | Max                      | Units                |

|------------------|-----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-----|--------------------------|----------------------|

|                  | Absolute Level                                                  | The nominal 0 dBm0 levels for the TP3020 and TP3021 are 1.520 Vrms and 1.525 Vrms respectively. The resulting nominal overload level is 3.096V peak for both devices. All gain measurements for the encode and decode portions of the TP3020/TP3021 are based on these nominal levels after the necessary sin x/x corrections are made. |                              |     |                          | j.                   |

| G <sub>RA</sub>  | Receive Gain, Absolute<br>TP3020, TP3021<br>TP3020-1, TP3021-1  | $T = 25^{\circ}C$ , $V_{CC} = 5V$ , $V_{BB} = -5V$                                                                                                                                                                                                                                                                                      | -0.125<br>-0.175             |     | 0.125<br>0.175           | dB<br>dB             |

| G <sub>RAT</sub> | Absolute Receive Gain Variation with Temperature                | T=0°C to 70°C                                                                                                                                                                                                                                                                                                                           | -0.05                        |     | 0.05                     | dB                   |

| G <sub>RAV</sub> | Absolute Receive Gain<br>Variation with Supply Voltage          | V <sub>CC</sub> =5V±5%,<br>V <sub>BB</sub> =-5V±5%                                                                                                                                                                                                                                                                                      | -0.07                        |     | 0.07                     | dB                   |

| G <sub>XA</sub>  | Transmit Gain, Absolute<br>TP3020, TP3021<br>TP3020-1, TP3021-1 | $T = 25^{\circ}C, V_{CC} = 5V, V_{BB} = -5V$                                                                                                                                                                                                                                                                                            | -0.325<br>-0.375             |     | -0.075<br>-0.025         | dB<br>dB             |

| G <sub>XAT</sub> | Absolute Transmit Gain Variation with Temperature               | T=0°C to 70°C                                                                                                                                                                                                                                                                                                                           | -0.05                        |     | 0.05                     | dB                   |

| G <sub>XAV</sub> | Absolute Transmit Gain<br>Variation with Supply Voltage         | $V_{CC} = 5V \pm 5\%,$<br>$V_{BB} = -5V \pm 5\%$                                                                                                                                                                                                                                                                                        | -0.07                        |     | 0.07                     | dB                   |

| G <sub>RAL</sub> | Absolute Receive Gain<br>Variation with Level                   | CCITT Method 2 Relative<br>to 10 dBm0<br>0 dBm0 to 3 dBm0<br>40 dBm0 to 0 dBm0<br>50 dBm0 to 40 dBm0<br>55 dBm0 to 50 dBm0                                                                                                                                                                                                              | -0.3<br>-0.2<br>-0.4<br>-1.0 |     | 0.3<br>0.2<br>0.4<br>1.0 | dB<br>dB<br>dB<br>dB |

| G <sub>XAL</sub> | Absolute Transmit Gain<br>Variation with Level                  | CCITT Method 2 Relative<br>to 10 dBm0<br>0 dBm0 to 3 dBm0<br>40 dBm0 to 0 dBm0<br>50 dBm0 to 40 dBm0<br>55 dBm0 to 50 dBm0                                                                                                                                                                                                              | -0.3<br>-0.2<br>-0.4<br>-1.0 |     | 0.3<br>0.2<br>0.4<br>1.0 | dB<br>dB<br>dB<br>dB |

| S/D <sub>R</sub> | Receive Signal to Distortion<br>Ratio                           | Sinusoidal Test Method Input<br>Level<br>— 30 dBm0 to 0 dBm0<br>— 40 dBm0<br>— 45 dBm0                                                                                                                                                                                                                                                  | 35<br>29<br>25               |     |                          | dBc<br>dBc<br>dBc    |

| S/D <sub>x</sub> | Transmit Signal to Distortion<br>Ratio                          | Sinusoidal Test Method Input<br>Level<br>— 30 dBm0 to 0 dBm0<br>— 40 dBm0<br>— 45 dBm0                                                                                                                                                                                                                                                  | 35<br>29<br>25               |     | dBc<br>dBc<br>dBc        |                      |

| N <sub>R</sub>   | Receive Idle Channel Noise                                      | D <sub>R</sub> = Steady State PCM Code                                                                                                                                                                                                                                                                                                  |                              |     | 6                        | dBrnc0               |

| N <sub>x</sub>   | Transmit Idle Channel Noise                                     | TP3020, (No Signaling)<br>TP3021 (Note 1)                                                                                                                                                                                                                                                                                               |                              |     | 13<br>-66*               | dBrnc0<br>dBn0p      |

| HDR              | Receive Harmonic Distortion                                     | 2nd or 3rd Harmonic                                                                                                                                                                                                                                                                                                                     |                              |     | -47                      | dB                   |

| HD <sub>x</sub>  | Transmit Harmonic Distortion                                    | 2nd or 3rd Harmonic                                                                                                                                                                                                                                                                                                                     |                              |     | -47                      | dB                   |

| PPSRX            | Positive Power Supply<br>Rejection, Transmit                    | Input Level = 0V, V <sub>CC</sub> = 5.0 V <sub>DC</sub><br>+ 300 mVrms, f = 1.02 kHz                                                                                                                                                                                                                                                    | 50                           |     |                          | dB                   |

## **AC Electrical Characteristics** (Continued)

Unless otherwise noted, the analog input is a 0 dBm0, 1.02 kHz sine wave. The digital input is a PCM bit stream generated by passing a 0 dBm0, 1.02 kHz sine wave through an ideal encoder. All output levels are  $\sin x/x$  corrected. Limits printed in **BOLD** characters are guaranteed for  $V_{CC} = +5V \pm 5\%$ ,  $V_{BB} = -5V \pm 5\%$ ;  $T_A = 0^{\circ}C$  to  $+70^{\circ}C$  by correlation with 100% electrical testing at  $T_A = 25^{\circ}C$ . All other limits are assured by correlation with other production tests and/or product design and characterization. All signals referenced to GND. Typicals specified at  $V_{CC} = +5V$ ,  $V_{BB} = -5V$ ,  $T_A = 25^{\circ}C$ .

| Symbol            | Parameter                                    | Conditions                                                                                              | Min | Тур | Max                 | Units    |

|-------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------|-----|-----|---------------------|----------|

| PPSR <sub>R</sub> | Positive Power Supply<br>Rejection, Receive  | D <sub>R</sub> = Steady PCM Code,<br>V <sub>CC</sub> = 5.0 V <sub>DC</sub> + 300 mVrms,<br>F = 1.02 kHz | 40  |     | -                   | dB       |

| NPSRX             | Negative Power Supply<br>Rejection, Transmit | Input Level = 0V, V <sub>BB</sub> = -5.0 V <sub>DC</sub><br>+ 300 mVrms, f = 1.02 kHz                   | 50  |     |                     | dΒ       |

| NPSR <sub>R</sub> | Negative Power Supply<br>Rejection, Receive  | $D_R$ = Steady PCM Code,<br>$V_{BB}$ = -5.0 $V_{DC}$ + 300 mVrms,<br>f = = 1.02 kHz                     | 45  |     |                     | dB       |

| CT <sub>XR</sub>  | Transmit to Receive Crosstalk                | D <sub>R</sub> = Steady PCM Code                                                                        |     |     | <b>-75</b>          | dB       |

| CT <sub>RX</sub>  | Receive to Transmit Crosstalk                | Transmit Input Level = 0V<br>TP3020<br>TP3021                                                           |     |     | -70<br>-65 (Note 2) | dB<br>dB |

Note 2: Theoretical worst-case for a perfectly zeroed encoder with alternating sign bit, due to the decoding law.

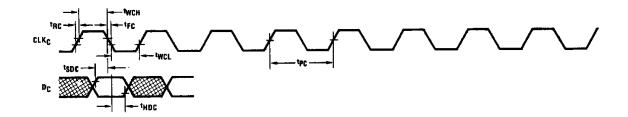

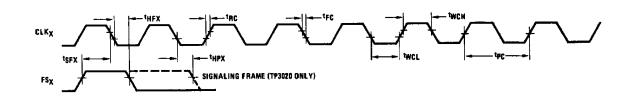

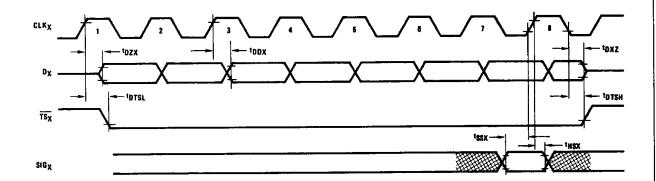

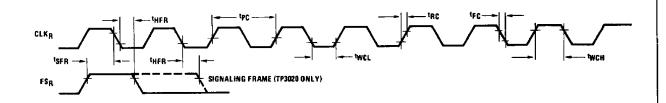

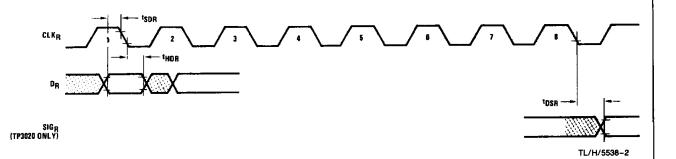

**Timing Specification** Unless otherwise noted, limits printed in **BOLD** characters are guaranteed for  $V_{CC}=+5V\pm5\%$ ,  $V_{BB}=-5V\pm5\%$ ;  $T_A=0^{\circ}C$  to 70°C by correlation with 100% electrical testing at  $T_A=25^{\circ}C$ . All other limits are assured by correlation with other production tests and/or product design and characterization. All digital signals referenced to GND. Typicals specified at  $V_{CC}=+5V$ ,  $V_{BB}=-5V$ ,  $T_A=25^{\circ}C$ . All timing parameters are measured at  $V_{OH}=2.0V$  and  $V_{OL}=0.7V$ .

| Symbol                            | Parameter                                                        | Conditions                                                        | Min | Тур    | Max | Units         |

|-----------------------------------|------------------------------------------------------------------|-------------------------------------------------------------------|-----|--------|-----|---------------|

| t <sub>PC</sub>                   | Period of Clock                                                  | CLK <sub>C</sub> , CLK <sub>R</sub> , CLK <sub>X</sub>            | 485 |        |     | ns            |

| t <sub>RC</sub> , t <sub>FC</sub> | Rise and Fall Time of Clock                                      | CLK <sub>C</sub> , CLK <sub>R</sub> , CLK <sub>X</sub>            |     |        | 30  | ns            |

| twch                              | Width of Clock High                                              | CLK <sub>C</sub> , CLK <sub>R</sub> , CLK <sub>X</sub>            | 165 |        |     | ns            |

| t <sub>WCL</sub>                  | Width of Clock Low                                               | CLK <sub>C</sub> , CLK <sub>R</sub> , CLK <sub>X</sub>            | 165 |        |     | ns            |

| <sup>t</sup> A/D                  | A/D Conversion Time                                              | From End of Encoder Time<br>Slot to Completion of<br>Conversion   |     |        | 16  |               |

| t <sub>D/A</sub>                  | D/A Conversion Time                                              | From End of Decoder Time<br>Slot to Transition of VF <sub>R</sub> |     |        | 2   | Time<br>Slots |

| t <sub>SDC</sub>                  | Set-Up Time, D <sub>C</sub> to CLK <sub>C</sub>                  |                                                                   | 100 |        |     | ns            |

| t <sub>HDC</sub>                  | Hold Time, CLK <sub>C</sub> to DC                                |                                                                   | 100 |        |     | ns            |

| t <sub>SFX</sub>                  | Set-Up Time, FS <sub>X</sub> to CLK <sub>X</sub>                 |                                                                   | 100 |        |     | ns            |

| t <sub>HFX</sub>                  | Hold Time, CLK <sub>X</sub> to FS <sub>X</sub>                   |                                                                   | 100 |        |     | ns            |

| <sup>t</sup> DZX                  | Delay Time to Enable D <sub>X</sub> on TS Entry                  | C <sub>L</sub> =150 pF                                            | 25  | 125    |     | ns            |

| t <sub>DDX</sub>                  | Delay Time, CLK <sub>X</sub> to D <sub>X</sub>                   | C <sub>L</sub> = 150 pF                                           |     |        | 125 | ns            |

| t <sub>DXZ</sub>                  | Delay Time, D <sub>X</sub> to High<br>Impedance State on TS Exit | C <sub>L</sub> =0 pF                                              | 50  | 50 165 |     | ns            |

| t <sub>DTSL</sub>                 | Delay to TS <sub>X</sub> Low                                     | 0≤C <sub>L</sub> ≤ 150 pF                                         | 30  |        | 185 | ns            |

| <sup>†</sup> DTSH                 | Delay to TS <sub>X</sub> Off                                     | C <sub>L</sub> =0 pF                                              | 30  |        | 185 | ns            |

| tssx                              | Set-Up Time, $SIG_X$ to $CLK_X$                                  |                                                                   | 100 | -      |     | ns            |

| t <sub>HSX</sub>                  | Hold Time, CLK <sub>X</sub> to SIG <sub>X</sub>                  |                                                                   | 100 |        |     | ns            |

| t <sub>SFR</sub>                  | Set-Up Time, FS <sub>R</sub> to CLK <sub>R</sub>                 |                                                                   | 100 |        |     | ns            |

| t <sub>HFR</sub>                  | Hold Time, CLK <sub>R</sub> to FS <sub>R</sub>                   |                                                                   | 100 |        |     | ns            |

| t <sub>SDR</sub>                  | Set-Up Time, D <sub>R</sub> to CLK <sub>R</sub>                  |                                                                   | 40  |        |     | ns            |

| t <sub>HDR</sub>                  | Hold Time, CLK <sub>R</sub> to D <sub>R</sub>                    |                                                                   | 30  |        |     | ns            |

| t <sub>DSR</sub>                  | Delay Time, CLK <sub>B</sub> to SIG <sub>B</sub>                 | C <sub>L</sub> =100 pF                                            |     |        | 300 | ns            |

# **Timing Waveforms**

## **Functional Description**

#### POWER-UP

Upon application of power, internal circuitry initializes the CODEC and places it into the power-down mode. No sequencing of 5V or  $-5\mathrm{V}$  is required. In the power-down mode, all non-essential circuits are deactivated, the TRI-STATE PCM data output  $D_X$  is placed in the high impedance state and the receive signaling output of the TP3020, SIGR, is reset to logical zero. Once in the power-down mode, the method of activating the TP3020/TP3021 depends on the chosen mode of operation, time slot assignment or fixed time slot.

#### TIME SLOT ASSIGNMENT MODE

The time slot assignment mode of operation is selected by maintaining CLKC in a normally low state. The state of the CODEC is updated by pulsing CLKC eight times within a period of 125  $\mu$ S or less. The falling edge of each clock pulse shifts the data on the DC input into the CODEC. The first two control bits determine if the subsequent control bits B3-B8 are to specify the time slot for the encoder (B1=0), the decoder (B2=0) or both (B1 and B2=0) or if the CO-DEC is to be placed into the power-down mode (B1 and B2=1). The desired action will take place upon the occurrence of the second frame sync pulse following the first pulse of CLK<sub>C</sub>. Assigning a time slot to either the encoder or decoder will automatically power-up the entire CODEC circuit. The DX output and DR input, however, will be inhibited for one additional frame to allow the analog circuitry time to stabilize. If separate time slots are to be assigned to the encoder and the decoder, the encoder time slot should be assigned first. This is necessary because up to four frames are required to assign both time slots separately, but only three frames are necessary to activate the D<sub>X</sub> output. If the encode time slot has not been updated the PCM data will be outputted during the previously assigned time slot which may now be assigned to another CODEC.

#### **FIXED TIME SLOT MODE**

There are several ways in which the TP3020/TP3021 may operate in the fixed time slot mode. The first and easiest method is to leave  ${\sf CLK}_C$  disconnected or to connect  ${\sf CLK}_C$  to  ${\sf V}_{CC}.$  In this situation,  ${\sf D}_C$  behaves as a power-down input. When  ${\sf D}_C$  goes low, both encode and decode time slots are set to one on the second subsequent frame sync pulse. Time slot one corresponds to the eight  ${\sf CLK}_X$  or  ${\sf CLK}_R$  cycles starting one cycle from the nominal leading edge of  ${\sf FS}_X$  or  ${\sf FS}_R$  respectively. As in the time slot assignment mode, the  ${\sf D}_X$  output is inhibited for one additional frame after the circuit is powered up. A logical "1" on  ${\sf D}_C$  powers the CODEC down on the second subsequent  ${\sf FS}_X$  pulse.

A second fixed time slot method is to operate  $CLK_C$  continuously. Placing a "1" on  $D_C$  will then cause the serial control register to fill up with ones. With B1 and B2 equal to "1" the CODEC will power-down. Placing a "0" on  $D_C$  will cause the serial control register to fill up with zeroes, assigning time slot one to both the encoder and decoder and powering up the device. One important restriction with this method of operation is that the rising transition of  $D_C$  must occur at least 8 cycles of  $CLK_C$  prior to  $FS_X$ . If this restriction is not fol-

lowed, it is possible that on the frame prior to power-down, the encoder could be assigned to an incorrect time slot (e.g., 1, 3, 7, 15 or 31), resulting in a possible PCM bus conflict.

#### **SERIAL CONTROL PORT**

When the TP3020/TP3021 is operated in the time slot assignment mode or the fixed time slot mode with continuous clock, the data on  $D_C$  is shifted into the serial control register, bit 1 first. In the time slot assignment mode, depending on B1 and B2, the data in the RCV or XMT time slot registers is updated at the second  $FS_R$  or  $FS_X$  pulse after the first  $CLK_C$  pulse, or the CODEC is powered down. In the continuous clock fixed time slot mode, the CODEC is powered up or down at every second  $FS_R$  or  $FS_X$  pulse. The control register data is interpreted as follows:

| B1 | <b>B</b> 2 | Action           |                                         |           |            |           |  |  |  |

|----|------------|------------------|-----------------------------------------|-----------|------------|-----------|--|--|--|

| 0  | 0          | Assig            | Assign time slot to encoder and decoder |           |            |           |  |  |  |

| 0  | 1          | Assiç            | Assign time slot to encoder             |           |            |           |  |  |  |

| 1  | 0          | Assiç            | ın time s                               | slot to d | ecoder     |           |  |  |  |

| 1  | 1          | Power-down CODEC |                                         |           |            |           |  |  |  |

| В3 | B4         | <b>B</b> 5       | <b>B</b> 6                              | B7        | <b>B</b> 8 | Time Slot |  |  |  |

| 0  | 0          | 0                | 0                                       | 0         | 0          | 1         |  |  |  |

| 0  | 0          | 0                | 0                                       | 0         | 1          | 2         |  |  |  |

| 0  | 0          | 0                | 0                                       | 1         | 0          | 3         |  |  |  |

| 0  | 0          | 0                | 0                                       | 1         | 1          | 4         |  |  |  |

|    |            |                  |                                         |           |            |           |  |  |  |

|    |            |                  |                                         |           |            |           |  |  |  |

|    |            |                  |                                         |           |            |           |  |  |  |

| 1  | 1          | 1                | 1                                       | 1         | 0          | 63        |  |  |  |

| 1  | 1          | 1                | 1                                       | 1         | 1          | 64        |  |  |  |

During the power-down command, bits 3 through 8 are ignored. Note that with 64 possible time slot assignments it is frequently possible to assign a time slot which does not exist. This can be useful to disable an encoder or decoder without powering down the CODEC.

#### **SIGNALING**

The TP3020  $\mu$ -law CODEC contains circuitry to insert and extract signaling information for the PCM data. The transmit signaling frame is signified by widening the FS $_X$  pulse from one cycle of CLK $_X$  to two or more cycles.

When this occurs, the data present on the  $SIG_X$  input at the eighth clock pulse of the encode time slot is inserted into the last bit of the PCM data stream. A receive signaling frame is indicated in a similar fashion by widening the  $FS_R$  pulse to two or more cycles of  $CLK_R$ .

During a receive signaling frame, the last PCM bit shifted in is latched into a flip-flop and appears at the SIG<sub>R</sub> output. This output will remain unchanged until the next signaling frame, until a power-down is executed or until power is removed from the device. Since the least significant bit of the PCM data is lost during a signaling frame, the decoder interprets the bit as a "½" (i.e., half way between a "0" and a "1"). This minimizes the noise and distortion due to the signaling.

# Functional Description (Continued)

#### **ENCODING DELAY**

The encoding process begins at the start of the encode time slot and is concluded no later than 17 time slots later. In normal applications, this PCM data is not shifted out until the next time slot 125  $\mu$ S later, resulting in an encoding delay of 125  $\mu$ S. In some applications it is possible to operate the CODEC at a higher frame rate to reduce this delay. With a 2.048 MHz clock, the FS rate could be increased to 15 kHz reducing the delay from 125  $\mu$ S to 67  $\mu$ S.

#### **DECODING DELAY**

The decoding process begins immediately after the end of the decoder time slot. The output of the decoder sample and hold amplifier is updated 28 CLK<sub>B</sub> cycles later. The decoding delay is therefore approximately 28 clock cycles plus one half of a frame time or 81  $\mu$ S for a 1.544 MHz system with an 8 kHz frame rate or 76  $\mu$ S for a 2.048 MHz system with an 8 kHz frame rate. Again, for some applications the frame rate could be increased to reduce this delay.

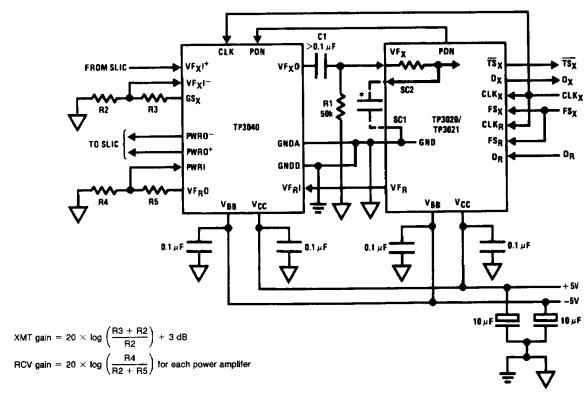

#### TYPICAL APPLICATION

A typical application of the TP3020/TP3021 used in conjunction with the TP3040 PCM filter is shown. The values of resistor R1 and DC blocking capacitor C1, are non-critical. The capacitor value should exceed 0.1  $\mu$ F, R1 should not exceed 160 k $\Omega$ , and the product R1  $\times$  C1 should exceed 4 rms. 0.1  $\mu$ f power supply bypass capacitors should be used and placed as close to the device as possible.

## **Typical Application**

TL/H/5538-5

The power supply decoupling capacitors should be 0.1  $\mu$ F. In order to take advantage of the excellent noise performance of the TP3020/TP3021/TP3040, care must be taken in board layout to prevent coupling of digital noise into the sensitive analog lines.

\*The external sample/hold capacitor required for use with pin-compatible NMOS CODECs introduces attenuation due to the capacitive divider formed with C1. The SC pin connects VF<sub>X</sub> to this sample/hold capacitor (via a 300Ω resistor) to ensure gain compatibility. The TP3020/TP3021 itself does not require an external sample/hold capacitor.