### **General Description**

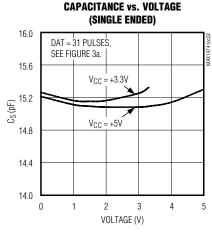

The MAX1474 is a fine-line (geometry) electronically trimmable capacitor (FLECAP) programmable through a simple digital interface. There are 32 programmable capacitance values ranging from 6.4pF to 13.3pF in 0.22pF increments (Table 1). The quartz dielectric capacitance is highly stable and exhibits a very low voltage coefficient. It has virtually no dielectric absorption and has a very low temperature drift coefficient (<33ppm/°C). The MAX1474 is programmed through two digital interface pins, which have Schmidt triggers and pulldown resistors to secure capacitance programming.

#### **Customization**

Maxim can customize the MAX1474 for specific highvolume applications. Contact Maxim for further information.

### **Applications**

Post-Trim of Low-Cost Regenerative Receivers Tunable RF Stages Low-Cost, Low-Temperature Drift Oscillators Garage Door Openers Keyless Entry Industrial Wireless Control Capacitive Sensor Trimming **RFID Tags**

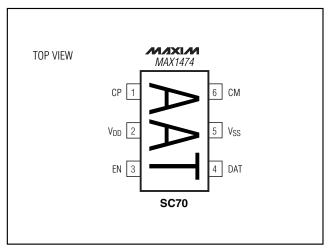

## **Pin Configuration**

#### **Features**

- ◆ Tiny SC70 Package (1.1mm x 2.2mm x 2.4mm)

- **♦ High-Performance Electronically Trimmable** Capacitance

- ♦ Very Simple Digital Interface

- ♦ Eliminates the Need for Mechanical Tuning

- ♦ Enabling Technology for Low-Cost Production **Line Automation**

- ♦ Fully Static Operation After Programming (No Switching)

### **Ordering Information**

| PART         | TEMP. RANGE     | PIN-<br>PACKAGE | TOP<br>MARK |

|--------------|-----------------|-----------------|-------------|

| MAX1474AXT-T | -40°C to +125°C | 6 SC70-6        | AAT         |

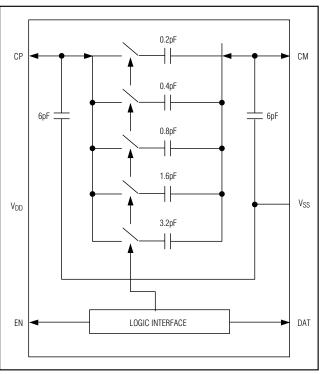

## **Functional Diagram**

MIXIM

Maxim Integrated Products 1

#### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage, $V_{DD}$ to $V_{SS}$          | Operating Temperature Range  MAX1474AXT |

|-----------------------------------------------|-----------------------------------------|

| 6-Pin SC70 (derate 3.1mW/°C above +70°C)245mW | Lead Temperature (soldering, 10s)+300°C |

|                                               |                                         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{DD} = +5V, V_{SS} = 0, T_A = +25^{\circ}C, unless otherwise noted.)$

| PARAMETER                            | SYMBOL                              | CONDITIONS                             | MIN                       | TYP  | MAX                       | UNITS  |

|--------------------------------------|-------------------------------------|----------------------------------------|---------------------------|------|---------------------------|--------|

| GENERAL CHARACTERISTICS              |                                     |                                        |                           |      |                           |        |

| Supply Voltage                       |                                     |                                        | 2.7                       |      | 5.5                       | V      |

| Supply Current                       |                                     | Normal DC operation only, EN, DAT pins |                           |      | 10                        | μΑ     |

| Supply Current                       |                                     | During programming at 1MHz             |                           | 200  |                           | μΑ     |

| CAPACITOR CHARACTERISTICS            |                                     |                                        |                           |      |                           |        |

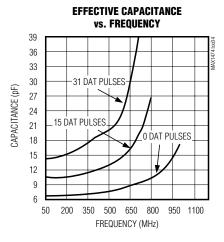

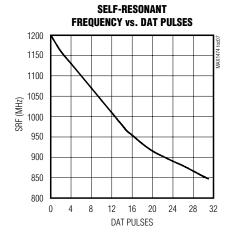

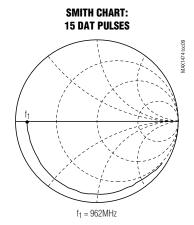

| Self-Resonant Frequency              | SRF                                 | 15 DAT pulses                          |                           | 960  |                           | MHz    |

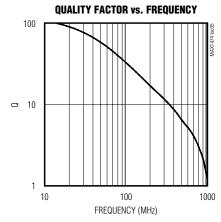

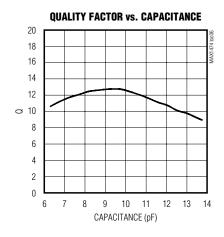

| Quality Factor                       | Q                                   | $f_0 = 315MHz$                         |                           | 12   |                           |        |

| Absolute Accuracy                    |                                     |                                        |                           | ±15  |                           | %      |

| Capacitance Increments (Note 1)      |                                     |                                        |                           | 0.22 |                           | рF     |

| Capacitance at 0 DAT Pulses (Note 1) | C <sub>MIN</sub>                    |                                        |                           | 6.4  |                           | рF     |

| Capacitance Range (Note 1)           | C <sub>MAX</sub> - C <sub>MIN</sub> |                                        |                           | 6.9  |                           | pF     |

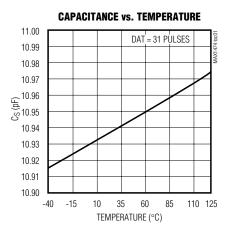

| Temperature Drift                    |                                     |                                        |                           | 33   |                           | ppm/°C |

| DIGITAL CHARACTERISTICS              |                                     |                                        |                           |      |                           |        |

| Low-Level Input Voltage              | VIL                                 |                                        |                           |      | 0.25 x<br>V <sub>DD</sub> | V      |

| High-Level Input Voltage             | VIH                                 |                                        | 0.75 x<br>V <sub>DD</sub> |      |                           | V      |

| Input Pulldown Resistor              |                                     |                                        |                           | 50   |                           | kΩ     |

| Input Leakage Current                |                                     |                                        |                           | 200  |                           | μΑ     |

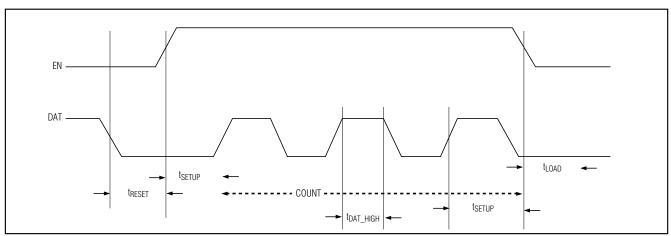

| TIMING CHARACTERISTICS               |                                     |                                        |                           |      |                           |        |

| Maximum Clock Rate on DAT            | fDAT                                |                                        |                           | 25   |                           | MHz    |

| Minimum DAT High Pulse Width         | tdat_high                           |                                        |                           | 20   |                           | ns     |

| Minimum Setup Time for DAT           | tSETUP                              |                                        |                           | 20   |                           | ns     |

| Minimum Data Load Time               | tload                               |                                        |                           | 20   |                           | ns     |

| Minimum Reset Time                   | treset                              |                                        |                           | 20   |                           | ns     |

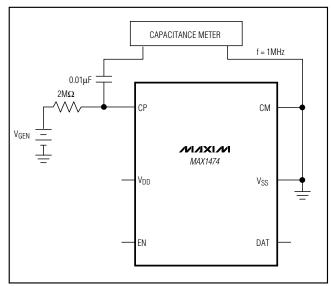

**Note 1:** Measurements made at CP with CM = GND.

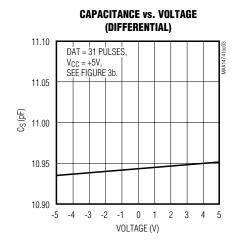

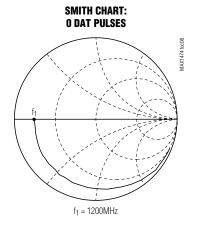

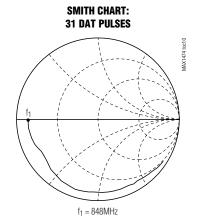

### **Typical Operating Characteristics**

$(V_{DD} = +5V, V_{SS} = 0, T_A = +25$ °C, unless otherwise noted.)

### Typical Operating Characteristics (continued)

$(V_{DD} = +5V, V_{SS} = 0, T_A = +25^{\circ}C, unless otherwise noted.)$

### **Pin Description**

| PIN | NAME            | FUNCTION                                                                       |

|-----|-----------------|--------------------------------------------------------------------------------|

| 1   | СР              | Capacitor Pin Connected to High-Impedance Node. See Detailed Description.      |

| 2   | V <sub>DD</sub> | Positive Supply Pin. Connect a 0.01µF capacitor to Vss.                        |

| 3   | EN              | Programming Enable Pin. Has an internal 50k $\Omega$ pulldown resistor to VSS. |

| 4   | DAT             | Programming Data Pin. Has an internal 50k $\Omega$ pulldown resistor to VSS.   |

| 5   | V <sub>SS</sub> | Negative Supply Pin                                                            |

| 6   | CM              | Capacitor Pin Connected to Low-Impedance Node. See Detailed Description.       |

#### **Detailed Description**

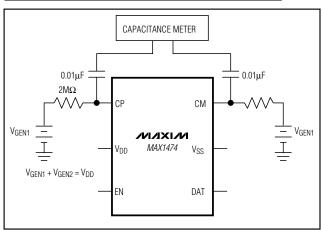

The MAX1474 consists of a binary-weighted array of capacitors that can be switched in and out of parallel to provide 32 monotonic steps. The switches implemented allow the DC bias of either terminal of the capacitor to be anywhere from ground to the supply voltage. There is no inherent polarity. The signal swing range is limited to 300mV above VDD and 300mV below Vss. Therefore, if a large-signal swing range is desired, care must be taken to bias the terminal(s) requiring high swing capability near midsupply.

If the capacitance is measured differentially from one terminal to the other, the greatest min/max ratio of the binary array can be realized, allowing tuning from 0.42pF to 10.9pF in 0.34pF steps. If one terminal is grounded, and the capacitance is measured to ground, the parasitics inherent in the package will become lumped with the switched array, allowing tuning from 6.4pF to 13.3pF in 0.22pF steps. When using the MAX1474, it is recommended for optimal performance to connect the CM terminal to the lowest impedance node (i.e., ground or supply if possible) and CP to the higher impedance node (i.e., the resonant node in a ground-referenced LC tank circuit).

#### **Digital Interface**

The digital interface sets the desired capacitance value. There are only two pins, EN and DAT, required for this operation. EN is an active-high control signal.

While EN is asserted, the internal counter counts positive edges of DAT. The number of sequential pulses on DAT determines the capacitance setting. As EN is deasserted, the counter value is latched into the capacitance control registers first, and then the counter is set to zero. The programmed capacitance value then appears between CP and CM. During the period when EN is asserted, the capacitance value between CP and CM stays unchanged. Figure 1 is a digital timing diagram.

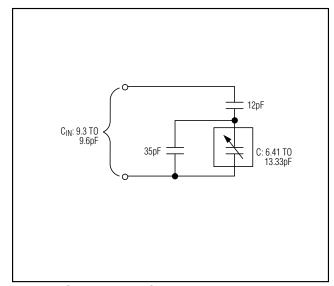

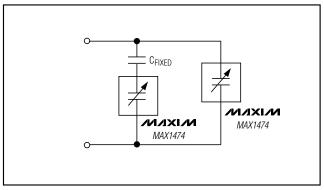

#### **Q** Enhancement Circuit

Since the capacitors have the multiplexer series resistance associated with them, the quality factor of the trimmable capacitors is not high. For example, a 10pF capacitor only has a theoretical Q of about 10 at 315MHz with  $5\Omega$  series resistance. As in Figure 2, an impedance transformer-like circuit is needed to overcome this low Q. With this circuit, a much higher Q is achievable using high-Q external capacitors. This configuration allows a tuning range of approximately 314MHz to 319MHz with 160kHz steps when resonated with a 27nH inductor. Figure 2 shows a Q enhancement circuit.

### Startup Sequence

The MAX1474 must be programmed before use. When powered up, the following sequence must occur:

- Deassert both EN and DAT.

- Assert EN.

- Send pulses on DAT. The total number of pulses determines the capacitance value (Table 1).

- Deassert EN.

## Applications Information

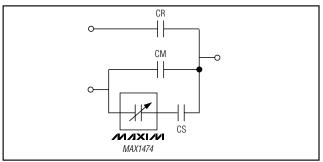

The MAX1474 offers users a wide range of applications, including trimming of regenerative receivers, oscillators, RFID tags, and capacitive sensors. A capacitive sensor is usually made of two capacitors. One capacitor (CM) changes with the sensed function, such as pressure, acceleration, or humidity. The second capacitor (CR) is used as a reference capacitance that does not vary with the sensed function. In most applications, it is needed to detect the difference between these capacitance values. Due to manufacturing tolerances, there are normally offsets between CM and CR, which can easily be nulled out by the FLECAP as shown in Figure 4.

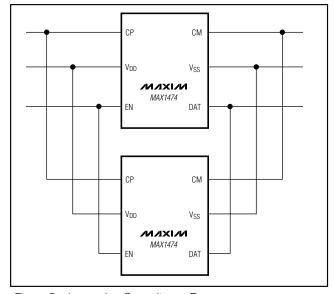

To increase the adjustment capacitance range, several FLECAPs can be placed in parallel. Several capacitors can be tied together to increase the number of steps or the resolution, as shown in Figures 5a and 5b.

The FLECAP zero step differential capacitance is low, typically 0.42pF. The parasitic capacitances are the reason for the 6pF of input capacitance and the decrease in range when configured as a single-ended capacitor. The MAX1474 is an excellent choice in applications where only differential capacitance matters.

**Table 1. Capacitance Values**

| NUMBER OF<br>PULSES ON<br>DAT | TYPICAL VALUES (CM = GND) (pF) | TYPICAL VALUES (DIFFERENTIAL) (pF) |

|-------------------------------|--------------------------------|------------------------------------|

| 0                             | 6.41                           | 0.424                              |

| 1                             | 6.63                           | 0.769                              |

| 2                             | 6.86                           | 1.11                               |

| 3                             | 7.09                           | 1.45                               |

| 4                             | 7.31                           | 1.79                               |

| 5                             | 7.54                           | 2.13                               |

| 6                             | 7.78                           | 2.47                               |

| 7                             | 8.00                           | 2.81                               |

| 8                             | 8.22                           | 3.13                               |

| 9                             | 8.45                           | 3.48                               |

| 10                            | 8.67                           | 3.82                               |

| 11                            | 8.90                           | 4.16                               |

| 12                            | 9.12                           | 4.49                               |

| 13                            | 9.34                           | 4.84                               |

| 14                            | 9.57                           | 5.18                               |

| 15                            | 9.77                           | 5.52                               |

| 16                            | 10.02                          | 5.84                               |

| 17                            | 10.25                          | 6.18                               |

| 18                            | 10.47                          | 6.53                               |

| 19                            | 10.67                          | 6.87                               |

| 20                            | 10.87                          | 7.20                               |

| 21                            | 11.10                          | 7.54                               |

| 22                            | 11.33                          | 7.88                               |

| 23                            | 11.57                          | 8.22                               |

| 24                            | 11.80                          | 8.55                               |

| 25                            | 12.02                          | 8.89                               |

| 26                            | 12.24                          | 9.24                               |

| 27                            | 12.46                          | 9.58                               |

| 28                            | 12.68                          | 9.91                               |

| 29                            | 12.91                          | 10.25                              |

| 30                            | 13.14                          | 10.59                              |

| 31                            | 13.33                          | 10.93                              |

## Test Circuits/Timing Diagrams

Figure 1. Digital Timing Diagram

Figure 2. Q Enhancement Circuit

Figure 3a. Capacitance vs. Voltage (Single Ended)

### Test Circuits/Timing Diagrams (continued)

Figure 3b. Capacitance vs. Voltage (Differential)

Figure 4. Electronic Offset Trimming

Figure 5a. Increasing Capacitance Range

Figure 5b. Increasing Capacitance Range and Resolution

\_Chip Information

TRANSISTOR COUNT: 634

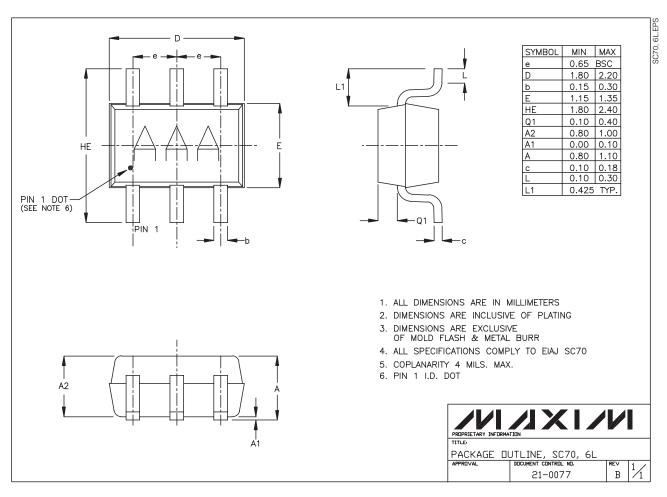

### Package Information

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.