## DM7556/DM8556 TRI-STATE® Programmable Binary Counters

### **General Description**

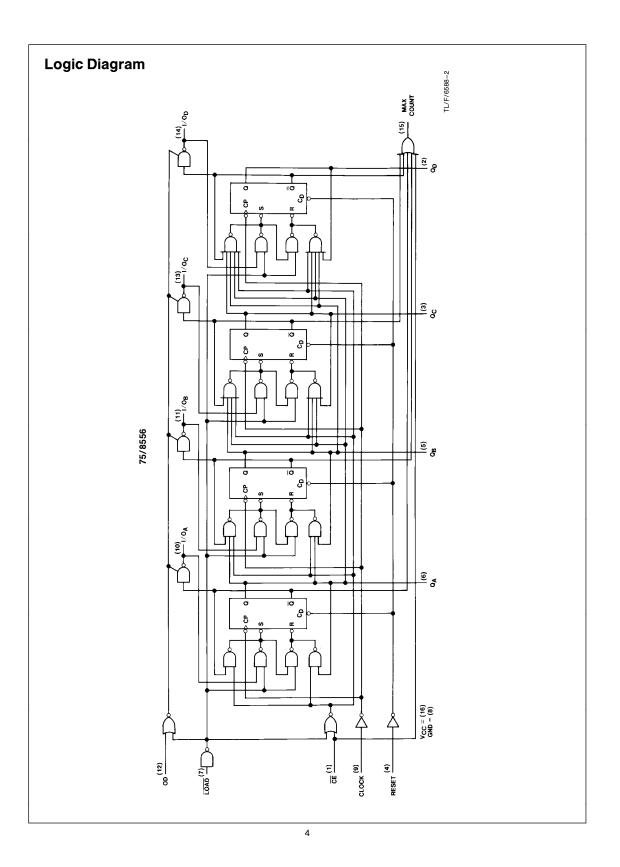

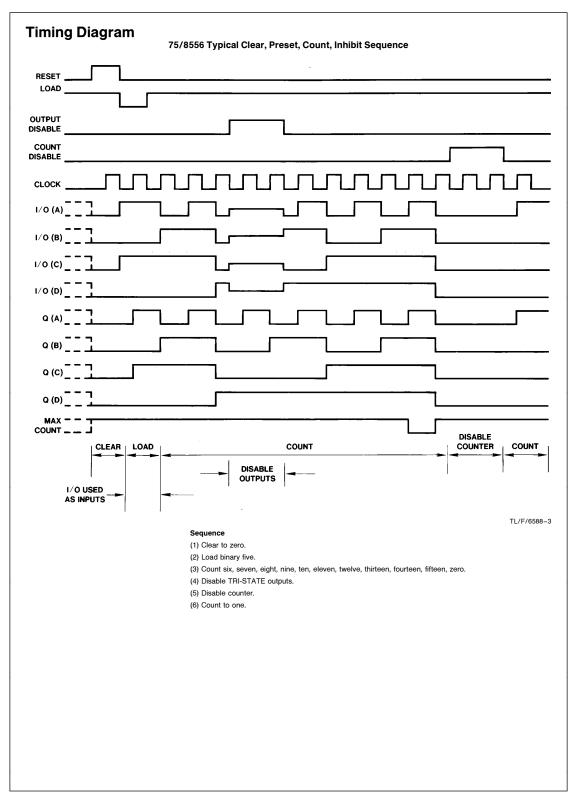

These circuits are synchronous, edge-sensitive, fully-programmable 4-bit counters. The counters feature both conventional totem-pole and TRI-STATE outputs; such that when the outputs are in the high impedance mode, they can be used to enter data from the bus lines. In addition, the clear input operates completely independent of all other inputs. During the programming operation, data is loaded into the flip-flops on the positive-going edge of the clock pulse. To facilitate cascading of these counters, the MAX COUNT output can be tied directly into the count enable input of the next counter.

### **Features**

- Typical clock frequency 35 MHz

- TRI-STATE outputs

- Fully independent clear

- Synchronous loading

- Cascading circuitry provided internally

TL/F/6588-1

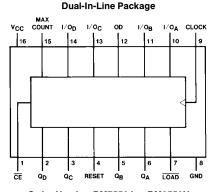

### **Connection Diagram**

### **Function Table**

| Control Inputs                      |                     |               |           | I/O Ports                            |                                   |                  |                  | Active Outputs   |                 |           |                 |                 |

|-------------------------------------|---------------------|---------------|-----------|--------------------------------------|-----------------------------------|------------------|------------------|------------------|-----------------|-----------|-----------------|-----------------|

| LOAD                                | CE                  | CLK           | OD        | Reset                                | 1/0 <sub>A</sub>                  | I/O <sub>B</sub> | I/O <sub>C</sub> | I/O <sub>D</sub> | QA              | QB        | Q <sub>C</sub>  | QD              |

| н                                   | х                   | х             | L         | н                                    | L                                 | L                | L                | L                | L               | L         | L               | L               |

| н                                   | X                   | X             | н         | н                                    | z                                 | Z                | Z                | Z                | L               | L         | L               | L               |

| н                                   | X                   | L             | L         | L                                    | Q <sub>A0</sub>                   | $Q_{B0}$         | $Q_{C0}$         | Q <sub>D0</sub>  | Q <sub>A0</sub> | $Q_{B0}$  | Q <sub>C0</sub> | Q <sub>D0</sub> |

| н                                   | X                   | L             | н         | L                                    | z                                 | Z                | Z                | Z                | Q <sub>A0</sub> | $Q_{B0}$  | Q <sub>C0</sub> | Q <sub>D0</sub> |

| L                                   | н                   | ↑             | L         | L                                    | a                                 | b                | с                | d                | Α               | В         | С               | D               |

| н                                   | L                   | ↑             | L         | L                                    | COUNT COUNT                       |                  |                  |                  |                 |           |                 |                 |

| н                                   | L                   | ↑             | н         | L                                    | Z Z Z Z COUNT                     |                  |                  |                  |                 |           |                 |                 |

| The I/O pir<br>when LOA<br>H = High | D input             | is High a     | and OD    | hen they ar<br>is Low.               | e TRI-ST/                         | ATED, an         | d the LOA        | ND input is      | s Low. Th       | ney are o | utputs ar       | nd activ        |

| L = Low L                           | evel (S             | Steady St     | ate)      |                                      |                                   |                  |                  |                  |                 |           |                 |                 |

| X = Don't                           | Care ir             | ncluding      | transitio | ns                                   |                                   |                  |                  |                  |                 |           |                 |                 |

| a, b, c, d =                        | The I               | evel of th    | ne stead  | dy state inp                         | ut at inpu                        | ts A, B, C       | , D respe        | ctively          |                 |           |                 |                 |

| Q <sub>A0</sub> , Q <sub>B0</sub> , | Q <sub>C0</sub> , Q | $p_{D0} = Th$ | e level   | of Q <sub>A</sub> , Q <sub>B</sub> , | Q <sub>C</sub> , Q <sub>D</sub> r | espective        | ly, before       | the indic        | ated ste        | ady state | input co        | ondition        |

were established.

TRI-STATE® is a registered trademark of the National Semiconductor Corporation.

©1995 National Semiconductor Corporation TL/F/6588

RRD-B30M105/Printed in U. S. A.

# DM7556/DM8556 TRI-STATE Programmable Binary Counters

August 1989

Absolute Maximum Ratings (Note) If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

| Supply Voltage                       | 7V                                  |

|--------------------------------------|-------------------------------------|

| Input Voltage                        | 5.5V                                |

| Operating Free Air Temperature Range |                                     |

| DM75                                 | -55°C to +125°C                     |

| DM85                                 | $0^{\circ}C$ to $+70^{\circ}C$      |

| Storage Temperature Range            | $-65^{\circ}$ C to $+150^{\circ}$ C |

Note: The "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaran-teed. The device should not be operated at these limits. The parametric values defined in the "Electrical Characteristics" table are not guaranteed at the absolute maximum ratings. The "Recommended Operating Conditions" table will define the conditions for actual device operation.

### **Recommended Operating Conditions**

| Symbol                | Param                     |           | DM7556 |     |     | DM8556 |     |       |      |

|-----------------------|---------------------------|-----------|--------|-----|-----|--------|-----|-------|------|

| Symbol                | Falain                    | Min       | Nom    | Max | Min | Nom    | Max | Units |      |

| V <sub>CC</sub>       | Supply Voltage            |           | 4.5    | 5   | 5.5 | 4.75   | 5   | 5.25  | V    |

| V <sub>IH</sub>       | High Level Input Voltag   | je        | 2      |     |     | 2      |     |       | V    |

| V <sub>IL</sub>       | Low Level Input Voltage   |           |        |     | 0.8 |        |     | 0.8   | V    |

| I <sub>OH</sub>       | High Level Output Current |           |        |     | -2  |        |     | -5.2  | mA   |

| I <sub>OL</sub>       | Low Level Output Curr     | ent       |        |     | 16  |        |     | 16    | mA   |

| f <sub>CLK</sub>      | Clock Frequency (Note     | e 1)      | 0      |     | 25  | 0      |     | 25    | MHz  |

|                       | Pulse Width<br>(Note 1)   | Clock     | 25     |     |     | 25     |     |       | ns   |

|                       |                           | Clear     | 20     |     |     | 20     |     |       |      |

|                       |                           | Load      | 30     |     |     | 30     |     |       |      |

| t <u>ce</u>           | Count Enable              | Setup     | 30     |     |     | 30     |     |       | - ns |

|                       | Time (Note 1)             | Hold      | - 10   |     |     | -10    |     |       |      |

| tSETUP(1)             | Setup Time High           | Data      | 25     |     |     | 25     |     |       | ns   |

|                       | Logic Level (Note 1)      | Load      | 30     |     |     | 30     |     |       |      |

| t <sub>HOLD(1)</sub>  | Hold Time High            | Data      | 5      |     |     | 5      |     |       | ns   |

|                       | Logic Level (Note 1)      | Load      | -10    |     |     | -10    |     |       |      |

| t <sub>SETUP(0)</sub> | Setup Time Low            | Data      | 30     |     |     | 30     |     |       | - ns |

|                       | Logic Level (Note 1)      | Load      | 25     |     |     | 25     |     |       |      |

| t <sub>HOLD(0)</sub>  | Hold Time Low             | Data      | 5      |     |     | 5      |     |       | ns   |

|                       | Logic Level (Note 1)      | Load      | - 10   |     |     | -10    |     |       | 113  |

| T <sub>A</sub>        | Free Air Operating Ter    | nperature | -55    |     | 125 | 0      |     | 70    | °C   |

Note 1:  $T_{A}\,=\,25^{\circ}C$  and  $V_{CC}\,=\,5V.$

| Symbol           | Parameter                                                             | Condi                                                                                                | tions    | Min | Typ<br>(Note 1) | Max  | Units |

|------------------|-----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|----------|-----|-----------------|------|-------|

| VI               | Input Clamp Voltage                                                   | $V_{CC} = Min, I_1 =$                                                                                | = -12 mA |     |                 | -1.5 | V     |

| V <sub>OH</sub>  | High Level Output<br>Voltage                                          | $V_{CC} = Min, I_{OH} = Max$<br>$V_{IL} = Max, V_{IH} = Min$                                         |          | 2.4 |                 |      | v     |

| V <sub>OL</sub>  | Low Level Output<br>Voltage                                           | $V_{CC} = Min, I_{OL} = Max$<br>$V_{IH} = Min, V_{IL} = Max$                                         |          |     |                 | 0.4  | V     |

| lı               | Input Current @ Max<br>Input Voltage                                  | $V_{CC} = Max, V_I = 5.5V$                                                                           |          |     |                 | 1    | mA    |

| IIH              | High Level Input Current                                              | $V_{CC} = Max, V_I = 2.4V$                                                                           |          |     |                 | 40   | μΑ    |

| ۱ <sub>IL</sub>  | Low Level Input Current                                               | $V_{CC} = Max, V_I = 0.4V$                                                                           |          |     |                 | -1.6 | mA    |

| I <sub>OZH</sub> | Off-State Output Current with<br>High Level Output<br>Voltage Applied | $\label{eq:V_CC} \begin{split} V_{CC} &= Max, V_O = 2.4V \\ V_{IH} &= Min, V_{IL} = Max \end{split}$ |          |     |                 | 40   | μΑ    |

| I <sub>OZL</sub> | Off-State Output Current with<br>Low Level Output<br>Voltage Applied  | $V_{CC} = Max, V_{CC}$<br>$V_{IH} = Min, V_{IL}$                                                     | 0        |     |                 | -40  | μΑ    |

| los              | Short Circuit                                                         | V <sub>CC</sub> = Max                                                                                | DM75     | -25 |                 | -70  | mA    |

|                  | Output Current                                                        | (Note 2)                                                                                             | DM85     | -25 |                 | -70  |       |

| Icc              | Supply Current                                                        | V <sub>CC</sub> = Max                                                                                |          |     | 75              | 100  | mA    |

Note 1: All typicals are at  $V_{CC}$  = 5V,  $T_A$  = 25°C. Note 2: Not more than one output should be shorted at a time.

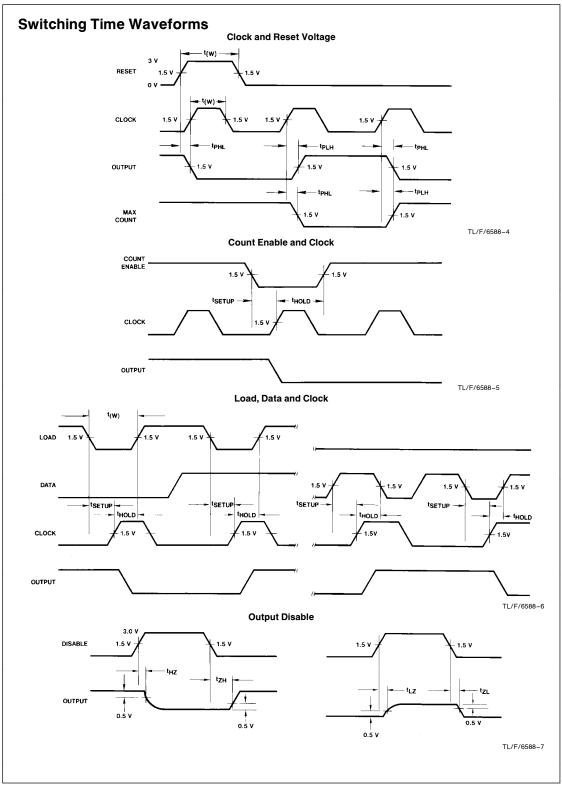

# Switching Characteristics at $V_{CC} = 5V$ and $T_A = 25^{\circ}C$ (See Section 1 for Test Waveforms and Output Load)

| Symbol           |                                                    | From (Input)<br>To (Output) |                         |      |                         |       |     |

|------------------|----------------------------------------------------|-----------------------------|-------------------------|------|-------------------------|-------|-----|

|                  | Parameter                                          |                             | <b>C</b> <sub>L</sub> = | 5 pF | <b>C</b> <sub>L</sub> = | Units |     |

|                  |                                                    |                             | Min                     | Max  | Min                     | Max   |     |

| f <sub>MAX</sub> | Maximum Clock Frequency                            |                             |                         |      | 25                      |       | MHz |

| t <sub>PLH</sub> | Propagation Delay Time<br>Low to High Level Output | Clock to<br>Output          |                         |      |                         | 22    | ns  |

| t <sub>PHL</sub> | Propagation Delay Time<br>High to Low Level Output | Clock to<br>Output          |                         |      |                         | 44    | ns  |

| t <sub>PLH</sub> | Propagation Delay Time<br>Low to High Level Output | Clock to<br>MAX-CNT         |                         |      |                         | 33    | ns  |

| t <sub>PHL</sub> | Propagation Delay Time<br>High to Low Level Output | Clock to<br>MAX-CNT         |                         |      |                         | 33    | ns  |

| t <sub>PHL</sub> | Propagation Delay Time<br>High to Low Level Output | Reset to<br>Output          |                         |      |                         | 44    | ns  |

| t <sub>PZH</sub> | Output Enable Time<br>to High Level Output         | Output<br>Disable to Q      |                         |      |                         | 20    | ns  |

| t <sub>PZL</sub> | Output Enable Time<br>to Low Level Output          | Output<br>Disable to Q      |                         |      |                         | 20    | ns  |

| t <sub>PHZ</sub> | Output Disable Time<br>from High Level Output      | Output<br>Disable to Q      |                         | 12   |                         |       | ns  |

| t <sub>PLZ</sub> | Output Disable Time<br>from Low Level Output       | Output<br>Disable to Q      |                         | 20   |                         |       | ns  |

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications