## Serial Input, Quad 8-Bit Nonvolatile DACPOT™

#### **FEATURES**

- Four 8-Bit DACS

- Differential Non-linearity ±0.5LSB max

- Integral Non-Linearity ±1LSB max

- Each DAC has Independent Reference Inputs

- Output Buffer Amplifiers Swing Rail-to-Rail

- Ground to V<sub>DD</sub> Reference Input Range

- Each DAC's Digital Input Data Maintained in Nonvolatile EEPROM

- Power-On Reset Reloads Registers with Nonvolatile Data

- Simple Serial Interface for Reading and Writing DAC values, SPI<sup>™</sup> and QSPI<sup>™</sup> compatible.

- Fully operational from 2.7V to 5.5V

- Low Power: <1mW @ 2.7V</li>

#### **OVERVIEW**

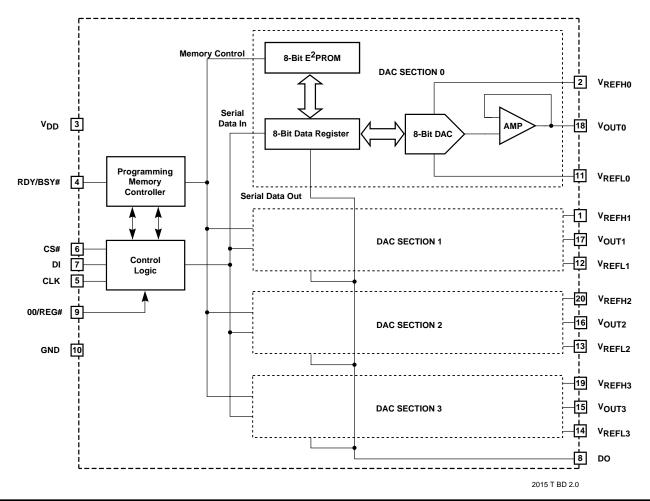

The S9408 DACPOT™ is a serial input, voltage output, quad 8-bit digital to analog converter. The S9408 operates from a single +2.7V to +5.5V supply. Internal precision buffers swing rail-to-rail and the reference input range includes both ground and the positive supply.

The S9408 integrates four 8-bit DACs and their associated circuits which include an enhanced unity-gain operational amplifier output, an 8-bit data latch, an 8-bit non-volatile register, and an industry-standard serial interface for reading and writing data to the DACs' data latches and registers. The DACs are independently programmable and each has its own electrically isolated Vreference inputs.

## **FUNCTIONAL BLOCK DIAGRAM**

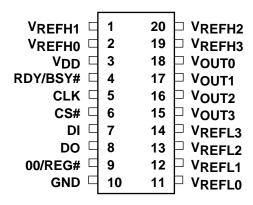

#### **PINOUT and SIGNAL DEFINITION**

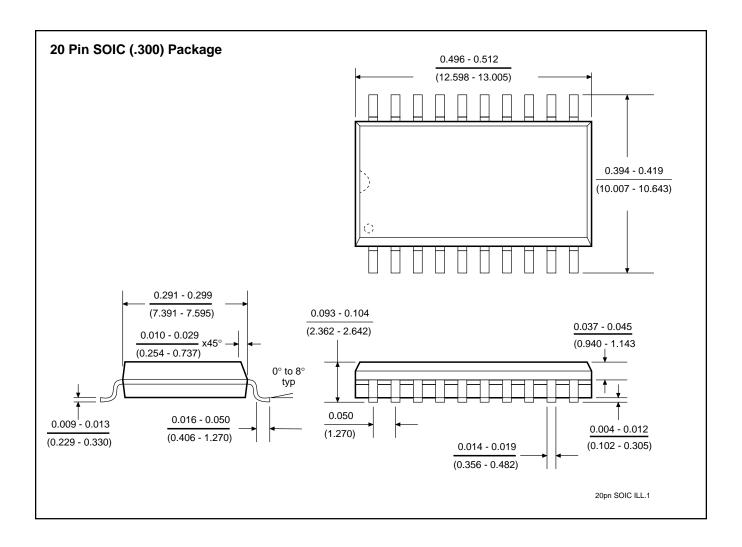

# 20-Pin PDIP or 20-Pin SOIC

2015 T PCon 2.0

The analog outputs of the S9408 can be programmed to any one of 256 individual voltage steps. Each step value is  $1/256^{th}$  of the voltage differential between  $V_{REFH}$  and  $V_{REFL}$  of the respective DAC. Once programmed these settings can be retained in nonvolatile memory during all power conditions and will be automatically recalled upon a power-up sequence. Each DAC can be independently read without affecting the output voltage during the read cycle. In addition, each output can be adjusted an unlimited number of times without altering the value stored in the nonvolatile memory.

#### **DEVICE OPERATION**

## **Analog Section**

The S9804 is an 8-bit, voltage output digital-to-analog converter (DAC). The DAC consists of a resistor network that converts 8-bit digital inputs into equivalent analog output voltages in proportion to the applied reference voltage.

## Reference inputs

The voltage differential between the  $V_{REFL}$  and  $V_{REFH}$  inputs sets the full-scale output voltage for its respective DAC.  $V_{REFL}$  must be equal to or greater than ground (positive voltage).  $V_{REFH}$  must be greater (more positive) than  $V_{REFL}$  and less than or equal to  $V_{DD}$ .

| Pin              | Name              | Function                                                                        |

|------------------|-------------------|---------------------------------------------------------------------------------|

| 1, 2<br>20, 19   | V <sub>REFH</sub> | Vreference High:<br>V <sub>REFL</sub> < V <sub>REFH</sub> - V <sub>DD</sub>     |

| 3                | $V_{DD}$          | Power Supply Voltage                                                            |

| 4                | RDY/BSY#          | Ready/Busy: open drain output indicating status of nonvolatile write operations |

| 5                | CLK               | Clock Input Pin: used for serial data communication                             |

| 6                | CS#               | Chip Select: When high deselects the device and places it in a low power mode   |

| 7                | DI                | Data Input: serial data input pin                                               |

| 8                | DO                | Data Output: serial data output pin                                             |

| 9                | 00/REG#           | Power On Recall Option Input                                                    |

| 10               | GND               | Power Supply Ground                                                             |

| 11, 12<br>13, 14 | V <sub>REFL</sub> | Vreference Low:<br>V <sub>REFH</sub> > V <sub>REFL</sub> • GND                  |

| 15, 16<br>17, 18 | V <sub>OUT</sub>  | DAC Output: buffered D to A converter output                                    |

## **Output Buffer Amplifiers**

The voltage outputs are precision unity-gain followers that slew up to  $1V/\mu s$ . The outputs can swing from  $V_{REFL}$  to  $V_{REFH}$ . With a 0V to 5V output transition the amplifier outputs typically settle to 1LSB in 40 $\mu s$ .

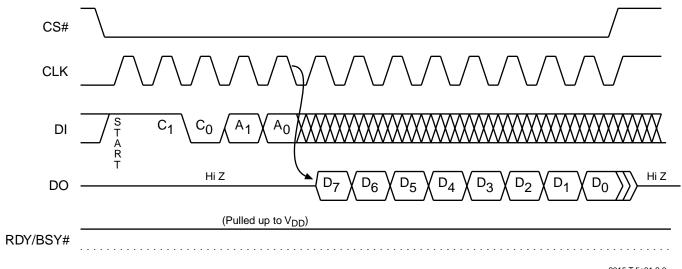

#### DIGITAL INTERFACE

The S9408 employs a common 4-wire serial interface. It is comprised of a Clock (CLK), Chip Select (CS#), Data In (DI) and Data Out (DO). Data is clocked into the device on the clock's rising edge and out of the device on the clock's falling edge. Data is shifted in and out MSB first. DO only becomes active after the device has been selected and after a valid read command and address has been received.

All data transfers are initiated after CS# goes low and a logic '1' is clocked into the device. This first data transfer is the start bit and must precede all operations. Following the start bit are two command bits used to specify which of four commands to execute. The next two bits are the address bits used to select one of the four DACs. The action of the next eight clock cycles will be dependent upon the command issued.

| Start | C <sub>1</sub> | C <sub>o</sub> | A <sub>1</sub> | A <sub>0</sub> | Command         |

|-------|----------------|----------------|----------------|----------------|-----------------|

| 1     | 0              | 0              | Α              | Α              | NV Write Enable |

| 1     | 0              | 1              | Α              | Α              | Write — Data In |

| 1     | 1              | 0              | Α              | Α              | Read — Data Out |

| 1     | 1              | 1              | Α              | Α              | Recall          |

**TABLE 1. COMMAND FORMAT**

Internally there are four DACs and associated with each are two registers. There is one data register that is used by the DAC to hold the digital value it converts. There is also one nonvolatile register that holds the default value that can be recalled into the data register during power-up or by executing the Recall command.

#### READ

Read operations are initiated by taking CS# low and clocking in a start bit followed by the read command and the address of the data register to be read. The next eight clocks will output on the DO pin the contents of the

selected data register. This read will not affect the contents of the register or the output of the DAC. Refer to Figure 1 for an illustration of the sequence of bus conditions for a read operation.

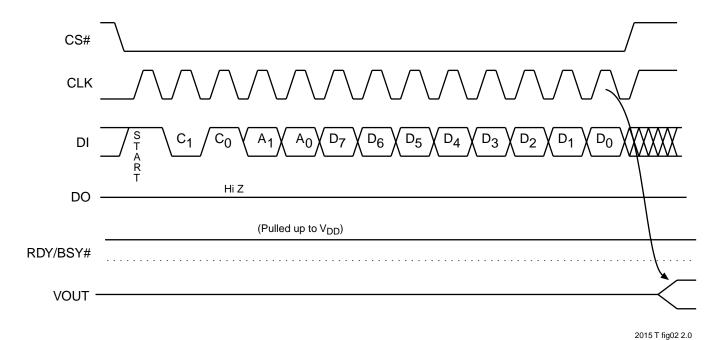

## **WRITE**

Write operations are initiated by taking CS# low and clocking in a start bit followed by the write command and the address of the data register to be written. This action is followed by the host clocking eight bits of data into the register, MSB first. The output of the selected DAC will change as the last bit is clocked into the device. At this point the clock counter will reset the command register, requiring a full sequence to be initiated in order to write to the DAC again.

**NOTE:** This write operation does not affect the contents of the nonvolatile register. Therefore, the nonvolatile register can contain the power-on default settings (e.g. volume), and the write DAC command can be used to make situational adjustments.

Refer to Figure 2 for an illustration of the sequence of bus conditions for a write operation.

FIGURE 1. READ SEQUENCE

2015 T fig01 2.0

## FIGURE 2. WRITE SEQUENCE

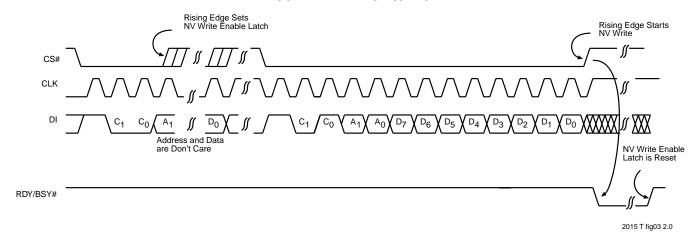

FIGURE 3. NONVOLATILE WRITE SEQUENCE

## **NONVOLATILE WRITE**

A nonvolatile write is a two step operation: it is initiated by taking CS# low and clocking in a start bit followed by the NV Enable command. At this point the host can take CS# back high or continue clocking in data. This data is don't care and will be ignored by the S9408. If any command other than write follows NV enable the NV latch will be cleared.

Next, the host takes CS# low again and issues a write command and address and then clocks in the eight data bits to be programmed. The host will then bring CS#HIGH and the data will be latched into the data register and a nonvolatile write operation will commence.

The status of the nonvolatile write can be monitored on the RDY/BSY# pin. A logic low indicates the write is still in progress and the S9408 will not be accessible to the host; a logic high indicates the write has completed and the S9408 is ready for the next command. Refer to Figure 3 for an illustration of the sequence of bus conditions for a nonvolatile write operation.

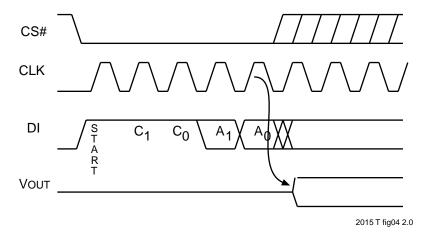

## **RECALL COMMAND**

The recall command will retrieve data from the selected nonvolatile register and write it into the data register of the associated DAC. This operation is initiated by taking CS# low and clocking in a start bit followed by the recall command and the address of the nonvolatile register to be recalled. The eight bits of data are don't care, so CS# can be taken high any time after the address bits are clocked in. Refer to Figure 4 for an illustration of the sequence of bus conditions for a Recall operation.

#### Power-on recall

Whenever the S9408 is powered on the DAC output values will be returned to the selected default setting. The default setting can be the nonvolatile register contents or all zeroes. The state of the 00/REG# pin will determine which operation will be performed. If it is tied to ground (or left floating) the nonvolatile register contents will be recalled. Conversely, if it is tied to  $V_{DD}$  the S9408 will recall zeroes.

FIGURE 4. RECALL COMMAND SEQUENCE

## **ABSOLUTE MAXIMUM RATINGS**

| V <sub>DD</sub> to GND      | 0.5V to +7V                   |

|-----------------------------|-------------------------------|

| Digital Inputs to GND       | 0.5V to V <sub>DD</sub> +0.5V |

| Analog Inputs to GND        | 0.5V to V <sub>DD</sub> +0.5V |

| Digital Outputs to GND      | 0.5V to V <sub>DD</sub> +0.5V |

| Analog Outputs to GND       | 0.5V to V <sub>DD</sub> +0.5V |

| Temperature Under Bias      | 55°C to +125°C                |

| Storage Temperature         | 65°C to +150°C                |

| Lead Soldering (10 Sec Max) | 300°C                         |

Stresses listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions outside those listed in the operational sections of this specification is not implied. Exposure to any absolute maximum rating for extended periods may affect device performance and reliability.

## RECOMMENDED OPERATING CONDITIONS

| Condition   | Min   | Max   |

|-------------|-------|-------|

| Temperature | -40°C | +85°C |

| $V_{DD}$    | +2.7V | +5.5V |

2015 PGM T2 1.2

## RELIABILITY CHARACTERISTICS (Over recommended operating conditions unless otherwise specified)

| Symbol           | Parameter          | Min       | Max | Unit           |

|------------------|--------------------|-----------|-----|----------------|

| $V_{ZAP}$        | ESD Susceptibility | 2000      |     | V              |

| I <sub>LTH</sub> | Latch-up           | 100       |     | mA             |

| T <sub>DR</sub>  | Data Retention     | 100       |     | Years          |

| N <sub>END</sub> | Endurance          | 1,000,000 |     | Storage Cycles |

## DC ELECTRICAL CHARACTERISTICS (Over recommended operating conditions unless otherwise specified)

| Symbol          | Parameter                            | Conditions                                                              | Min            | Тур | Max             | Unit |

|-----------------|--------------------------------------|-------------------------------------------------------------------------|----------------|-----|-----------------|------|

| I <sub>DD</sub> | Supply current during store (note 1) | CS = V <sub>IL</sub>                                                    |                | 1.8 | 3.0             | mA   |

| I <sub>SB</sub> | Standby supply current               | CS = V <sub>IH</sub>                                                    |                | 260 | 500             | μA   |

| I <sub>IH</sub> | Input leakage current                | $V_{IN} = V_{DD}$                                                       |                | <1  | 10              | μA   |

| I <sub>IL</sub> | Input leakage current                | $V_{IN} = 0V$                                                           |                | <1  | -10             | μA   |

| V <sub>IH</sub> | High level input voltage             |                                                                         | 2              |     | V <sub>DD</sub> | V    |

| V <sub>IL</sub> | Low level input voltage              |                                                                         | 0              |     | 0.8             | V    |

| V <sub>OH</sub> | High level output voltage            | IOH = -400μA                                                            | $V_{DD} - 0.3$ |     |                 | V    |

| V <sub>OL</sub> | Low level output voltage             | IOL = 1mA, V <sub>DD</sub> = 5V;<br>IOL = 0.4mA, V <sub>DD</sub> = 2.7V |                |     | 0.4             | V    |

Note 1: I<sub>DD</sub> is the supply current drawn while the EEPROM is being updated.

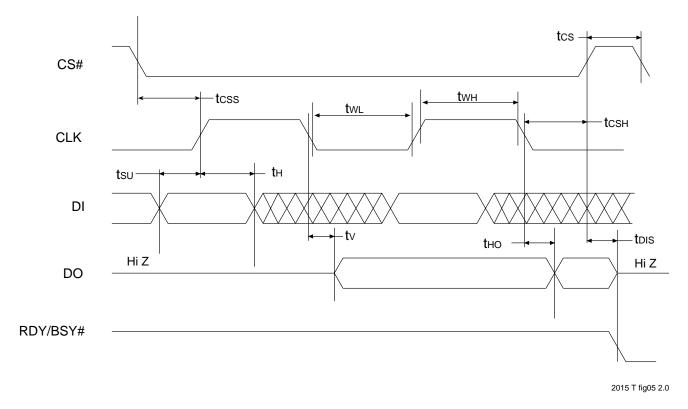

## **AC ELECTRICAL CHARACTERISTICS**

$V_{DD}$  = +4.5V to +5.5V,  $V_{REFH}$  =  $V_{DD}$ ,  $V_{REFL}$  = 0V,  $T_A$  = -40°C to +85°C, unless otherwise specified

| Symbol            | Parameter             | Conditions    | Min. | Тур. | Max. | Units |

|-------------------|-----------------------|---------------|------|------|------|-------|

| f <sub>C</sub>    | Clock Frequency       |               | DC   |      | 1    | MHz   |

| t <sub>WH</sub>   | Minimum CLK High Time |               | 500  |      |      | ns    |

| t <sub>WL</sub>   | Minimum CLK Low Time  |               | 300  |      |      | ns    |

| tCS               | Minimum CS High Time  |               | 150  |      |      | ns    |

| tCSS              | CS Setup Time         |               | 100  |      |      | ns    |

| <sup>t</sup> CSH  | CS Hold Time          |               | 0    |      |      | ns    |

| tsu               | Data In Setup Time    | $C_L = 100pF$ | 50   |      |      | ns    |

| <sup>t</sup> H    | Data In Hold Time     | See Note 1    | 50   |      |      | ns    |

| t <sub>V</sub>    | Output Valid Time     |               |      |      | 150  | ns    |

| <sup>t</sup> HO   | Data Out Hold Time    |               | 0    |      |      | ns    |

| t <sub>DIS</sub>  | Output Disable Time   |               |      | 400  |      | ns    |

| <sup>t</sup> BUSY | Write Cycle Time      |               |      | 3.3  | 5    | ms    |

Notes:

1. All timing measurements are defined at the point of signal crossing  $V_{DD}/2$ .

2015 PGM T5 1.1

FIGURE 5. AC TIMING DIAGRAM

## DAC DC ELECTRICAL CHARACTERISTICS

$V_{DD}$  = 2.7V to 5.5V,  $V_{REFH}$  =  $V_{DD}$ ,  $V_{REFL}$  = 0V,  $T_A$  = -40°C to +85°C, unless otherwise specified

| Property   | Symbol              | Parameter                                               | Conditions                                                       | Min        | Тур      | Max        | Unit     |

|------------|---------------------|---------------------------------------------------------|------------------------------------------------------------------|------------|----------|------------|----------|

| Accuracy   | INL                 | Integral non-linearity                                  | $I_{LOAD} = 100 \mu A$                                           |            | 0.5      | ±1         | LSB      |

| Accuracy   | DNL                 | Differential non-linearity                              | $I_{LOAD} = 100\mu A \text{ (note 1)}$                           |            | 0.1      | ±0.5       | LSB      |

|            | $V_{REFH}$          | Input voltage                                           |                                                                  | $V_{REFL}$ |          | $V_{DD}$   | V        |

|            | $V_{REFL}$          | Input voltage                                           |                                                                  | GND        |          | $V_{REFh}$ | V        |

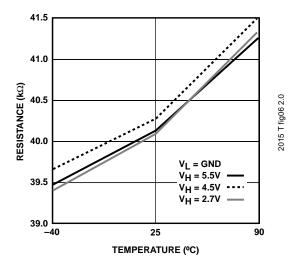

| References | R <sub>IN</sub>     | $V_{\rm \tiny REFH}$ to $V_{\rm \tiny REFL}$ resistance |                                                                  |            | 40k      |            | Ω        |

|            | TCR <sub>IN</sub>   | Temp. coefficient of R <sub>IN</sub>                    |                                                                  |            | 300      | 600        | ppm/ºC   |

|            | $\Delta R_{IN}$     | Input resistance match                                  |                                                                  |            | ±0.5     | ±1         | %        |

|            | $G_{EFS}$           | Full-scale gain error                                   | $D = FF_{HEX}$                                                   |            |          | ±1         | LSB      |

|            | V <sub>out</sub> ZS | Output offset voltage                                   | $D = 00_{HEX}$                                                   | 0          | 2.5      | 5          | mV       |

|            | TCV <sub>OUT</sub>  | $V_{\text{OUT}}$ temp. coeffiecient                     | $V_{DD} = 5V$ , $I_{LOAD} = 50\mu A$ (note 1)                    |            |          | 50         | μV/ºC    |

|            | I <sub>L</sub>      | Amp output load current                                 |                                                                  | -200       |          | 1000       | μΑ       |

| Analog     | R <sub>OUT</sub>    | Amp output resistance                                   | I <sub>LOAD</sub> = 100μA 5V<br>3V                               |            | 10<br>20 |            | $\Omega$ |

| Output     | PSRR                | Power supply rejection                                  | $I_{LOAD} = 10\mu A$                                             |            |          | 1          | LSB/V    |

|            | t <sub>s</sub>      | DAC settling time to 1LSB                               | 10pF 5V<br>10pF 3V                                               |            | 36<br>27 |            | µs<br>µs |

|            | e <sub>N</sub>      | Amp output noise                                        | $f = 1kHz, V_{DD} = 5V$                                          |            | 90       |            | nV√Hz    |

|            | THD                 | Total harmonic distortion                               | $V_{REFH} = 2.5V, V_{DD} = 5V,$<br>$f = 1kHz, V_{IN} = 1V_{RMS}$ |            | 0.08     |            | %        |

|            | BW                  | Bandwidth –3dB                                          | $V_{REFH} = 2.5V, V_{DD} = 5V,$ $V_{IN} = 100 \text{mV}_{RMS}$   |            | 300      |            | kHz      |

Note 1: Guaranteed but not tested

FIGURE 6. VL to VH END-TO-END RESISTANCE OVER TEMPERATURE

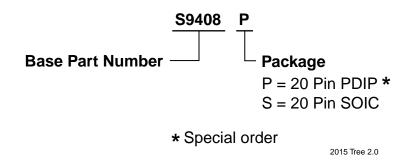

## ORDERING INFORMATION

## NOTICE

SUMMIT Microelectronics, Inc. reserves the right to make changes to the products contained in this publication in order to improve design, performance or reliability. SUMMIT Microelectronics, Inc. assumes no responsibility for the use of any circuits described herein, conveys no license under any patent or other right, and makes no representation that the circuits are free of patent infringement. Charts and schedules contained herein reflect representative operating parameters, and may vary depending upon a user's specific application. While the information in this publication has been carefully checked, SUMMIT Microelectronics, Inc. shall not be liable for any damages arising as a result of any error or omission.

SUMMIT Microelectronics, Inc. does not recommend the use of any of its products in life support or aviation applications where the failure or malfunction of the product can reasonably be expected to cause any failure of either system or to significantly affect their safety or effectiveness. Products are not authorized for use in such applications unless SUMMIT Microelectronics, Inc. receives written assurances, to its satisfaction, that: (a) the risk of injury or damage has been minimized; (b) the user assumes all such risks; and (c) potential liability of SUMMIT Microelectronics, Inc. is adequately protected under the circumstances.

© Copyright 2000 SUMMIT Microelectronics, Inc.