# **USBvision<sup>TM</sup> II Data Decoder**

## VBI Data and Remote Control Interface for ZR6504

## Data Sheet

Revision 1.00

November 1999.

Zoran reserves the right to make changes without further notice to any product herein. Zoran makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Zoran assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. Zoran products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Zoran product could create a situation where personal injury or death may occur.

## Table of Contents:

| 1.  | SERIAL CONTROL                           | 7  |

|-----|------------------------------------------|----|

|     | VBI DATA QUALIFIER                       |    |

| 2.1 | VBI Input Interface                      |    |

| 2.2 | VBI Lines Qualifier                      | 13 |

| 2.3 | VBI and IRD (Remote Control) Data Format | 17 |

| 3.  | Bulk Interface                           | 21 |

| 4.  | Programmable I/O Pins                    | 25 |

|     | Soft Reset operation                     |    |

| 6.  | Mechanical Specification                 | 27 |

**ZR36505** - VBI (Teletext) pipe and Remote Control interface for USB TV applications

The ZR36505 is a complimentary chip for the ZR36504 in USB TV applications. Combined with certain video decoders, it adds a VBI (Vertical Blank Interval) data pipe to the system, which utilizes the general purpose Bulk channel of the NT1004. The VBI is used by TV broadcast providers to send digital data hidden in the analog video signal. One or more video lines, taken from lines 1-21 of each video field are used for carrying this information - each line providing about 9,600 bits/sec data rate.

The ZR36505 provides the application S/W with access to data such as Teletext, Close-Caption, Intercast, IR receiver samples, etc. It uses a 1KByte SRAM buffer to grabe the processed data from the video decoder during the Blank Interval time slot, and sends this data to the USB through the ZR36504 Bulk pipe during the time left prior to beginning of next Blak Interval. For the remote Control interface, the input pin IO\_1 is sampled at 4Ksamp/sec rate, and the sampled bits are moved to host computer via the (NT1004) for S/W process.

#### Features

- Enables Teletext and Close-Caption

- Supports WST625, WST525, CC625, CC525, US NABTS, MOJI (Japanese), and JFS formats

- Provides Remote Control interface with IR receiver (sampled at 4K samp./sec.)

- Low Cost, Low Power, 3.3v operated

- 24-pin SOIC package

#### **Product Description**

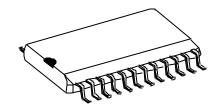

Refer to Fig.1 for an internal Block Diagram of the ZR36505.

The IIC block uses the LRNACK mode of the ZR36504 serial control bus to provide access to its internal registers. The address range for output registers and input registers is 0x00-0x07 each.

The internal Input and Output Registers are used by the Host (PC S/W via ZR36504) to control the parameters of the ZR36505 blocks and to read their status. There are two general I/O pins to be used by S/W for specific designs.

The VBI DATA QUALIFIER block can be programmed to restrict VBI data capture to any specified range of lines within the video field. Also, a specific data type can be defined, to filter out all other types of VBI data.

The 1KByte Buffer is used for capturing all VBI data from every coming video field (after qualification), and sending it via the Bulk Interface. This is done for one field at a time, and Write/Read cannot be done simultaneously.

The BULK INTERFACE block is designed to match the ZR36504 specification. It can coexist with an audio Codec source to share the same clock and data pins of the NT1004.

Finally, The ZR36505 uses 2 clock sources: 27MHz for VBI data, and 48MHz (from NT1004) for the other blocks. The ZR36505 does not require a crystal of its own.

November-99

Fig.1 ZR36505 Block Diagram

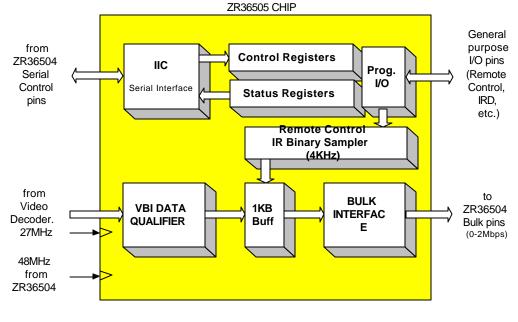

## **Pin Assignments (Top View)**

#### Table 1 - PIN DESCRIPTIONS

| PIN NUMBER | SIGNAL    | I/O | DESCRIPTION                                                                                                                                                                                                                                      |

|------------|-----------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TINNOWIDER | SIGNAL    | 10  | DESCRIPTION                                                                                                                                                                                                                                      |

| 24         | VDD       |     | Digital 3.3V power supply                                                                                                                                                                                                                        |

| 12, 14     | GND       |     | Digital ground connection                                                                                                                                                                                                                        |

| 1          | VSYNC_IN  | Ι   | Video Vertical-Sync input signal from Video Decoder                                                                                                                                                                                              |

| 2          | HSYNC_IN  | Ι   | Video Vertical-Sync input signal from Video Decoder                                                                                                                                                                                              |

| 3-10       | YIN0-YIN7 | Ι   | VBI data-bus from Video Decoder. Usually used also for delivering the digital video samples.                                                                                                                                                     |

| 11         | CLK27     | Ι   | VBI clock from Video Decoder. Used to sample the VBI data in<br>its positive edge. This clock is used for capturing and storing the<br>VBI data.                                                                                                 |

| 13         | CLK48     | Ι   | This is the ZR36505 Global clock, which comes from the NT1004.                                                                                                                                                                                   |

| 15         | DAT_OUT   | 0   | VBI Data Output pin, goes to DAT_IN pin of the<br>ZR36504(which is used for both Audio CODEC T x chan and<br>Bulk Data in This pin is Open Drain, and is set to high-z upon<br>Power-On or Soft Reset. It requires an external pull-up resistor. |

| 16         | BLK_EN    | 0   | Bulk Data Enable output. When set to '1', Bulk output data at DAT_OUT pin is sampled into the ZR36504by falling edge of BCLK.<br>This pin is set to Hi-Z upon Power-On or Soft Reset.                                                            |

| 17         | BLK_FULL  | Ι   | "Bulk-Fifo full" indication signal from NT1004. This signal is<br>normally '0', and is set to '1' when the ZR36504Bulk -Fifo is full.                                                                                                            |

| 18         | FS_L      | Ι   | Audio Codec Frame-Sync pulse for Left channel., which comes<br>from the NT1004. The ZR36505 uses this signal to trigger the<br>beginning of its VBI Bulk data output immediately after the 16th                                                  |

November-99

Page 5 of 5

|    |      |   | bit of audio Left.                                                                                                                                       |

|----|------|---|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 19 | BCLK | Ι | Bulk-data clock (ZR36504uses this clock for both Audio CODEC<br>and Bulk Data). This clock must be set to 2.024MHz for proper<br>operation with ZR36505. |

#### Table 1 - PIN DESCRIPTIONS (continued)

| PIN NUMBER | SIGNAL              | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------|---------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20-21      | IO-1/IRD_IN<br>IO-2 | I/O | General Programmable I/O pins. Each of these 2 pins has a 5-<br>volt Tolerant Open Drain output, and it is supposed to be<br>connected to an external pull-up resistor. The host uses these<br>pins as programmable output ports by writing '0' or '1'. By writing<br>'1' and read back, the host can use these pins as input ports - as<br>this allows any external source to force the pull-up resistor.<br>These outputs are set to high -z upon Power-On or Soft Reset.<br>The pin IO-1 is also used as the input for IRD data. This pin is<br>internally sampled at 4KHz sampling rate. |

| 22         | IICDT               | I/O | This pin is used for sending and receiving serial control data<br>between the ZR36505 (slave) and ZR36504(master). It operates<br>in the LRNACK mode of operation (refer to the ZR36504data<br>sheet). This pin is Open Drain, and is set to high-z upon Power-<br>On or Soft Reset.                                                                                                                                                                                                                                                                                                         |

| 23         | IICCK               | Ι   | This pin is used as the sampling clock for sending and receiving<br>serial control data between the ZR36505 (slave) and<br>ZR36504(master). It operates in the LRNACK mode of<br>operation (refer to the ZR36504data sheet).                                                                                                                                                                                                                                                                                                                                                                 |

#### Table 2- ABSOLUTE MAXIMUM RATINGS (Voltages Referenced to GND)

| Rating                                                     | Symbol                | Value                 | Unit |

|------------------------------------------------------------|-----------------------|-----------------------|------|

| DC Supply Voltage                                          | V <sub>dd</sub> - GND | -0.5 to 4.6           | V    |

| Voltage, any pin to GND                                    | V                     | -0.5 to $V_{dd}$ +0.5 | V    |

| DC Current Drain per Pin (Excluding V <sub>dd</sub> , GND) | Ι                     | ±10                   | mA   |

| Operating Temperature Range                                | T <sub>A</sub>        | 0 to +70              | °C   |

| Storage Temperature Range                                  | T <sub>stg</sub>      | -65 to +150           | °C   |

#### **Table 3 - ELECTRICAL CHARACTERISTICS** ( $V_{dd}$ =3.3V, $T_A$ = 0 to 70°C)

| Characteristic                                               | Symbol          | Min  | Тур | Max                  | Unit |

|--------------------------------------------------------------|-----------------|------|-----|----------------------|------|

| DC Supply Voltage (V <sub>di</sub> to GND)                   | $V_{dd}$        | 3.0  | 3.3 | 3.6                  | V    |

| DC Supply Current (@ V <sub>dd</sub> =3.3V)                  | $I_{cc}$        | -    | 12  | 18                   | mA   |

| High Level Input Voltage (other than XIN, CAPTRN, and RESIN) | $V_{_{\rm IH}}$ | 2.0  | -   | $V_{dd}^{+}+0.3^{*}$ | V    |

| Low Level Input Voltage (other than XIN, CAPTRN, and RESIN)  | V <sub>IL</sub> | -0.3 | -   | 0.8                  | V    |

| Input Current $V_{I} = V_{dd} + 0.3 \text{ or GND}$          | I <sub>in</sub> | -10  | +1  | +10                  | μA   |

| Input Capacitance                                            | C <sub>in</sub> | -    | 2.5 | 7.0                  | pF   |

| 3-State Output Leakage Current $V_0 = V_{dd} + 0.3$ or GND | I <sub>oz</sub>  | -10 | +1  | +10      | μΑ |

|------------------------------------------------------------|------------------|-----|-----|----------|----|

| Output Capacitance                                         | C <sub>out</sub> | -   | 2.0 | 7.0      | pF |

| High Level Output Voltage (@ Iout = -4mA)                  | V <sub>OH</sub>  | 2.4 | -   | $V_{dd}$ | V  |

| Low Level Output Voltage (@ Iout = $4mA$ )                 | V <sub>OL</sub>  | 0   | -   | 0.4      | V  |

## 1. SERIAL CONTROL

The ZR36505 uses a Serial Control Interface to access its internal registers.

| Reg.    | Reg. Name  | Function                                                                                                                | Default |

|---------|------------|-------------------------------------------------------------------------------------------------------------------------|---------|

| Address |            |                                                                                                                         | Value   |

| 0       | LINE_LEN_L | d7-d0: LINE_LEN[70]                                                                                                     | 00H     |

| 1       | LINE_LEN_H | d2-d0: LINE_LEN[108]                                                                                                    | 00H     |

|         |            | d7-d3: reserved                                                                                                         |         |

| 2       | LINE_WIN_L | d7-d0: WIN_OFFSET[70]                                                                                                   | 00H     |

| 3       | LINE_WIN_H | d7-d3: WIN_LEN[40]                                                                                                      | 00H     |

|         |            | d2-d1: reserved                                                                                                         |         |

|         |            | d0: WIN_OFFSET[8]                                                                                                       |         |

| 4       | VBI_REG    | d7: EN_TYPE_QUALIFIER '1': enable '0': disable                                                                          | 00H     |

|         |            | d6: EN_WIN_QUALIFIER '1': enable '0': disable                                                                           |         |

|         |            | d5: EN_RAW_SAMPLES '1': enable '0': disable                                                                             |         |

|         |            | d4: EN_VBI_QUALIFIER '1': enable '0': disable                                                                           |         |

|         |            | d3-d0: DATA_TYPE_QUALIFIER[30]                                                                                          |         |

| 5       | BLK_OPER_  | d3: BCLK_RATE '1': 2048KHz '0': 1544KHz                                                                                 | 00H     |

|         | MODE       | d2: AUDIO_DAT '1': exists '0': does not exist                                                                           |         |

|         |            | d1: AUDIO_RATE '1': 16KS/s '0': 8KS/s                                                                                   |         |

|         |            | d0: AUDIO_STEREO '1': stereo '0': mono                                                                                  |         |

|         |            | d7: BLK_IO_EN '1': En bulk output pins. '0': Disable.                                                                   |         |

|         | 10 550     | d6-d4: reserved                                                                                                         | 0.077   |

| 6       | IO_REG     | d0: IO_1 Read/Write level of ZR36505 pin IO-1                                                                           | 00H     |

|         |            | d1: IO_2 Read/Write level of ZR36505 pin IO-2                                                                           |         |

|         |            | d7-d2: reserved                                                                                                         | 0011    |

| 7       | SOFT_RESET | d0: SOFT_RESET '1': Perform RESET                                                                                       | 00H     |

|         |            | This regulation of the writing $0.01$                                                                                   |         |

|         |            | This reg is always read 0x00 (even after writing 0x01).<br>Writing 0x01 to this register will result in a general reset |         |

|         |            | operation to the ZR36505, leaving all registers in their                                                                |         |

|         |            | default values.                                                                                                         |         |

|         | 1          | uciaun varues.                                                                                                          |         |

#### Table 4 - ZR36505 Registers List:

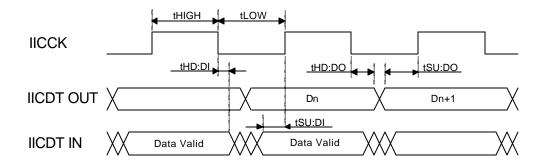

The serial bus consists of a clock signal and a data signal, which relate to the ZR36505 as a bus slave (where the ZR36504 is used as the bus master).

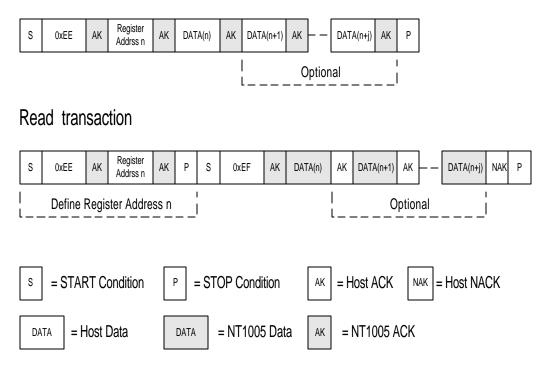

The ZR36505 device address is 0xEE for a Write operation, and 0xEF for a Read operation.

The diagram in the following page specifies general Read and Write transactions. In both transactions the register address is auto-incremented, which requires from the host computer to define the address of the first register only. The data bytes are then sent or received one after the other from the first register to the last one (any number of registers is possible). A Read transaction requires a Write sequence of 0 data bytes, in order to define the first address register to be read.

## Write transaction

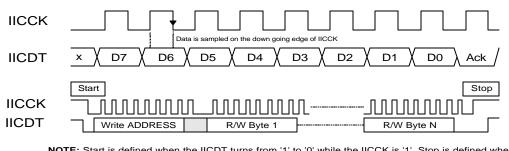

It is recommended to set the ZR36504(master) chip to its IIC LRNACK mode of operation to communicate with the ZR36505.

The following waveforms and timing diagrams specify the IIC serial interface bus in the signal level:

USBvision II Data Decoder

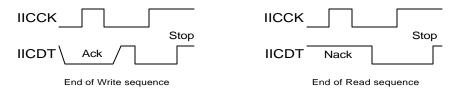

**NOTE:** Start is defined when the IICDT turns from '1' to '0' while the IICCK is '1'. Stop is defined when the IICDT turns from '0' to '1' while the IICCK is '1'. The Address byte is written like any other byte.

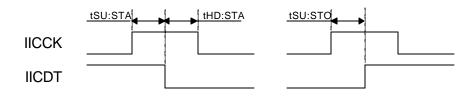

Start/Stop Timings

November-99

| Symbol             | Parameter                       | Min  | Max  | Unit |

|--------------------|---------------------------------|------|------|------|

| tsu:sta            | START condition setup time      | 5300 | -    | ns   |

| thd:sta            | START condition hold time       | 5300 | -    | ns   |

| tsu:sto            | STOP condition setup time       | 5300 | -    | ns   |

| thigh              | Clock high time                 | 5300 | -    | ns   |

| tLOW               | Clock low time                  | 5300 | -    | ns   |

| tsu:do             | Data output setup time          | 2500 | 2670 | ns   |

| t <sub>HD:DO</sub> | Data output hold time           | 2500 | 2670 | ns   |

| tsu:DI             | Data input setup time           | 20   | -    | ns   |

| t <sub>HD:DI</sub> | Data input hold time            | 0    | -    | ns   |

| Fiicck             | Frequency of IICCK clock signal | 0    | 100  | KHz  |

#### Table 5 - SERIAL CONTROL TIMINGS

## 2. VBI DATA QUALIFIER

## 2.1 VBI Input Interface

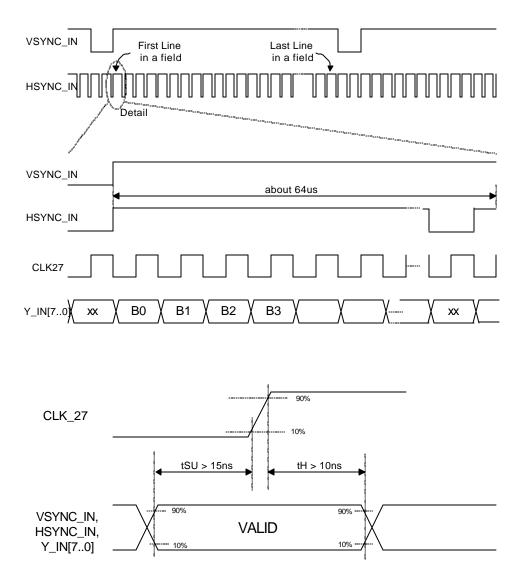

The ZR36505 is designed to connect to the 8-bit VBI output bus of the Video Decoder (Philips SAA7113 in its CCIR-656 mode of operation). This bus is sampled by the rising edge of CLK27 (27MHz clock, which is also provided by the Video Decoder chip), and provides the processed data bytes in the Blank lines. The same bus contains the Y/U/V video data on the valid video lines, which go directly to the NT1004.

The VBI input interface consists of the following signals:

$Y\_IN[7..0]$  ( Inputs ) This is the 8-bit VBI bus (contains also the Y/U/V samples in non-blank lines).

VSYNC\_IN (Input) This is the negative Vertical Synchronization pulse, which indicates the start of a new video field (Interlace mode).

$HSYNC\_IN\ (Input)$  This is the negative Horizontal Synchronization pulse, which indicates the start of a new video line.

CLK27 (Input)

This signal is the video pixel clock. It is used by the ZR36505 to sample all the other inputs in the digital video interface. It is also used by all state machines and logic to capture the VBI data into the 1Kbyte on-chip memory.

The timing of the VBI input bus, as expected by the ZR36505 is specified in the following timing diagram:

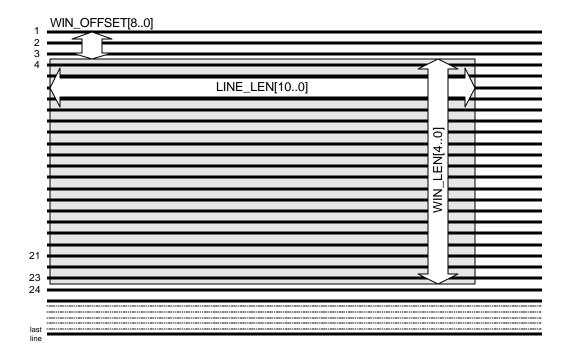

## 2.2 VBI Lines Qualifier

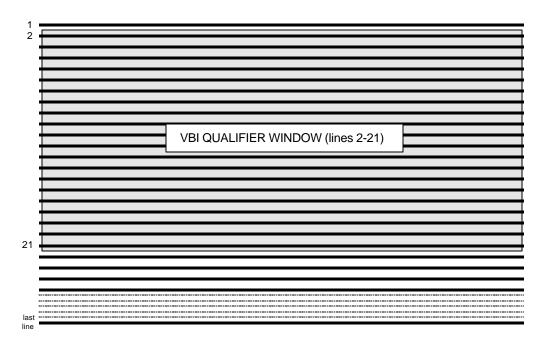

The VBI lines are defined in the range 2-21 of the 1st and 2nd fields, but in most TV stations not all the VBI lines are used for digital data.

The ZR36505 provides a way of restricting the search range, and filtering out the undesired data. This allows the ZR36505 to produce smaller buffers of data to be delivered via the USB Bulk channel, which do not interfere with the isochroneous video and audio channels. To do this, the ZR36505 uses the following qualifiers:

#### Line Window Qualifier (Regs. 0-3):

| LINE_LEN_L (Reg. 0) |                |             |    |    |    |    |           |  |  |  |

|---------------------|----------------|-------------|----|----|----|----|-----------|--|--|--|

| D7                  | D6             | D5          | D4 | D3 | D2 | D1 | <b>D0</b> |  |  |  |

| LINE_LEN[70]        |                |             |    |    |    |    |           |  |  |  |

| LINE_LEN_H (Reg. 1) |                |             |    |    |    |    |           |  |  |  |

| LINE_LI             | EN_H (Re       | g. 1)       |    |    |    |    |           |  |  |  |

| LINE_LI<br>D7       | EN_H (Re<br>D6 | g. 1)<br>D5 | D4 | D3 | D2 | D1 | D0        |  |  |  |

#### LINE\_WIN\_L (Reg. 2)

|                     |    | \ <b>0</b> | ,  |    |         |         |            |     |  |  |

|---------------------|----|------------|----|----|---------|---------|------------|-----|--|--|

| D7                  | D  | 6          | D5 | D4 | D3      | D2      | D1 1       | D0  |  |  |

| WIN_OFFSET[70]      |    |            |    |    |         |         |            |     |  |  |

| LINE_WIN_H (Reg. 3) |    |            |    |    |         |         |            |     |  |  |

| <b>D7</b>           | D6 | D5         | D4 | D3 | D2      | D1      | D0         |     |  |  |

| WIN_LEN[40]         |    |            |    |    | resrved | resrved | WIN_OFFSET | [8] |  |  |

The dark window represents the Line Window Qualifier. LINE\_LEN[10..0] is counted from the up-going edge of the HSYNC\_IN pulse and relates to CLK27 cycles, and WIN\_OFFSET[8..0] is counted from the up-going edge of the VSYNC\_IN pulse and relates to HSYNC\_IN pulses. Note that bit d6 of VBI\_REG (reg.4) should be enabled:

#### VBI\_REG (Reg. 4)

November-99

| D7 | D6               | D5 | <b>D4</b> | D3 | D2 | D1 | <b>D0</b> |

|----|------------------|----|-----------|----|----|----|-----------|

|    | EN_WIN_QUALIFIER |    |           |    |    |    |           |

#### VBI Window Qualifier:

To enable VBI Window Qualifier, bit d4 of VBI\_REG (reg.4) should be set to '1'. This will restrict data capture to those lines that are reported "VBI lines" by the video decoder. Normally, the VBI lines are expected to be lines 2-21.

| VBI_R | EG | (Reg. | 4) |

|-------|----|-------|----|

|-------|----|-------|----|

| D7 | D6 | D5 | D4               | D3 | D2 | <b>D1</b> | <b>D0</b> |

|----|----|----|------------------|----|----|-----------|-----------|

|    |    |    | EN_VBI_QUALIFIER |    |    |           |           |

Note that if both bits d4 and d6 of VBI\_REG (reg.4) are enabled, the data capture window will consist of all lines that are common to the VBI wondow and the given Line Window.

## VBI Type Qualifier:

To enable VBI Type Qualifier, bit d7 of VBI\_REG (reg.4) should be set to '1', and the desired VBI Type code should be defined in the DATA\_TYPE\_QUALIFIER[3..0] field (bits d3-d0 of VBI\_REG).

#### VBI\_REG (Reg. 4)

| D7                | D6-D4 | D3 | D2        | D1        | D0   |

|-------------------|-------|----|-----------|-----------|------|

| EN_TYPE_QUALIFIER |       | DA | TA_TYPE_0 | QUALIFIER | [30] |

Refer to Table 6 for available VBI Data Type codes for this qualifier. Note that the same code should be defined to the video decoder for specific lines in order to get any data that will match this qualifier.

#### Raw Samples:

To enable Raw Samples, bit d5 of VBI\_REG (reg.4) should be set to '1':

| VBI   | REG | (Reg. 4) | ) |

|-------|-----|----------|---|

| · • • |     |          | , |

| D7 | D6 | D5             | D4 | D3 | D2 | D1 | <b>D0</b> |

|----|----|----------------|----|----|----|----|-----------|

|    |    | EN_RAW_SAMPLES |    |    |    |    |           |

When Raw Samples are enabled, up to 720 raw samples of a VBI line (or any other video line) can be provided for S/W processing.

If the EN\_RAW\_SAMPLES bit is not set, raw samples are filtered out by default.

## 2.3 VBI and IRD (Remote Control) Data Format

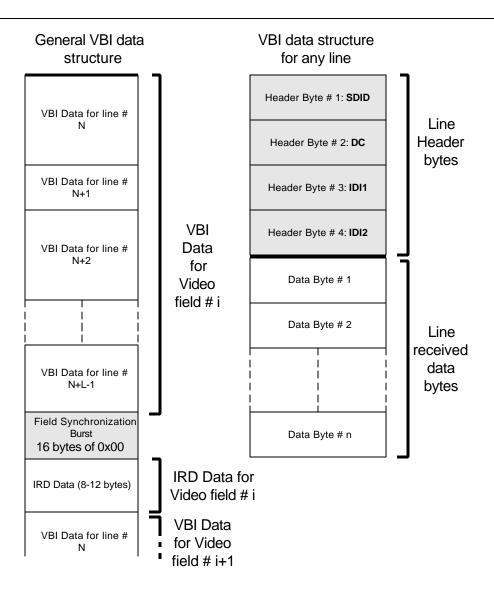

During the Vertical Blank Time Interval, The VBI Data Qualifier stores the incoming VBI data into the internal 1KByte SRAM. Soon after that, all binary samples from the IRD input (IO\_1) are added (about 8-12 bytes per video field). It is assumed that the total VBI data and IRD data in a single video field never exceeds the 1KB boundary, and that all accumulated data can be transfered via the Bulk port until the beginning of next Blank Interval.

The data that is transferred to the host computer via the Bulk interface contains an additional Field Synchronization Burst (which is produced after the VBI data and before the IRD data), and is specified in the following diagrams:

The following tables specifies the Line Header bytes:

SDID

| SDID |     |     |     |     |     |     |            |

|------|-----|-----|-----|-----|-----|-----|------------|

| D7   | D6  | D5  | D4  | D3  | D2  | D1  | <b>D</b> 0 |

| '1'  | '0' | '0' | '0' | '0' | '1' | '0' | '1'        |

DC

| D7  | D6  | D5  | D4  | D3  | D2  | D1  | <b>D0</b> |

|-----|-----|-----|-----|-----|-----|-----|-----------|

| '1' | '0' | DC5 | DC4 | DC3 | DC2 | DC1 | DC0       |

DC[5:0] is the number of data bytes that were actually received in this line. Note that this number may be different than the expected number of data bytes, due to noise or corruption in the received analog signal.

DC[5:0]='000000' means that no data bytes follow the Line Header.

IDI1

| D7 | D6  | D5 | D4 | D3 | D2 | D1 | <b>D</b> 0 |

|----|-----|----|----|----|----|----|------------|

| OP | FID | L8 | L7 | L6 | L5 | L4 | L3         |

L[8:3]: MSbits of Line Number (look for LSbits 2:0 in IDI2 byte).

FID : Field Identifier. '0' means FIRST field, '1' means SECOND field.

OP is Odd Parity bit. Examp.: D6:D0='0000101' ==> OP='1', IDI1=0x85.

IDI2

| D7 | D6 | D5 | D4 | D3  | D2  | D1  | <b>D</b> 0 |

|----|----|----|----|-----|-----|-----|------------|

| OP | L2 | L1 | LO | DT3 | DT2 | DT1 | DT0        |

OP is Odd Parity bit. Examp.: D6:D0='1110000' ==> OP='0', IDI1=0x70.

L[2:0]: LSbits of Line Number (look for MSbits 8:3 in IDI1 byte).

DT[3:0] defines the VBI Data Type for the given line. The host computer should define the Data Type per every VBI line (lines between 2-21). The video decoder needs this information in order to look for the given data type per line (there is no auto detect). Regardless of decoding success, the same data type code that was programmed by the host controller will be returned in the DT[3:0] nibble.

The following table specifies the Data Type codes (DT[3:0]):

| DT[3:0] | VBI Data Type                      | Standard        | Expected<br>number of<br>Data bytes |

|---------|------------------------------------|-----------------|-------------------------------------|

| 0000    | Teletext EuroWST, CCST             | WST625          | 42                                  |

| 0001    | European Closed Caption            | CC625           | 2                                   |

| 0010    | Video Programming Service          | VPS             | 26                                  |

| 0011    | Wide screen signalling bits        | WSS             | 14                                  |

| 0100    | US Teletext (WST)                  | WST525          | 34                                  |

| 0101    | US Closed Caption (line 21)        | CC525           | 2                                   |

| 0110    | Video Component signal             | S/W mode        | 718                                 |

| 0111*   | Oversampled CVBS data (do not use) | ** intercast ** |                                     |

| 1000    | Teletext                           | General Text    | 42                                  |

| 1001    | VITC/EBU time codes (Europe)       | VITC625         | 11                                  |

| 1010    | VITC/EBU time codes (USA)          | VITC625         | 11                                  |

| 1011*   | reserved (do not use)              |                 |                                     |

| 1100    | US NABTS                           | NABTS           | 34                                  |

| 1101    | MOJI (Japanese)                    | Japtext         | 35                                  |

| 1110    | Japanese format switch (L20/22)    | JFS             | 26                                  |

| 1111*   | Active Video Region (do not use)   |                 | 718                                 |

## Table 6 - VBI DATA TYPE CODES

The IRD (Remote Control) data Header byte contains two fields as specified bellow. It is followed by 7 to 11 bytes (depends one broadcast system PAL/NTSC, and sampling phase):

#### **IR\_HEADER**

| D7  | D6  | D5  | D4  | D3 | D2     | D1    | <b>D0</b> |

|-----|-----|-----|-----|----|--------|-------|-----------|

| '0' | '1' | '1' | '1' |    | IRD_LI | ENGTH |           |

IRD\_LENGTH contains the number of bytes for IRD data samples that follow the header.

## 3. Bulk Interface

The Bulk Interface in the ZR36505 is capable of transferring serial data from the 1KB buffer to the ZR36504 at a bit rate of up to 2Mbit/sec.

The Bulk channel takes advantage of the existing interface for the audio codec. In order to work simultaneously with the audio channel, the ZR36505 stops the data transfer from time to time - as specified in the Bulk waveform diagram.

The ZR36505 pins for the Bulk interface are BCLK, DAT\_OUT, BLK\_EN, BLK\_FULL, and FS\_L. The signal FS\_L is monitored by the ZR36505 in order to coexist with the audio channel (if exists).

The following parameters in the BLK\_OPER\_MODE register (reg. 5) must be properly defined to match the ZR36504 setup:

| BLK | OPER | REG | (Reg. 5 | ) |

|-----|------|-----|---------|---|

|     |      |     | (1105.0 | / |

| D7        | D6-D4 D3 |           | D2        | D1         | D0           |

|-----------|----------|-----------|-----------|------------|--------------|

| BLK_IO_EN | resrved  | BCLK_RATE | AUDIO_DAT | AUDIO_RATE | AUDIO_STEREO |

**BLK\_IO\_EN** - This bit enables the ZR36505 Bulk control output signals. When this bit is '0', the DAT\_OUT and BLK\_EN pins are constant Hi-Z.

**BCLK\_RATE** - This bit defines the BCLK frequency, and must match the appropriate parameter that is programmed in the AUDO\_CONT register of the ZR36504(Reg.50, d7-d6). BCLK\_RATE='1' defines 2048KHz (= '11' in NT1004), and BCLK\_RATE='0' defines 1544KHz (= '10' in NT1004).

AUDIO\_DAT - This bit defines whether or not the audio channel is active, and must match the appropriate parameter that is programmed in the AUDO\_CONT register of the ZR36504(Reg.50, d0). AUDIO\_DAT='1' defines audio active (= '1' in NT1004), and AUDIO\_DAT='0' defines that there is no audio data sharing the bus (= '0' in NT1004).

AUDIO\_RATE - This bit defines the audio sampling rate, and must match the appropriate parameter that is programmed in the AUDO\_CONT register of the ZR36504(Reg.50, d5). AUDIO\_RATE='1' defines 16Ks/sec (= '1' in NT1004), and AUDIO\_RATE='0' defines 8Ks/sec (= '0' in NT1004).

AUDIO\_STEREO - This bit defines the audio stereo/mono mode, and must match the appropriate parameter that is programmed in the AUDO\_CONT register of the

November-99

ZR36504(Reg.50, d4). AUDIO\_STEREO='1' defines Stereo mode (= '1' in NT1004), and AUDIO\_STEREO ='0' defines Mono mode (= '0' in NT1004).

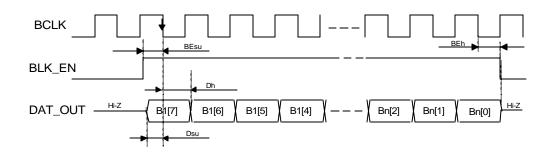

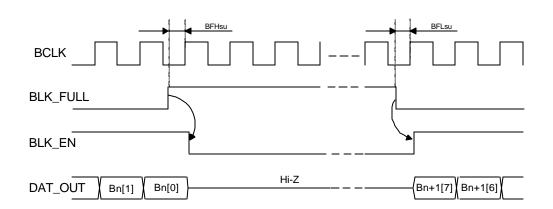

The following waveform diagrams specify the procedure and timings for the ZR36505 Bulk interface. Note that the output data is supposed to be sampled on the falling edge of the BCLK clock signal. The BLK\_EN output is set to '1' to indicate the beginning of a byte sequence; it always turns to '1' before the most significant bit of the first byte, and returns to '0' after the least significant bit of the last byte in sequence. When the BLK\_FULL input signal turns '1', the ZR36505 waits (by switching BLK\_EN to '0') until the BLK\_FULL indication returns to '0'.

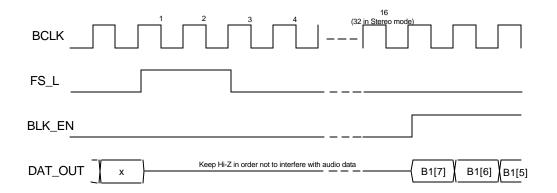

If the audio channel is enabled (bit d2 of Reg.5 is '1'), the ZR36505 waits at least 16 clock cycles after the FS\_L pulse before beginning to send its own data (if bit d0 of Reg.5 is '1', it waits for 32 clock cycles). During this time it keeps the DAT\_OUT signal in the Hi-Z state, in order not to interfere with the audio data.

#### Table 7 - BULK INTERFACE TIMINGS

| Parameter                                  | Symbol    | Min  | Max  | Unit |

|--------------------------------------------|-----------|------|------|------|

| Setup Time from BLK_EN High to BCLK Low    | BEsu      | 100  | -    | ns   |

| Hold Time from BCLK Low to BLK_EN Low      | BEh       | 100  | -    | ns   |

| Setup Time from DAT_IN valid to BCLK Low   | Dsu       | 100  | -    | ns   |

| Hold Time from BCLK Low to DAT_IN valid    | Dh        | 100  | -    | ns   |

| Setup Time from BLK_FULL High to BCLK High | BFHsu     | 80   | -    | ns   |

| Hold Time from BLK_FULL Low to BCLK High   | BFLsu     | 0    | -    | ns   |

| BCLK frequency                             | Freq.BCLK | 1544 | 2048 | KHz  |

## 4. Programmable I/O Pins

The ZR36505 has two programmable I/O pins for general purpose usage. These are IO-1 and IO-2 pins, which are Open-Drain.

Each of these pins - if used - must be connected to an external pull-up resistor to 3.3v (if not used, it can be tied to GND). The external pull-up resistor should be in the range 1-10K $\Omega$ .

To use these pins as inputs, the host computer should write '1' to the appropriate bit in the IO\_REG register (reg. 6); these are IO\_1 and IO\_2 bits respectively. In this condition, the voltage level presented on the IO-1 or IO-2 pin can be read by the host computer via the appropriate bit ('0' represents <0.8v, '1' represents >2.0v).

To use these pins as outputs, the host computer should write the output value to the appropriate bit in the IO\_REG register; In this condition, and assuming that no external device forces the voltage level presented on the IO-1 or IO-2 pin, the written value will be reflected out ('0' will generate 0v, '1' will generate 3.3-5.0v).

#### IO\_REG (Reg. 6)

| D7      | D6      | D5      | D4      | D3      | D2      | D1   | <b>D</b> 0 |

|---------|---------|---------|---------|---------|---------|------|------------|

| resrved | resrved | resrved | resrved | resrved | resrved | IO_2 | IO_1       |

Upon a Soft Reset operation, the IO-1 and IO-2 pins are cleared to '0'.

## 5. <u>Soft Reset operation</u>

It is strongly recommended that the S/W application will perform a Soft Reset to the ZR36505 prior to any other operation. All registers will contain their default values after this operation (refer to table 4 for default values).

To perform a Soft Reset, the value 0x01 must be written in the SOFT\_RESET register (reg. 7). There is no need to write 0x00 after writing 0x01, because this register is automatically cleared.

## SOFT\_RESET (Reg. 7)

| D7-D1   | D0         |

|---------|------------|

| resrved | SOFT_RESET |

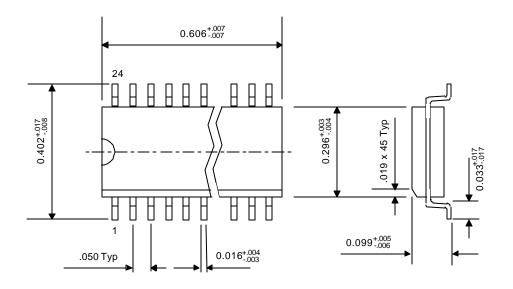

## 6. Mechanical Specification

Dimensions in inches.

24-pin 300-Mil SOIC GULL WING

November-99

0

# For more information, contact Zoran's Santa Clara office or the office nearest you:

#### USA

Zoran Corporation 3112 Scott Boulevard Santa Clara, CA 95054-3317 Tel: 408-919-4111 Fax: 408-919-4122

#### Israel

Zoran Microelectronics Ltd. Advanced Technology Ctr. P.O. Box 2495 Haifa, 31024 Israel Tel : +972-4-8545-777 Fax: +972-4-8551-551

#### China

Zoran China Office Suite 2507 Electronics Science & Tech Building 2070 Central Shennan Rd. Shenzhen, Guangdong, 518031 P.R. China Tel : +86-755-378-0319 Fax: +86-755-378-0852

#### Japan

Zoran Japan Office 2-2-8 Roppongi, Minato-ku Tokyo 106-0032, Japan Tel : +81-03-5574-7081 Fax: +81-03-5574-7156

#### Taiwan

Zoran Taiwan Office 4F-1, No. 5, Alley 22 Lane 513, Reikuang Rd. Taipei, Taiwan R.O.C. Tel : +886-2-2659-9797 Fax: +886-2-2659-9595

#### Canada

Zoran Toronto Lab 2175 Queen St. East, Suite 302 Toronto, Ontario M4E 1E5 Canada Tel : (416) 690-3356 Fax: (416) 690-336