**Vishay Semiconductors**

# **Dual - MOSMIC®- two AGC Amplifiers for TV-Tuner Prestage with 5 V Supply Voltage**

MOSMIC - MOS Monolithic Integrated Circuit

Electrostatic sensitive device. Observe precautions for handling.

#### **Applications**

Low noise gain controlled input stages in UHF-and VHF- tuner with 5 V supply voltage.

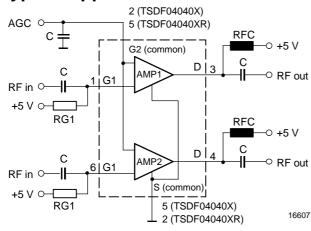

#### **Typical Application**

#### **Features**

- Two AGC amplifiers in a single package

- Easy Gate 1 switch-off with PNP switching transistors inside PLL

- Integrated gate protection diodes

- Low noise figure

- High gain, very high forward transadmittance (40 mS typ.)

- Biasing network on chip

- Improved cross modulation at gain reduction

- High AGC-range with less steep slope

- SMD package, reverse pinning possible

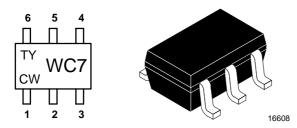

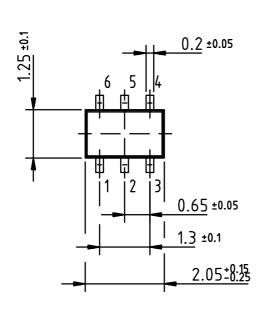

TSDF04040X Marking: WC7 Plastic case (SOT 363)

1 = Gate 1 (amplifier 1), 2 = Gate 2,

3 = Drain (amplifier 1), 4 = Drain (amplifier 2),

5 = Source, 6 = Gate1 (amplifier 2)

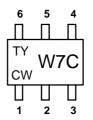

TSDF04040XR Marking: W7C Plastic case (SOT 363)

1 = Gate 1 (amplifier 1), 2 = Source,

3 = Drain (amplifier 1), 4 = Drain (amplifier 2),

5 = Gate 2, 6 = Gate 1 (amplifier 2)

T = Telefunken

Y = Year, is variable for digit from 0 to 9 (e.g. 0 = 2000, 1 = 2001)

CW = Calendar Week, is variable for number from 01 to 52

Number of Calendar Week is always indicating place of pin 1

## TSDF04040X/TSDF04040XR

# **Vishay Semiconductors**

# All of following data and characteristics are valid for operating either amplifier 1 (pin 1, 3, 2, 5) or amplifier 2 (pin 6, 4, 2, 5)

### **Absolute Maximum Ratings**

$T_{amb} = 25^{\circ}C$ , unless otherwise specified

| Parameter                           | Test Conditions          | Symbol                               | Value       | Unit |

|-------------------------------------|--------------------------|--------------------------------------|-------------|------|

| Drain - source voltage              |                          | $V_{DS}$                             | 8           | V    |

| Drain current                       |                          | I <sub>D</sub>                       | 30          | mA   |

| Gate 1/Gate 2 - source peak current |                          | ±I <sub>G1/G2SM</sub>                | 10          | mA   |

| Gate 1/Gate 2 - source voltage      |                          | +V <sub>G1</sub> /±V <sub>G2SM</sub> | 6           | V    |

| Gate 1/Gate 2 - source voltage      |                          | -V <sub>G1SM</sub>                   | 1.5         | V    |

| Total power dissipation             | T <sub>amb</sub> ≤ 60 °C | P <sub>tot</sub>                     | 200         | mW   |

| Channel temperature                 |                          | T <sub>Ch</sub>                      | 150         | °C   |

| Storage temperature range           |                          | T <sub>stg</sub>                     | -55 to +150 | °C   |

#### **Maximum Thermal Resistance**

$T_{amb} = 25^{\circ}C$ , unless otherwise specified

| Parameter       | Test Conditions                                                            | Symbol | Value | Unit |

|-----------------|----------------------------------------------------------------------------|--------|-------|------|

| Channel ambient | annel ambient on glass fibre printed board (25 x 20 x 1.5) mm <sup>3</sup> |        | 450   | K/W  |

|                 | plated with 35µm Cu                                                        |        |       |      |

#### **Electrical DC Characteristics**

T<sub>amb</sub> = 25°C, unless otherwise specified

| Tamb = 0, amos outletimes opening |                                                                                      |                        |      |      |      |      |

|-----------------------------------|--------------------------------------------------------------------------------------|------------------------|------|------|------|------|

| Parameter                         | Test Conditions                                                                      | Symbol                 | Min. | Тур. | Max. | Unit |

| Drain - source breakdown voltage  | $I_D = 10 \mu A, V_{G1S} = V_{G2S} = 0$                                              | V <sub>(BR)DSS</sub>   | 12   |      |      | V    |

| Gate 1 - source breakdown voltage | $+I_{G1S} = 10 \text{ mA}, V_{G2S} = V_{DS} = 0$                                     | +V <sub>(BR)G1SS</sub> | 7    |      | 10   | V    |

| Gate 2 - source breakdown voltage | $\pm I_{G2S} = 10 \text{ mA}, V_{G2S} = V_{DS} = 0$                                  | ±V <sub>(BR)G2SS</sub> | 7    |      | 10   | V    |

| Gate 1 - source leakage current   | $+V_{G1S} = 5 \text{ V}, V_{G2S} = V_{DS} = 0$                                       | +I <sub>G1SS</sub>     |      |      | 20   | nA   |

| Gate 2 - source leakage current   | $\pm V_{G2S} = 5 \text{ V}, V_{G1S} = V_{DS} = 0$                                    | ±I <sub>G2SS</sub>     |      |      | 20   | nA   |

| Drain - source operating current  | $V_{DS} = V_{RG1} = 5 \text{ V}, V_{G2S} = 4 \text{ V}, R_{G1} = 56 \text{ k}\Omega$ | I <sub>DSO</sub>       | 10   | 15   | 20   | mA   |

| Gate 1 - source cut-off voltage   | $V_{DS} = 5 \text{ V}, V_{G2S} = 4, I_{D} = 20 \mu\text{A}$                          | V <sub>G1S(OFF)</sub>  | 0.5  |      | 1.3  | V    |

| Gate 2 - source cut-off voltage   | $V_{DS} = V_{RG1} = 5 \text{ V}, R_{G1} = 56 \text{ k}\Omega, I_D = 20 \mu\text{A}$  | V <sub>G2S(OFF)</sub>  | 8.0  | 1.0  | 1.4  | V    |

# **Vishay Semiconductors**

#### **Electrical AC Characteristics**

$V_{DS} = V_{RG1} = 5 \text{ V}, V_{G2S} = 4 \text{ V}, R_{G1} = 56 \text{ k}\Omega, I_D = I_{DSO}, f = 1 \text{ MHz}, T_{amb} = 25^{\circ}\text{C}, unless otherwise specified}$

| Parameter                | Test Conditions                                                                          | Symbol             | Min. | Тур. | Max. | Unit |

|--------------------------|------------------------------------------------------------------------------------------|--------------------|------|------|------|------|

| Forward transadmittance  |                                                                                          | y <sub>21s</sub>   | 35   | 40   | 50   | mS   |

| Gate 1 input capacitance |                                                                                          | C <sub>issg1</sub> |      | 2.4  | 2.8  | pF   |

| Feedback capacitance     |                                                                                          | C <sub>rss</sub>   |      | 30   | 40   | fF   |

| Output capacitance       |                                                                                          | Coss               |      | 1.5  |      | pF   |

| Power gain               | $G_S = 2 \text{ mS}, G_L = 0.5 \text{ mS}, f = 200 \text{ MHz}$                          | G <sub>ps</sub>    |      | 28   |      | dB   |

| Power gain               | $G_S = 3.3 \text{ mS}, G_L = 1 \text{ mS}, f = 800 \text{ MHz}$                          | G <sub>ps</sub>    | 18   | 24   |      | dB   |

| AGC range                | $V_{DS} = 5 \text{ V}, V_{G2S} = 1 \text{ to 4 V}, f = 800 \text{ MHz}$                  | $\Delta G_{ps}$    |      | 45   |      | dB   |

| Noise figure             | $G_S = 2 \text{ mS}, G_L = 0.5 \text{ mS}, f = 200 \text{ MHz}$                          | F                  |      | 1    |      | dB   |

| Noise figure             | $G_S = 3.3 \text{ mS}, G_L = 1 \text{ mS}, f = 800 \text{ MHz}$                          | F                  |      | 1.3  |      | dB   |

| Cross modulation         | Input level for k = 1 % @ 0 dB AGC<br>f <sub>w</sub> = 50 MHz, f <sub>unw</sub> = 60 MHz | X <sub>mod</sub>   | 90   |      |      | dBμV |

| Cross modulation         | Input level for k = 1 % @ 40 dB AGC $f_w = 50$ MHz, $f_{unw} = 60$ MHz                   | X <sub>mod</sub>   | 100  | 105  |      | dBμV |

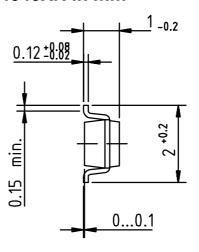

#### Dimensions of TSDF04040X/TSDF04040XR in mm

$\bigcirc \bigcirc$

according to DIN

14280 specifications

#### TSDF04040X/TSDF04040XR

#### **Vishay Semiconductors**

#### **Ozone Depleting Substances Policy Statement**

It is the policy of Vishay Semiconductor GmbH to

- 1. Meet all present and future national and international statutory requirements.

- 2. Regularly and continuously improve the performance of our products, processes, distribution and operating systems with respect to their impact on the health and safety of our employees and the public, as well as their impact on the environment.

It is particular concern to control or eliminate releases of those substances into the atmosphere which are known as ozone depleting substances (ODSs).

The Montreal Protocol (1987) and its London Amendments (1990) intend to severely restrict the use of ODSs and forbid their use within the next ten years. Various national and international initiatives are pressing for an earlier ban on these substances.

**Vishay Semiconductor GmbH** has been able to use its policy of continuous improvements to eliminate the use of ODSs listed in the following documents.

- 1. Annex A, B and list of transitional substances of the Montreal Protocol and the London Amendments respectively

- Class I and II ozone depleting substances in the Clean Air Act Amendments of 1990 by the Environmental Protection Agency (EPA) in the USA

- 3. Council Decision 88/540/EEC and 91/690/EEC Annex A, B and C (transitional substances) respectively.

Vishay Semiconductor GmbH can certify that our semiconductors are not manufactured with ozone depleting substances and do not contain such substances.

We reserve the right to make changes to improve technical design and may do so without further notice. Parameters can vary in different applications. All operating parameters must be validated for each customer applications.

Parameters can vary in different applications. All operating parameters must be validated for each customer application by the customer. Should the buyer use Vishay Semiconductors products for any unintended or unauthorized application, the buyer shall indemnify Vishay Semiconductors against all claims, costs, damages, and expenses, arising out of, directly or indirectly, any claim of personal damage, injury or death associated with such unintended or unauthorized use.

Vishay Semiconductor GmbH, P.O.B. 3535, D-74025 Heilbronn, Germany Telephone: 49 (0)7131 67 2831, Fax number: 49 (0)7131 67 2423