# UMC

T-75-07-15

UM93510 A/B/C

Speech Recording and Reproduction IC(with SRAM)

#### PRELIMINARY

#### **Features**

- Uses ADM algorithm to process voice data

- Uses three sampling rates (16K, 22K, 32K) selected by single pin (SRS)

- Useful in applications such as: answering machines, announcing phones and toys

- Metal mask option for answering machine or announce phone selection

- Data can be stored on SRAM or ROM:

- Two 256K SRAMs for 32K sample rate

- One 256K SRAM for 22K or 16K sample rate

- One 256K SRAM and one 256K ROM for toy applications

- Activating the CE pin stops recording

- On-chip amplifier for sound recording

- On-chip band-pass filter for reproducing sound

- On-chip oscillation circuit for 3.579545 MHz ceramic oscillator

- 4.5V power supply using three 1.5V batteries

- Available in 48 pin flat package or in chip form

### **General Description**

The UM93510 A/B/C is a speech recording and reproduction chip. It stores voice data on external 256K SRAMs. The primary use for the UM93510 A/B/C is in answering

machines or announcing phones. It can also be used for toys. The 256K ROM should be partitioned into four parts for toy applications.

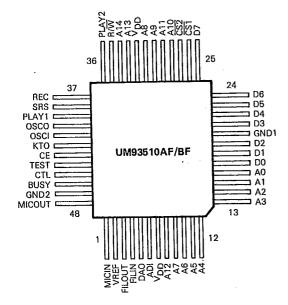

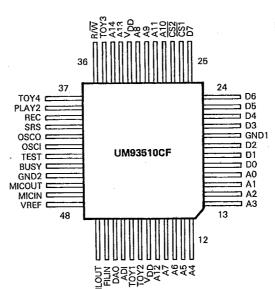

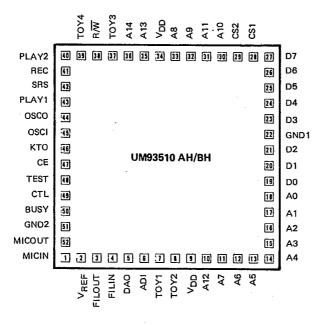

## Pin Configurations

**Pad Configuration**

T-75-07-15

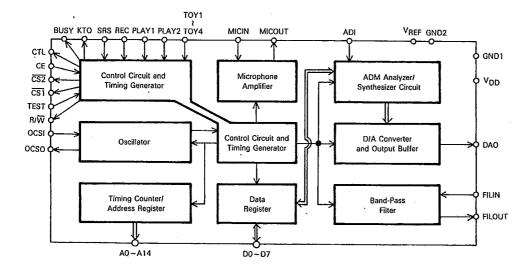

### **Block Diagram**

T-75-07-15

### Pin and Pad Description

| Pi                              | n                               | Symbol                    | Pad Description                  |                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|---------------------------------|---------------------------------|---------------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| A/B                             | С                               |                           | AH/BH                            | Description                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| 1                               | 47                              | MICIN<br>(I/P)            | 1                                | The inverting input terminal of the built-in microphone operational amplifier.                                                                                                                                                                                                                                                                                                                               |  |  |

| 2                               | 48                              | V <sub>REF</sub><br>(O/P) | 2                                | The bias voltage terminal of the built-in analog circuit. This pin is pulled to GND at standby state.                                                                                                                                                                                                                                                                                                        |  |  |

| 3                               | 1                               | FILOUT<br>(O/P)           | 3                                | The output pin of the built-in bandpass filter. The DC bias voltage of this pin is equal to 1/2 $\rm V_{DD}$ in playing mode and is pulled to GND in standby state.                                                                                                                                                                                                                                          |  |  |

| 4                               | 2                               | FILIN<br>(I/P)            | 4                                | The input terminal of the built-in bandpass filter for reproducing.                                                                                                                                                                                                                                                                                                                                          |  |  |

| 5                               | 3                               | DAO<br>(O/P)              | 5                                | The voice output terminal of the voice synthesizing circuit. Output signals have been biased to $1/2\ V_{DD}$ . This pin is pulled to GND at standby state.                                                                                                                                                                                                                                                  |  |  |

| 6                               | 4                               | ADI<br>(I/P)              | 6                                | The voice input terminal of the voice analysis circuit. Input signal must have been biased to 1/2 $\rm V_{DD}$ .                                                                                                                                                                                                                                                                                             |  |  |

| 7<br>32                         | 7<br>32                         | V <sub>DD</sub><br>(I/P)  | 9<br>34                          | Positive power supply.                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| 8<br>16<br>28<br>31<br>33<br>34 | 8<br>16<br>28<br>23<br>31<br>33 | A0-A14<br>(O/P)           | 10<br>18<br>30<br>33<br>35<br>36 | The address bus output pins.                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| 17<br>18<br>19<br>21<br>25      | 17<br>18<br>19<br>21<br>1       | D0-D7<br>(I/O)            | 19<br>20<br>21<br>23<br>1<br>27  | The data bus input/output pins.                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| 20                              | 20                              | GND1<br>(I/P)             | 22                               | Digital circuit ground pin.                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| 26<br>27                        | 26<br>27                        | CS1, CS2<br>(O/P)         | 28<br>29                         | The chip selector output pins for 256K SRAM1 and SRAM2 (or ROM). If toy play is used, it is always to active $\overline{\text{CS2}}$ .                                                                                                                                                                                                                                                                       |  |  |

| 35                              | 36                              | R/W<br>(O/P)              | 38                               | The read, write control output pin for SRAM.                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| 36                              | 38                              | PLAY2<br>(I/P)            | 40                               | The PLAY2 input pin is triggered manually. It is pulled low internally.                                                                                                                                                                                                                                                                                                                                      |  |  |

| 37                              | 39                              | REC<br>(I/P)              | 41                               | Record input trigger pin. Whenever this pin is triggered, the chip stops automatically under two conditions: (1) The SRAM memory is full (2) the CE pin has been pulled low. In the second case, the time for BUSY from HIGH to LOW is 0-1 second. (counts from the moment when the CE pin is switched to LOW) The delay time is not known, but depends on the current address. It is pulled low internally. |  |  |

## Pin and Pad Description (Continued)

T-75-07-15

| Pi       | n        |                          | Pad      | <del></del>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | · · · · · · · · · · · · · · · · · · · |                  |                      |  |

|----------|----------|--------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|------------------|----------------------|--|

| A/B      | C        | Symbol                   | AH/BH    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                       |                  |                      |  |

| 38       | 40       | SRS<br>(I/P)             | 42       | Sample rate selector pin for ADM algorithm. There are three difference sample rates: 16 KHz, 22 KHz and 32 KHz. The relationship between SRS and sample rate is:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                       |                  | different<br>between |  |

|          |          |                          |          | SRS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Samp                                  | le Rate          |                      |  |

|          |          |                          |          | high                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 32                                    | KHz              |                      |  |

|          |          |                          |          | low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 22                                    | KHz              |                      |  |

|          |          |                          |          | open                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 16                                    | KHz              |                      |  |

| 39       | NA       | PLAY1<br>(1/P)           | 43       | The PLAY1 input pin is triggered by the ringing of the telephone. While high normally, it is pulled low when triggered. After the pin is triggered, the chip starts processing data after a delay of about 12 seconds for 22 KHz sample rate and 12,5 seconds for the 32 KHz sample rate and 16 KHz sample rates. If the ring time is less than 7.5 seconds, the trigger will not be successful and the chip will automatically enter the standby state. If the ring time is longer than 7.5 seconds but shorter than 12.5 seconds (or 12.0 seconds when the sample rate is 22 KHz), triggering will be successful and the chip will start to work. When this pin is pulled to GND, the current sourcing to GND is 20 $\mu$ A (max.) at $V_{\rm DD}$ = 4.5V. |                                       |                  |                      |  |

| 40<br>41 | 41<br>42 | OSCI, OSCO<br>(I/P, O/P) | 44<br>45 | 3.579545 MHz ceramic oscillator connecting pins,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                       |                  |                      |  |

| 42       | NA       | KTO<br>(O/P)             | 46       | Key tone output pin. When the REC, PLAY2 pins are triggered or after BUSY pin from high to low (only in UM93510A/B & Chip form), this pin will send out a key tone. Duration and frequency are:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                       |                  | or after<br>this pin |  |

|          |          |                          |          | Sample<br>rate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Tone<br>frequency                     | Tone<br>duration | 7                    |  |

|          |          |                          |          | 32 KHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 500 Hz                                | 112 ms           | -                    |  |

|          |          |                          |          | 22 KHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 688 Hz                                | 163 ms           | 1                    |  |

|          |          |                          |          | 16 KHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 500 Hz                                | 224 ms           |                      |  |

|          |          |                          |          | This pin is always pulled lo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ow, except during key                 | tone period.     |                      |  |

| 42       | NA       | CE<br>(I/P)              | 47       | The chip enable input control pin. If CE is enabled, i. e., it can normally operate as described in the specification. If CE is low, it remains in a standby state, no matter which pin is triggered. If the CE pin is pulled low while operating, it enters the standby state immediately. It is internally pulled high. When this pin is switched to GND, the current sourcing to GND through this pin is $20~\mu\text{A}$ (max.) at $V_{DD} = 4.5\text{V}$ .                                                                                                                                                                                                                                                                                              |                                       |                  |                      |  |

| 44       | 43       | TEST<br>(1/P)            | 48       | Test input pin for testing mode. It is internally pulled low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                       |                  |                      |  |

T-75-07-15

## Pin and Pad Description (Continued)

| Pin |    | Symbol          | Pad   | Description                                                                                                                                                                                                                                                 |  |  |  |

|-----|----|-----------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| A/B | С  | 2Aumoi          | AH/BH | 3H                                                                                                                                                                                                                                                          |  |  |  |

| 45  | NA | CTL<br>(O/P)    | 49    | Provides output control to the telephone set. It is high only in PLAY Operation.                                                                                                                                                                            |  |  |  |

| 46  | 44 | BUSY<br>(O/P)   | 50    | Output signal to indicate the chip is busy processing data, BUSY is high when the chip is active.                                                                                                                                                           |  |  |  |

| 47  | 45 | GND2<br>(1/P)   | 51    | Analog and some digital circuit ground pin.                                                                                                                                                                                                                 |  |  |  |

| 48  | 46 | MICOUT<br>(O/P) | 52    | The output terminal of the built-in microphone operational amplif Output signal has been biased to 1/2 V <sub>DD</sub> and can be directly connect to ADI terminal. This pin can not have DC path to GND in standate, or it will have DC power dissipation. |  |  |  |

| NA  | 5  | TOY1<br>(I/P)   | 7     | This pin is only available for TOY applications. (i. e. UM93510C). Who triggered, this pin will cause the first quarter of the data on the 256 ROM to be played. It is pulled low internally.                                                               |  |  |  |

| NA  | 6  | TOY2<br>(1/P)   | 8     | This pin is only available for TOY applications. (i. e. UM93510C). Wi triggered, this pin will cause the second quarter of the data on the 25 ROM to be played. It is pulled low internally.                                                                |  |  |  |

| NA  | 35 | TOY3<br>(I/P)   | 37    | This pin is only available for TOY applications. (i. e. UM93510C). W triggered, this pin will cause the third quarter of the data on the 25 ROM to be played. It is pulled low internally.                                                                  |  |  |  |

| NA  | 37 | TOY4<br>(I/P)   | 39    | This pin is only available for TOY applications. (i. e. UM93510C). Whe triggered, this pin will cause the last quarter of the data on the 256 ROM to be played. It is pulled low internally.                                                                |  |  |  |

- 2. The chip can not accept a new input trigger signal if any control pin has already been triggered. No new trigger signals can be accepted until the chip enters the standby state.

- 3. When the chip is used in an announce phone or an answering machine:

- a. If the sample rate is 32 KHz, two SRAMs are required to store the data. One SRAM can be used, but will only store eight seconds of data, then wait another eight seconds before stopping.

- b. If the sample rate is 16 KHz or 22 KHz, only one SRAM needs to be connected to CS1. It will not activate CS2.

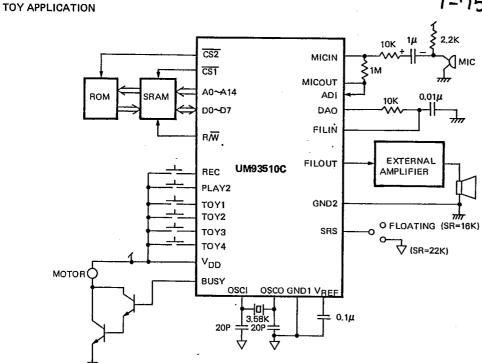

- 4. When the chip is used in toy applications, the 32 KHz sample rate is not used to synthesize speech. One SRAM chip can be connected to  $\overline{\text{CS1}}$  or one ROM chip to  $\overline{\text{CS2}}$ , or one SRAM chip to  $\overline{\text{CS1}}$  and one ROM chip to  $\overline{\text{CS2}}$ .

- 5. NA: Not available

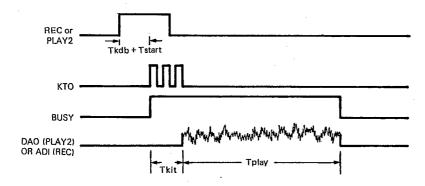

- The difference between the UM93510 A and B is the CTL and KTO output timings shown in Timing Waveform(3).

T-75-07-15 UM93510 A/B/C

### **Functional Description:**

The UM93510 A/B/C is a voice processing and reproducing chip which can be used in both answering machine and toy applications. The input voice signals are processed into digital signals using the ADM (Adaptive Delta Modulation) algorithm. The digital data will be reproduced into analog voice signals when proper trigger conditions occur.

#### (a) UM93510 A/B

This chip can go into play mode by connecting the PLAY 2 pin to logical 1 level for a period more than 23 ms debounce time or by connecting the PLAY 1 pin to a logical 0 level for more than 7.5 sec. For answering machine or announce phone applications PLAY 1 is normally connected to a ringer detect circuit.

Note: The UM93510A will go into standby mode after the stored data is played while the UM93510B will enable the recorder for about 36 sec. The differences between A and B versions is shown in Timing Waveform (3).

### (b) UM93510C

This chip can be triggered into play mode by either connecting PLAY 2 to logical 1 or connecting one of the TOY1, TOY2, TOY3, TOY4 to logical 1 level. The debounce time of the above pins is 23 ms.

The sample rate of 32K Hz, 22K Hz, 16K Hz can be selected by the SRS pin connecting to the HIGH, LOW, or

FLOATING condition respectively. When the 32K Hz sample rate is selected two 256K SRAM should be used.

#### Absolute Maximum Ratings \*

### **Recommended Operating Conditions**

#### \*Comments

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional Operation of this device at these or any other conditions above those indicated in the operational sections of this specification is not implied and exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **DC Electrical Characteristics** $(V_{DD} = 4.5V, V_{SS} = 0V, F_{OSC} = 3.579545 \text{ MHz}, T_{OP} = 25^{\circ}\text{C}, \text{ unless otherwise specified})$

| Parameter                                        | Symbol            | Min.     | Тур.  | Max. | Units           | Conditions                                   |

|--------------------------------------------------|-------------------|----------|-------|------|-----------------|----------------------------------------------|

| Operating voltage                                | V <sub>DD</sub>   | 4.0      |       | 5.5  | V               |                                              |

| Supply Operating current                         | l <sub>dd</sub>   |          | , , , | 4.0  | mA              | Oscillator running, all outputs unloaded     |

| Standby Current                                  | l <sub>sb</sub>   |          |       | 2.0  | μΑ              | Oscillator not running, all outputs unloaded |

| Digital output sink current (1)                  | I <sub>do11</sub> |          | 0.5   |      | mA              | V <sub>01</sub> = 0.8V                       |

| Digital output source current (1)                | I <sub>do12</sub> | <u> </u> | 0.5   |      | mA              | V <sub>oh</sub> = 2.4V                       |

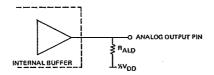

| Resistor Load to get full swing of Analog output | R <sub>ALD</sub>  | 15       | ,     |      | ΚΩ              | Test circuit (2)                             |

| District and the second                          | V <sub>dil</sub>  |          |       | 0.8  | v               |                                              |

| Digital input voltage rating                     | V <sub>dih</sub>  | 2.4      |       |      | 1 '             |                                              |

| District                                         | V <sub>dol</sub>  |          |       | 0.8  | V               | l <sub>do11</sub> = 0,5 mA                   |

| Digital output voltage rating .                  | V <sub>doh</sub>  | 2.4      |       |      | ]               | I <sub>do 12</sub> = 0,5 mA                  |

| Analog output voltage rating                     | V <sub>aol</sub>  | 0.25     |       | 0.75 | V <sub>DD</sub> | $R_L > 5 K\Omega$                            |

Note: 1. Pins BUSY, CTL, CS1, CS2, RW, A0 - A14, D0 - D7

2. Pins FILOUT, DAO, MICOUT

T-75-07-15

## **AC Electrical Characteristics**

$(V_{DD} = 4.5V, V_{SS} = 0V, F_{OSC} = 3,579545 \text{ MHz}, T_{OP} = 25^{\circ}\text{C}, \text{unless otherwise specified})$

| Parameter                                | Symbol  | Conditions                       | Min. | Тур.                 | Max. | Unit  |  |

|------------------------------------------|---------|----------------------------------|------|----------------------|------|-------|--|

| Key debounce time                        | Tkdb    |                                  |      | 23                   |      | mS    |  |

| Key-in-tone duration                     | Tkit    | sample rate<br>16K<br>22K<br>32K |      | 224<br>163<br>112    |      | mS    |  |

| Key-in-tone frequency                    | Fkit    | sample rate<br>16K<br>22K<br>32K |      | 500<br>688<br>500    |      | Hz    |  |

| Period of announcement output            | Tplay   | 256K or 512K<br>memory maximum   |      |                      | 16   | Sec   |  |

| Trigger period of incoming ringer signal | Tring   | sample rate<br>16K<br>22K<br>32K |      | 12.5<br>12.0<br>12.5 |      | Sec   |  |

| Recording period for answer machine      | Trec    |                                  |      | 36                   |      | Sec   |  |

| Time between ringer signals              | Trs     |                                  |      |                      | 4    | Sec · |  |

| Oscillator start up time                 | Tstrart |                                  |      | <u> </u>             | 50   | mS    |  |

### **Timing Waveform**

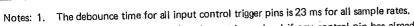

(1) Timing Waveform for TOY1, TOY2, TOY3, TOY4

Tkit: Key tone output period 224 ms or 163 ms Tplay: Play or announcement period, 64K memory

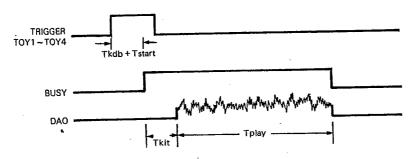

#### (2) Timing Waveform for Recording and Reproducing (for UM93510A/B/C)

T-75-07-15

Tkit: Key Tone output Period 224 ms or 163 ms or 112 ms

Tplay: Play or Recording Period, maximum memory space: 256K or 512K

Note: The UM93510C, KTO pin is not available.

### (3) Timing Diagram for Announcement-Recording (for UM93510A/B)

Tring: Trigger period of incoming ringer signal, 12 sec

Tkit: Key tone output period 224 ms or 163 ms or 112 ms

Tplay: Play or recording period, maximum memory space: 256K or 512K

Trec: Recording period for answering machine, 36 sec

NOTE: For announce phone, these states are replaced by standby state during this period.

i. e. the KTO signal always stays at low, and the CTL signal has the same waveform as the BUSY signal.

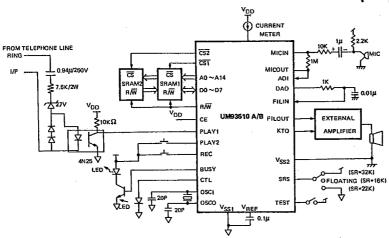

### **Application Circuits**

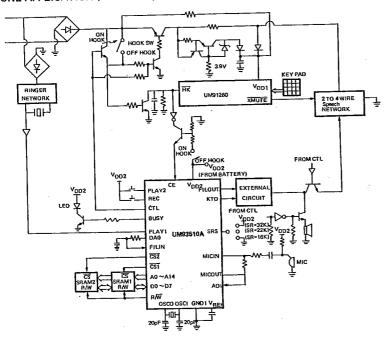

ANNOUNCE PHONE APPLICATION (UM93510A)

T-75-07-15

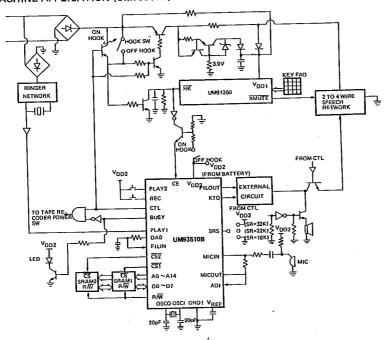

## ANSWERING MACHINE APPLICATION (UM93510B)

T-75-07-15

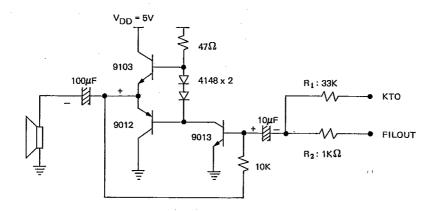

Notes: F1LOUT is  $\rm ^4V_{DD} \sim ^4V_{DD}$  analog signal. Its output maximum current, Imax, is about 0.2 mA.

### REFERENCE CIRCUIT FOR EXTERNAL AMPLIFIER

T-75-07-15

### Test Circuit (2)

## **Ordering Information**

| Part No.  | Application             | Package Information |  |

|-----------|-------------------------|---------------------|--|

| UM93510AF | Announcing phone        | 48-pin Flat pack    |  |

| UM93510BF | Answering machine       | 48-pin Flat pack    |  |

| UM93510CF | Toy Application         | 48-pin Flat pack    |  |

| UM93510AH | Announcing phone & Toy  | Chip Form           |  |

| UM93510BH | Answering machine & Toy | Chip Form           |  |

Telephone Related Products