# LM2633 Advanced Two-Phase Synchronous Triple Regulator Controller for Notebook CPUs

### **General Description**

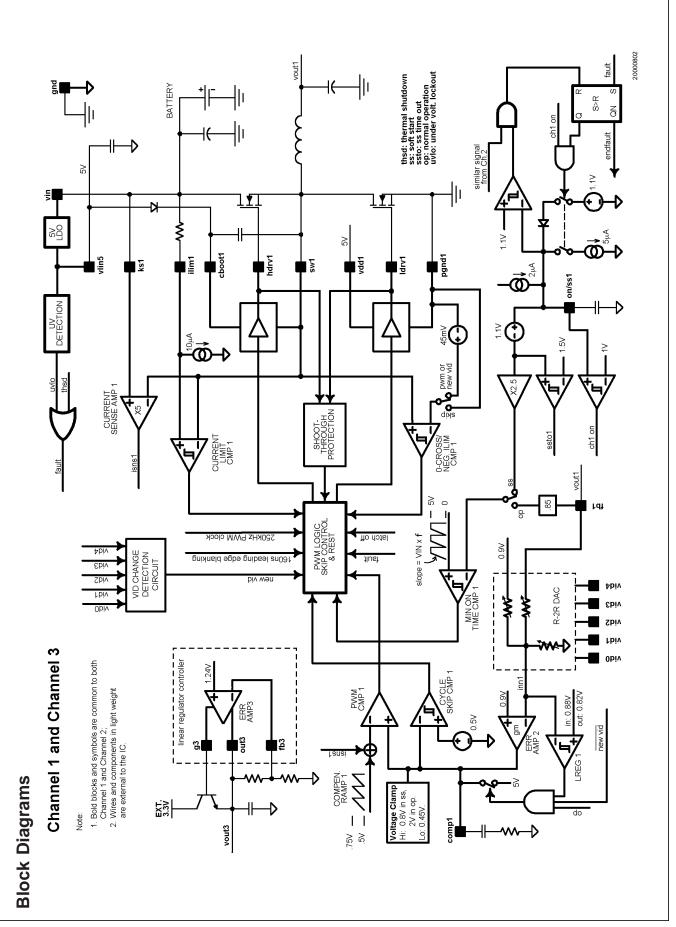

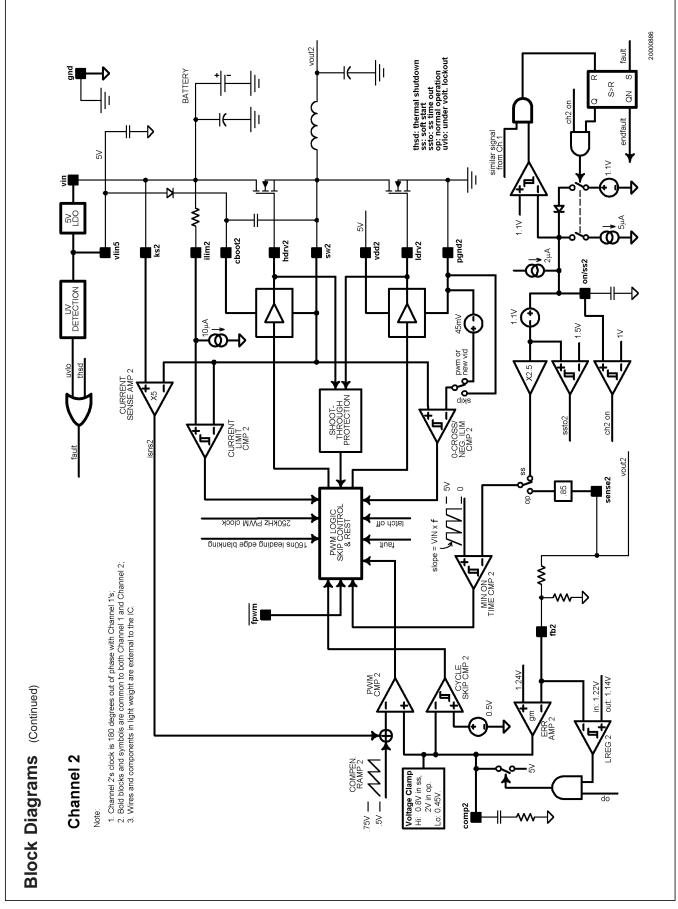

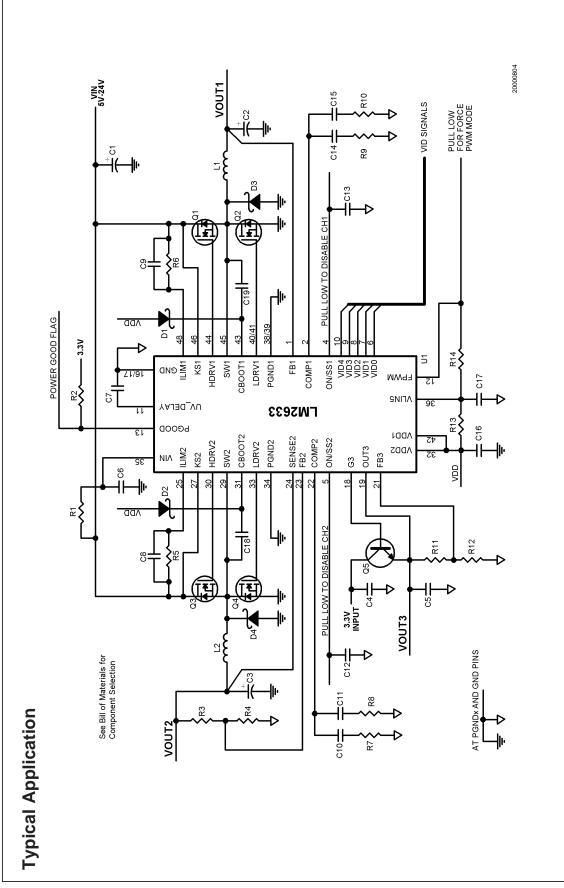

The LM2633 is a feature-rich IC that combines three regulator controllers - two current mode synchronous buck regulator controllers and a linear regulator controller.

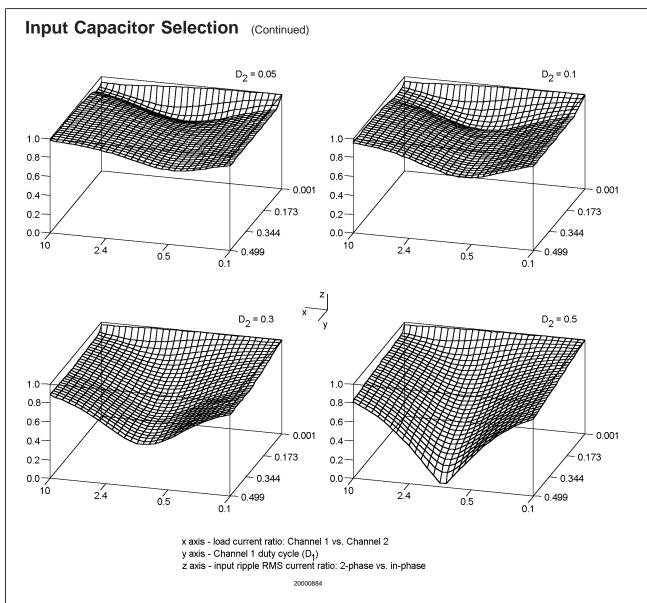

The two switching regulator controllers operate 180° out of phase. This feature reduces the input ripple RMS current, resulting in a smaller input filter.

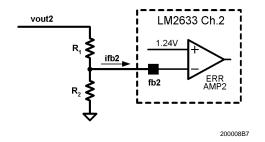

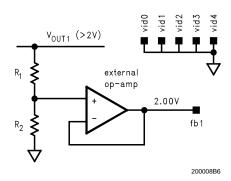

The first switching controller (Channel 1) features an Intel mobile CPU compatible precision 5-bit digital-to-analog converter which programs the output voltage from 0.925V to 2.00V. It is also compatible with the dynamic VID requirements. The second switching controller (Channel 2) is adjustable between 1.25V to 6.0V.

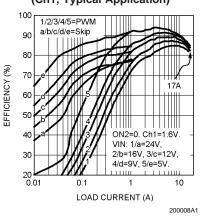

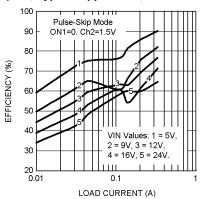

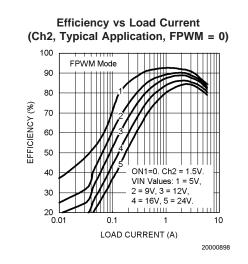

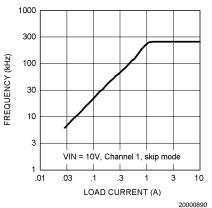

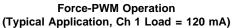

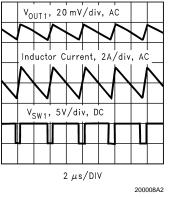

Use of synchronous rectification and pulse-skip operation at light load achieves high efficiency over a wide load range. Fixed-frequency operation can be obtained by disabling the pulse-skip mode.

Current-mode feedback control assures excellent line and load regulation and a wide loop bandwidth for good response to fast load transient events. Current mode control is achieved through sensing the Vds of the top FET and thus an external sense resistor is not necessary.

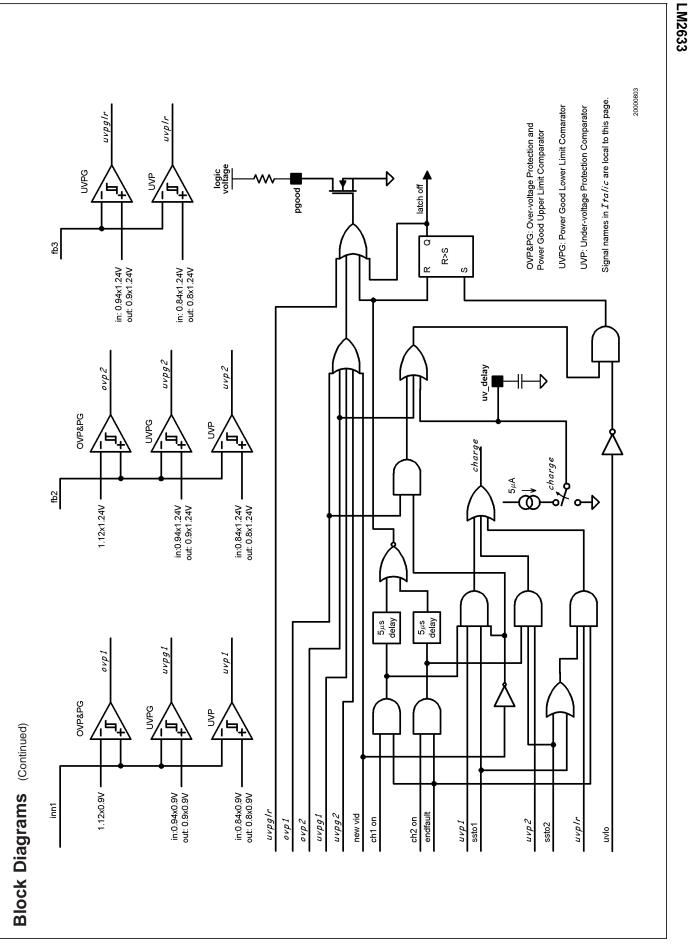

A power good signal is available to indicate the general health of the output voltages.

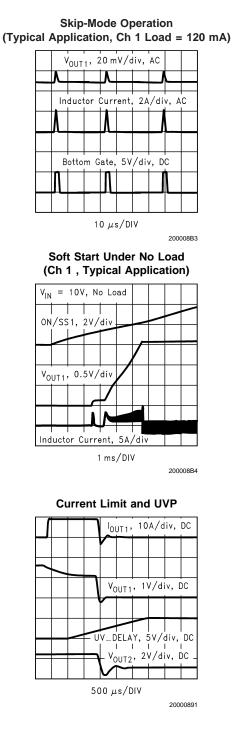

A unique feature is the analog soft-start for the switching controllers is independent of the slew rate of the input voltage. This will make the soft start behavior more predictable and controllable. An internal 5V rail is available externally for boot-strap circuitry (only) when no 5V is available from other sources.

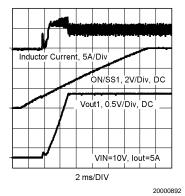

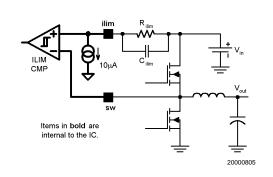

Current limit for either of the two switching channels is achieved through sensing the top FET  $V_{DS}$  and the value is adjustable. The two switching controllers have under-voltage and over-voltage latch protections, and the linear regulator has under-voltage latch protection. Under-voltage latch can be disabled or delayed by a programmable amount of time.

The input voltage for the switching channels ranges from 5V to 30V, which makes possible the choice of different battery chemistries and options.

### Features

### GENERAL

- Three regulated output voltages

- 4.5V to 30V input range

- Power good function

- Input under-voltage lockout

- Thermal shutdown

- Tiny TSSOP package

### SWITCHING SECTION

- Two channels operating 180° out of phase

- Separate on/off control for each channel

- Current mode control without sense resistor

- Skip-mode operation available

- Adjustable cycle-by-cycle current limit

- Negative current limit

- Analog soft start independent of input voltage slew rate

- Power ground pins separate

- Output UVP and OVP

- Programmable output UVP delay

- 250kHz switching frequency (for Vin < 17V)

- Channel 1 output from 0.925V to 2.00V

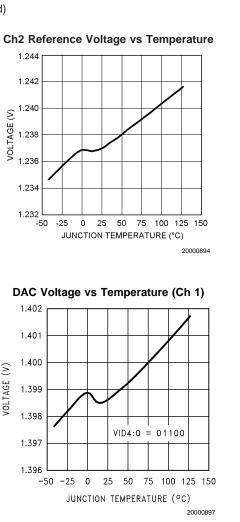

- ±1.5% DAC accuracy from 0°C to 125°C

- ±1.7% initial tolerance for Channel 2

- Dynamic VID change ready

- Power good flags VID changes

- Channel 2 output from 1.3V to 6.0V

### LINEAR SECTION

- Output voltage adjustable

- 50mA maximum driving current

- Output UVP

- ±2% initial tolerance

### Applications

- Power supply for CPUs of notebook PCs that require the SpeedStep<sup>™</sup> technique

- Power supply for information appliances

- General low voltage DC/DC buck regulators

SpeedStep™ is a trademark of Intel Corporation.

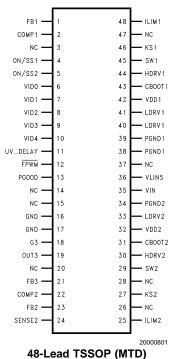

## Connection Diagram

**TOP VIEW**

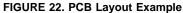

48-Lead TSSOP (MTD) Order Number LM2633MTD See NS Package Number MTD48

### **Pin Descriptions**

**FB1 (Pin 1):**The feedback input for Channel 1. Connect to the load directly.

**COMP1 (Pin 2):** Channel 1 compensation network connection (connected to the output of the voltage error amplifier).

NC (Pins 3, 14, 15, 20, 26, 28, 37 and 47): No internal connection.

**ON/SS1 (Pin 4):** Adding a capacitor to this pin provides a soft-start function which minimizes inrush current and output voltage overshoot; A lower than 0.8V input (open-collector type) at this pin turns off Channel 1; also if both ON/SS1 and ON/SS2 pins are below 0.8V, the whole IC goes into *shut down mode*. The soft-start capacitor voltage will eventually be charged to  $V_{IN}$  or 6V, whichever is lower.

**ON/SS2 (Pin 5):** Adding a capacitor to this pin provides a soft-start function which minimizes inrush current and output voltage overshoot; A lower than 0.8V input (open-collector type) at this pin turns off Channel 2; also if both ON/SS1 and ON/SS2 pins are below 0.8V, the whole IC goes into *shut down mode*. The soft-start capacitor voltage will eventually be charged to  $V_{IN}$  or 6V, whichever is lower.

**VID4-0 (Pins 6-10):** Voltage identification code. Each pin has an internal pull-up. They can accept open collector compatible 5-bit binary code from the CPU. The code table is shown in *Table 3.*

**UV\_ DELAY (Pin 11):** A capacitor from this pin to ground adjusts the delay for the output under-voltage lockout.

**FPWM** (Pin 12): When FPWM is low, pulse-skip mode operation at light load is disabled. The regulator is forced to operate in constant frequency mode.

**PGOOD (Pin 13):** A constant monitor on the output voltages. It indicates the general health of the regulators. For more information, *see Power Good Truth Table (Table 2)* and *Power Good Function* in *Operation Descriptions*.

GND (Pin 16-17): Low-noise analog ground.

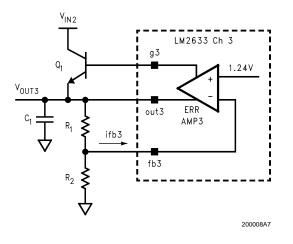

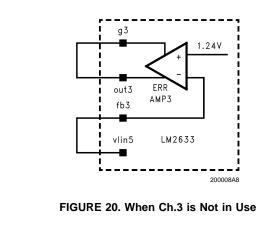

**G3 (Pin 18):** Connect to the base or gate of the linear regulator pass transistor.

OUT3 (Pin 19): Connect to the output of the linear regulator.

**FB3 (Pin 21):** The feedback input for the linear regulator, connected to the center of the external resistor divider.

**COMP2 (Pin 22):** Channel 2 compensation network connection (it's the output of the voltage error amplifier).

**FB2 (Pin 23):** The feedback input for Channel 2. Connect to the center of the output resistor divider.

**SENSE2 (Pin 24):** Remote sense pin of Channel 2. This pin is used for skip-mode operation.

**ILIM2 (Pin 25):** Current limit threshold setting for Channel 2. It sinks at a constant 10  $\mu$ A current. A resistor is connected between this pin and the top MOSFET drain. The voltage across this resistor is compared with the V<sub>DS</sub> of the top MOSFET to determine if an over-current condition has occurred in Channel 2.

**KS2 (Pin 27):** The Kelvin sense for the drain of the top MOSFET of Channel 2.

**SW2 (Pin 29):** Switch-node connection for Channel 2, which is connected to the source of the top MOSFET.

**HDRV2 (Pin 30):** Top gate-drive output for Channel 2. HDRV2 is a floating drive output that rides on SW2 voltage.

**CBOOT2 (Pin 31):** Bootstrap capacitor connection for Channel 2 top gate drive. It is the positive supply rail for Channel 2 top gate drive.

VDD2 (Pin 32): The supply rail for Channel 2 bottom gate drive.

LDRV2 (Pin 33): Bottom gate-drive output for Channel 2.

PGND2 (Pin 34): Power ground for Channel 2.

VIN (Pin 35): The regulator input voltage supply.

**VLIN5 (Pin 36):** The output of the internal 5V linear regulator. Bypass to the ground with a 1UF ceramic capacitor. When regulator input voltage is 5V, this pin can be tied to VIN pin to improve light-load efficiency.

PGND1 (Pin 38-39): Power ground for Channel 1.

LDRV1 (Pin 40-41): Bottom gate-drive output for Channel 1. VDD1 (Pin 42): The supply rail for the Channel 1 bottom gate drive.

**CBOOT1 (Pin 43):** Bootstrap capacitor connection for Channel 1 top gate drive. It is the positive supply rail for Channel 1 top gate drive.

**HDRV1 (Pin 44):** Top gate-drive output for Channel 1. HDRV1 is a floating drive output that rides on SW1 voltage.

**SW1 (Pin 45):** Switch-node connection for Channel 1, which is connected to the source of the top MOSFET.

**KS1 (Pin 46):** The Kelvin sense for the drain of the top MOSFET of Channel 1.

**ILIM1 (Pin 48):** Current limit threshold setting for Channel 1. It sinks at a constant 10  $\mu$ A current. A resistor is connected between this pin and the top MOSFET drain. The voltage across this resistor is compared with the V<sub>DS</sub> of the top MOSFET to determine if an over-current condition has occurred in Channel 1.

### TABLE 1. Shut Down Latch Truth Table

| v |   |

|---|---|

| ç | າ |

| G | D |

| C | N |

|   | 5 |

|   | = |

| _ |   |

| _ | _ |

|      |      |      |      |       |            |            |        |       |       |       |          | 1         |

|------|------|------|------|-------|------------|------------|--------|-------|-------|-------|----------|-----------|

|      |      |      |      |       | li li      | nput       |        |       |       |       |          | Output    |

| ovp1 | ovp2 | uvp1 | uvp2 | uvplr | new<br>vid | ch1 on     | ch2 on | fault | ssto1 | ssto2 | uv_delay | latch off |

| 1    |      |      |      |       | 0          | Σ:         | =1     | 0     |       |       |          | 1         |

|      | 1    |      |      |       |            | Σ:         | =1     | 0     |       |       |          | 1         |

|      |      | 1    |      |       | 0          | 1          |        | 0     | 1     |       | сар      | 1         |

|      |      |      | 1    |       |            |            | 1      | 0     |       | 1     | сар      | 1         |

|      |      |      |      | 1     |            | $\Sigma$ : | = 1    | 0     | Σ :   | = 1   | сар      | 1         |

|      |      |      |      |       | All other  | combinatio | ons    |       |       |       |          | 0         |

Note 1: ' $\Sigma$ =1' means at least one variable is high.

Note 2: 'Fault' is the logic OR of UVLO and thermal shutdown.

Note 3: 'Cap' means the pin has a capacitor of appropriate value between it and ground.

Note 4: Positive logic is used.

Note 5: For meanings of the variables, refer to the block diagrams.

Note 6: A blank value means 'don't care'.

TABLE 2. Power Good Truth Table

|      | Input |       |       |             |            |        |        | Output |           |       |

|------|-------|-------|-------|-------------|------------|--------|--------|--------|-----------|-------|

| ovp1 | ovp2  | uvpg1 | uvpg2 | uvpglr      | new<br>vid | ch1 on | ch2 on | fault  | latch off | PGOOD |

| 1    |       |       |       |             |            |        |        |        |           | 0     |

|      | 1     |       |       |             |            |        |        |        |           | 0     |

|      |       | 1     |       |             |            |        |        |        |           | 0     |

|      |       |       | 1     |             |            |        |        |        |           | 0     |

|      |       |       |       | 1           |            |        |        |        |           | 0     |

|      |       |       |       |             | 1          |        |        |        |           | 0     |

|      |       |       |       |             |            | π :    | = 0    |        |           | 0     |

|      |       |       |       |             |            |        |        | 1      |           | 0     |

|      |       |       |       |             |            |        |        |        | 1         | 0     |

|      |       |       |       | All other c | ombinatior | IS     |        |        |           | 1     |

Note 7: " $\pi = 0$ " means at least one variable is low.

Note 8: Positive logic is used.

Note 9: A blank value means 'don't care'.

Note 10: For meanings of the variables, refer to the block diagrams.

| TABLE 3. | VID | Code | and | DAC | Output |

|----------|-----|------|-----|-----|--------|

|          |     |      |     |     |        |

| VID4 | VID3 | VID2 | VID1 | VID0 | DAC Voltage (V) |

|------|------|------|------|------|-----------------|

| 1    | 1    | 1    | 1    | 1    | No CPU*         |

| 1    | 1    | 1    | 1    | 0    | 0.925           |

| 1    | 1    | 1    | 0    | 1    | 0.950           |

| 1    | 1    | 1    | 0    | 0    | 0.975           |

| 1    | 1    | 0    | 1    | 1    | 1.000           |

| 1    | 1    | 0    | 1    | 0    | 1.025           |

| 1    | 1    | 0    | 0    | 1    | 1.050           |

| 1    | 1    | 0    | 0    | 0    | 1.075           |

| 1    | 0    | 1    | 1    | 1    | 1.100           |

| 1    | 0    | 1    | 1    | 0    | 1.125           |

| 1    | 0    | 1    | 0    | 1    | 1.150           |

| 1    | 0    | 1    | 0    | 0    | 1.175           |

| 1    | 0    | 0    | 1    | 1    | 1.200           |

| 1    | 0    | 0    | 1    | 0    | 1.225           |

| Ζ   |

|-----|

| N   |

| င္သ |

| ũ   |

| VID4 | VID3 | VID2 | VID1 | VID0 | DAC Voltage (V) |

|------|------|------|------|------|-----------------|

| 1    | 0    | 0    | 0    | 1    | 1.250           |

| 1    | 0    | 0    | 0    | 0    | 1.275           |

| 0    | 1    | 1    | 1    | 1    | No CPU          |

| 0    | 1    | 1    | 1    | 0    | 1.30            |

| 0    | 1    | 1    | 0    | 1    | 1.35            |

| 0    | 1    | 1    | 0    | 0    | 1.40            |

| 0    | 1    | 0    | 1    | 1    | 1.45            |

| 0    | 1    | 0    | 1    | 0    | 1.50            |

| 0    | 1    | 0    | 0    | 1    | 1.55            |

| 0    | 1    | 0    | 0    | 0    | 1.60            |

| 0    | 0    | 1    | 1    | 1    | 1.65            |

| 0    | 0    | 1    | 1    | 0    | 1.70            |

| 0    | 0    | 1    | 0    | 1    | 1.75            |

| 0    | 0    | 1    | 0    | 0    | 1.80            |

| 0    | 0    | 0    | 1    | 1    | 1.85            |

| 0    | 0    | 0    | 1    | 0    | 1.90            |

| 0    | 0    | 0    | 0    | 1    | 1.95            |

| 0    | 0    | 0    | 0    | 0    | 2.00            |

\*This code is set to 0.900V for convenience.

### Absolute Maximum Ratings (Note 11)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

Voltages from the indicated pins to GND/PGND:

| VIN, KS1, KS2, SW1, SW2                    | -0.3V to 31V     |

|--------------------------------------------|------------------|

| VIN, NOT, NOZ, SWT, SWZ                    | -0.37 10 317     |

| ILIM1, ILIM2                               | -0.3V to 31V     |

| VID0-VID4                                  | -0.3V to 5V      |

| VLIN, VDD1, VDD2, PGOOD                    | -0.3V to 6V      |

| FB1, FB2, SENSE2, G3, FB3, OUT3            | -0.3V to 6V      |

| CBOOT1                                     | -0.3V to SW1+ 7V |

| CBOOT2                                     | -0.3V to SW2+ 7V |

| ON/SS1, ON/SS2                             | -0.3V to 5V      |

| FPWM                                       | -0.3V to 7V      |

| Power Dissipation ( $T_A = 25^{\circ}C$ ), |                  |

| (Note 12)                                  | 1.56W            |

| Junction Temperature                       | +150°C           |

|                                            |                  |

| ESD Rating (Note 14)                 | 2kV             |

|--------------------------------------|-----------------|

| Ambient Storage Temperature          |                 |

| Range                                | –65°C to +150°C |

| Soldering Dwell Time, Temperature (N | Note 13)        |

| Wave                                 | 4 sec, 260°C    |

| Infrared                             | 10sec, 240°C    |

| Vapor Phase                          | 75sec, 219°C    |

|                                      |                 |

### Operating Ratings(Note 11)

| VIN (VIN and VLIN5 tied      |                 |

|------------------------------|-----------------|

| together)                    | 4.5V to 5.5V    |

| VIN (VIN and VLIN5 separate) | 5.0V to 30V     |

| Junction Temperature 1       | 0°C to +125°C   |

| Junction Temperature 2       | –40°C to +125°C |

| VDD1, VDD2                   | 4.5V to 5.5V    |

### **Electrical Characteristics**

$V_{CC}$  = +15V unless otherwise indicated under the **Conditions** column. Typicals and limits appearing in plain type apply for T<sub>A</sub> = T<sub>J</sub> = +25°C. Limits appearing in **boldface** type apply over 0°C to +125°C.

| Symbol                  | Parameter                                                 | Conditions                                                  | Min | Тур  | Max | Units |

|-------------------------|-----------------------------------------------------------|-------------------------------------------------------------|-----|------|-----|-------|

| SYSTEM                  | 1                                                         | 1                                                           | 1   |      |     | -1    |

| $\Delta V_{out1\_load}$ | Channel 1 Load<br>Regulation (Note 17)                    | V <sub>COMP1</sub> moves from 0.5V to 1.5V,<br>VID4:0=01101 |     | 0    |     | mV    |

| $\Delta V_{out2\_load}$ | Channel 2 Load<br>Regulation (Note 17)                    | $V_{\rm COMP2}$ moves from 0.5V to 1.5V                     |     | 1.5  |     | mV    |

| $\Delta V_{fb}$         | Line Regulation (for the two switching regulators)        | $5.0V \le VIN \le 30V$ , VID4:0=01101                       |     | 2    |     | mV    |

| l <sub>vin</sub>        | Input Supply Current<br>with the Switching<br>Channels ON | V <sub>FB</sub> = 0.9V, no VLIN5 DC Current<br>(Note 18)    |     | 1.5  | 2.4 | mA    |

| I <sub>vin_sd</sub>     | Input Supply Current<br>with the IC Shut Down             | $V_{ON/SS1} = V_{ON/SS2} = 0V$<br>(Note 19)                 |     | 10   | 18  | μA    |

| $V_{vlin5}$             | VLIN5 Output Voltage                                      | $I_{VLIN5} = 0$ to 25mA, 5.5V < VIN < 30V                   | 4.7 | 5.0  | 5.3 | V     |

| l <sub>ilim_pos</sub>   | ILIM1 and ILIM2 Pins<br>Sink Current                      |                                                             | 8   | 10   | 12  | μA    |

| V <sub>ilim_neg</sub>   | Negative Current Limit<br>(SWx vs PGNDx<br>voltage)       |                                                             |     | 45   |     | mV    |

| I <sub>ss_sc</sub>      | Soft Start Charge<br>Current                              |                                                             | 0.5 | 2.25 | 5   | μA    |

| l <sub>ss_sk</sub>      | Soft Start Sink Current                                   | In UVLO or thermal shutdown                                 |     | 2    |     | μA    |

| V <sub>ss_on</sub>      | Soft Start ON Threshold                                   |                                                             |     | 1.2  |     | V     |

| V <sub>ssto</sub>       | Soft Start Timeout<br>Threshold                           | (Note 20)                                                   |     | 3.5  |     | V     |

| V <sub>uvd</sub>        | UV_DELAY Threshold                                        | VLIN5 = 5V (Note 21)                                        |     | 2.1  |     | V     |

| I <sub>delay</sub>      | UV_DELAY Source<br>Current                                |                                                             | 1.0 | 5    | 9.0 | μA    |

| l <sub>vid</sub>        | VID4:0 Internal Pull Up<br>Current                        |                                                             |     | 6    | 13  | μA    |

|                       | C. Linnis appearing in <b>Dolu</b>                                                                                | face type apply over 0°C to +125°C.         |     |       |     |                     |

|-----------------------|-------------------------------------------------------------------------------------------------------------------|---------------------------------------------|-----|-------|-----|---------------------|

| Symbol                | Parameter                                                                                                         | Conditions                                  | Min | Тур   | Max | Units               |

| SYSTEM                |                                                                                                                   | · · · · · · · · · · · · · · · · · · ·       |     | · · · |     |                     |

| $V_{uvlo\_thr}$       | VIN Under-voltage<br>Lockout (UVLO)<br>Threshold                                                                  | Rising Edge                                 |     | 4.2   | 4.5 | V                   |

| V <sub>uvlo_hys</sub> | VIN UVLO Hysteresis                                                                                               |                                             |     | 300   |     | mV                  |

| V <sub>uvp1</sub>     | Channel 1 V <sub>OUT</sub><br>Under-voltage Shutdown<br>Latch Threshold<br>(Measured at the FB1)                  | VID4:0 = 01100                              | 73  | 80    | 83  | %V <sub>OUT</sub>   |

| V <sub>uvp2, 3</sub>  | Channels 2 and 3 V <sub>OUT</sub><br>Undervoltage Shutdown<br>Latch Threshold<br>(Measured at the FB2<br>and FB3) | VID4:0 = 01100                              | 76  | 80    | 86  | %V <sub>OUT</sub>   |

| V <sub>ovp1</sub>     | V <sub>OUT</sub> Overvoltage<br>Shutdown Latch<br>Threshold for Channel 1<br>(Measured at the FB1)                |                                             | 110 | 114   | 119 | %V <sub>OUT</sub>   |

| V <sub>ovp2</sub>     | V <sub>OUT</sub> Overvoltage<br>Shutdown Latch<br>Threshold for Channel 2<br>(Measured at the FB2)                |                                             | 109 | 112   | 115 | %V <sub>OUT</sub>   |

| V <sub>Ireg_thr</sub> | V <sub>OUT</sub> Low Regulation<br>Comparator Enable<br>Threshold for Channels<br>1 and 2                         |                                             |     | 91.5  |     | %V <sub>OUT</sub>   |

| $V_{lreg_hys}$        | Hysteresis of Low<br>Regulation Comparator                                                                        |                                             |     | 7     |     | %V <sub>out</sub>   |

| V <sub>pwrbad</sub>   | Regulator Window<br>Detector Thresholds                                                                           |                                             | 85  | 88    |     | – %V <sub>оит</sub> |

|                       | (PGOOD from High to<br>Low)                                                                                       | (Note 22)                                   | 110 | 112   | 119 | ,                   |

| V <sub>pwrgd</sub>    | Regulator Window<br>Detector Thresholds<br>(PGOOD from Low to<br>High)                                            |                                             | 90  | 93    | 97  | %V <sub>OUT</sub>   |

| Gate Drive (          | For Channel 1 Switching R                                                                                         | legulator Controller)                       |     |       |     |                     |

| I <sub>boot1</sub>    | CBOOT Leakage<br>Current                                                                                          | V <sub>CBOOT1</sub> = 7V                    |     | 100   |     | nA                  |

|                       | HDRV1 Source Current                                                                                              | $V_{HDRV1} = V_{SW1} = 0V, V_{CBOOT1} = 5V$ |     | 1.2   |     | Α                   |

|                       | HDRV1 Sink Current                                                                                                | V <sub>HDRV1</sub> = 5V                     |     | 1.0   |     | A                   |

|                       | LDRV1 Source Current                                                                                              | $V_{LDRV1} = 0V$                            |     | 1.2   |     | Α                   |

|                       | LDRV1 Sink Current                                                                                                | V <sub>LDRV1</sub> = 5V                     |     | 2.0   |     | A                   |

|                       | HDRV1 High-Side FET<br>On-Resistance                                                                              |                                             |     | 1.84  |     | Ω                   |

|                       | LDRV1 High-Side FET<br>On-Resistance                                                                              |                                             |     | tbd   |     | Ω                   |

|                       | LDRV1 Low-Side FET<br>On-Resistance                                                                               |                                             |     | 0.5   |     | Ω                   |

www.national.com

9

**Electrical Characteristics** (Continued)  $V_{CC} = +15V$  unless otherwise indicated under the **Conditions** column. Typicals and limits appearing in plain type apply for  $T_A = T_J = +25^{\circ}C$ . Limits appearing in **boldface** type apply over 0°C to +125°C.

| Symbol                                   | Parameter                                | Conditions                                                                | Min   | Тур   | Max   | Units |

|------------------------------------------|------------------------------------------|---------------------------------------------------------------------------|-------|-------|-------|-------|

| Gate Drive (                             | For Channel 2 Switching F                | Regulator Controller)                                                     |       | · .   |       |       |

| l <sub>boot2</sub>                       | CBOOT Leakage<br>Current                 | V <sub>CBOOT2</sub> = 7V                                                  |       | 100   |       | nA    |

|                                          | HDRV2 Source Current                     | $V_{HDRV2} = V_{SW2} = 0V, V_{CBOOT2} = 5V$                               |       | tbd   |       | A     |

|                                          | HDRV2 Sink Current                       | $V_{HDRV2} = 5V$                                                          |       | tbd   |       | A     |

|                                          | LDRV2 Source Current                     | $V_{LDRV2} = 0V$                                                          |       | tbd   |       | A     |

|                                          | LDRV2 Sink Current                       | $V_{LDRV2} = 5V$                                                          |       | tbd   |       | A     |

|                                          | HDRV2 FET                                |                                                                           |       |       |       |       |

|                                          | On-Resistance                            |                                                                           |       | tbd   |       | Ω     |

|                                          | LDRV2 FET                                |                                                                           |       |       |       |       |

|                                          | On-Resistance                            |                                                                           |       | tbd   |       | Ω     |

| Oscillator                               |                                          |                                                                           |       | 11    |       |       |

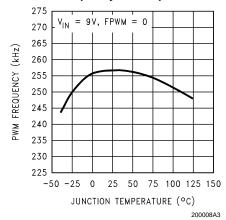

| F <sub>osc</sub>                         | Oscillator Frequency                     |                                                                           | 225   | 250   | 275   | kHz   |

| T <sub>off_min</sub>                     | Minimum Off-Time                         |                                                                           |       | 400   |       | ns    |

| T <sub>on_min</sub>                      | Minimum On-Time                          |                                                                           |       | 220   |       | ns    |

| Error Ampli                              | fier                                     |                                                                           |       |       |       |       |

| I <sub>fb1</sub>                         | Feedback Input Bias                      | V <sub>FB1</sub> = 2.4V                                                   |       |       |       |       |

| 101                                      | Current, Channel 1                       | FBI                                                                       |       | 55    |       | μΑ    |

| I <sub>fb2</sub>                         | Feedback Input Bias                      | V <sub>FB2</sub> = 1.36V                                                  |       |       |       |       |

| 102                                      | Current, Channel 2                       | 1 02                                                                      |       | 18    |       | nA    |

| I <sub>fb3</sub>                         | Feedback Input Bias                      | V <sub>FB3</sub> = 1.36V                                                  |       |       |       |       |

|                                          | Current, Channel 3                       |                                                                           |       | 70    |       | nA    |

| I <sub>comp1</sub> ,                     | COMP Output Sink                         | $V_{FB1} = 150\%$ of measured 1.4V DAC,                                   |       |       |       |       |

| I <sub>comp2</sub>                       | Current                                  | $V_{FB2}$ = 150% of measured bandgap,                                     |       | 60    | μA    |       |

|                                          |                                          | $V_{COMP1} = V_{COMP2} = 1V$                                              |       |       |       |       |

| V <sub>comp_max</sub>                    | COMP Pin Maximum                         |                                                                           | tbd   | 1.96  |       | V     |

|                                          | Voltage                                  |                                                                           | ibu   | 1.90  |       | v     |

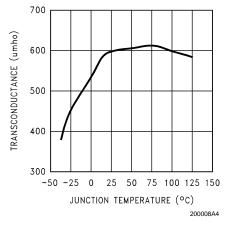

| Gm                                       | Transconductance                         |                                                                           |       | 576   |       | µmho  |

| DAC Output                               | and V <sub>FB2</sub>                     |                                                                           |       |       |       |       |

| $\Delta V_{dac}$                         | Channel 1 DAC Output<br>Voltage Accuracy | VCOMP1 = 1V, DAC codes from 1.3V<br>to 1.6V                               | -1.5  |       | 1.5   |       |

|                                          |                                          | VCOMP1 = 1V, DAC codes from<br>0.925V to 1.25V and from 1.65V to<br>2.00V | -1.7  |       | 1.7   | %     |

| V <sub>fb2</sub>                         | Channel 2 DC Output<br>Voltage Accuracy  | COMP2 pin from 0.5V to 1.8V                                               | 1.217 | 1.238 | 1.259 | V     |

| Linear Requ                              | lator Controller                         | 1                                                                         |       |       |       | 1     |

| V <sub>fb3</sub>                         | Channel 3 DC Output                      |                                                                           |       |       |       |       |

| * 103                                    | Voltage Accuracy                         |                                                                           | 1.215 | 1.24  | 1.265 | V     |

| V <sub>g3_sk</sub>                       | G3 Sink Current                          |                                                                           |       | 20    |       | μA    |

| <sup>v</sup> g3_sk<br>I <sub>g3_sc</sub> | G3 Minimum Source                        |                                                                           |       |       |       | P"''  |

| .g3_sc                                   | Current                                  |                                                                           |       | 20    |       | mA    |

| V <sub>g3_max</sub>                      | G3 Maximum Voltage                       |                                                                           |       | 3.6   |       | V     |

#### Electrical Characteristics (Continued) $V_{CC} = +15V$ unless otherwise indicated under the **Conditions** column. Typicals and limits appearing in plain type apply for $T_A = T_J = +25^{\circ}C$ . Limits appearing in **boldface** type apply over 0°C to +125°C. Symbol Parameter Conditions Min Тур Мах Units Logic Inputs and Outputs $\mathsf{V}_{\mathsf{ih}}$ Minimum High Level Input Voltage (FPWM, 2.0 V VID0-VID4) $V_{il}$ Maximum Low Level Input Voltage (FPWM, V 0.8 ON/SS1, ON/SS2, VID0-VID4) PGOOD Output High PGOOD = 5.7V (Note 23) I<sub>oh\_pg</sub> 5 μΑ Current V<sub>ol\_pg</sub> PGOOD Output Low PGOOD Sinking 20 µA V 0.3 Voltage

### **Electrical Characteristics**

$V_{CC}$  = +15V unless otherwise indicated under the **Conditions** column. Typicals and limits appearing in plain type apply for T<sub>A</sub> = T<sub>J</sub> = +25°C. Limits appearing in **boldface** type apply over -40°C to +125°C.

| Symbol                  | Parameter                                                                                                         | Conditions                                                                                                                     | Min | Тур  | Max | Units            |

|-------------------------|-------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|------------------|

| SYSTEM                  |                                                                                                                   |                                                                                                                                |     |      |     |                  |

| $\Delta V_{out1\_load}$ | Channel 1 Load<br>Regulation (Note 17)                                                                            | V <sub>COMP1</sub> moves from 0.5V to 1.5V,<br>VID4:0=01101                                                                    |     | 0    |     | mV               |

| $\Delta V_{out2\_load}$ | Channel 2 Load<br>Regulation (Note 17)                                                                            | V <sub>COMP2</sub> moves from 0.5V to 1.5V                                                                                     |     | 1.5  |     | mV               |

| ΔV <sub>fb</sub>        | Line Regulation (for the two switching regulators)                                                                | $5.0V \le VIN \le 30V$ , VID4:0=01101                                                                                          |     | 2    |     | mV               |

| l <sub>vin</sub>        | Input Supply Current<br>with the Switching<br>Channels ON                                                         | V <sub>FB</sub> = 0.9V, no VLIN5 DC Current<br>(Note 18)                                                                       |     | 1.5  | 2.5 | mA               |

| l <sub>vin_sd</sub>     | Input Supply Current<br>with the IC Shut Down                                                                     | $V_{ON/SS1} = V_{ON/SS2} = 0V$<br>(Note 19)                                                                                    |     | 10   | 18  | μA               |

| V <sub>vlin5</sub>      | VLIN5 Output Voltage                                                                                              | $I_{VLIN5} = 0$ to 25mA, 5.5V < VIN < 4.30V                                                                                    |     | 5.0  | 5.3 | V                |

| l <sub>ilim_pos</sub>   | ILIM1 and ILIM2 Pins<br>Sink Current                                                                              | 7                                                                                                                              |     | 10   | 13  | μA               |

| V <sub>ilim_neg</sub>   | Negative Current Limit<br>(SWx vs PGNDx<br>voltage)                                                               |                                                                                                                                |     | 45   |     | mV               |

| I <sub>ss_sc</sub>      | Soft Start Charge<br>Current                                                                                      |                                                                                                                                | 0.5 | 2.25 | 5   | μA               |

| ss_sk                   | Soft Start Sink Current                                                                                           | In UVLO or thermal shutdown                                                                                                    |     | 2    |     | μA               |

| V <sub>ss_on</sub>      | Soft Start ON Threshold                                                                                           |                                                                                                                                |     | 1.2  |     | V                |

| V <sub>ssto</sub>       | Soft Start Timeout<br>Threshold                                                                                   | (Note 20)                                                                                                                      |     | 3.5  |     | V                |

| V <sub>uvd</sub>        | UV_DELAY Threshold                                                                                                | VLIN5 = 5V (Note 21)                                                                                                           |     | 2.1  |     | V                |

| l <sub>delay</sub>      | UV_DELAY Source<br>Current                                                                                        |                                                                                                                                | 1.0 | 5    | 9.0 | μA               |

| l <sub>vid</sub>        | VID4:0 Internal Pull Up<br>Current                                                                                |                                                                                                                                |     | 6    | 13  | μA               |

| V <sub>uvlo_thr</sub>   | VIN Under-voltage<br>Lockout (UVLO)<br>Threshold                                                                  | Rising Edge                                                                                                                    |     | 4.2  | 4.6 | V                |

| V <sub>uvlo_hys</sub>   | VIN UVLO Hysteresis                                                                                               |                                                                                                                                |     | 300  |     | mV               |

| V <sub>uvp1</sub>       | Channel 1 V <sub>OUT</sub><br>Under-voltage Shutdown<br>Latch Threshold<br>(Measured at the FB1)                  | VID4:0 = 01100                                                                                                                 | 72  | 80   | 84  | %V <sub>ol</sub> |

| V <sub>uvp2, 3</sub>    | Channels 2 and 3 V <sub>OUT</sub><br>Undervoltage Shutdown<br>Latch Threshold<br>(Measured at the FB2<br>and FB3) | Channels 2 and 3 V <sub>OUT</sub> VID4:0 = 01100Undervoltage Shutdown<br>Latch Threshold<br>(Measured at the FB2VID4:0 = 01100 |     | 80   | 87  | %V <sub>ol</sub> |

| V <sub>ovp1</sub>       | V <sub>OUT</sub> Overvoltage<br>Shutdown Latch<br>Threshold for Channel 1<br>(Measured at the FB1)                |                                                                                                                                | 109 | 114  | 120 | %V <sub>ot</sub> |

| -                              |                                 | face type apply over -40°C to +125°C.       |     |      |     |                     |

|--------------------------------|---------------------------------|---------------------------------------------|-----|------|-----|---------------------|

| Symbol                         | Parameter                       | Conditions                                  | Min | Тур  | Max | Units               |

| SYSTEM                         |                                 |                                             |     |      |     |                     |

| V <sub>ovp2</sub>              | V <sub>OUT</sub> Overvoltage    |                                             |     |      |     |                     |

|                                | Shutdown Latch                  |                                             | 108 | 112  | 116 | %V <sub>OUT</sub>   |

|                                | Threshold for Channel 2         |                                             |     |      |     |                     |

|                                | (Measured at the FB2)           |                                             |     |      |     |                     |

| V <sub>Ireg_thr</sub>          | V <sub>OUT</sub> Low Regulation |                                             |     |      |     |                     |

|                                | Comparator Enable               |                                             |     | 91.5 |     | %V <sub>OUT</sub>   |

|                                | Threshold for Channels          |                                             |     |      |     |                     |

|                                | 1 and 2                         |                                             |     |      |     |                     |

| V <sub>Ireg_hys</sub>          | Hysteresis of Low               |                                             |     | 7    |     | %V <sub>OUT</sub>   |

|                                | Regulation Comparator           |                                             |     |      |     |                     |

| V <sub>pwrbad</sub>            | Regulator Window                |                                             | 84  | 88   |     |                     |

|                                | Detector Thresholds             |                                             |     |      |     | - %V <sub>оυт</sub> |

|                                | (PGOOD from High to             | (Note 22)                                   | 109 | 112  | 120 |                     |

|                                | Low)                            |                                             |     |      |     |                     |

| V <sub>pwrgd</sub>             | Regulator Window                |                                             |     |      |     |                     |

|                                | Detector Thresholds             |                                             | 89  | 93   | 98  | %V <sub>OUT</sub>   |

|                                | (PGOOD from Low to              |                                             |     |      |     |                     |

|                                | High)                           |                                             |     |      |     |                     |

|                                | For Channel 1 Switching R       |                                             |     |      |     |                     |

| l <sub>boot1</sub>             | CBOOT Leakage                   | V <sub>CBOOT1</sub> = 7V                    |     | 100  |     | nA                  |

|                                | Current                         |                                             |     |      |     |                     |

|                                | HDRV1 Source Current            | $V_{HDRV1} = V_{SW1} = 0V, V_{CBOOT1} = 5V$ |     | 1.2  |     | A                   |

|                                | HDRV1 Sink Current              | $V_{HDRV1} = 5V$                            |     | 1.0  |     | A                   |

|                                | LDRV1 Source Current            | $V_{LDRV1} = 0V$                            |     | 1.2  |     | A                   |

|                                | LDRV1 Sink Current              | $V_{LDRV1} = 5V$                            |     | 2.0  |     | A                   |

|                                | HDRV1 High-Side FET             |                                             |     | 1.84 |     | Ω                   |

|                                | On-Resistance                   |                                             |     | 1.04 |     |                     |

|                                | LDRV1 High-Side FET             |                                             |     | tbd  |     | Ω                   |

|                                | On-Resistance                   |                                             |     |      |     | 32                  |

|                                | LDRV1 Low-Side FET              |                                             |     | 0.5  |     | Ω                   |

|                                | On-Resistance                   |                                             |     | 0.5  |     | 52                  |

| Gate Drive (                   | For Channel 2 Switching R       | Regulator Controller)                       |     |      |     |                     |

| I <sub>boot2</sub>             | CBOOT Leakage                   | V <sub>CBOOT2</sub> = 7V                    |     | 100  |     | nA                  |

|                                | Current                         |                                             |     | 100  |     |                     |

|                                | HDRV2 Source Current            | $V_{HDRV2} = V_{SW2} = 0V, V_{CBOOT2} = 5V$ |     | tbd  |     | A                   |

|                                | HDRV2 Sink Current              | $V_{HDRV2} = 5V$                            |     | tbd  |     | A                   |

|                                | LDRV2 Source Current            | $V_{LDRV2} = 0V$                            |     | tbd  |     | A                   |

|                                | LDRV2 Sink Current              | $V_{LDRV2} = 5V$                            |     | tbd  |     | A                   |

|                                | HDRV2 FET                       |                                             |     |      |     |                     |

|                                | On-Resistance                   |                                             |     | tbd  |     | Ω                   |

|                                | LDRV2 FET                       |                                             |     |      |     |                     |

|                                | On-Resistance                   |                                             |     | tbd  |     | Ω                   |

| Oscillator                     | 1                               | 1 1                                         |     |      |     |                     |

| F <sub>osc</sub>               | Oscillator Frequency            |                                             | 225 | 250  | 275 | kHz                 |

| T <sub>off_min</sub>           | Minimum Off-Time                |                                             | -   | 400  | -   | ns                  |

| T <sub>on_min</sub>            | Minimum On-Time                 |                                             |     | 220  |     | ns                  |

| <u>'on_min</u><br>Error Amplif |                                 | <u> </u>                                    |     |      |     |                     |

| -                              | Feedback Input Bias             | V <sub>FB1</sub> = 2.4V                     |     |      |     |                     |

| fb1                            | Current, Channel 1              | v <sub>FB1</sub> - 2.4v                     |     | 55   |     | μA                  |

|                                |                                 |                                             |     |      |     |                     |

www.national.com

### Electrical Characteristics (Continued)

$V_{CC}$  = +15V unless otherwise indicated under the **Conditions** column. Typicals and limits appearing in plain type apply for T<sub>A</sub> = T<sub>J</sub> = +25°C. Limits appearing in **boldface** type apply over -40°C to +125°C.

| Symbol                                     | Parameter                                                                  | Conditions                                                                                                        | Min   | Тур   | Max   | Units |  |

|--------------------------------------------|----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|--|

| Error Ampli                                | fier                                                                       |                                                                                                                   |       |       |       | 1     |  |

| I <sub>fb2</sub>                           | Feedback Input Bias<br>Current, Channel 2                                  | V <sub>FB2</sub> = 1.36V                                                                                          |       | 18    |       | nA    |  |

| I <sub>fb3</sub>                           | Feedback Input Bias<br>Current, Channel 3                                  | V <sub>FB3</sub> = 1.36V                                                                                          |       | 70    |       | nA    |  |

| I <sub>comp1</sub> ,<br>I <sub>comp2</sub> | COMP Output Sink<br>Current                                                | $V_{FB1}$ = 150% of measured 1.4V DAC,<br>$V_{FB2}$ = 150% of measured bandgap,<br>$V_{COMP1}$ = $V_{COMP2}$ = 1V |       | 91    |       | μA    |  |

| $V_{comp_max}$                             | COMP Pin Maximum<br>Voltage                                                |                                                                                                                   | tbd   | 1.96  |       | V     |  |

| Gm                                         | Transconductance                                                           |                                                                                                                   |       | 576   |       | µmho  |  |

| DAC Output                                 | t and V <sub>FB2</sub>                                                     |                                                                                                                   |       |       |       |       |  |

| $\Delta V_{\text{dac}}$                    | Channel 1 DAC Output<br>Voltage Accuracy                                   | VCOMP1 = 1V, DAC codes from 1.3V<br>to 1.6V                                                                       | -2.0  |       | 2.0   |       |  |

|                                            |                                                                            | VCOMP1 = 1V, DAC codes from<br>0.925V to 1.25V and from 1.65V to<br>2.00V                                         | -2.2  |       | 2.2   | %     |  |

| V <sub>fb2</sub>                           | Channel 2 DC Output<br>Voltage Accuracy                                    | COMP2 pin from 0.5V to 1.8V                                                                                       | 1.212 | 1.238 | 1.264 | V     |  |

| Linear Regu                                | lator Controller                                                           |                                                                                                                   |       | -11   |       | 1     |  |

| V <sub>fb3</sub>                           | Channel 3 DC Output<br>Voltage Accuracy                                    |                                                                                                                   | 1.209 | 1.24  | 1.271 | V     |  |

| V <sub>g3_sk</sub>                         | G3 Sink Current                                                            |                                                                                                                   |       | 20    |       | μA    |  |

| l <sub>g3_sc</sub>                         | G3 Minimum Source<br>Current                                               |                                                                                                                   |       | 20    |       | mA    |  |

| V <sub>g3_max</sub>                        | G3 Maximum Voltage                                                         |                                                                                                                   |       | 3.6   |       | V     |  |

|                                            | s and Outputs                                                              |                                                                                                                   |       |       |       |       |  |

| V <sub>ih</sub>                            | Minimum High Level<br>Input Voltage (FPWM,<br>VID0-VID4)                   |                                                                                                                   | 2.2   |       |       | V     |  |

| V <sub>il</sub>                            | Maximum Low Level<br>Input Voltage (FPWM,<br>ON/SS1, ON/SS2,<br>VID0-VID4) |                                                                                                                   |       |       | 0.7   | V     |  |

| I <sub>oh_pg</sub>                         | PGOOD Output High<br>Current                                               | PGOOD = 5.7V (Note 23)                                                                                            |       | 5     |       | μA    |  |

| V <sub>ol_pg</sub>                         | PGOOD Output Low<br>Voltage                                                | PGOOD Sinking 20 µA                                                                                               |       | 0.3   |       | V     |  |

Note 11: Absolute maximum ratings indicate limits beyond which damage to the device may occur. Operating Ratings are conditions under which operation of the device is guaranteed. For guaranteed performance limits and associated test conditions, see the Electrical Characteristics table.

**Note 12:** Maximum allowable power dissipation is calculated by using  $P_{DMAX} = (T_{JMAX} - T_A)/\theta_{JA}$ , where  $T_{JMAX}$  is the maximum junction temperature,  $T_A$  is the ambient temperature and  $\theta_{JA}$  is the junction-to-ambient thermal resistance of the specified package. The 1.56W rating results from using 150°C, 25°C, and 80°C/W for  $T_{JMAX}$ ,  $T_A$ , and  $\theta_{JA}$  respectively. A  $\theta_{JA}$  of 90°C/W represents the worst-case condition of no heat sinking of the 48-pin TSSOP. Heat sinking allows the safe dissipation of more power. The Absolute Maximum power dissipation should be derated by 12.5mW per °C above 25°C ambient. The LM2633 actively limits its junction temperature to about 150°C.

Note 13: For detailed information on soldering plastic small-outline packages, refer to the Packaging Databook available from National Semiconductor Corporation. Note 14: Except for ILIM1 and ILIM2 pins, which are 1.5kV. For testing purposes, ESD was applied using the human-body model, a 100pF capacitor discharged through a 1.5kΩ resistor.

Note 15: A typical is the center of characterization data taken with  $T_A = T_J = 25^{\circ}C$ . Typical data are not guaranteed.

**Note 16:** All limits are guaranteed. All electrical characteristics having room-temperature limits are tested during production with  $T_A = T_J = 25$ °C. All hot and cold limits are guaranteed by correlating the electrical characteristics to process and temperature variations and applying statistical process control.

Note 17: This test simulates heavy load condition by changing COMP pin voltage.

Note 18: This parameter indicates how much current the LM2633 is drawing from the input supply when it is functioning but not driving external MOSFETs or a bipoloar transistor.

### Electrical Characteristics (Continued)

Note 19: This parameter indicates how much current the LM2633 is drawing from the input supply when it is completely shut off.

- Note 20: When ON/SS1,2 pins are charged above this voltage, the under voltage protection feature is enabled.

- Note 21: Above this voltage, the under-voltage protection is enabled.

- **Note 22:** This is the same as over-voltage protection threshold.

Note 23: This is the amount of current PGOOD sinks when PGOOD is high and is forced to the voltage indicated

| C2<br>C3<br>C4<br>C5<br>C6<br>C7<br>C8<br>C9<br>C10<br>C11<br>C12<br>C13<br>C14<br>C15<br>C16<br>C17<br>C18         | Number           25SP56M           T510E108M004AS           T510E108M004AS           VJ1206S105MXJAC           VJ1206S105MXJAC           VJ0805Y104MXAAB           VJ0805Y153MXJAB | Type<br>Capacitor, OSCON<br>Capacitor, Tantalum<br>Capacitor, Tantalum<br>Capacitor, Ceramic | Size           Radial, $\Phi \times L = 10.5$ x 10.5 mm <sup>2</sup> | Parameters           25V, 56 μF, 25 mΩ,           2 20 | <b>Qt.</b><br>3 | Vendor<br>Sanyo |

|---------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------|--------------------------------------------------------|-----------------|-----------------|

| C2<br>C3<br>C4<br>C5<br>C6<br>C7<br>C8<br>C9<br>C10<br>C11<br>C12<br>C13<br>C14<br>C15<br>C16<br>C17<br>C18         | T510E108M004AS<br>T510E108M004AS<br>VJ1206S105MXJAC<br>VJ1206S105MXJAC<br>VJ0805Y104MXAAB                                                                                          | Capacitor, Tantalum<br>Capacitor, Tantalum                                                   | x 10.5 mm <sup>2</sup>                                               |                                                        | 3               | Sanvo           |

| C3<br>C4<br>C5<br>C6<br>C7<br>C8<br>C9<br>C10<br>C11<br>C12<br>C13<br>C14<br>C15<br>C14<br>C15<br>C16<br>C17<br>C18 | T510E108M004AS<br>VJ1206S105MXJAC<br>VJ1206S105MXJAC<br>VJ0805Y104MXAAB                                                                                                            | Capacitor, Tantalum                                                                          | 70,460,400,3                                                         | 3.2A                                                   |                 |                 |

| C4<br>C5<br>C6<br>C7<br>C8<br>C9<br>C10<br>C11<br>C12<br>C11<br>C12<br>C13<br>C14<br>C15<br>C16<br>C17<br>C18       | VJ1206S105MXJAC<br>VJ1206S105MXJAC<br>VJ0805Y104MXAAB                                                                                                                              |                                                                                              | 7.3 x 6.0 x 3.6 mm <sup>3</sup>                                      | 4V, 1 mF, 18 mΩ                                        | 3               | Kemet           |

| C5<br>C6<br>C7<br>C8<br>C9<br>C10<br>C11<br>C12<br>C13<br>C14<br>C15<br>C16<br>C17<br>C18                           | VJ1206S105MXJAC<br>VJ0805Y104MXAAB                                                                                                                                                 | Capacitor Ceramic                                                                            | 7.3 x 6.0 x 3.6 mm <sup>3</sup>                                      | 4V, 1 mF, 18 mΩ                                        | 1               | Kemet           |

| C6<br>C7<br>C8<br>C9<br>C10<br>C11<br>C12<br>C13<br>C14<br>C15<br>C16<br>C17<br>C18                                 | VJ0805Y104MXAAB                                                                                                                                                                    |                                                                                              | 1206                                                                 | 16V, 1 μF, X7S                                         | 1               | Vishay          |

| C7<br>C8<br>C9<br>C10<br>C11<br>C12<br>C13<br>C14<br>C15<br>C16<br>C17<br>C18                                       |                                                                                                                                                                                    | Capacitor, Ceramic                                                                           | 1206                                                                 | 16V, 1 μF, X7S                                         | 1               | Vishay          |

| C8<br>C9<br>C10<br>C11<br>C12<br>C13<br>C14<br>C15<br>C16<br>C17<br>C18                                             |                                                                                                                                                                                    | Capacitor, Ceramic                                                                           | 0805                                                                 | 50V, 0.1 µF, X7R                                       | 1               | Vishay          |

| C9<br>C10<br>C11<br>C12<br>C13<br>C14<br>C15<br>C16<br>C17<br>C18                                                   | V JUUUJ I I JJIVIAJAD                                                                                                                                                              | Capacitor, Ceramic                                                                           | 0805                                                                 | 16V, 0.015 µF, X7R                                     | 1               | Vishay          |

| C10           C11           C12           C13           C14           C15           C16           C17           C18 | VJ0805Y103MXAAB                                                                                                                                                                    | Capacitor, Ceramic                                                                           | 0805                                                                 | 50V, 0.01 µF, X7R                                      | 1               | Vishay          |

| C11           C12           C13           C14           C15           C16           C17           C18               | VJ0805Y103MXAAB                                                                                                                                                                    | Capacitor, Ceramic                                                                           | 0805                                                                 | 50V, 0.01 µF, X7R                                      | 1               | Vishay          |

| C12<br>C13<br>C14<br>C15<br>C16<br>C17<br>C18                                                                       | VJ0805Y222MXJAB                                                                                                                                                                    | Capacitor, Ceramic                                                                           | 0805                                                                 | 16V, 2200 pF, X7R                                      | 1               | Vishay          |

| C13<br>C14<br>C15<br>C16<br>C17<br>C18                                                                              | VJ0805Y681MXJAB                                                                                                                                                                    | Capacitor, Ceramic                                                                           | 0805                                                                 | 16V, 680 pF, X7R                                       | 1               | Vishay          |

| C14<br>C15<br>C16<br>C17<br>C18                                                                                     | VJ0805Y472MXJAB                                                                                                                                                                    | Capacitor, Ceramic                                                                           | 0805                                                                 | 16V, 4700 pF, X7R                                      | 1               | Vishay          |

| C15<br>C16<br>C17<br>C18                                                                                            | VJ0805Y472MXJAB                                                                                                                                                                    | Capacitor, Ceramic                                                                           | 0805                                                                 | 16V, 4700 pF, X7R                                      | 1               | Vishay          |

| C16<br>C17<br>C18                                                                                                   | VJ0805Y821MXJAB                                                                                                                                                                    | Capacitor, Ceramic                                                                           | 0805                                                                 | 16V, 820 pF, X7R                                       | 1               | Vishay          |

| C17<br>C18                                                                                                          | VJ0805A221MXAAB                                                                                                                                                                    | Capacitor, Ceramic                                                                           | 0805                                                                 | 50V, 220 pF, X7R                                       | 1               | Vishay          |

| C18                                                                                                                 | VJ0805Y474MXJAB                                                                                                                                                                    | Capacitor, Ceramic                                                                           | 0805                                                                 | 16V, 0.47 µF, X7R                                      | 1               | Vishay          |

|                                                                                                                     | VJ1206S105MXJAC                                                                                                                                                                    | Capacitor, Ceramic                                                                           | 1206                                                                 | 16V, 1 µF, X7S                                         | 1               | Vishay          |

| C19                                                                                                                 | VJ0805Y104MXJAC                                                                                                                                                                    | Capacitor, Ceramic                                                                           | 0805                                                                 | 16V, 0.1 µF, X7R                                       | 1               | Vishay          |

|                                                                                                                     | VJ0805Y104MXJAC                                                                                                                                                                    | Capacitor, Ceramic                                                                           | 0805                                                                 | 16V, 0.1 µF, X7R                                       | 1               | Vishay          |

| D1                                                                                                                  | BAT54                                                                                                                                                                              | Diode, Schottky                                                                              | SOT-23                                                               | 30V, 200 mA                                            | 1               | Vishay          |

| D2                                                                                                                  | BAT54                                                                                                                                                                              | Diode, Schottky                                                                              | SOT-23                                                               | 30V, 200 mA                                            | 1               | Vishay          |

| D3                                                                                                                  |                                                                                                                                                                                    | Diode, Schottky                                                                              |                                                                      |                                                        | 1               | (optional)      |

| D4                                                                                                                  |                                                                                                                                                                                    | Diode, Schottky                                                                              |                                                                      |                                                        | 1               | (optional)      |

| L1                                                                                                                  | CEPH149-1R6MC                                                                                                                                                                      | Inductor, Power                                                                              | 14.6 x 14.6 mm <sup>2</sup>                                          | 1.6 μH, 15.5A, 1.5 mΩ                                  | 1               | Sumida          |

| L2                                                                                                                  | CDRH127-100MC                                                                                                                                                                      | Inductor, Power                                                                              | 12 x 12 mm <sup>2</sup>                                              | 10 μH, 5.4A, 21.6 mΩ                                   | 1               | Sumida          |

| Q1                                                                                                                  | IRF7805                                                                                                                                                                            | MOSFET, N-CHAN                                                                               | SO-8                                                                 | 30V, 10 mΩ @ 4.5V                                      | 1               | IR              |

| Q2                                                                                                                  | IRF7805                                                                                                                                                                            | MOSFET, N-CHAN                                                                               | SO-8                                                                 | 30V, 10 mΩ @ 4.5V                                      | 2               | IR              |

| Q3                                                                                                                  | IRF7807                                                                                                                                                                            | MOSFET, N-CHAN                                                                               | SO-8                                                                 | 30V, 25 mΩ @ 4.5V                                      | 1               | IR              |

| Q4                                                                                                                  | IRF7807                                                                                                                                                                            | MOSFET, N-CHAN                                                                               | SO-8                                                                 | 30V, 25 mΩ @ 4.5V                                      | 1               | IR              |

| Q5                                                                                                                  | MMBT2222ALT1                                                                                                                                                                       | BJT, NPN                                                                                     | SOT-23                                                               | 40V, 600 mA                                            | 1               | Motorola        |

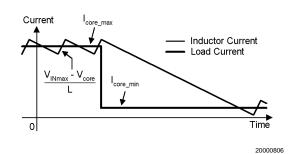

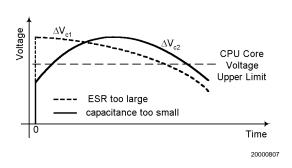

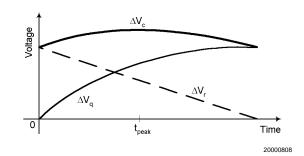

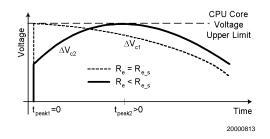

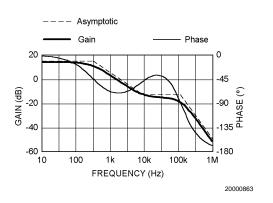

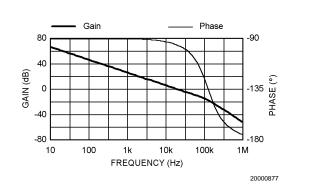

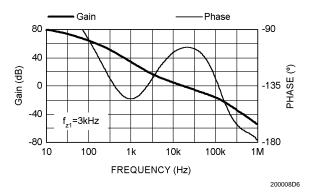

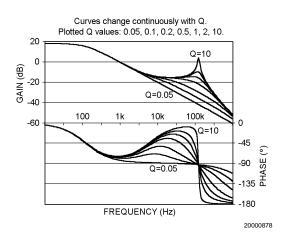

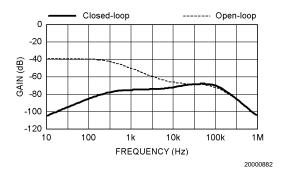

| R1                                                                                                                  | CRCW0805 100J                                                                                                                                                                      | Resistor                                                                                     | 0805                                                                 | 10Ω, 5%                                                | 1               | Vishay          |