# THIS DOCUMENT IS FOR MAINTENANCE PURPOSES ONLY AND IS NOT RECOMMENDED FOR NEW DESIGNS

DS3007-2.1

# ZN428E8/ZN428J8/ZN428D

# **8-BIT LATCHED INPUT D-A CONVERTER**

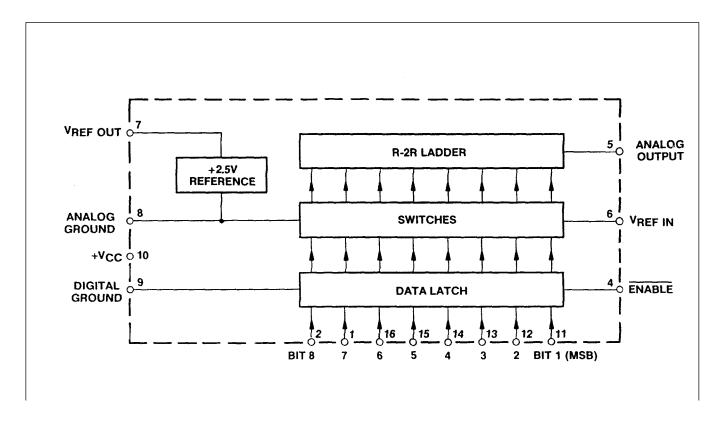

The ZN428 is a monolithic 8-bit D-A converter with input latches to facilitate updating from a data bus. The latch is transparent when enable is LOW and the data is held when enable is taken HIGH. The ZN428 also contains a 2.5V reference the use of which is pin optional to retain flexibility. An external fixed or varying reference may therefore be substituted.

#### **FEATURES**

- Contains DAC with Data Latch and On-Chip Reference

- Guaranteed Monotonic over the Full Operating Temperature Range

- Single +5V Supply

- Microprocessor Compatible

- TTL and 5V CMOS Compatible

- 800ns Settling Time

- Complementary to ZN427 A to D Series

- Commercial or Military Temperature Range

#### ORDERING INFORMATION

| Device Type | Operating temperature | Package |

|-------------|-----------------------|---------|

| ZN428D      | 0°C to +70°C          | MP16W   |

| ZN428E8     | 0°C to +70°C          | DP16    |

| ZN428J8     | -55°C to +125°C       | DC16    |

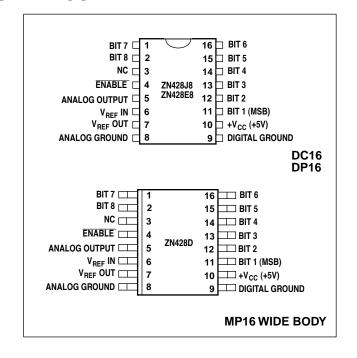

Fig.1 Pin connections (not to scale) - top view

# **ZN428**

# **ABSOLUTE MAXIMUM RATINGS**

Supply voltage V<sub>CC</sub>

Max.voltage, logic and V<sub>REF</sub> inputs

Operating temperature range +7.0V

+V<sub>CC</sub> 0°C to +70°C (ZN428E8, ZN428D) -55°C to +125°C (ZN428J8) -55°C to +125°C

Storage temperature range

Analog ground to digital ground ±200mV

# **ELECTRICAL CHARACTERISTICS**

( $V_{CC}$  = +5V,  $T_{amb}$  = 25°C unless otherwise specified)

| Parameter                                                      | Min.     | Тур.   | Max.      | Units    | Conditions                                              |

|----------------------------------------------------------------|----------|--------|-----------|----------|---------------------------------------------------------|

| Internal Voltage Reference<br>Output voltage                   | 2.475    | 2.550  | 2.625     | V        | R <sub>REF</sub> = 390Ω                                 |

| Slope resistance                                               | -        | 0.5    | 2         | Ω        | $C_{REF} = 1\mu F$                                      |

| V <sub>REF OUT</sub> T.C.                                      | -        | 50     | -         | ppm/°C   |                                                         |

| Reference current                                              | 4        | -      | 15        | mA       | Note 1                                                  |

| D-A Converter<br>Linearity error                               | -        | -      | ±0.5      | LSB      | 2.0V ≤V <sub>REF IN</sub> ≤3.0V                         |

| Differential non-linearity                                     | -        | ±0.5   | -         | LSB      |                                                         |

| Linearity error T.C.                                           | -        | ±3     | -         | ppm/°C   |                                                         |

| Differential non-linearity T.C.                                | -        | ±6     | -         | ppm/°C   |                                                         |

| Offset voltage                                                 | -        | 2      | 5         | mV       | All bits off                                            |

| Offset voltage T.C.                                            | -        | ±6     | -         | μV/°C    |                                                         |

| Full-scale output                                              | 2.545    | 2.550  | 2.555     |          | External reference                                      |

| Full-scale output T.C.                                         | -        | 2      | -         | ppm/°C   | $V_{REF\ IN} = 2.560V$ , all bits ON                    |

| Analog output resistance                                       | -        | 4      | -         | kΩ       |                                                         |

| External reference voltage                                     | 0        | -      | 3.0       | V        |                                                         |

| Settling time to 0.5 LSB                                       | -        | 800    | -         | ns       | 1 LSB major transition                                  |

|                                                                | -        | 1.25   | -         | μs       | (Note 2)<br>All bits ON to OFF or<br>OFF to ON (Note 2) |

| Operating temperature range:<br>ZN428D and ZN428 E8<br>ZN428J8 | 0<br>-55 | -<br>- | 70<br>125 | °C<br>°C |                                                         |

| Supply voltage (V <sub>CC</sub> )                              | 4.5      | 5.0    | 5.5       | V        |                                                         |

| Supply current                                                 | -        | 20     | 30        | mA       | Note 3                                                  |

| Power consumption                                              | -        | 100    | -         | mW       |                                                         |

Note 1: See REFERENCE Note 2:  $R_L = 10M\Omega$ ,  $C_L = 10pF$ Note 3: All inputs HIGH ( $V_{IH} = 3.5V$ )

### **ELECTRICAL CHARACTERISTICS (cont.)**

| Parameter                                          | Min. | Тур. | Max.     | Units    | Conditions                                                       |

|----------------------------------------------------|------|------|----------|----------|------------------------------------------------------------------|

| Logic (over specified operating temperature range) |      |      |          |          |                                                                  |

| High level input voltage                           | 2.0  | -    | -        | V        |                                                                  |

| Low level input voltage                            | -    | -    | 0.8      | V        |                                                                  |

| High level input current                           | -    | -    | 60<br>20 | μA<br>μA | $V_{IN} = 5.5V, V_{CC} = Max.$<br>$V_{IN} = 2.4V, V_{CC} = Max.$ |

| Low level input current                            | -    | -    | -5       | μΑ       | $V_{IN} = 0.4V$ , $V_{CC} = Max$ .                               |

| Input clamp diode voltage                          | -    | -1.5 | -        | V        | I <sub>IN</sub> = -8mA                                           |

| Enable pulse width                                 | 100  | -    | -        | ns       |                                                                  |

| Data set-up time                                   | 150  | -    | -        | ns       | Note 4                                                           |

| Data hold time                                     | 10   | -    | -        | ns       | Note 5                                                           |

Note 4: Set up time before ENABLE goes high Note 5: Hold time after ENABLE goes high

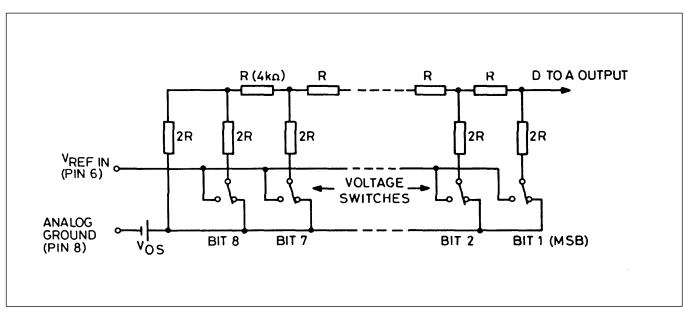

#### **D-A CONVERTER**

The converter is of the voltage switching type and uses an R-2R ladder network as shown in Fig.3. Each 2R element is connected to 0V or  $V_{\sf REF\ IN}$  by transistor voltage switches

specially designed for low offset voltage (<1mV). A binary weighted voltage is produced at the output of the R-2R ladder.

Fig.3 The R-2R ladder network

Analog output =

$$\frac{n}{256}$$

(V<sub>REF IN</sub> - V<sub>OS</sub>) + V<sub>OS</sub>

where n is the digital input to the D-A from the data latch.

${

m V}_{

m OS}$  is a small offset voltage produced by the D-A switch currents flowing through the package lead resistance. The

value of  $V_{OS}$  is typically 1mV. This offset will normally be removed by the setting up procedure (see Operating Notes) and because the offset temperature coefficient is low ( $\pm 6\mu V/^{\circ}C$ )the effect on accuracy is negligible.

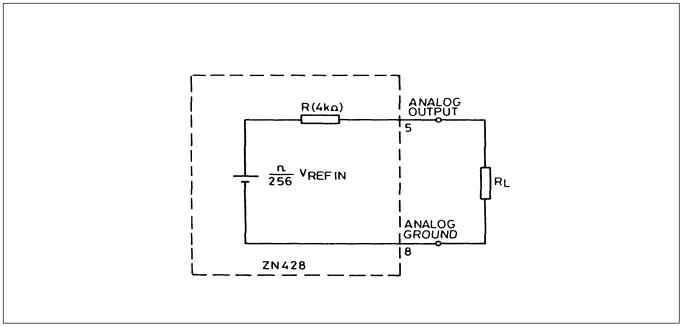

Fig.4 Analog output equivalent circuit

Fig.4 shows equivalent circuit of the output (ignoring  $V_{OS}$ ). The output resistance R has a temperature coefficient of +0.2% per  $^{\circ}$ C.

The gain drift due to this is  $\frac{0.2R}{R+R_1}$  % per °C.

$R_L$  should be chosen as large as possible to make the gain drift small. As an example if  $R_L=400 \mathrm{k}\Omega$  then the gain drift due to the T.C. of R for a  $100^\circ\mathrm{C}$  change in ambient temperature will be less than 0.2%. Alternatively the ZN428 can be buffered by an amplifier (see Operating Notes).

#### **REFERENCE**

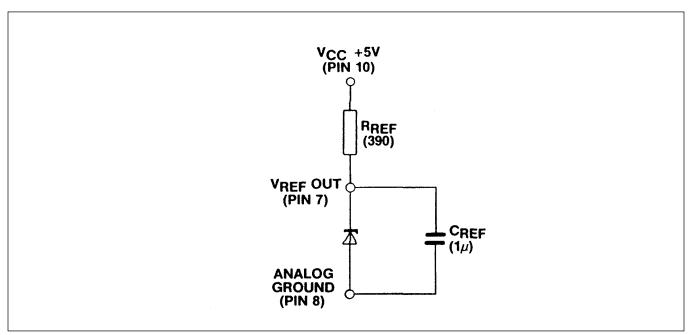

#### (a) Internal Reference

The internal reference is an active bandgap circuit which is equivalent to a 2.5V Zener diode with very low slope impedance (Fig.5). A resistor ( $R_{REF}$ ), should be connected between + $V_{CC}$  (pin 10) and pin 7. The recommended value of 390 $\Omega$  will supply a nominal reference current of (5.0-2.5)/0.39 = 6.4mA. A stabilising/decoupling capacitor  $C_{REF}$  = 1 $\mu$ F is required between pins 7 and 8 for internal reference option,  $V_{REF}$  (pin 7) being connected to  $V_{REF}$  (pin 6).

Fig.5 Internal voltage reference

Up to five ZN428s may be driven from one internal reference (there is no need to reduce  $R_{REF}$ ). This useful feature saves power and gives excellent gain tracking between the converters.

#### (b) External Reference

If required an external reference voltage may be connected to  $V_{REF\,IN}.$  The slope resistance of such a reference should be less than  $\frac{2.5}{n}\,\Omega,$  where n is the number of converters supplied.

$\rm V_{REF\ IN}$  can be varied from 0 to +3V for ratiometric operation. The ZN428 is guaranteed monotonic for  $\rm V_{REF\ IN}$  above 2V.

#### **LOGIC**

Input coding is binary for unipolar operation and offset binary for bipolar operation. When the ENABLE input is low the data inputs drive the D to A directly. When ENABLE goes high the input data word is held in the data latch.

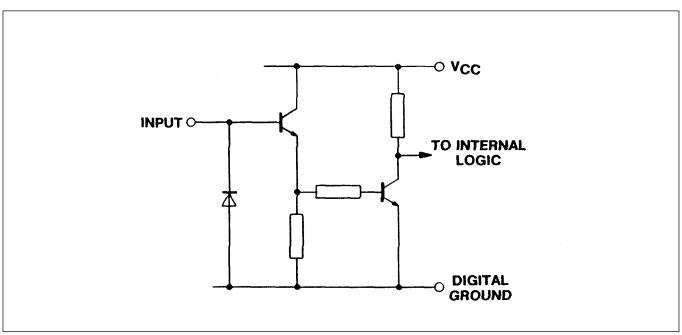

The equivalent circuit for the data and clock inputs is shown in Fig.6.

The ZN428 is provided with separate analog and digital ground connections. The circuit will operate correctly with as much as  $\pm 200 \, \text{mV}$  between the two grounds.

Fig.6 Equivalent circuit of all inputs

# **OPERATING NOTES**

## (1) Unipolar D-A Converter

The nominal output range of the ZN428 is 0 to  $V_{REF\ IN}$  through a  $4\Omega$  resistance. Other output ranges can readily be obtained by using an external amplifier.

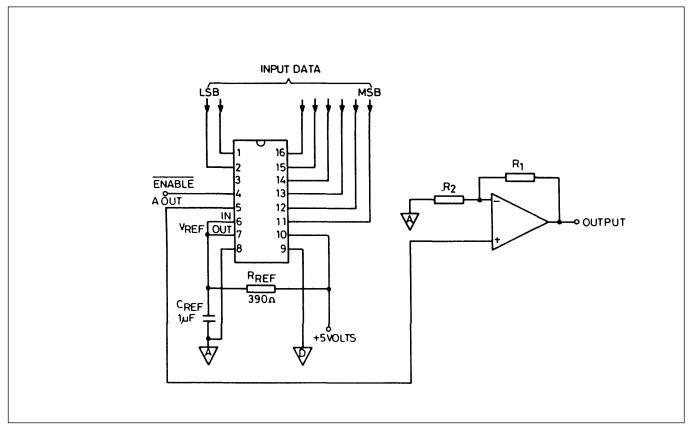

The general scheme (Fig.7) is suitable for amplifiers with input bias currents less than  $1.5\mu A$ .

The resulting full-scale range is given by:

$$V_{OUT}$$

FS =  $\left(\frac{1 + \frac{R1}{R2}}{R2}\right) V_{REF IN} = G.V_{REF IN}$

The impedance at the inverting input is R1//R2 and for low drift with temperature this parallel combination should be equal to the ladder resistance (4k $\Omega$ ). The required nominal values of R1 and R2 are given by R1 = 4Gk $\Omega$  and R<sub>2</sub> = 4G/(G-1)k $\Omega$ .

Using these relationships a table of nominal resistance values for  $R_1$  and  $R_2$  can be constructed for  $V_{REF\ IN} = 2.5V$ .

| Output Range | G | R <sub>1</sub> | R <sub>2</sub> |

|--------------|---|----------------|----------------|

| +5V          | 2 | 8kΩ            | 8kΩ            |

| +10V         | 4 | 16kΩ           | 5.33kΩ         |

For gain setting  $R_1$  is adjusted about its nominal value. Practical circuit realisations (including amplifier stabilising components) for +5 and +10V output ranges are given in Fig.8. Settling time for a major transition is 1.5 $\mu$ s typical.

Fig.7 Unipolar operation - basic circuit

Fig.8 Unipolar operation - component values

#### UNIPOLAR ADJUSTMENT PROCEDURE

(i) Set all bits to OFF (low) with  $\overline{\text{ENABLE}}$  low and adjust zero until V\_OUT = 0.0000V.

(ii) Set all bits ON (high) and adjust gain until  $V_{OUT} = FS$

#### **UNIPOLAR SETTING UP POINTS**

| Output Range, +FS | LSB     | FS - 1LSB |

|-------------------|---------|-----------|

| +5V               | 19.5 mV | 4.9805V   |

| +10V              | 39.1mV  | 9.9609V   |

#### **UNIPOLAR LOGIC CODING**

| Input Code<br>(Binary) | Analog Output<br>(Nominal Value)      |

|------------------------|---------------------------------------|

| 11111111               | FS - 1LSB                             |

| 11111110               | FS - 2 LSB                            |

| 11000000               | <sup>3</sup> / <sub>4</sub> FS        |

| 1000001                | <sup>1</sup> / <sub>2</sub> FS + 1LSB |

| 1000000                | $\frac{1}{2}$ FS                      |

| 01111111               | <sup>1</sup> / <sub>2</sub> FS - 1LSB |

| 01000000               | 1/ <sub>4</sub> FS                    |

| 0000001                | 1LSB                                  |

| 00000000               | 0                                     |

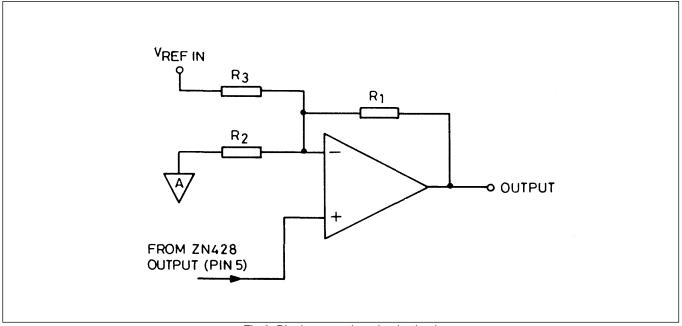

Fig.9 Bipolar operation - basic circuit

#### (2) Bipolar D-A Converter

For bipolar operation the output from the ZN428 is offset by half full-scale by connecting a resistor R3 between  $V_{REF}$  and the inverting input of the buffer amplifier (Fig.9).

When the digital input to the ZN428 is zero the analog output is zero and the amplifier output should be -Full-scale. An input of all ones to the D-A will give a ZN428 output of  $V_{REF\ IN}$  and the amplifier output required is +Full-scale. Also, to match the ladder resistance the parallel combination of  $R_1$ ,  $R_2$  and  $R_3$  should be  $4k\Omega$ .

The nominal values of  $R_1$ ,  $R_2$  and  $R_3$  which meet these conditions are given by

$R_1 = 8Gk\Omega$ ,  $R_2 = 8G/(G-1)k\Omega$  and  $R_3 = 8k\Omega$ .

where the resultant output range is  $\pm G \ V_{REF\ IN}$ . A bipolar output range of  $\pm V_{REF\ IN}$  (which corresponds to the basic unipolar range 0 to  $V_{REF\ IN}$ ) is obtained if  $R_1=R_3=8k\Omega$  and  $R_2=\infty$ .

Assuming that  $V_{REF\ IN}=2.5V$  the nominal values of resistors for  $\pm 5$  and  $\pm 10V$  output ranges are given in the following table:

| Output Range | G | R <sub>1</sub> | R <sub>2</sub> | R <sub>3</sub> |

|--------------|---|----------------|----------------|----------------|

| +5V          | 2 | 16kΩ           | 16kΩ           | 8kΩ            |

| +10V         | 4 | 32kΩ           | 10.66kΩ        | 8kΩ            |

Minus full scale (0ffset) is set by adjusting  $R_1$  about its nominal value relative to  $R_3$ . Plus full-scale (gain) is set by adjusting  $R_2$  relative to  $R_1$ .

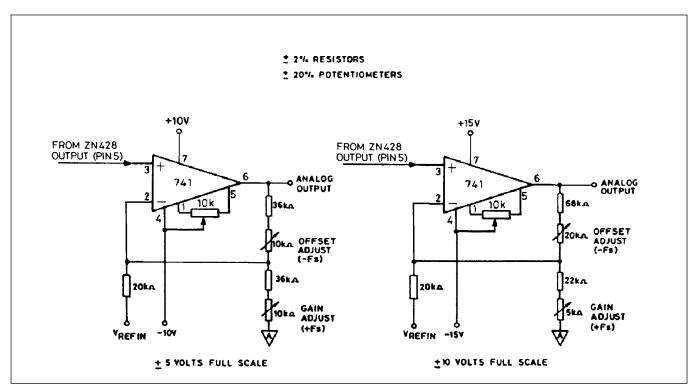

Practical circuit realisations are given in Fig.10.

Note that in the  $\pm 5\text{V}$  case R<sub>3</sub> has been chosen as  $7.5\text{k}\Omega$  (instead of  $8.2\text{k}\Omega$ ) to get a more symmetrical range of adjustment using standard potentiometers. Settling time for a major transition is  $1.5\mu\text{s}$  typical.

Fig.10 Bipolar operation - component values

#### **BIPOLAR ADJUSTMENT PROCEDURE**

- (i) Set all bits to OFF (low) with  $\overline{\text{ENABLE}}$  low and adjust offset until the amplifier output reads -full-scale.

- (ii) Set all bits ON (high) and adjust gain until the amplifier output reads +(full-scale 1LSB).

#### **BIPOLAR SETTING UP POINTS**

| Input Range,<br>± FS | LSB     | -FS       | +(FS -<br>1LSB) |

|----------------------|---------|-----------|-----------------|

| ±5V                  | 39.1 mV | -5.0000V  | +4.9609V        |

| ±10V                 | 78.1mV  | -10.0000V | 9.9219V         |

1LSB = <u>2FS</u>

#### **BIPOLAR LOGIC CODING**

| Input Code<br>(Offset Binary) | Analog Output<br>(Nominal Value) |

|-------------------------------|----------------------------------|

| 11111111                      | +(FS - 1LSB)                     |

| 11111110                      | +(FS - 2 LSB)                    |

| 11000000                      | + <sup>1</sup> / <sub>2</sub> FS |

| 10000001                      | + 1LSB                           |

| 10000000                      | 0                                |

| 01111111                      | -1 LSB                           |

| 01000000                      | -1/ <sub>2</sub> FS              |

| 0000001                       | -(FS - 1LSB)                     |

| 00000000                      | -FS                              |

HEADQUARTERS OPERATIONS

GEC PLESSEY SEMICONDUCTORS

Cheney Manor, Swindon, Wiltshire, United Kingdom. SN2 2QW Tel: (0793) 518000

Tel: (0793) 518000 Fax: (0793) 518411

#### **GEC PLESSEY SEMICONDUCTORS**

P.O. Box 660017, 1500 Green Hills Road, Scotts Valley, California 95067-0017, United States of America. Tel (408) 438 2900 Fax: (408) 438 5576 CUSTOMER SERVICE CENTRES

- FRANCE & BENELUX Les Ulis Cedex Tel: (1) 64 46 23 45 Fax: (1) 64 46 06 07

- GERMANY Munich Tel: (089) 3609 06-0 Fax: (089) 3609 06-55

- ITALY Milan Tel: (02) 66040867 Fax: (02)66040993

- JAPAN Tokyo Tel: (03) 5276-5501 Fax: (03) 5276-5510

- NORTH AMERICA Scotts Valley, USA Tel: (408) 438 2900 Fax: (408) 438 7023

- SOUTH EAST ASIA Singapore Tel: (65) 3827708 Fax: (65) 3828872

- SWEDEN Stockholm Tel: 46 8 702 97 70 Fax: 46 8 640 47 36

- TAIWAN, ROC Taipei Tel: 886 2 5461260 Fax: 886 2 7190260

- UK, EIRE, DENMARK, FINLAND & NORWAY

Swindon Tel: (0793) 518510 Fax: (0793) 518582

These are supported by Agents and Distributors in major countries world-wide.

© GEC Plessey Semiconductors 1994 Publication No. DS3007 Issue No. 2.1 August 1994

TECHNICAL DOCUMENTATION - NOT FOR RESALE. PRINTED IN UNITED KINGDOM