# **MP7524A**

**CMOS**

Buffered Multiplying 8-Bit Digital-to-Analog Converter

### **FEATURES**

- I<sub>OUT</sub> Pin Voltages are User Definable

- · Improved Isolation of Analog from Digital Ground

- · Full Four-Quadrant Multiplication

- · On-chip Bus Interface Logic

- +5 V to +15 V V<sub>DD</sub> Operation

- · Low Power Consumption

- Monotonicity Guaranteed (Full Temperature Range)

- · Use in Single Supply Design Designs

- 3 V Version: MP75L24

### **APPLICATIONS**

- · Microprocessor Controlled Gain Circuits

- Microprocessor Controlled Attenuator Circuits

- Microprocessor Controlled Function Generation

- · Precision AGC Circuits

- Bus Structured Instruments

- · Disk Drives

### **GENERAL DESCRIPTION**

The MP7524A is a low cost, 8-bit CMOS Digital-to-Analog Converter designed for direct interface to most microprocessors.

The MP7524A is pin-to-pin compatible to the MP7524. In addition, the  $I_{OUT1,\ 2}$  pins may be taken to a non-ground voltage. This allows its use in single supply circuits. The  $I_{OUT2}$  current is 1 LSB higher than that of the MP7524.

Basically an 8-bit DAC with input latches, the MP7524A's

load cycle is similar to the "write" cycle of a random access memory. Using an advanced thin-film on CMOS fabrication process, the MP7524A provides accuracy to 1/8 LSB with power dissipation of only 10mW.

Featuring operation from +5 V to +15 V, the MP7524A interfaces directly to most microprocessor buses or output ports. Excellent multiplying characteristics (2- or 4-quadrant) make the MP7524A an ideal choice for many microprocessor controlled gain setting and signal control applications.

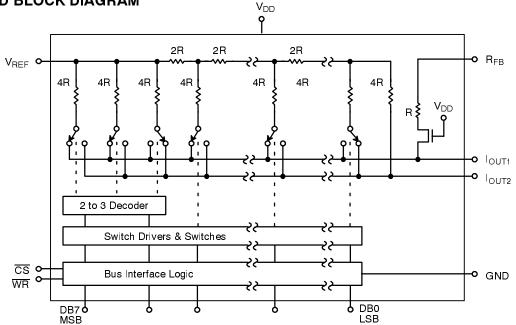

### SIMPLIFIED BLOCK DIAGRAM

3 Segment D/A Converter with Termination to I<sub>OUT2</sub> Logical "1" at Digital Input Steers Current to IOUT1

Rev. 3.00

©1998

### **ORDERING INFORMATION**

| Package<br>Type | Temperature<br>Range | Part No.  | INL<br>(LSB) | DNL<br>(LSB) | Gain Error<br>(% FSR) |

|-----------------|----------------------|-----------|--------------|--------------|-----------------------|

| Plastic Dip     | -40 to +85°C         | MP7524AAN | ±1/2         | ±1           | ±0.6                  |

| Plastic Dip     | -40 to +85°C         | MP7524ABN | ±1/4         | ±1           | ±0.6                  |

| Plastic Dip     | -40 to +85°C         | MP7524ACN | ±1/8         | ±1           | ±0.6                  |

| SOIC            | -40 to +85°C         | MP7524AAR | ±1/2         | ±1           | ±0.6                  |

| SOIC            | -40 to +85°C         | MP7524ABR | ±1/4         | ±1           | ±0.6                  |

| SOIC            | -40 to +85°C         | MP7524ACR | ±1/8         | ±1           | ±0.6                  |

### **PIN CONFIGURATIONS**

See Packaging Section for Package Dimensions

16 Pin PDIP (0.300")

16 Pin SOIC (Jedec, 0.150")

### **PIN OUT DEFINITIONS**

| PIN NO. | NAME              | DESCRIPTION            |

|---------|-------------------|------------------------|

| 1       | l <sub>OUT1</sub> | Current Output 1       |

| 2       | I <sub>OUT2</sub> | Current Output 2       |

| 3       | GND               | Ground                 |

| 4       | DB7               | Data Input Bit 7 (MSB) |

| 5       | DB6               | Data Input Bit 6       |

| 6       | DB5               | Data Input Bit 5       |

| 7       | DB4               | Data Input Bit 4       |

| 8       | DB3               | Data Input Bit 3       |

| PIN NO. | NAME          | DESCRIPTION            |  |  |  |

|---------|---------------|------------------------|--|--|--|

| 9       | DB2           | Data Input Bit 2       |  |  |  |

| 10      | DB1           | Data Input Bit 1       |  |  |  |

| 11      | DB0           | Data Input Bit 0 (LSB) |  |  |  |

| 12      | <del>CS</del> | Chip Select            |  |  |  |

| 13      | WR            | Write                  |  |  |  |

| 14      | $V_{DD}$      | Power Supply           |  |  |  |

| 15      | $V_{REF}$     | Reference Input        |  |  |  |

| 16      | $R_FB$        | Feedback Resistance    |  |  |  |

# **ELECTRICAL CHARACTERISTICS**

$(V_{DD} = + 5 V, V_{REF} = +10 V \text{ unless otherwise noted})$

| Parameter                                                                                                                   | Symbol                                                                           | Min  | 25°C<br>Typ Max      | Tmin to Tmax<br>Min Max   | Units                | Test Conditions/Comments                                                              |

|-----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|------|----------------------|---------------------------|----------------------|---------------------------------------------------------------------------------------|

| STATIC PERFORMANCE <sup>1</sup>                                                                                             |                                                                                  |      |                      |                           |                      | FSR = Full Scale Range                                                                |

| Resolution (All Grades)                                                                                                     | N                                                                                | 8    |                      | 8                         | Bits                 |                                                                                       |

| Integral Non-Linearity<br>(Relative Accuracy)<br>A<br>B<br>C                                                                | INL                                                                              |      | ±1/2<br>±1/2<br>±1/2 | ±1/2<br>±1/2<br>±1/2      | LSB                  | End Point Linearity                                                                   |

| Differential Non-Linearity A B C                                                                                            | DNL                                                                              |      | ±1<br>±1<br>±1       | ±1<br>±1<br>±1            | LSB                  | All grades monotonic over full temperature range.                                     |

| Gain Error                                                                                                                  | GE                                                                               |      | <u>+</u> 1.0         | <u>+</u> 1.4              | % FSR                | Using Internal R <sub>FB</sub><br>Digital Inputs = V <sub>INH</sub>                   |

| Power Supply Rejection Ratio                                                                                                | PSRR                                                                             |      | <u>+</u> 800         | <u>+</u> 1600             | ppm/%                | $ \Delta Gain/\Delta V_{DD}  \Delta V_{DD} = \pm 10\%$<br>Digital Inputs = $V_{INH}$  |

| Output Leakage Current (Pin 1)                                                                                              | l <sub>OUT1</sub>                                                                |      | <u>+</u> 50n A       | <u>+</u> 400nA            | nA                   | Digital Inputs = V <sub>INL</sub>                                                     |

| DYNAMIC PERFORMANCE                                                                                                         |                                                                                  |      |                      |                           |                      | RL = 100Ω, C <sub>L</sub> = 10pF                                                      |

| Current Settling Time <sup>2</sup> AC Feedthrough at I <sub>OUT1</sub> <sup>2</sup>                                         | t <sub>S</sub><br>F⊤                                                             |      | 100<br><u>+</u> 1/2  | 150<br><u>±</u> 1         | ns<br>LSB            | Full Scale Change to 1/2 LSB<br>V <sub>REF</sub> =100kHz, 20 Vp-p,<br>sinewave        |

| at I <sub>OUT2</sub>                                                                                                        |                                                                                  |      | <u>+</u> 1/2         | <u>+</u> 1                | LSB                  | DB0-DB7 = 0 V,                                                                        |

| REFERENCE INPUT                                                                                                             |                                                                                  |      |                      |                           |                      |                                                                                       |

| Input Resistance                                                                                                            | R <sub>IN</sub>                                                                  | 5    | 20                   | 5 20                      | kΩ                   |                                                                                       |

| DIGITAL INPUTS <sup>3</sup> Logical "1" Voltage  Logical "0" Voltage  Input Leakage Current  Input Capacitance <sup>2</sup> | V <sub>IH</sub><br>V <sub>IL</sub><br>LKG<br>C <sub>IN</sub>                     | +2.4 | +0.8<br>±1<br>20     | +2.4<br>+0.8<br>±10<br>20 | V<br>V<br>μΑ<br>pF   | V <sub>IN</sub> = 0 V                                                                 |

| ANALOG OUTPUTS <sup>2</sup>                                                                                                 |                                                                                  |      |                      |                           |                      |                                                                                       |

| Output Capacitance                                                                                                          | C <sub>OUT1</sub><br>C <sub>OUT1</sub><br>C <sub>OUT2</sub><br>C <sub>OUT2</sub> |      | 70<br>30<br>20<br>60 | 70<br>30<br>20<br>60      | pF<br>pF<br>pF<br>pF | DAC inputs all 1's<br>DAC inputs all 0's<br>DAC inputs all 1's<br>DAC inputs all 0's  |

| POWER SUPPLY <sup>5</sup>                                                                                                   |                                                                                  |      |                      |                           |                      |                                                                                       |

| Supply Current                                                                                                              | l <sub>DD</sub>                                                                  |      | 1 2<br>1 2           | 2                         | mA<br>mA             | All digital inputs = 0 V or all = 5 V All digital inputs = $V_{IL}$ or all = $V_{IH}$ |

# **ELECTRICAL CHARACTERISTICS (CONT'D)**

| Parameter                                                                                                                                                                               | Symbol                                                                                      | Min                          | 25° C<br>Typ | Max | Tmin to<br>Min               | Tmax<br>Max | Units                | Test Conditions/Comments                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|------------------------------|--------------|-----|------------------------------|-------------|----------------------|------------------------------------------------------|

| SWITCHING<br>CHARACTERISTICS <sup>2, 4</sup>                                                                                                                                            |                                                                                             |                              |              |     |                              |             |                      |                                                      |

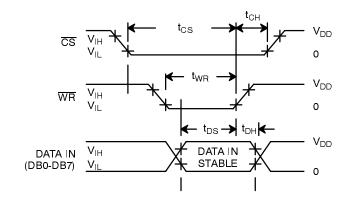

| Chip Select to Write Set-Up Time Chip Select to Write Hold Time Data Valid to Write Set-Up Time Data Valid to Write Hold Time Write Pulse Width  VOLTAGE MODE OPERATION <sup>2, 6</sup> | t <sub>CS</sub><br>t <sub>CH</sub><br>t <sub>DS</sub><br>t <sub>DH</sub><br>t <sub>WR</sub> | 170<br>0<br>135<br>10<br>170 |              |     | 220<br>0<br>170<br>10<br>220 |             | ns<br>ns<br>ns<br>ns |                                                      |

| Integral Nonlinearity Error @ V <sub>REF</sub>                                                                                                                                          | NL                                                                                          |                              |              | 1   |                              |             | LSB                  | I <sub>OUT1</sub> = 1.5 V<br>I <sub>OUT2</sub> = 0 V |

#### NOTES:

- <sup>1</sup> Full Scale Range (FSR) is 10V for unipolar mode and  $\pm$ 10V for bipolar.

- Guaranteed but not production tested.

- Digital input levels should not go below ground or exceed the positive supply voltage, otherwise damage may occur.

- See timing diagram.

- Specified values guarantee functionality. Refer to other parameters for accuracy.

- 6 Refer to Figure 7.

Specifications are subject to change without notice

# **ELECTRICAL CHARACTERISTICS**

(VDD = + 15 V, VREF = +10 V unless otherwise noted)

| Param et er                                                                                              | Symbol                                                                           | Min   | 25°C<br>Typ Max                      | Tmin to Tm<br>Min M | ax<br>lax                                    | Units                | Test Conditions/Comments                                                                                                     |

|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|-------|--------------------------------------|---------------------|----------------------------------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------|

| STATIC PERFORMANCE <sup>1</sup>                                                                          |                                                                                  |       |                                      |                     |                                              |                      | FSR = Full Scale Range                                                                                                       |

| Resolution (All Grades)                                                                                  | N                                                                                | 8     |                                      | 8                   |                                              | Bits                 |                                                                                                                              |

| Integral Non-Linearity<br>(Relative Accuracy)<br>A<br>B<br>C                                             | INL                                                                              |       | ±1/2<br>±1/4<br>±1/8                 | <u>±</u>            | <u>+</u> 1/2<br><u>+</u> 1/4<br><u>+</u> 1/8 | LSB                  | End Point Linearity                                                                                                          |

| Differential Non-Linearity<br>A<br>B<br>C                                                                | DNL                                                                              |       | ±1<br>±1<br>±1                       |                     | ±1<br>±1<br>±1                               | LSB                  | All grades monotonic over full temperature range.                                                                            |

| Gain Error                                                                                               | GE                                                                               |       | <u>+</u> 0.5                         | <u>+</u>            | <u>+</u> 0.6                                 | % FSR                | Using Internal R <sub>FB</sub><br>Digital Inputs = V <sub>INH</sub>                                                          |

| Power Supply Rejection Ratio                                                                             | PSRR                                                                             |       | <u>+</u> 200                         | ±                   | 400                                          | ppm/%                | $ \Delta Gain/\Delta V_{DD}  \Delta V_{DD} = \pm 10\%$<br>Digital Inputs = $V_{INH}$                                         |

| Output Leakage Current (Pin 1)                                                                           | l <sub>OUT1</sub>                                                                |       | <u>+</u> 50nA                        | <u>+</u> 400        | 0n A                                         | nA                   | Digital Inputs = V <sub>INL</sub>                                                                                            |

| DYNAMIC PERFORMANCE                                                                                      |                                                                                  |       |                                      |                     |                                              |                      | RL=100Ω, CL=13pF                                                                                                             |

| Current Settling Time <sup>2</sup> AC Feedthrough at I <sub>OUT1</sub> <sup>2</sup> at I <sub>OUT2</sub> | t <sub>S</sub><br>FT                                                             |       | 50<br><u>±</u> 0.50<br><u>±</u> 0.50 | <u>±</u> 1          | 100<br>1.00<br>1.00                          | ns<br>LSB<br>LSB     | Full Scale Change to $1/2$ LSB $V_{REF}$ = 10kHz, 20 Vp-p, sinewave DB0 - DB7 = 0 V, $\overline{CS}$ = $\overline{WR}$ = 0 V |

| REFERENCE INPUT                                                                                          |                                                                                  |       |                                      |                     |                                              |                      |                                                                                                                              |

| Input Resistance                                                                                         | R <sub>IN</sub>                                                                  | 5     | 20                                   | 5                   | 20                                           | kΩ                   |                                                                                                                              |

| DIGITAL INPUTS <sup>3</sup>                                                                              |                                                                                  |       |                                      |                     |                                              |                      |                                                                                                                              |

| Logical "1" Voltage<br>Logical "0" Voltage<br>Input Leakage Current<br>Input Capacitance <sup>2</sup>    | V <sub>IH</sub><br>V <sub>IL</sub><br>I <sub>LKG</sub><br>C <sub>IN</sub>        | +13.5 | +1.5<br><u>+</u> 1<br>20             |                     | +1.5<br><u>+</u> 10<br>20                    | V<br>V<br>μΑ<br>pF   |                                                                                                                              |

| ANALOG OUTPUTS <sup>2</sup>                                                                              |                                                                                  |       |                                      |                     |                                              |                      |                                                                                                                              |

| Output Capacitance                                                                                       | C <sub>OUT1</sub><br>C <sub>OUT1</sub><br>C <sub>OUT2</sub><br>C <sub>OUT2</sub> |       | 70<br>30<br>20<br>60                 |                     | 70<br>30<br>20<br>60                         | pF<br>pF<br>pF<br>pF | DAC inputs all 1's<br>DAC inputs all 0's<br>DAC inputs all 1's<br>DAC inputs all 0's                                         |

| POWER SUPPLY                                                                                             |                                                                                  |       |                                      |                     |                                              |                      |                                                                                                                              |

| Supply Current                                                                                           | <sub>DD</sub>                                                                    |       | 1 2<br>1 2                           |                     | 2<br>2                                       | mA<br>mA             | All digital inputs = 0 V or all = 15 V All digital inputs = $V_{IL}$ or all = $V_{IH}$                                       |

### **ELECTRICAL CHARACTERISTICS (CONT'D)**

| Parameter                                                                                                                                       | Symbol                                                                                      | Min                         | 25°C<br>Typ | Мах | Tmin to<br>Min              | Tmax<br>Max | Units                | Test Conditions/Comments                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-----------------------------|-------------|-----|-----------------------------|-------------|----------------------|------------------------------------------------|

| SWITCHING<br>CHARACTERISTICS <sup>2, 4</sup>                                                                                                    |                                                                                             |                             |             |     |                             |             |                      |                                                |

| Chip Select to Write Set-Up Time Chip Select to Write Hold Time Data Valid to Write Set-Up Time Data Valid to Write Hold Time Write Pulse Width | t <sub>CS</sub><br>t <sub>CH</sub><br>t <sub>DS</sub><br>t <sub>DH</sub><br>t <sub>WR</sub> | 100<br>0<br>60<br>10<br>100 |             |     | 130<br>0<br>80<br>10<br>130 |             | ns<br>ns<br>ns<br>ns |                                                |

| VOLTAGE MODE OPERATION <sup>2, 6</sup> Integral Nonlinearity Error @ V <sub>REF</sub>                                                           | INL                                                                                         |                             |             | 1   |                             |             | LSB                  | <sub>OUT1</sub> = 3V<br>  <sub>OUT2</sub> = 0V |

#### NOTES:

- <sup>1</sup> Full Scale Range (FSR) is 10V for unipolar mode and  $\pm$ 10V for bipolar.

- Guaranteed but not production tested.

- Digital input levels should not go below ground or exceed the positive supply voltage, otherwise damage may occur.

- See timing diagram.

- <sup>5</sup> Specified values guarantee functionality. Refer to other parameters for accuracy.

- 6 Refer to Figure 7.

Specifications are subject to change without notice

## ABSOLUTE MAXIMUM RATINGS (TA = +25°C unless otherwise noted)<sup>1, 2</sup>

| V <sub>DD</sub> to GND                                       | Storage Temperature65°C to +150°C               |

|--------------------------------------------------------------|-------------------------------------------------|

| Digital Input Voltage to GND (2) GND –0.5 to $V_{DD}$ +0.5 V | Lead Temperature (Soldering, 10 seconds) +300°C |

| <sub>OUT1</sub> ,   <sub>OUT2</sub> to GND –0.5 to 7 V       | Package Power Dissipation Rating to 75°C        |

| V <sub>REF</sub> to GND                                      | PDIP, SOIC                                      |

| V <sub>RFB</sub> to GND                                      | Derates above 75°C                              |

#### NOTES:

- Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation at or above this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

- <sup>2</sup> Any input pin which can see a value outside the absolute maximum ratings should be protected by Schottky diode clamps (HP5082-2835) from input pin to the supplies.

#### **APPLICATION NOTES**

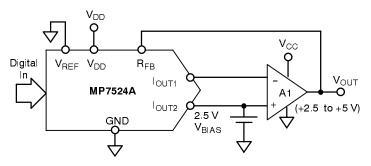

Figure 1. Single Supply Operation with 2.5 V to 5 V Swing

The R-2R ladder termination resistor on the MP7524A is internally connected to  $l_{OUT2}$  instead of ground as in the MP7524. This configuration allows the use of the DAC in the single supply current steering mode, where  $l_{OUT2}$  is biased above ground level.

Figure 2. shows the generalized configuration.

Figure 2. Single Supply Operation in Current Switching Mode

The advantage of this single supply configuration over the voltage switching mode is the greater flexibility with which the

output voltage swing can be defined. A low impedance reference bias voltage is needed. Unlike the voltage switching mode which has a minimum output voltage of 0V, the current steering mode allows for output swings that do not have to approach the rail voltages. The describing equation for this configuration is:

$$V_{OUT} = \frac{D}{256} (V_{BIAS} - V_{IN}) + V_{BIAS}$$

where D=decimal equivalent of the DAC digital input code  $V_{B|AS}$  is a voltage reference: 0 V  $\leq$   $V_{B|AS} \leq$  2.5V for best linearity.

V<sub>IN</sub> is a bipolar input voltage

By choosing the proper  $V_{B|AS}$  and  $V_{IN}$ , the output voltage can be set in the range between  $V_{B|AS}$  and  $2V_{B|AS} - V_{IN}$ . For example, for  $V_{DD} = 5$  V &  $V_{CC} = 15$  V, select  $V_{IN} = 0$  V and  $V_{B|AS} = 2.5$  V. This will result in a swing of 2.5 V to 5 V.

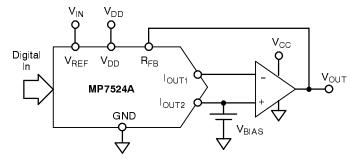

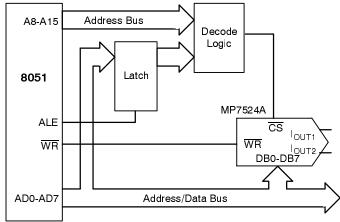

Figure 3. Microcontroller Interface

#### INTERFACE LOGIC INFORMATION

#### **Mode Selection**

MP7524A mode selection is controlled by the  $\overline{\text{CS}}$  and  $\overline{\text{WR}}$  inputs.

#### Write Mode

When  $\overline{\text{CS}}$  and  $\overline{\text{WR}}$  are both LOW, the MP7524A is in the WRITE mode, and the MP7524A analog circuit responds to data activity at the DB0-DB7 data bus inputs. In this mode, the MP7524A acts like a non-latched input D/A converter.

#### **Hold Mode**

When either  $\overline{\text{CS}}$  or  $\overline{\text{WR}}$  is HIGH, the MP7524A is in the HOLD mode. The MP7524A analog output holds the value corresponding to the last digital input present at DB0-DB7 prior to  $\overline{\text{WR}}$  or  $\overline{\text{CS}}$  assuming the high state.

| CS | WR | Mode  | DAC Response                                                 |

|----|----|-------|--------------------------------------------------------------|

| L  | L  | Write | DAC responds to data bus<br>(DB0-DB7) inputs                 |

| Н  | Х  | Hold  | Data Bus (DB0-DB7) is<br>locked out                          |

| Х  | Ι  | Hold  | DAC holds last data present<br>when WR assumed HIGH<br>state |

L = LOW state, H = HIGH state, X = Don't care state

Table 1. Mode Selection Table

Figure 4. Write Cycle Timing Diagram

#### MICROPROCESSOR INTERFACE

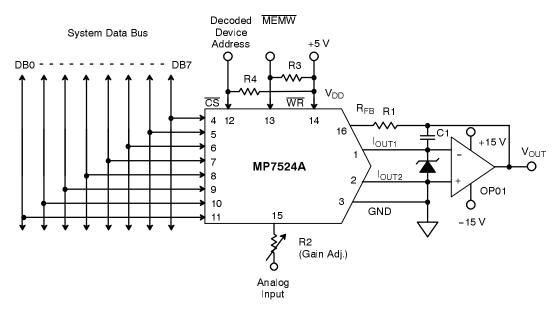

#### MP7524A/8080A Interface

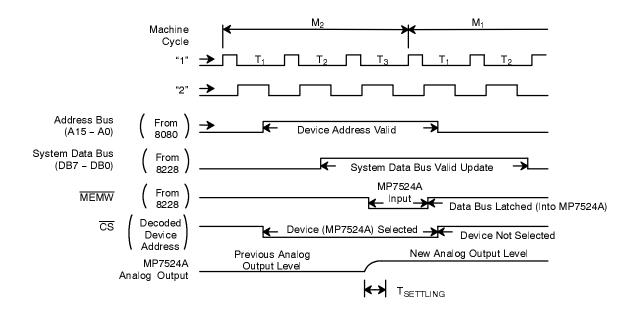

Figure 5. shows the MP7524A used in the MCS-80 microcomputer system as a Memory Mapped Output Device. The basic CPU group consists of the 8080A CPU, 8224 clock generator and 8228 system controller/bus driver. The MP7524A  $\overline{\rm WR}$  input is connected to the 8228 system data bus outputs. The  $\overline{\rm CS}$  input is connected to the system address decoding logic. Note that pull-up resistors R3 and R4 are required to ensure that the  $\overline{\rm CS}$  and  $\overline{\rm WR}$  input HIGH states reach 3.0V min. Pull-ups are not required on the system data bus since the 8228 VOH is 3.6 V min for DB0-DB7.

System timing is shown in Figure 6. Data is loaded into the MP7524A when the  $\overline{WR}$  and  $\overline{CS}$  inputs are both LOW. The data is latched into the MP7524A when  $\overline{WR}$  returns HIGH. MP7524A updating is accomplished by using any of the 8080A memory write instructions.

The MP7524A can also be addressed and loaded as an isolated Output Device by connecting the MP7524A  $\overline{WR}$  input to the 8228  $\overline{I/O}$  W terminal (instead of  $\overline{MEMW}$ ).

Figure 5. MP7524A/8080A Interface

Figure 6. Timing Diagram

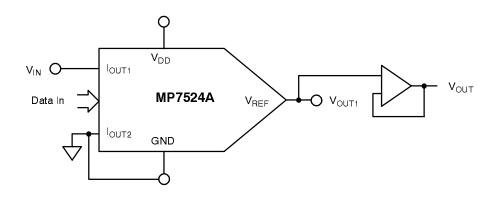

Figure 7. Voltage Mode Operation