## MIC4467/4468/4469

#### Quad 1.2A-Peak Low-Side MOSFET Driver

#### **Bipolar/CMOS/DMOS**

#### **General Description**

The MIC4467/8/9 family of 4-output CMOS buffer/drivers is an expansion from the earlier single- and dual-output drivers, to which they are functionally closely related. Because package pin count permitted it, each driver has been equipped with a 2-input logic gate for added flexibility. Placing four highpower drivers in a single package also improves system reliability and reduces total system cost. In some applications, one of these drivers can replace not only two packages of single-input drivers, but some of the associated logic as well.

Although primarily intended for driving power MOSFETs, and similar highly capacitive loads, these drivers are equally well suited to driving any other load (capacitive, resistive, or inductive), which requires a high-efficiency, low-impedance driver capable of high peak currents, rail-to-rail voltage swings, and fast switching times. For example, heavily loaded clock lines, coaxial cables, and piezoelectric transducers can all be

#### **Features**

- Built using reliable, low power CMOS processes

- Latchproof. Withstands 500mA Inductive Kickback

- 3 Input Logic Choices

- Short, Equal Delay Times ...... 75ns

- High Peak Output Current ......1.2A

- Wide Operating Range .......4.5 to 18V

- Low Equivalent Input Capacitance (typ) ...... 6pF

- Inputs = Logic 1 for Any Input From 2.4V to V<sub>S</sub>

- **ESD Protected**

## **Applications**

- General-Purpose CMOS Logic Buffer

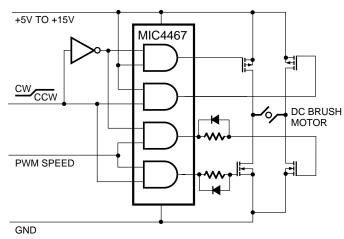

- Driving All 4 MOSFETs in an H-Bridge

- **Direct Small-Motor Driver**

- Relay or Peripheral Drivers

- **Dual Differential Output Power Drivers**

- **CCD** Driver

- Pin-Switching Network Driver

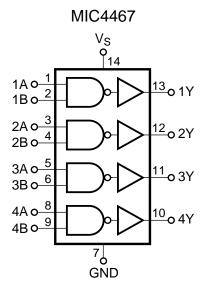

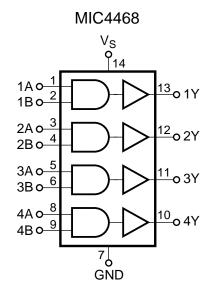

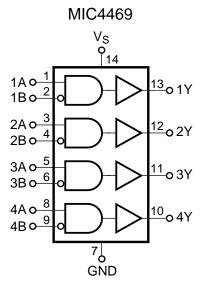

# **Logic Diagrams**

driven easily with MIC446X series drivers. The only limitation on loading is that total power dissipation in the IC must be kept within the power dissipation limits of the package.

The MIC446X series drivers are built using a BCD process. They will not latch under any conditions within their power and voltage ratings. They are not subject to damage when up to 5V of noise spiking (either polarity) occurs on the ground line. They can accept up to half an amp of inductive kickback current (either polarity) into their outputs without damage or logic upset.

# **Ordering Information**

| Part No.    | Package            | Temp. Range   |

|-------------|--------------------|---------------|

| MIC44xxCN*  | 14-Pin Plastic DIP | 0° to +70°C   |

| MIC44xxCWM* | 16-Pin Wide SOIC   | 0° to +70°C   |

| MIC44xxBN*  | 14-Pin Plastic DIP | –40° to +85°C |

| MIC44xxBWM* | 16-Pin Wide SOIC   | −40° to +85°C |

<sup>\*</sup> xx identifies input logic: 67 — NAND

68 — AND 69 — AND with 1 inverting input

## **Truth Table**

| Part No.                 | Inp<br>A    | uts<br>B    | Output<br>Y |

|--------------------------|-------------|-------------|-------------|

| MIC4467<br>(Each Driver) | L<br>X<br>H | X<br>L<br>H | H<br>H<br>L |

| MIC4468<br>(Each Driver) | H<br>L<br>X | H<br>X<br>L | H<br>L<br>L |

| MIC4469<br>(Each Driver) | L<br>X<br>H | X<br>H<br>L | L<br>L<br>H |

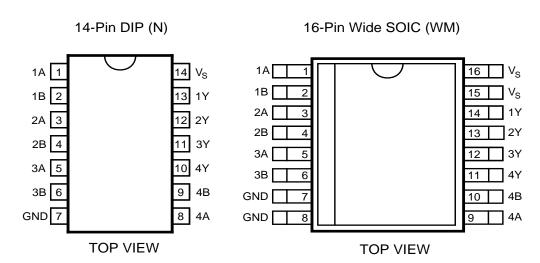

# **Pin Configurations**

**April 1998** 5-81

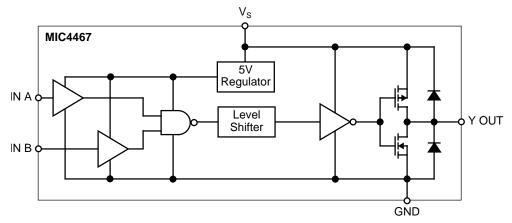

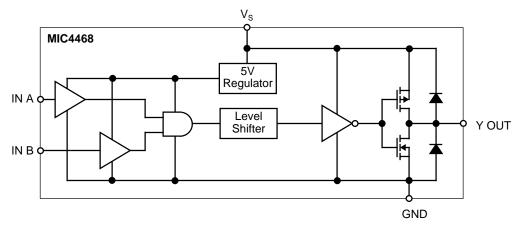

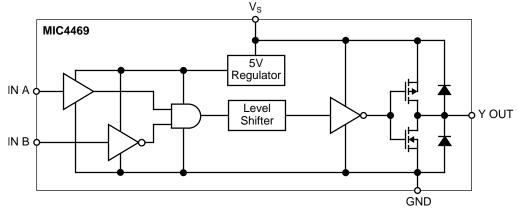

# **Block Diagrams**

Functional Diagram for One Driver (Four Drivers per Package-Ground Unused Inputs)

Functional Diagram for One Driver (Four Drivers per Package-Ground Unused Inputs)

Functional Diagram for One Driver (Four Drivers per Package-Ground Unused Inputs)

5-82 April 1998

### Absolute Maximum Ratings (Notes 1 and 2)

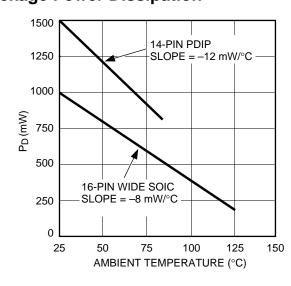

Supply Voltage **Power Dissipation**

Input Voltage (GND - 5V) to  $(V_S + 0.3V)$ N Package (14-Pin Plastic DIP)

Maximum Chip Temperature

Operating 150°C

Storage -65° to +150°C

Maximum Load Temperature

(10 sec, for soldering) 300°C

**Operating Ambient Temperature**

C Version 0° to +70°C **B** Version -40° to +85°C

1.5W WM Package (16-Pin Wide SOIC) 1W

Package Thermal Resistance

N Package (14-Pin Plastic DIP)  $\theta_{JA}$ 80°C/W WM Package (16-Pin Wide SOIC) θ<sub>JA</sub> 120°C/W

**Electrical Characteristics:** Measured at  $T_A = 25^{\circ}C$  with  $4.5V \le V_S \le 18V$  unless otherwise specified.

| Symbol          | Parameter                                        | Conditions                                    | Min                  | Тур | Max  | Units |

|-----------------|--------------------------------------------------|-----------------------------------------------|----------------------|-----|------|-------|

| INPUT           |                                                  |                                               | -                    |     | •    |       |

| $V_{IH}$        | Logic 1 Input Voltage                            |                                               | 2.4                  | 1.3 |      | V     |

| V <sub>IL</sub> | Logic 0 Input Voltage                            |                                               |                      | 1.2 | 0.8  | V     |

| I <sub>IN</sub> | Input Current                                    | $0 \le V_{IN} \le V_{S}$                      | -1                   |     | 1    | μА    |

| OUTPUT          |                                                  |                                               |                      |     |      |       |

| V <sub>OH</sub> | High Output Voltage                              | I <sub>LOAD</sub> = 10mA                      | V <sub>S</sub> -0.15 |     |      | V     |

| V <sub>OL</sub> | Low Output Voltage                               | I <sub>LOAD</sub> = 10mA                      |                      |     | 0.15 | V     |

| R <sub>O</sub>  | Output Resistance                                | I <sub>OUT</sub> = 10mA, V <sub>S</sub> = 18V |                      | 5   | 15   | Ω     |

| I <sub>PK</sub> | Peak Output Current                              |                                               |                      | 1.2 |      | А     |

| I               | Latch-Up Protection<br>Withstand Reverse Current |                                               | >500                 |     |      | mA    |

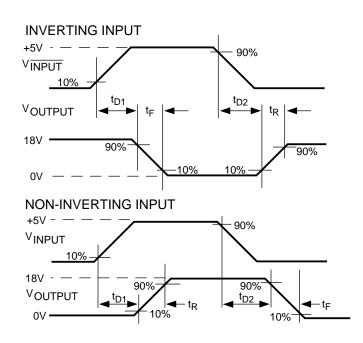

| SWITCHIN        | IG TIME                                          |                                               |                      |     |      |       |

| t <sub>R</sub>  | Rise Time                                        | Test Figure 1                                 |                      | 14  | 25   | ns    |

| t <sub>F</sub>  | Fall Time                                        | Test Figure 1                                 |                      | 13  | 25   | ns    |

| t <sub>D1</sub> | Delay Time                                       | Test Figure 1                                 |                      | 30  | 75   | ns    |

| t <sub>D2</sub> | Delay Time                                       | Test Figure 1                                 |                      | 45  | 75   | ns    |

| POWER S         | UPPLY                                            |                                               |                      |     |      |       |

| I <sub>S</sub>  | Power Supply Current<br>Supply                   |                                               |                      | 0.2 | 4    | mA    |

**April 1998** 5-83

## **Electrical Characteristics:**

Measured over operating temperature range with 4.5V  $\leq$  V  $_{\mbox{\scriptsize S}} \leq$  18V unless otherwise specified.

| Symbol          | Parameter                                        | Conditions                                     | Min                 | Тур | Max | Units |

|-----------------|--------------------------------------------------|------------------------------------------------|---------------------|-----|-----|-------|

| INPUT           |                                                  | •                                              | •                   | •   |     | •     |

| $V_{IH}$        | Logic 1 Input Voltage                            |                                                | 2.4                 | 1.4 |     | V     |

| V <sub>IL</sub> | Logic 0 Input Voltage                            |                                                |                     | 1.0 | 0.8 | V     |

| I <sub>IN</sub> | Input Current                                    | $0 \le V_{IN} \le V_{S}$                       | -1                  |     | 1   | μΑ    |

| OUTPUT          |                                                  |                                                |                     |     |     |       |

| V <sub>OH</sub> | High Output Voltage                              | I <sub>LOAD</sub> = 10 mA                      | V <sub>S</sub> -0.3 |     |     | V     |

| V <sub>OL</sub> | Low Output Voltage                               | I <sub>LOAD</sub> = 10 mA                      |                     |     | 0.3 | V     |

| R <sub>O</sub>  | Output Resistance                                | I <sub>OUT</sub> = 10 mA, V <sub>S</sub> = 18V |                     | 7   | 30  | Ω     |

| I <sub>PK</sub> | Peak Output Current                              |                                                |                     | 1.2 |     | Α     |

| 1               | Latch-Up Protection<br>Withstand Reverse Current |                                                | 500                 |     |     | mA    |

| SWITCHIN        | NG TIME                                          |                                                |                     |     | -   |       |

| t <sub>R</sub>  | Rise Time                                        | Test Figure 1                                  |                     | 17  | 50  | ns    |

| t <sub>F</sub>  | Fall Time                                        | Test Figure 1                                  |                     | 16  | 50  | ns    |

| t <sub>D1</sub> | Delay Time                                       | Test Figure 1                                  |                     | 35  | 100 | ns    |

| t <sub>D2</sub> | Delay Time                                       | Test Figure 1                                  |                     | 55  | 100 | ns    |

| POWER S         | UPPLY                                            |                                                | •                   |     |     |       |

| I <sub>S</sub>  | Power Supply Current<br>Supply                   |                                                |                     | 0.4 | 8   | mA    |

**NOTE 1:** Functional operation above the absolute maximum stress ratings is not implied.

**NOTE 2:** Static sensitive device. Store only in conductive containers. Handling personnel and equipment should be grounded to prevent static damage.

5-84 April 1998

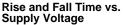

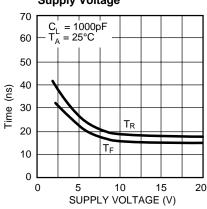

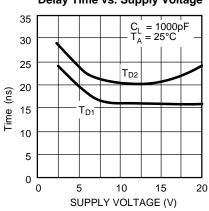

# **Typical Characteristics**

Delay Time vs. Supply Voltage

Rise and Fall Time vs. Temperature

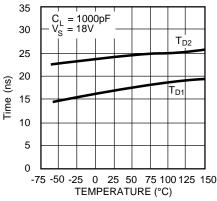

**Delay Time vs. Temperature**

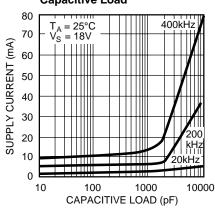

Supply Current vs. Capacitive Load

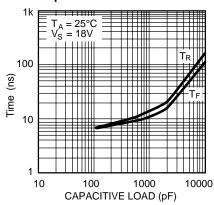

Rise and Fall Time vs. Capacitive Load

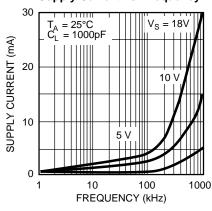

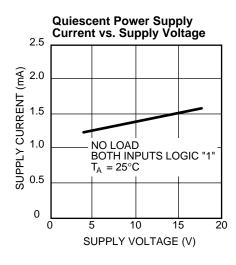

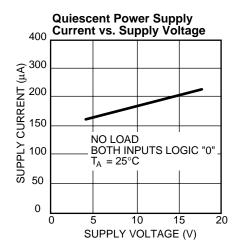

Supply Current vs. Frequency

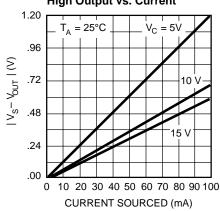

High Output vs. Current

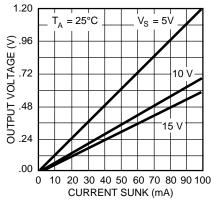

Low Output vs. Current

April 1998 5-85

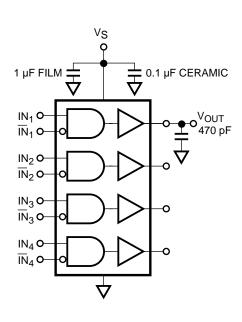

# **Test Figure 1**

# **Package Power Dissipation**

# **Quad Driver Drives H Bridge to Control Motor Speed and Direction**