## 8-CH 10-BIT A/D **CONVERTER(ADC)**

## **MB4051**

July 1989 Edition 1.0

#### 8-CHANNEL 10-BIT A/D CONVERTER

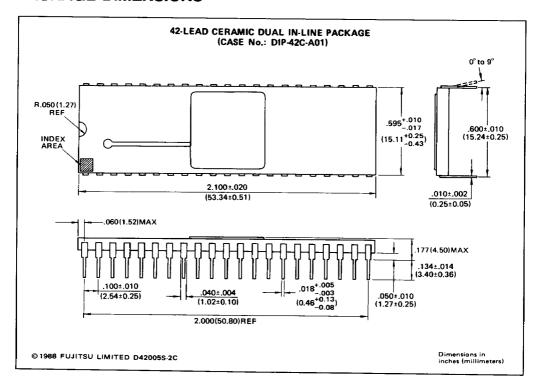

The Fujitsu MB4051 is a general purpose analog-to-digital converter (ADC) which features eight channels of analog inputs, 10-bit parallel data I/O port and programmable control register. Analog input signal on a selected input channel is converted to 10-bit digital data by the successive-approximation technique which provides high-speed conversion. The MB4051 is packaged in a standard 42-pin dual in-line packages.

- Multiplex 8-channel Analog Inouts

- Resolution: 10 bits

- Relative Accuracy: 8 bits Min.

- Linearity: ±1/2 LSB

- Successive-Approximation Technique: 50  $\mu$ s/ch Max. at f<sub>CLK</sub> = 250kHz

- Analog input Voltage Range: 0V to 6.5V

- Analog Input Bias Current: 1μA Max.

- Input Impedance: over 500kΩ (for 6.5V Input)

- Built-in High Stabilized Reference Voltage Source

- Directly Connectable to DMA Controller as well as Microprocessor

- TTL Compatible Digital I/O Port

- Standard 42-pin DIP

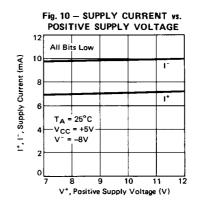

- Power Supplies: +5V and ±8V

- Power Consumption: 400mW Typ.

## Symbol Value Unit Parameter

| Supply Voltage   | 1                     | V <sub>cc</sub>  | +7                     | ٧           |  |

|------------------|-----------------------|------------------|------------------------|-------------|--|

| Supply Voltage   | 2                     | V <sup>+</sup>   | +10                    | ٧           |  |

| Supply Voltage   | 3                     | V-               | -10                    | <b>&gt;</b> |  |

| Digital Input Vo | Digital Input Voltage |                  | -0.5 to +5.5           | ٧           |  |

| Analog Input V   | oltage                | VIA              | -3.0 to V <sup>+</sup> | ٧           |  |

| Operating Temp   | erature               | TA               | -35 to +90             | °c          |  |

| Storage          | Ceramic               | +                | -55 to +150            | °c          |  |

| Temperature      | Plastic               | T <sub>STG</sub> | -40 to +125            | C           |  |

ABSOLUTE MAXIMUM RATINGS (All Voltage referenced to A.G/D.G)

NOTE: Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to the conditions as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| ı |                                            |                                                        |                                                                                                           | •                                                        |

|---|--------------------------------------------|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

|   |                                            | (ТОР                                                   | VIEW)                                                                                                     |                                                          |

|   | DEC COMP COMP COMP COMP COMP COMP COMP COM | 1 2 2 3 4 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 | 42<br>411<br>40<br>39<br>38<br>37<br>36<br>35<br>34<br>33<br>32<br>29<br>28<br>27<br>26<br>25<br>24<br>23 | Reset  RA  RA  REN  DES  DES  DES  DES  DES  DES  DES  D |

|   |                                            |                                                        |                                                                                                           |                                                          |

PIN ASSIGNMENT

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields. However, it is advised that normal precautions be taken to avoid application of any voltage higher than maxi-mum rated voltages to this high impedance circuit.

## **RECOMMENDED OPERATING CONDITIONS**

| Parameter                   | Sh - I          |      | 11.5 |      |      |

|-----------------------------|-----------------|------|------|------|------|

|                             | Symbol          | Min  | Тур  | Max  | Unit |

| Supply Voltage 1            | V <sub>cc</sub> | 4.75 | 5.0  | 5.25 | v    |

| Supply Voltage 2            | V <sup>+</sup>  | 7.6  | 8.0  | 8.4  | v    |

| Supply Voltage 3            | V-              | -8.4 | -8.0 | -7.6 | v    |

| Digital Output High Current | I <sub>OH</sub> |      |      | -0.4 | mA   |

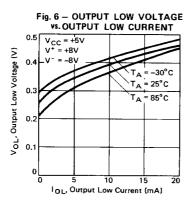

| Digital Output Low Current  | I <sub>OL</sub> |      |      | 8    | mA   |

| Operating Temperature       | T <sub>OP</sub> | -30  |      | +85  | °c   |

NOTE: The negative value means "flow of current" from IC to out side of IC.

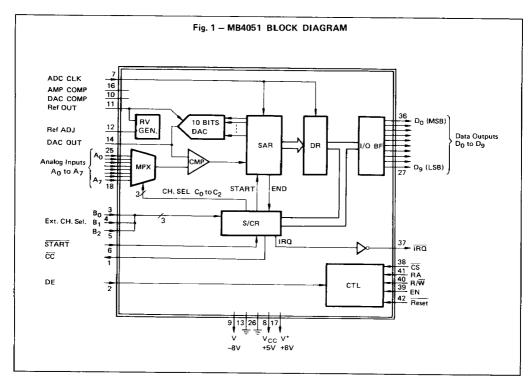

## FUNCTIONAL BLOCK DESCRIPTIONS

| Symbol | Name                                     | Function                                                                                                                                                                                                                                                                                             |

|--------|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MPX    | Multiplexer                              | Selects one channel from 8-channel analog input signals. Channel assignment is done by the 2nd thru 4th bits of control register which are programmed by the external channel select inputs $B_0$ thru $B_2$ or by a data from MPU.                                                                  |

| СМР    | Comparator                               | Compares an unknown analog input signal with an output signal of built-in DA converter. The result of comparison is transferred to the successive-approximation register (SAR).                                                                                                                      |

| DAC    | DA Converter                             | 10-bit digital-to-analog converter. Generates analog signal corresponding to digital signal specified by the SAR.                                                                                                                                                                                    |

| SAR    | Successive-<br>Approximation<br>Register | According to the result from the comparator, generates the next step digital output to be transferred to the DAC and compared in the comparator. Composed of 10-bit register and control logic. After completion of data-conversion, acts as the data register (DR).                                 |

| SR     | Status Register                          | 10-bit register which indicates the status of operations. Indicates the assigned channel by SR-2 to SR-4, status of the external control/MPU by SR-5, operation of AD conversion by SR-6 and completion of AD conversion by SR-7. (See Table 1, 2 of page 14)                                        |

| CR     | Control Register                         | 10-bit register which controls the operation of ADC. Assigns a channel by CR-2 to CR-4, switches MPU/external control each other by CR-5, initiates AD conversion by CR-6. (See Table 1, 2 of page 14)                                                                                               |

| DR     | Data Register                            | Stores a 10-bit data at the completion of AD conversion. Outputs the data at DE=1 during the external control mode (CR-5=5). If the DR is selected ( $\overline{\text{CS}}$ =0, RA=0, and R/ $\overline{\text{W}}$ =1) during the MPU control mode (CR-5=1), the contents can be read by MPU (EN=1). |

| I/O BF | Input/Output<br>Buffer                   | Connected to the data-bus of MPU for sending or receiving the 10-bit data. The output is three-state TTL compatible.                                                                                                                                                                                 |

| CTL    | Control Logic                            | Controls sending and receiving of data between blocks and used for initializing.                                                                                                                                                                                                                     |

| Ref    | Reference Voltage<br>Regulator           | Specifies the maximum analog input signal level of ADC.                                                                                                                                                                                                                                              |

## PIN DESCRIPTIONS

| Symbol                                                                       | Name                                                           | Function                                                                                                                                                                                                                                                                                    |

|------------------------------------------------------------------------------|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A <sub>0</sub> to A <sub>7</sub>                                             | Analog Input                                                   | Analog input terminals of 8 channels, one of which is assigned by CR-2 to CR-4.                                                                                                                                                                                                             |

| D <sub>0</sub> to D <sub>9</sub><br>D <sub>0</sub> MSB<br>D <sub>9</sub> LSB | Data I/O Port                                                  | Connected to 10-bit parallel data-bus for transferring 10-bit data between internal registers and MPU.                                                                                                                                                                                      |

| <del>CS</del>                                                                | Chip Select                                                    | Chip-select terminal of ADC which is selected at $\overline{\text{CS}}$ =0.                                                                                                                                                                                                                 |

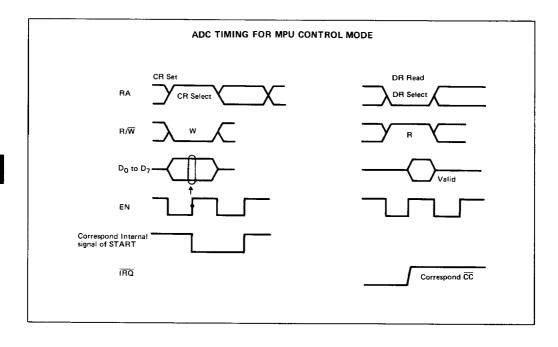

| RA                                                                           | Register<br>Address                                            | Address input for the internal registers. Selects the data register (DR) at RA=0 and the control register (CR)/status register (SR) at RA=1.                                                                                                                                                |

| R/W                                                                          | Read-Write Control                                             | Input for the read-write signal from MPU (MPU read mode at R/W=1).                                                                                                                                                                                                                          |

| EN                                                                           | Enable Signal                                                  | Input for the enable signal of MPU system. EN is used as timing for data transfer between MPU and ADC.                                                                                                                                                                                      |

| Reset                                                                        | Reset                                                          | Initializes the ADC at Reset=0.                                                                                                                                                                                                                                                             |

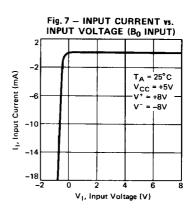

| B <sub>0</sub> to B <sub>2</sub>                                             | External Channel<br>Select Input                               | When ADC is controlled external (CR-5=0), the inputs from $B_0$ to $B_2$ are set in CR-2 to CR-4 at the falling edge of START. (See Table 3 of page 14)                                                                                                                                     |

| START                                                                        | Start                                                          | AD conversion starts at the rising edge of START when the external control mode (CR-5=0).                                                                                                                                                                                                   |

| CC/IRQ<br>(Open<br>Collector)                                                | Conversion Complete/<br>Interrupt Request                      | Indicates the completion of data conversion. After completion of data conversion, $\overline{CC}$ goes low at the external control mode (CR-5=0) or $\overline{IRC}$ goes low at the MPU control mode (CR-5=1). In both cases, they go high after the content of the data register is read. |

| DE                                                                           | Data Enable                                                    | During DE=1 at the external control mode, the data in a register assigned by RA are output on $D_0$ to $D_9$ .                                                                                                                                                                              |

| ADC CLK                                                                      | AD Conversion<br>Clock                                         | Clock for AD conversion which is input to the SAR and determines the conversion speed of ADC. A data conversion is completed by 12 cycles of clock. Not required to synchronize with the EN (Enable) signal from MPU system. Minimum cycle time of this clock is $2\mu s$ .                 |

| Ref OUT/<br>Ref ADJ                                                          | Reference Output/<br>Reference Adjustment                      | Terminals for output of reference voltage which specifies the full-scale value of analog input signal and for its adjustment.                                                                                                                                                               |

| AMP COMP/<br>DAC COMP/<br>DAC OUT/<br>SUM NODE                               | Amplifier Compensation/ DAC Compensation/ DAC Output/ Sum Node | Terminals for frequency adjustment of the internal operational amplifier with connected capacitors having specified capacitances.  SUM NODE is also used for offset adjustment.                                                                                                             |

| V <sup>+</sup> /V <sub>cc</sub> /V <sup>-</sup>                              | Terminals for<br>Power Supply                                  | To be supplied +8V, +5V and -8V, respectively. (Note 1)                                                                                                                                                                                                                                     |

| GA/GD                                                                        | Analog Ground/<br>Digital Ground                               | Terminals for ground.                                                                                                                                                                                                                                                                       |

NOTE 1: MB3758 DC-DC Converter is available, which generates +8V and -8V from signal +5V power supply.

## **ELECTRICAL CHARACTERISTICS**

1. ANALOG CIRCUIT CHARACTERISTICS  $(V_{CC} = +5V, V^+ = +8V, V^- = -8V, T_A = -30^{\circ}C \text{ to } +85^{\circ}C)$

| _                                   |                                 |             | Value |     |               | Ness                        |  |

|-------------------------------------|---------------------------------|-------------|-------|-----|---------------|-----------------------------|--|

| Parameter                           |                                 | Min Typ Max |       | Max | Unit          | Note                        |  |

| Resolution                          |                                 |             |       | 10  | bit           |                             |  |

|                                     | Relative Accuracy               | 8           |       |     | bit           |                             |  |

|                                     | Gain Error                      |             | ±1    |     | % of FSR      | Adjustable                  |  |

| Accuracy                            | Offset Error                    |             | ±0.03 |     | % of FSR      | Adjustable                  |  |

|                                     | Differential<br>Linearity Error |             | ±0.5  |     | LSB           |                             |  |

|                                     | Full Scale Voltage              |             | 40    |     | ppm/°C        |                             |  |

| Drift                               | Offset Voltage                  |             | ±0.5  |     | ppm of FSR/°C |                             |  |

| Full Scale<br>Power Supply          | Positive Power<br>Supply        |             | 1.0   |     | mV/V          | 8V±5%                       |  |

| Fluctuation<br>Suppressing<br>Ratio | Negative Power<br>Supply        |             | -0.5  |     | mV/V          | -8V±5%                      |  |

|                                     | Input Current                   |             |       | 1   | μΑ            | V <sub>IA</sub> = 0 to 6.5V |  |

| Analog Input                        | Full Scale Voltage              |             |       | 6.5 | V             |                             |  |

| Reference                           | Reference Voltage               |             | 5.0   |     | v             |                             |  |

| Voltage                             | Drift                           |             | 30    |     | ppm/°C        |                             |  |

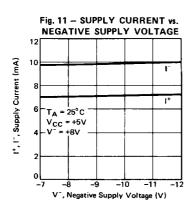

| Supply Current                      | Positive Power<br>Supply        |             | 7     | 12  | mA            |                             |  |

|                                     | Negative Power<br>Supply        |             | -10   | -17 | mA            |                             |  |

| Conversion Cycle Ti                 | me                              |             |       | 50  | μs/ch         | f <sub>CLK</sub> = 250Hz    |  |

## 2. DIGITAL CIRCUIT DC CHARACTERISTICS $(V_{CC} = +5V \pm 5\%, V^+ = +8V, V^- = -8V, T_A = -30^{\circ}C \text{ to } +85^{\circ}C)$

| Parameter              | Parameter Symbol |                                                                                                    |                                                 |     | Value |      |      |

|------------------------|------------------|----------------------------------------------------------------------------------------------------|-------------------------------------------------|-----|-------|------|------|

| raiametei              | Symbol           | Condi                                                                                              | ition                                           | Min | Тур   | Max  | Unit |

| Input High Voltage     | V <sub>IH</sub>  |                                                                                                    |                                                 | 2   |       |      | v    |

| Input Low Voltage      | V <sub>IL</sub>  |                                                                                                    | -                                               |     |       | 0.8  | v    |

| Input Clamp Voltage    | V <sub>IC</sub>  | V <sub>CC</sub> = 4.75V, I <sub>I</sub>                                                            | c = -18mA                                       |     |       | -1.5 | v    |

| Output High Voltage    | V <sub>oH</sub>  | V <sub>CC</sub> = 4.75V, V <sub>IH</sub> = 2V,<br>V <sub>IL</sub> = 0.8V, I <sub>OH</sub> = -2.6mA |                                                 | 2.4 |       |      | ٧    |

| Output Low Voltage     | Vol              | V <sub>CC</sub> = 4.75V,<br>V <sub>IH</sub> = 2V,<br>V <sub>IL</sub> = 0.8V,                       | J <sub>OL</sub> = 4mA                           |     |       | 0.4  | .,   |

| - Compare Love Voltage | *OL              |                                                                                                    | I <sub>OL</sub> = 8mA                           |     |       | 0.5  | V    |

| Output Current         |                  | V <sub>IH</sub> = 2V,<br>V <sub>CC</sub> = 5.25V                                                   | V <sub>O</sub> = 2.7V                           |     |       | 20   |      |

| (Off State)            | loz              | V <sub>CC</sub> = 5.25V<br>V <sub>IL</sub> = 0.8V                                                  | V <sub>O</sub> = 0.4V                           |     |       | -20  | μΑ   |

| Input High Current     | l <sub>in</sub>  | V <sub>IH</sub> = 2.7V, V <sub>CC</sub>                                                            | = 5.25V                                         |     |       | 20   |      |

| input riigii current   | 'IH              | V <sub>IH</sub> = 7V, V <sub>CC</sub> =                                                            | = 5.25V                                         |     |       | 100  | μΑ   |

| Input Low Current      | I <sub>IL</sub>  | V <sub>IL</sub> = 0.4V, V <sub>CC</sub>                                                            | V <sub>1L</sub> = 0.4V, V <sub>CC</sub> = 5.25V |     |       | -400 | μΑ   |

| Output Short Current   | los              | V <sub>O</sub> = 0V, V <sub>CC</sub> = 5.25V                                                       |                                                 | -15 |       | -95  | mA   |

| Supply Current         | Icc              | A <sub>0</sub> to A <sub>7</sub> , Reset<br>V <sub>CC</sub> = 5.25V                                | = GND,                                          | 30  | 55    | 92   | mA   |

# MB4051 HIMMAN

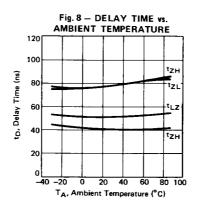

## 3. DIGITAL CIRCUIT AC CHARACTERISTICS $(V_{CC} = +5V\pm5\%, V^+ = +8V, V^- = -8V, T_A = -30^{\circ}C \text{ to } +85^{\circ}C)$

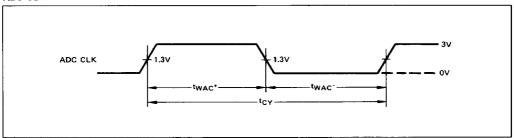

## ADC CLK

| Parameter           | Symbol             | Condition |     | Unit |     |    |

|---------------------|--------------------|-----------|-----|------|-----|----|

|                     |                    |           | Min | Тур  | Max |    |

| Cycle time          | t <sub>CY</sub>    |           | 4   |      |     | μs |

| H Level Pulse Width | t <sub>wac</sub> + |           | 1   |      |     | μs |

| L Level Pulse Width | <sup>t</sup> wac⁻  |           | 1   |      |     | μs |

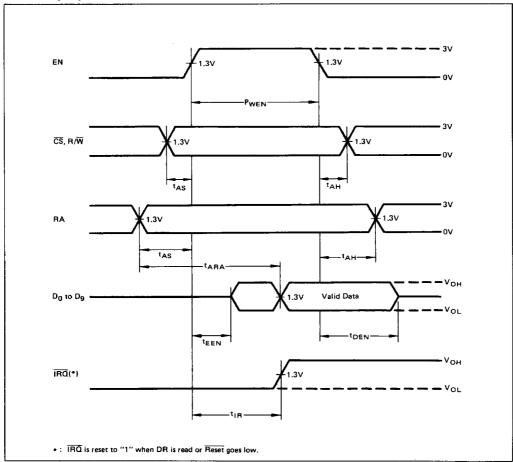

## Read Mode

| Parameter                 |                  |           | Value |     |     | Unit |  |

|---------------------------|------------------|-----------|-------|-----|-----|------|--|

|                           | Symbol           | Condition | Min   | Тур | Max | Unit |  |

| EN Pulse Width            | P <sub>WEN</sub> |           | 270   |     |     | ns   |  |

| CS, R/W, RA Setup Time    | t <sub>AS</sub>  |           | 20    |     |     | ns   |  |

| CS, R/W, RA Hold Time     | t <sub>AH</sub>  |           | 10    |     |     | ns   |  |

| Enable Time from EN       | teen             | Fig. 2*   |       |     | 160 | ns   |  |

| Access Time from RA       | <sup>†</sup> ARA | Fig. 2*   |       |     | 300 | ns   |  |

| Disable Time from EN      | t <sub>DEN</sub> | Fig. 2*   | 10    |     | 120 | ns   |  |

| IRQ Recovery Time from EN | t <sub>IR</sub>  | Fig. 3*   |       |     | 240 | ns   |  |

<sup>\* :</sup> See page 11

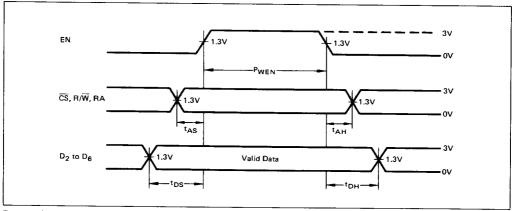

#### Write Mode

| Parameter              | Symbol           | Condition |     | Value |      |      |

|------------------------|------------------|-----------|-----|-------|------|------|

|                        | Symbol           | Condition | Min | Тур   | Max  | Unit |

| EN Pulse Width         | P <sub>WEN</sub> |           | 270 |       | - 11 | ns   |

| CS, R/W, RA Setup Time | t <sub>AS</sub>  |           | 20  |       |      | ns   |

| CS, R/W, RA Hold Time  | t <sub>AH</sub>  |           | 10  |       |      | ns   |

| Data Setup Time        | t <sub>DS</sub>  |           | 10  |       |      | ns   |

| Data Hold Time         | t <sub>DH</sub>  |           | 10  |       |      | ns   |

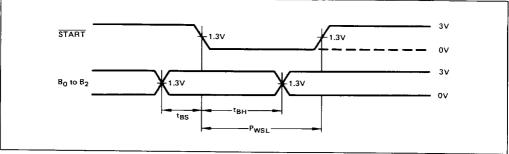

## **External Control AD Conversion**

| Parameter          | Symbol Condition - |           |     |     |     |      |

|--------------------|--------------------|-----------|-----|-----|-----|------|

|                    |                    | Condition | Min | Тур | Max | Unit |

| START Pulse Width  | PwsL               |           | 270 |     |     | ns   |

| Channel Setup Time | t <sub>BS</sub>    |           | 20  |     |     | ns   |

| Channel Hold Time  | t <sub>BH</sub>    |           | 270 |     |     | ns   |

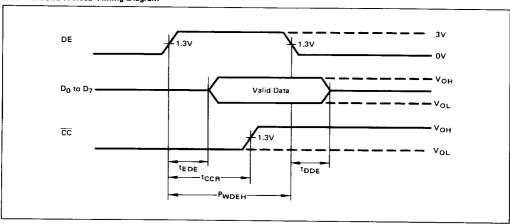

## External Control Read Mode

| Parameter                | Symbol            | Condition |     |     |     |      |

|--------------------------|-------------------|-----------|-----|-----|-----|------|

|                          | Symbol            |           | Min | Тур | Max | Unit |

| DE Pulse Width           | P <sub>WDEH</sub> |           | 270 |     |     | ns   |

| Enable Time from DE      | t <sub>EDE</sub>  | Fig. 2*   | -   |     | 160 | ns   |

| Disable Time from DE     | t <sub>DDE</sub>  | Fig. 2*   | 10  |     | 160 | ns   |

| CC Recovery Time from DE | t <sub>CCR</sub>  | Fig. 3*   |     |     | 280 | ns   |

<sup>\* :</sup> See page 11

# MB4051

## **READ Timing Diagram**

## WRITE Timing Diagram

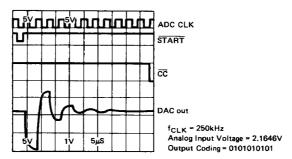

## **External Control AD Conversion Timing Diagram**

## **External Control Read Timing Diagram**

7/

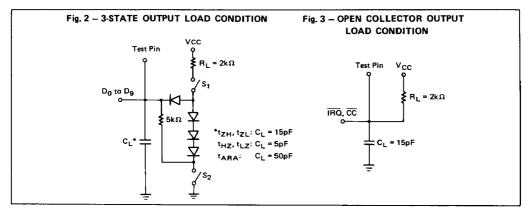

## 4. SWITCHING CHARACTERISTICS TEST CONDITIONS

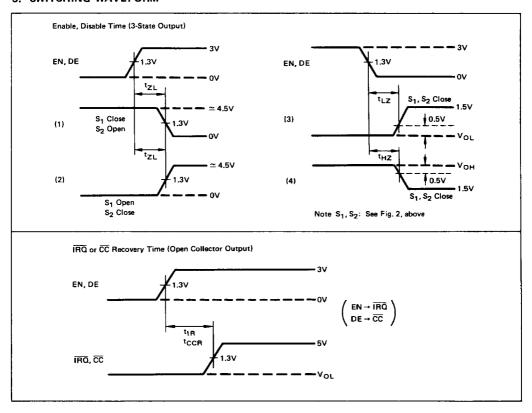

#### 5. SWITCHING WAVEFORM

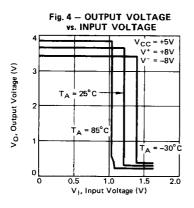

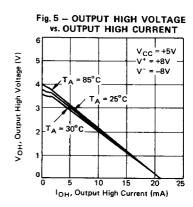

## TYPICAL CHARACTERISTICS CURVES

## TYPICAL CHARACTERISTICS CURVES (continued)

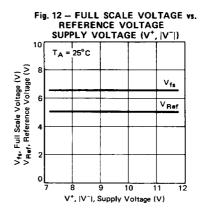

Fig. 13 - OPERATION WAVEFORM

Table 1. BIT CONSTRUCTION OF DR AND S/C R

|       | RA | R/W        | Do             | D <sub>1</sub> | D <sub>2</sub> | D <sub>3</sub> | D <sub>4</sub> | D <sub>5</sub>  | D <sub>6</sub> | D <sub>7</sub> | D <sub>8</sub> | D <sub>9</sub> |

|-------|----|------------|----------------|----------------|----------------|----------------|----------------|-----------------|----------------|----------------|----------------|----------------|

| DR    | 0  | 1<br>Read  | Bit 0<br>(MSB) | Bit 1          | Bit 2          | Bit 3          | Bit 4          | Bit 5           | Bit 6          | Bit 7          | Bit 8          | Bit 9<br>(LSB) |

| S/C R | 1  | 1<br>Read  |                |                | ln             | put CH. Se     | elect          | Mode<br>Control | Busy           | IRQ            |                |                |

|       | •  | 0<br>Write |                |                | Co             | C <sub>1</sub> | C <sub>2</sub> | INT/EXT         | Start          | -              | _              | _              |

Table 2. CHANNEL SELECT FOR MPU CONTROL

| C <sub>2</sub> | C <sub>1</sub> | Co | Selected CH.   |

|----------------|----------------|----|----------------|

| 0              | 0              | 0  | A <sub>0</sub> |

| 0              | 0              | 1  | A <sub>1</sub> |

| 0              | 1              | 0  | A <sub>2</sub> |

| 0              | 1              | 1  | A <sub>3</sub> |

| 1              | 0              | 0  | A <sub>4</sub> |

| 1              | 0              | 1  | A <sub>5</sub> |

| 1              | 1              | 0  | A <sub>6</sub> |

| 1              | 1              | 1  | A <sub>7</sub> |

Table 3. CHANNEL SELECT FOR EXTERNAL CONTROL

| B <sub>2</sub> | B <sub>1</sub> | Bo | Selected CH.   |

|----------------|----------------|----|----------------|

| 0              | 0              | 0  | A <sub>o</sub> |

| 0              | 0              | 1  | A <sub>1</sub> |

| 0              | 1              | 0  | A <sub>2</sub> |

| 0              | 1              | 1  | A <sub>3</sub> |

| 1              | 0              | 0  | A <sub>4</sub> |

| 1              | 0              | 1  | A <sub>5</sub> |

| 1              | 1              | 0  | A <sub>6</sub> |

| 1              | 1              | 1  | A <sub>7</sub> |

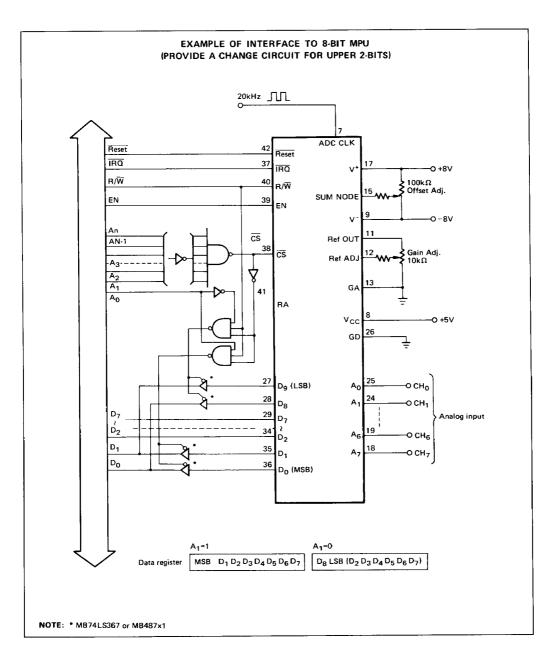

## **ADC OPERATION MODES**

According to the status of 5th bit (CR-5) in the built-in control register, ADC has two operation modes: external control mode and MPU control mode.

Just after an initialization (Reset going from low to high), ADC is in the external control mode (designation of channel, start of data conversion and data output are controlled through the external control input terminals). This mode is useful for ADC applications only or for DMA operation independent of MPU.

When the MPU control mode is required, set CR-5 of the control register high through MPU.

## EXTERNAL CONTROL MODE (CR-5=0):

This mode is used when ADC is controlled by the external hardware. An analog input signal channel is designated by  $B_0$  to  $B_2$  and the AD conversion starts at the second rising edging of ADC clock after  $\overline{START}$  goes low.

At the completion of 10-bit data conversion,  $\overline{CC}$  (Convert Complete) goes low to notify it to external devices. The converted data is read after the low state of  $\overline{CC}$  and DE goes high.

## MPU CONTROL MODE (CR-5=1):

This mode is used when ADC is controlled by the MPU software. Because of CR-5=0 at initialization, CR-5 should be set high through MPU. After completion of the conversion, CR-7 (IRQ flag) is set high and  $\overline{\text{IRQ}}$  output goes low to interrupt MPU operation.

After confirming  $\overline{\text{IRO}}$ =0, MPU starts the interrupt routine to select the data register of ADC and reads it. After MPU reads the data register,  $\overline{\text{IRO}}$  is reset high. In this mode, all signals on  $\overline{\text{START}}$  and  $B_0$  to  $B_2$  are ignored. When the ADC is required to return to the external control mode, CR-5 is set low through MPU or  $\overline{\text{RESET}}$  is set low.

## **TECHNICAL INFORMATION**

#### **DEFINITION OF TERMS**

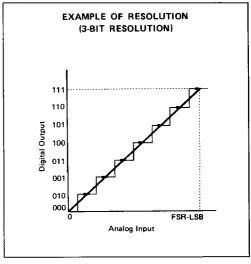

#### Resolution:

The minimum distinguishable analog deviation in AD converter. Since MB4051 is 10-bit AD converter, it is possible to resolute an analog signal, from OV to 6.5V (FSR), into  $2^{10} = 1024$  parts.

#### Relative Accuracy:

Deviation between a straight line from the zero point of the device (all "O") to the full-scale point (all 'L') and an actual conversion characteristic curve.

#### Gain Error:

Difference between an ideal input voltage span and an actual input voltage span. In the MB4051, according to the procedure described separately, it is possible to adjust the gain error to zero.

#### Offset Error:

Difference between an ideal cirtical input voltage which makes all output bits zero and an actual critical input voltage. In the MB4051, such offset error can be adjusted according to the procedure described separately.

## **DEFINITION OF TERMS (Continued)**

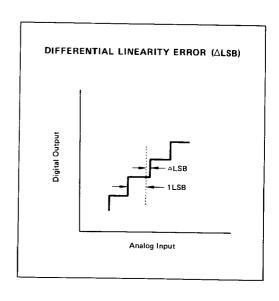

#### Differential Linearity Error:

Input voltage deviation from an ideal input voltage which is necessary to change the output code as large as 1LSB. The differential linearity error of  $\pm 1/2$ LSB means that, when the input signal changes 1/2LSB to 3/2LSB, digital code varies 1LSB.

## **Example of Output Coding**

| Scale          | Input Voltage | M<br>S<br>B | D<br>1 |   |   | D<br>4 |   |   |   |   | L<br>S<br>B |

|----------------|---------------|-------------|--------|---|---|--------|---|---|---|---|-------------|

| FS-1LSB        | 6.4937        | 1           | 1      | 1 | 1 | 1      | 1 | 1 | 1 | 1 | 1           |

| FS/2           | 3.2500        | 1           | 0      | 0 | 0 | 0      | 0 | 0 | 0 | 0 | 0           |

| FS/4           | 1.6250        | 0           | 1      | 0 | 0 | 0      | 0 | 0 | 0 | 0 | 0           |

| FS/8           | 0.8125        | 0           | 0      | 1 | 0 | 0      | 0 | 0 | 0 | 0 | 0           |

| FS/16          | 0.4063        | 0           | 0      | 0 | 1 | 0      | 0 | 0 | 0 | 0 | 0           |

| FS/32          | 0.2031        | 0           | 0      | 0 | 0 | 1      | 0 | 0 | 0 | 0 | 0           |

| FS/64          | 0.1016        | 0           | 0      | 0 | 0 | 0      | 1 | 0 | 0 | 0 | 0           |

| FS/128         | 0.0508        | 0           | 0      | 0 | 0 | 0      | 0 | 1 | 0 | 0 | 0           |

| FS/256         | 0.0254        | 0           | 0      | 0 | 0 | 0      | 0 | 0 | 1 | 0 | 0           |

| FS/512         | 0.0127        | 0           | 0      | 0 | 0 | 0      | 0 | 0 | 0 | 1 | 0           |

| FS/1024 = 1LSB | 0.0063        | 0           | 0      | 0 | 0 | 0      | 0 | 0 | 0 | 0 | 1           |

| 0              | 0.0000        | 0           | 0      | 0 | 0 | 0      | 0 | 0 | 0 | 0 | 0           |

## APPLICATIONS INFORMATION

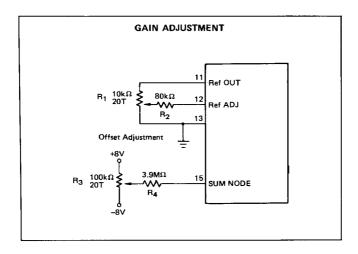

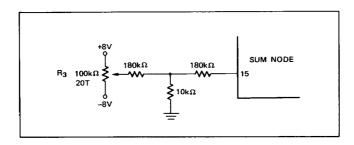

#### ADJUSTMENT OF OFFSET AND GAIN

In the MB4051, Both gain-error and offset-error can be adjusted to zero by trimmers connected as shown below. In this case, potentiometers and resistors for trimmers should have temperature characteristics below 100 ppm/°C to ensure long-term stability and less temperature drift.

The following external adjustment circuits should be located as near as possible to the package.

#### Offset Adjustment

By applying the voltage of 1/2LSB, i.e., 3.2mV to an analog input channel, continuously execute AD conversion of the applied input voltage. Then, adjust potentiometer R<sub>3</sub> during the conversion so that the conversion results become "0000000000" and "0000000001", alternatively. The range of adjustment is about ±0.2% of FSR in the circuit shown below.

The R<sub>4</sub> resistor for offset adjustment can be replaced with smoller resistors as follows.

#### **GAIN ADJUSTMENT**

After offset adjustment, by applying FSR-3/2LSB (6.4905V) to an analog input, execute AD conversion of the applied input voltage. Then, adjust potentiometer  $R_1$  during the conversion so that the conversion results become "1111111111" and "1111111110", alternatively. The range of adjustment is about -12% to +5% of FSR in the circuit shown.

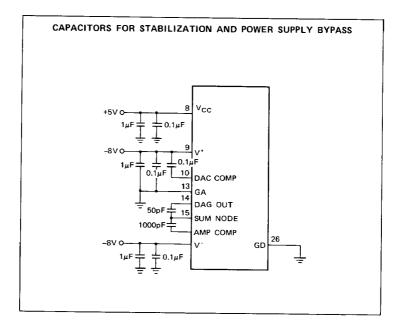

## PRECAUTIONS FOR CIRCUIT STABILIZATION

To stabilize the ADC operation and by-pass power supply line noise, connect the external capacitors as shown.

Bypass capacitor for filtering line-noise should have good high-frequency characteristics and should be connected as near as possible to the package.

If a printed circuit board is used, the ground-line should be made as wide as possible and the pattern should be made in such a manner that the analog input signal line does not pick up noise from the digital signal and so on. Unused digital input should be kept in an inactive state listed below and unused analog input should be connected to analog ground (GA).

| Inactive State | Terminals                                         |  |  |  |  |  |

|----------------|---------------------------------------------------|--|--|--|--|--|

| "L"            | EN, RA, R/W, DE, B <sub>0</sub> to B <sub>2</sub> |  |  |  |  |  |

| "H"            | Reset, CS, START                                  |  |  |  |  |  |

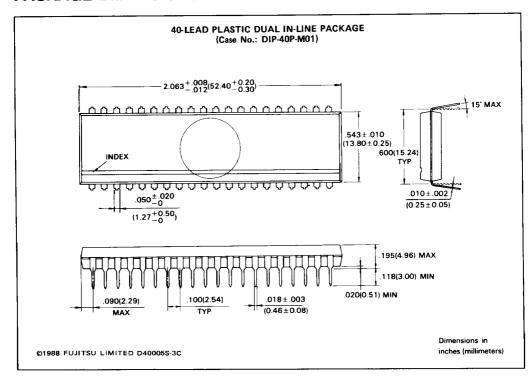

## **PACKAGE DIMENSIONS**

## **PACKAGE DIMENSIONS (continued)**