$2\Omega$

# National Semiconductor

# AH5009/AH5010/AH5011/AH5012 Monolithic **Analog Current Switches**

### **General Description**

A versatile family of monolithic JFET analog switches economically fulfills a wide variety of multiplexing and analog switching applications.

Even numbered switches may be driven directly from standard 5V logic, whereas the odd numbered switches are intended for applications utilizing 10V or 15V logic. The monolithic construction guarantees tight resistance match and

For voltage switching applications see LF13331, LF13332, and LF13333 Analog Switch Family, or the CMOS Analog Switch Family.

# **Applications**

- A/D and D/A converters

- Micropower converters

- Industrial controllers

- Position controllers

- Data acquisition

- Active filters

- Signal multiplexers/demultiplexers

- Multiple channel AGC

- Quad compressors/expanders

- Choppers/demodulators

- Programmable gain amplifiers

- High impedance voltage buffer

- Sample and hold

#### **Features**

- Interfaces with standard TTL and CMOS

- "ON" resistance match  $100\Omega$ Low "ON" resistance 50 pA Very low leakage ±10V peak Large analog signal range High switching speed 150 ns

- Excellent isolation between 80 dB at 1 kHz channels

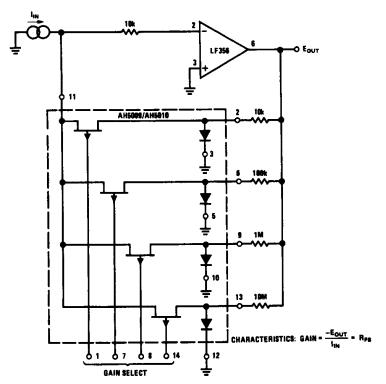

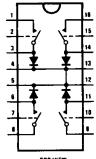

#### Connection and Schematic Diagrams (All switches shown are for logical "1" input) **Dual-In-Line Package**

#### **Dual-In-Line Package**

AH5009C and AH5010C MUX Switches

(4-Channel Version Shown)

Order Number AH5009CM, AH5009CN, AH5010CM or AH5010CN

See NS Package Number M14A or N14A

| LOGIC DRIVE | 4 CHANNEL<br>MUX | 4 SPST<br>SWITCHES |

|-------------|------------------|--------------------|

| 5V LOGIC    | AH5010C          | AH5012C            |

| 15V LOGIC   | AH5009C          | AH5011C            |

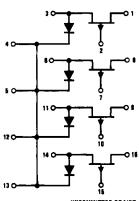

AH5011C and AH5012C SPST Switches (Quad Version Shown) Order Number AH5011CM, AH5011CN, AH5012CM or AH5012CN See NS Package Number M16A or N16A

Note: All diode cathodes are internally connected to the substrate.

UNCOMMITTED DRAINS TL/H/5659-1

### **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Soldering Information: N Package 10 sec

**Drain Current**

30 mA

Input Voltage

30V

SO Package Vapor Phase (60 sec.) Infrared (15 sec.) 300°C 215°C

AH5009/AH5010/AH5011/AH5012 Positive Analog Signal Voltage

30V

Power Dissipation

220°C 500 mW

Negative Analog Signal Voltage

-15V

Operating Temperature Range

-25°C to +85°C

**Diode Current**

10 mA

Storage Temperature Range

-65°C to +150°C

### Électrical Characteristics AH5010 and AH5012 (Notes 2 and 3)

| Symbol              | Parameter               | Conditions                                                             | Тур  | Max        | Units    |

|---------------------|-------------------------|------------------------------------------------------------------------|------|------------|----------|

| lgsx                | Input Current "OFF"     | $4.5V \le V_{GD} \le 11V$ , $V_{SD} = 0.7V$<br>$T_A = 85^{\circ}C$     | 0.01 | 0.2<br>10  | nA<br>nA |

| I <sub>D(OFF)</sub> | Leakage Current "OFF"   | V <sub>SD</sub> =0.7V, V <sub>GS</sub> =3.8V<br>T <sub>A</sub> =85°C   | 0.02 | 0.2<br>10  | nA<br>nA |

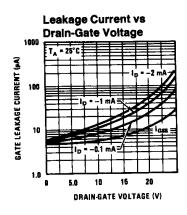

| IG(ON)              | Leakage Current "ON"    | V <sub>GD</sub> =0V, I <sub>S</sub> =1 mA<br>T <sub>A</sub> =85°C      | 0.08 | 1<br>200   | nA<br>nA |

| IG(ON)              | Leakage Current "ON"    | V <sub>GD</sub> =0V, I <sub>S</sub> = 2 mA<br>T <sub>A</sub> =85°C     | 0.13 | 5<br>10    | nA<br>μA |

| I <sub>G(ON)</sub>  | Leakage Current "ON"    | V <sub>GD</sub> =0V, I <sub>S</sub> =-2 mA<br>T <sub>A</sub> =85°C     | 0.1  | 10<br>20   | nA<br>μA |

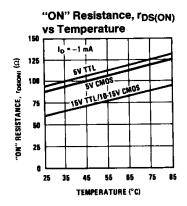

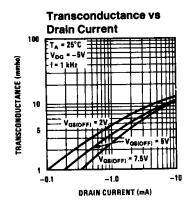

| rds(ON)             | Drain-Source Resistance | $V_{GS} = 0.35V$ , $I_S = 2 \text{ mA}$<br>$T_A = +85^{\circ}\text{C}$ | 90   | 150<br>240 | Ω        |

| V <sub>DIODE</sub>  | Forward Diode Drop      | I <sub>D</sub> =0.5 mA                                                 |      | 0.8        | V        |

| rds(ON)             | Match                   | V <sub>GS</sub> =0V, I <sub>D</sub> =1 mA                              | 4    | 20         | Ω        |

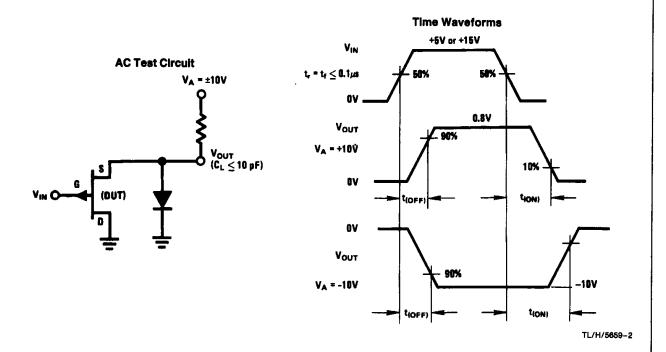

| T <sub>ON</sub>     | Turn "ON" Time          | See AC Test Circuit                                                    | 150  | 500        | ns       |

| T <sub>OFF</sub>    | Turn "OFF" Time         | See AC Test Circuit                                                    | 300  | 500        | ns       |

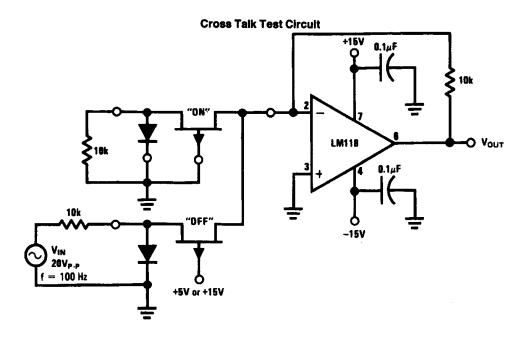

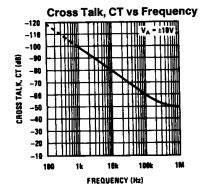

| CT                  | Cross Talk              | See AC Test Circuit                                                    | 120  |            | dB       |

### Electrical Characteristics AH5009 and AH5011 (Notes 2 and 3)

| Symbol              | Parameter               | Conditions                                                              | Тур  | Max        | Units    |

|---------------------|-------------------------|-------------------------------------------------------------------------|------|------------|----------|

| I <sub>GSX</sub>    | Input Current "OFF"     | 11V≤V <sub>GD</sub> ≤15V, V <sub>SD</sub> =0.7V<br>T <sub>A</sub> =85°C | 0.01 | 0.2<br>10  | nA<br>nA |

| I <sub>D(OFF)</sub> | Leakage Current "OFF"   | V <sub>SD</sub> =0.7V, V <sub>GS</sub> =10.3V<br>T <sub>A</sub> =85°C   | 0.01 | 0.2<br>10  | nA<br>nA |

| I <sub>G(ON)</sub>  | Leakage Current "ON"    | V <sub>GD</sub> =0V, I <sub>S</sub> = 1 mA<br>T <sub>A</sub> =85°C      | 0.04 | 0.5<br>100 | nA<br>nA |

| I <sub>G(ON)</sub>  | Leakage Current "ON"    | V <sub>GD</sub> =0V, I <sub>S</sub> =2 mA<br>T <sub>A</sub> =85°C       |      | 2<br>1     | nA<br>μA |

| I <sub>G(ON)</sub>  | Leakage Current "ON"    | $V_{GD} = 0V$ , $I_S = -2 \text{ mA}$<br>$T_A = 85^{\circ}\text{C}$     |      | 5<br>2     | nA<br>μA |

| rds(ON)             | Drain-Source Resistance | $V_{GS} = 1.5V, I_S = 2 \text{ mA}$<br>$T_A = 85^{\circ}\text{C}$       | 60   | 100<br>160 | Ω        |

| V <sub>DIODE</sub>  | Forward Diode Drop      | I <sub>D</sub> =0.5 mA                                                  |      | 0.8        | ٧        |

| <sup>r</sup> DS(ON) | Match                   | V <sub>GS</sub> =0V, I <sub>D</sub> =1 mA                               | 2    | 10         | Ω        |

| T <sub>ON</sub>     | Turn "ON" Time          | See AC Test Circuit                                                     | 150  | 50         | ns       |

| TOFF                | Turn "OFF" Time         | See AC Test Circuit                                                     | 300  | 500        | ns       |

| СТ                  | Cross Talk              | See AC Test Circuit. f = 100 Hz.                                        | 120  |            | dB       |

Note 1: Absolute maximum ratings indicate limits beyond which damage to the device may occur. DC and AC electrical specifications do not apply when operating the device beyond its specified operating conditions.

Note 2: Test conditions 25°C unless otherwise noted.

Note 3: "OFF" and "ON" notation refers to the conduction state of the FET switch.

Note 4: Thermal Resistance:

N14A, N16A M14A, M16A

θ<sub>JA</sub> 92°C/W 115°C/W

# **Test Circuits and Switching Time Waveforms**

# **Typical Performance Characteristics**

# **Applications Information**

#### **Theory of Operation**

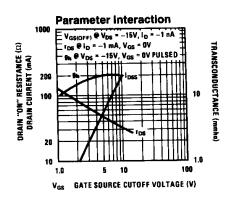

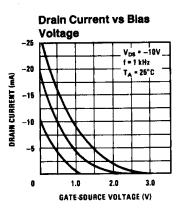

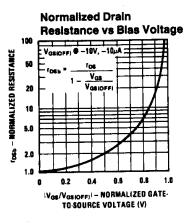

The AH series of analog switches are primarily intended for operation in current mode switch applications; i.e., the drains of the FET switch are held at or near ground by operating into the summing junction of an operational amplifier. Limiting the drain voltage to under a few hundred millivolts eliminates the need for a special gate driver, allowing the switches to be driven directly by standard TTL (AH5010), 5V-10V CMOS (AH5010), open collector 15V TTL/CMOS (AH5009).

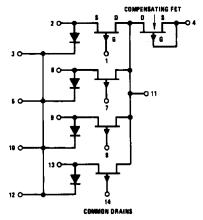

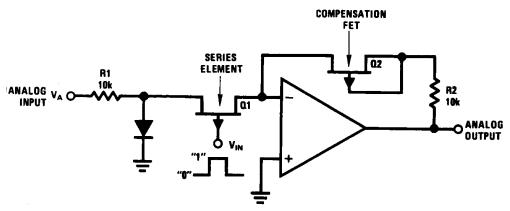

Two basic switch configurations are available: 4 independent switches (SPST) and 4 pole switches used for multiplexing (4 PST-MUX). The MUX versions such as the AH5009 offer common drains and include a series FET operated at  $V_{\rm GS}=$  0V. The additional FET is placed in the feedback path in order to compensate for the "ON" resistance of the switch FET as shown in *Figure 1*.

The closed-loop gain of Figure 1 is:

$$A_{VCL} = \frac{R2 + r_{DS(ON)Q2}}{R1 + r_{DS(ON)Q1}}$$

For R1 = R2, gain accuracy is determined by the  $r_{DS(ON)}$  match between Q1 and Q2. Typical match between Q1 and Q2 is 4 ohms resulting in a gain accuracy of 0.05% (for R1 = R2 = 10 k $\Omega$ ).

#### **Noise immunity**

The switches with the source diodes grounded exhibit improved noise immunity for positive analog signals in the

"OFF" state. With  $V_{IN}=15V$  and the  $V_A=10V$ , the source of Q1 is clamped to about 0.7V by the diode ( $V_{GS}=14.3V$ ) ensuring that ac signals imposed on the 10V input will not gate the FET "ON."

#### Selection of Gain Setting Resistors

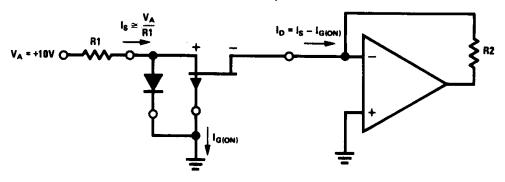

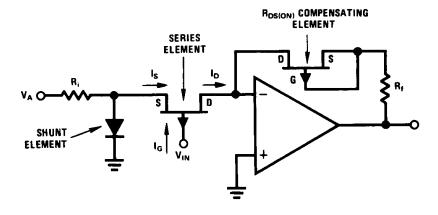

Since the AH series of analog switches are operated in current mode, it is generally advisable to make the signal current as large as possible. However, current through the FET switch tends to forward bias the source to gate junction and the signal shunting diode resulting in leakage through these junctions. As shown in *Figure 2*, I<sub>G(ON)</sub> represents a finite error in the current reaching the summing junction of the op

Secondly, the  $r_{DS(ON)}$  of the FET begins to "round" as  $l_S$  approaches  $l_{DSS}$ . A practical rule of thumb is to maintain  $l_S$  at less than  $\frac{1}{10}$  of  $l_{DSS}$ .

Combining the criteria from the above discussion yields:

$$R1_{min} \ge \frac{V_{A(MAX)} A_{D}}{I_{G(ON)}}$$

(2a)

or:

$$\geq \frac{V_{A(MAX)}}{I_{DSS}/10}$$

(2b)

whichever is larger.

FIGURE 1. Use of Compensation FET

FIGURE 2. On Leakage Current, IG(ON)

# **Applications Information (Continued)**

Where:  $V_{A(MAX)}$  = Peak amplitude of the analog

input signal

A<sub>D</sub> = Desired accuracy

$I_{G(ON)}$  = Leakage at a given  $I_S$

I<sub>DSS</sub> = Saturation current of the FET

switch ≅ 20 mA

In a typical application,  $V_A$  might =  $\pm 10V$ ,  $A_D$ =0.1%,  $0^{\circ}C \le T_A \le 85^{\circ}C$ . The criterion of equation (2b) predicts:

$$R1_{(MIN)} \ge \frac{(10V)}{\left(\frac{20 \text{ mA}}{10}\right)} = 5 \text{ k}\Omega$$

For R1 = 5k,  $I_S \cong 10V/5k$  or 2 mA. The electrical characteristics guarantee an  $I_{G(ON)} \le 1\mu A$  at 85°C for the AH5010. Per the criterion of equation (2a):

$$R1_{(MIN)} \ge \frac{(10V)(10^{-3})}{1 \times 10^{-6}} \ge 10 \text{ k}\Omega$$

Since equation (2a) predicts a higher value, the 10k resistor should be used.

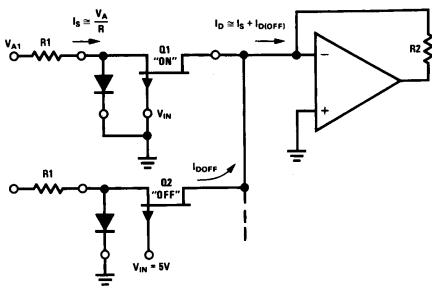

The "OFF" condition of the FET also affects gain accuracy. As shown in *Figure 3*, the leakage across Q2, I<sub>D(OFF)</sub> represents a finite error in the current arriving at the summing junction of the op amp.

Accordingly:

$$R1_{(MAX)} \leq \frac{V_{A(MIN)} A_{D}}{(N) I_{D(OFF)}}$$

Where:  $V_{A(MIN)}$  = Minimum value of the analog

input signal

$A_D$  = Desired accuracy

N = Number of channels

I<sub>D(OFF)</sub> = "OFF" leakage of a given FET

switch

As an example, if N = 10,  $A_D$  = 0.1%, and  $I_{D(OFF)} \le 10$  nA at 85°C for the AH5009. R1<sub>(MAX)</sub> is:

$$R1_{(MAX)} \le \frac{(1V)(10^{-3})}{(10)(10 \times 10^{-9})} = 10k$$

Selection of R2, of course, depends on the gain desired and for unity gain R1 = R2.

Lastly, the foregoing discussion has ignored resistor tolerances, input bias current and offset voltage of the op amp—all of which should be considered in setting the overall gain accuracy of the circuit.

#### **TTL Compatibility**

The AH series can be driven with two different logic voltage swings: the even numbered part types are specified to be driven from standard 5V TTL logic and the odd numbered types from 15V open collector TTL.

FIGURE 3

# **Applications Information (Continued)**

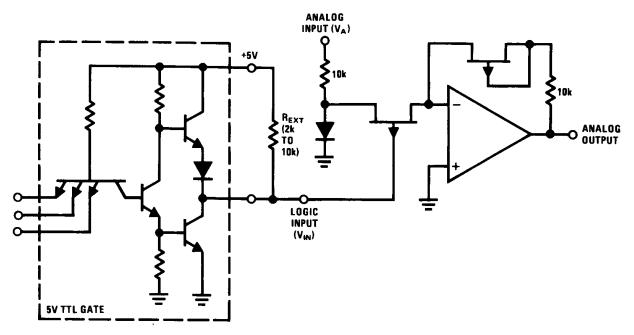

Standard TTL gates pull-up to about 3.5V (no load). In order to ensure turn-off of the even numbered switches such as AH5010, a pull-up resistor,  $R_{EXT}$ , of at least 10  $k\Omega$  should be placed between the 5V  $V_{CC}$  and the gate output as shown in Figure 4.

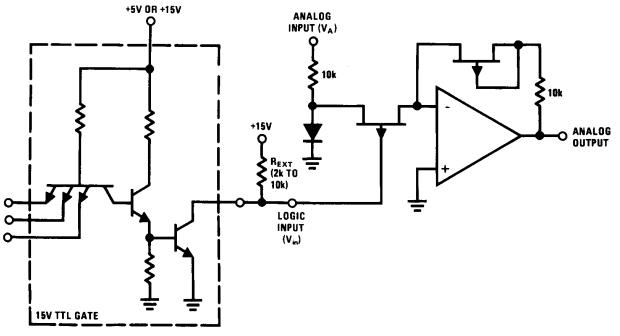

Likewise, the open-collector, high voltage TTL outputs should use a pull-up resistor as shown in Figure 5. In

both cases,  $t_{(OFF)}$  is improved for lower values of  $R_{\text{EXT}}$  at the expense of power dissipation in the low state.

#### **Definition of Terms**

The terms referred to in the electrical characteristics tables are as defined in *Figure 6*.

FIGURE 4. Interfacing with +5V TTL

FIGURE 5. Interfacing with + 15V Open Collector TTL

# Applications Information (Continued)

FIGURE 6. Definition of Terms

# **Typical Applications**

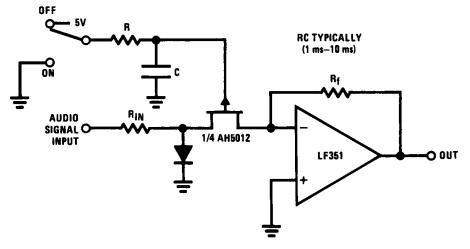

### De-Glitched Switch for Noiseless Audio Switching

TL/H/5859-7

# **Typical Applications (Continued)**

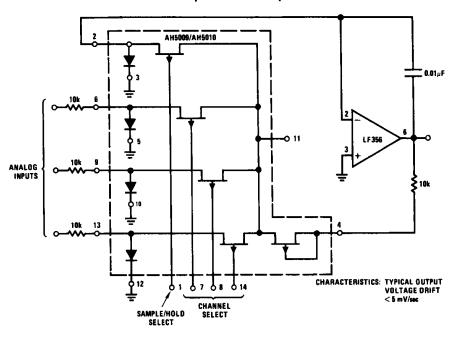

#### 3-Channel Multiplexer with Sample and Hold

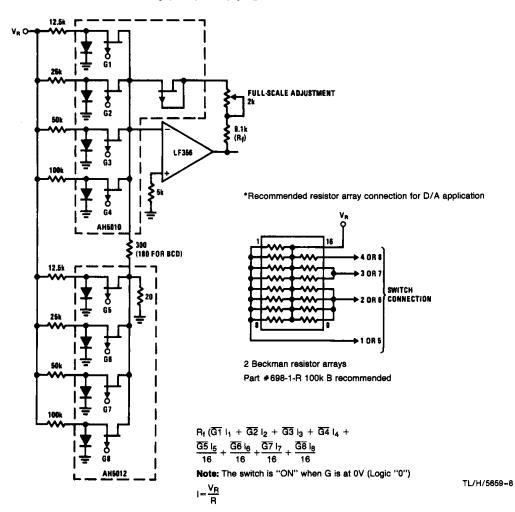

8-Bit Binary (BCD) Multiplying D/A Converter\*

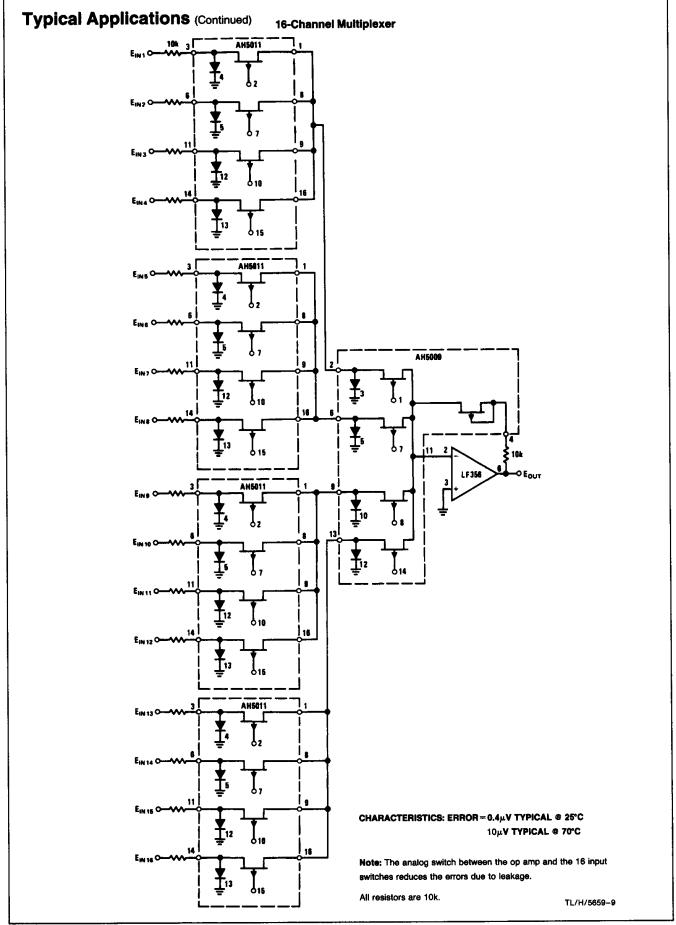

# Typical Applications (Continued)

### Gain Programmable Ampilfier