# **Z89320**

# 16-BIT DSP DIGITAL SIGNAL PROCESSOR

#### GENERAL DESCRIPTION

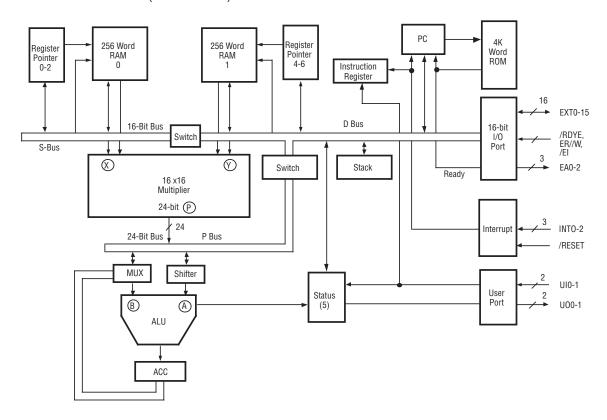

The Z89320 is a second generation, 16-bit fractional, two's complement CMOS Digital Signal Processor (DSP). Most instructions, including multiply and accumulate, are accomplished in a single clock cycle. The processor contains 1Kbyte of on-chip data RAM (two blocks of 256 16-bit words), 4K words of program ROM. Also, the processor features a 24-bit ALU, a 16x16 multiplier, a 24-bit Accumulator and a shifter. Additionally, the processor contains a six-level stack, three vectored interrupts and two inputs for conditional program jumps. Each RAM block contains a set of three pointers which may be incremented or decremented automatically to affect hardware looping without software overhead. The data RAMs can be simultaneously addressed and loaded to the multiplier for a true single cycle multiply.

The device includes a 16-bit I/O bus for transferring data or for mapping peripherals into the processor address space. Additionally, there are two general purpose user inputs and two user outputs. Operation with slow peripherals is accompished with a ready input pin.

Development tools for the IBM PC include a relocatable assembler, a linker loader, and an ANSI-C compiler. Also, the development tools include a simulator/debugger, a cross assembler for the TMS320 family assembly code and a hardware emulator.

#### Notes:

All Signals with a preceding front slash, "/", are active Low, e.g.: B//W (WORD is active Low); /B/W (BYTE is active Low, only).

Power connections follow conventional descriptions below:

| Connection      | Circuit                | Device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power<br>Ground | V <sub>cc</sub><br>GND | $egin{array}{c} egin{array}{c} \egin{array}{c} \egin{array}{c} \egin{array}{c} \egin{array}{c} \egin{array}{c} \egin{array}$ |

DC-4128-00 (12-2-92)

# **GENERAL DESCRIPTION** (Continued)

**Functional Block Diagram**

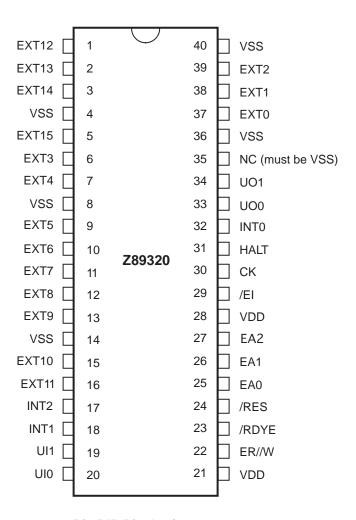

## **PIN DESCRIPTION**

**40-Pin DIP Pin Assignments**

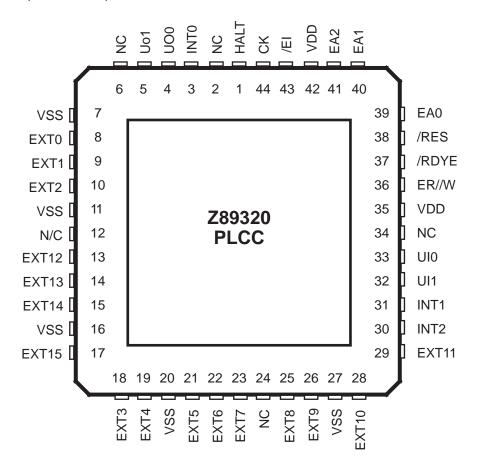

# PIN DESCRIPTION (Continued)

44-Pin PLCC Pin Assignments (Standard Mode)

#### **ABSOLUTE MAXIMUM RATINGS**

| Storage temperature range                  | -65°C to +150°C                  |

|--------------------------------------------|----------------------------------|

| Lead temperature (if packaged)             | 300°C for 10 sec.                |

| V <sub>DD</sub> Voltage to V <sub>SS</sub> | -0.5 to 7.0V                     |

| All other pins                             | $V_{DD}$ +0.5V to $V_{SS}$ -0.5V |

Stresses greater than those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; operation of the device at any condition above those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for extended period may affect device reliability.

#### STANDARD TEST CONDITIONS

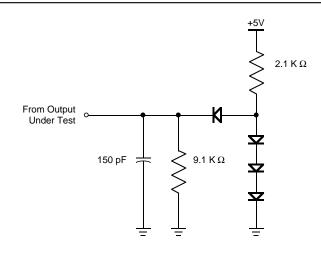

The characteristics listed below apply for standard test conditions as noted. All voltages are referenced to ground. Positive current flows into the referenced pin (Test Load Diagram).

**Test Load Diagram**

#### DC ELECTRICAL CHARACTERISTICS

$(V_{DD} = 5V \pm 5\%, T_A = 0$ °C to +70°C unless otherwise specified)

| Symbol                                                | Parameter                                                                    | Condition                                           | Min.                 | Max.                | Units        |

|-------------------------------------------------------|------------------------------------------------------------------------------|-----------------------------------------------------|----------------------|---------------------|--------------|

| I <sub>DD</sub>                                       | Supply Current                                                               | V <sub>DD</sub> =5.25V<br>fclock=10 MHz             |                      | 40                  | mA           |

| $I_{\rm DC}$                                          | DC Power Consumption                                                         | $V_{DD} = 5.25 V$                                   | 1 mA                 | 5                   | mA           |

| V <sub>IH</sub><br>V <sub>IL</sub><br>IL              | Input High Level<br>Input Low Level<br>Input Leakage                         |                                                     | 0.9 V <sub>DD</sub>  | 0.1 V <sub>DD</sub> | V<br>V<br>μΑ |

| V <sub>OH</sub><br>V <sub>OL</sub><br>I <sub>FL</sub> | Output High Voltage<br>Output Low Voltage<br>Output Floating Leakage Current | I <sub>OH</sub> =-100 μA<br>I <sub>OL</sub> =0.5 mA | V <sub>DD</sub> -0.2 | 0.5<br>5            | V<br>V<br>μΑ |

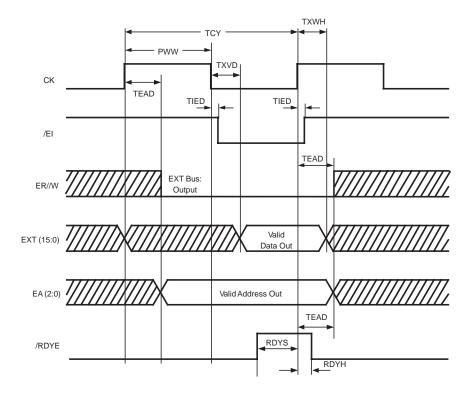

# **AC TIMING DIAGRAM**

WRITE to external device timing

**READ** from external device timing

## **AC ELECTRICAL CHARACTERISTICS**

$(V_{DD} = 5V \pm 5\%, T_{A} = 0^{\circ}C \text{ to } +70^{\circ}C \text{ unless otherwise specified})$

| Symbol | Parameter                     | Min. | Max. | Units |

|--------|-------------------------------|------|------|-------|

| TCY    | Clock Cycle Time              | 100  | 1000 | ns    |

| PWW    | Clock Pulse Width             | 45   |      | ns    |

| Tr     | Clock Rise Time               | 2    | 4    | ns    |

| Tf     | Clock Fall Time               | 2    | 4    | ns    |

| TEAD   | EA,ER//W Delay from CK        | 15   | 25   | ns    |

| TXVD   | EXT Data Output Valid from CK | 5    | 25   | ns    |

| TXWH   | EXT Data Output Hold from CK  | 15   |      | ns    |

| TXRS   | EXT Data Input Setup Time     | 15   |      | ns    |

| TXRH   | EXT Data Input Hold from CK   | 0    | 15   | ns    |

| TIED   | /EI Delay Time from CK        | 0    | 5    | ns    |

| RDYS   | Ready Setup Time              | 10   |      | ns    |

| RDYH   | Ready Hold Time               | 0    |      | ns    |

#### Low Margin:

Customer is advised that this product does not meet Zilog's internal guardbanded test policies for the specification requested and is supplied on an exception basis. Customer is cautioned that delivery may be uncertain and that, in addition to all other limitations on Zilog liability

stated on the front and back of the acknowledgement, Zilog makes no claim as to quality and reliability under the CPS. The product remains subject to standard warranty for replacement due to defects in materials and workmanship.

$\ensuremath{\mathsf{IBM}}$  is a registered trademark of International Business Machines Corporation.

© 1992 by Zilog, Inc. All rights reserved. No part of this document may be copied or reproduced in any form or by any means without the prior written consent of Zilog, Inc. The information in this document is subject to change without notice. Devices sold by Zilog, Inc. are covered by warranty and patent indemnification provisions appearing in Zilog, Inc. Terms and Conditions of Sale only. Zilog, Inc. makes no warranty, express, statutory, implied or by description, regarding the information set forth herein or regarding the freedom of the described devices from intellectual property infringement. Zilog, Inc. makes no warranty of mer-

chantability or fitness for any purpose. Zilog, Inc. shall not be responsible for any errors that may appear in this document. Zilog, Inc. makes no commitment to update or keep current the information contained in this document.

Zilog, Inc. 210 East Hacienda Ave. Campbell, CA 95008-6600 Telephone (408) 370-8000 FAX 408 370-8056