# Digital Television DVB-T-On-a-Chip Processor

Data Sheet

**Features**

DTV-SoC for Digital Terrestrial Television (DTT)

- On-chip DVB-T COFDM demodulator with FEC.

- 6 Video DACs on-chip, for Composite or Component (RGB or Y U/V) Analog Video

- Twin PAL/NTSC DENCs

- Low Power (<1.4W Typical)</li>

- Low Component Count

- · Unified SDRAM controller

- I<sup>2</sup>S Digital Audio Input

- I<sup>2</sup>S and S/PDIF Digital Audio outputs

- · MPEG-2 Audio & Video decoders

- PowerPC 405<sup>TM</sup> CPU Core with 16k/16k cache, Memory manager and Virtual memory system

- Complete Linux-based Software Development Kit (SDK)

- IDE interface

- Inputs for external MPEG-2 Transport Streams, allowing support for external demodulators (e.g. Cable TV, Satellite TV)

- · Conditional Access (CA) DVB-descrambler

Issue 1.0

November 2002

#### **Ordering Information**

ZL10310/GAC 388 ball EPBGA ZL10311/GAC 388 ball EPBGA

$0^{0}$ C to + $70^{0}$ C

- · Smart Card Interface

- Infrared & UART interface

- DVB-compatible Common Interface (CI) control and bitstream interfaces

- Multi-stream multiplexing to support internal and external demodulators

- External Modem support interface

- Supports Macrovision<sup>TM</sup> Copy Protection -(ZL10311 only; available to Macrovision license holders only)

- Dolby<sup>®</sup> Digital\* Decoding (ZL10311 only; available to Dolby<sup>®</sup> Digital\* license holders only -\*awaiting certification)

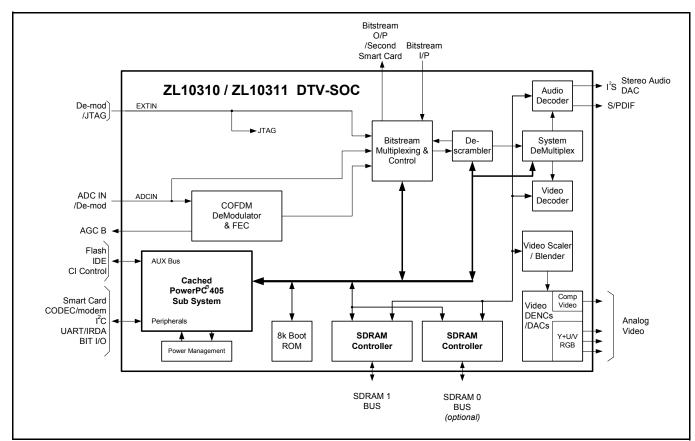

Figure 1 - Block Diagram of ZL10310 and ZL10311

#### **Applications**

- Low power, small footprint TV adaptors

- Integrated Digital Televisions (iDTV)

- Digital terrestrial set-top boxes

- DTT / DVD Combo

- DVB-T radio receivers

- Terrestrial / Satellite Combo

- Terrestrial / Cable Combo

- Terrestrial / IP (Internet Protocol) Combo

#### **Description**

Zarlink Semiconductor has responded to market demand by integrating its key DVB-T compliant COFDM demodulation technology with Set Top Box functionality (MPEG-2 A/V decoder and system interfaces) together with a high performance CPU to offer a "DVB-T On-a-Chip" solution.

The ZL10310 DVB-T On-a-Chip, can address a wide range of DVB-T consumer electronic products. At the entry level it can be used to build ultra-compact Free-To-View Digital TV adaptors (such as for FreeView in the UK), yet consumes less than 4W of power in full operational mode.

This level of compactness also considerably eases the integration of DVB-T receiver technology inside integrated Digital TV sets (iDTV's) where space considerations and thermal management are key design issues.

The ZL10310 is based upon an industry standard PowerPC 405<sup>TM</sup> RISC processor, which has Virtual and Memory Management sub-systems. This permits the device to be effectively deployed in compelling applications such as interactive Digital TV which are able to exploit the superior processing performance offered by the PowerPC® processor core.

The PowerPC<sup>®</sup> provides an ideal platform for running robust open standard operating systems such as Linux which can benefit system developers in a number of key areas:

- Unified software development environment, from entry level basic channel zapper systems through to fully interactive high performance Digital Set Top Boxes.

- Re-use of software code from multiple projects

- Exploit software code developed in the Linux community.

- Low cost-per-seat software development environment.

- Familiar software development environment.

- Royalty free.

Also available is the ZL10311 DVB-T On-a-Chip, which additionally offers Dolby<sup>®</sup> Digital<sup>1</sup> multi-channel audio decoding, and Macrovision<sup>TM</sup> Copy Protection for applications requiring Dolby<sup>®</sup> Audio and Pay TV services.

<sup>1.</sup> The ZL10311 device is awaiting Dolby Certification

ZL10310/ZL10311

#### **Table of Contents**

| 1.0 Device Overview                                                   | 4   |

|-----------------------------------------------------------------------|-----|

| 2.0 Device Interfaces                                                 | 4   |

| 3.0 Typical Digital Television (DTV) Receiver                         |     |

| 4.0 Functional Blocks Overview                                        |     |

| 4.1 Boot ROM                                                          |     |

| 4.2 Clock Generation Block                                            |     |

| 4.3 Coded Orthogonal Frequency Division Multiplex (COFDM) Demodulator |     |

| 4.4 MPEG Audio Decoder                                                |     |

| 4.5 MPEG-2 Video Decoder                                              |     |

| 4.6 PowerPC 405TM Processor                                           | 8   |

| 4.7 Transport Engine                                                  |     |

| 4.8 Video Display System                                              | 9   |

| 5.0 Physical Specification                                            |     |

| 6.0 ZL10310/ZL10311 388-pin Package Pin Descriptions                  |     |

| 6.1 Pin Types                                                         |     |

| 6.2 Front End Interfaces                                              |     |

| 6.3 Video DAC Outputs                                                 | 14  |

| 6.4 SDRAM Interfaces                                                  |     |

| 6.5 Bit Stream Interfaces                                             |     |

| 6.6 Auxiliary External Bus                                            |     |

| 6.7 Peripheral Port                                                   |     |

| 6.8 Modem/Codec Interface                                             |     |

| 6.9 Smart Card Interface                                              |     |

| 6.10 General Purpose Input Output Interfaces                          |     |

| 6.11 Simplified General Purpose Input Output Interface                |     |

| 6.12 Inter Integrated Circuit (I2C) Interface                         |     |

| 6.13 Inter IC Sound (I2S) Audio Interface                             |     |

| 6.14 Clock and Reset Interface                                        |     |

| 6.15 Power Supply Pins                                                |     |

|                                                                       |     |

| 7.0 Characteristics                                                   |     |

| / LAC 300 DC Electrical Characteristics                               | 310 |

IBM®, the IBM Logo, PowerPC® and PowerPC405<sup>TM</sup> are trademarks of International Business Machines Corporation.

Dolby<sup>®</sup> is a trademark of Dolby Laboratories. Supply of this implementation of Dolby Technology does not convey a license or imply a right under any patent, or any other Industrial or Intellectual Property Right of Dolby Laboratories, to use this implementation in any finished end-user or ready-to-use final product. It is hereby notified that a license for such use is required from Dolby Laboratories<sup>1</sup>.

This device is protected by US patent numbers 4631603, 4577216 and 4819098 and other intellectual property rights. Use of the Macrovision anticopy process in the device is licensed by Macrovision for non-commercial, home and limited exhibition use only. Reverse engineering or disassembly is prohibited. A valid Macrovision license must be in effect between the purchaser of the ZL10311 IC and Macrovision Corporation. Additional per-chip royalties may be required and are payable by the purchaser to Macrovision.

<sup>1.</sup> The ZL10311 device is awaiting Dolby Certification

#### 1.0 Device Overview

Zarlink Semiconductor has designed the ZL10310 and ZL10311 System On a Chip (SoC) devices specifically for DVB-T applications. Integrating a high performance PowerPC 405<sup>TM</sup> processor with robust industry proven MPEG-2 audio and video decoding, OSD and a COFDM demodulator, the ZL10310 and ZL10311 deliver the performance and functionality required for advanced Digital TV entertainment products. It enables the rapid design and manufacture of cost-effective iDTV and Digital Audio Visual Home Entertainment Centers.

The enhanced ZL10311 also supports DVD playback with up to six Dolby<sup>®</sup> Digital<sup>1</sup> audio channels. In addition, by integrating the COFDM demodulator, the ZL10310 and ZL10311 enable the implementation of very small footprint TV Adaptor modules.

#### 2.0 Device Interfaces

The following peripheral interfaces are available to the user. Apart from possible level translation and connector buffering, no external devices are required to support any of the interfaces.

- 10-bit input that may be configured for an ADC input to the internal COFDM demodulator

- Additional input bus for additional MPEG-2 Transport Sources

- AGC (PWM) outputs for a terrestrial tuner

- · Serial control port for a digital tuners

- Common interface control and bitstream interfaces for an external descrambler

- Normal PC (PCMCIA) memory module interface for local software updates

- Unified 64 Mbit SDRAM interface for all decoders and PowerPC 405<sup>TM</sup>

- Additional SDRAM interface for high end systems requiring increased memory bandwidth

- · Static memory interface for Flash and external peripherals

- IDE/ATAPI interface for hard disk and DVD drives

- · External DMA channel and interrupts

- Six analog video outputs give full flexibility on RGB, S-VHS, and composite signals (with and without OSD)

- I<sup>2</sup>S input port from external Digital Stereo source

- Three I<sup>2</sup>S ports to external audio DACs for main, surround, and centre channels

- Dolby<sup>®</sup> surround sound control signals

- Sony/Philips Digital InterFace (S/PDIF)

If not required in a particular system, any of the peripheral interfaces can be replaced by individual I/O bits from internal general purpose registers. These can then be used for additional purpose, such as interfacing to switches and displays.

- Full RS232 interface to an external modem or a 4 wire interface to a Codec

- IRDA interface or an additional asynchronous serial interface

- · Synchronous serial interface for EEPROM, etc.

- Two Smart card Interfaces (one instead of a Common Interface)

- General purpose I<sup>2</sup>C interface

- · General purpose timer for Infrared (IR) decoding

- General purpose individual bit I/Os

<sup>1.</sup> The ZL10311 device is awaiting Dolby Certification

Data Sheet ZL10310/ZL10311

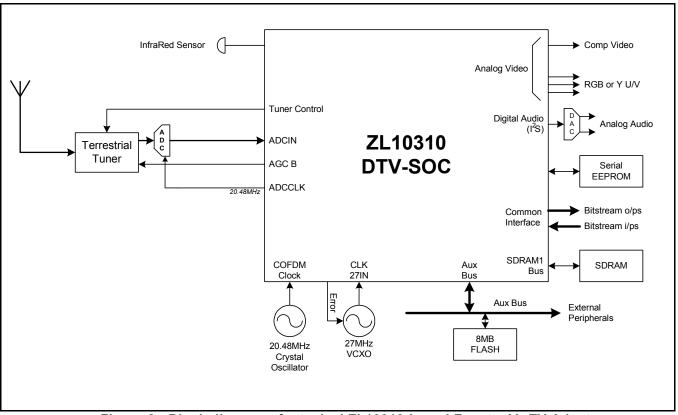

Figure 2 - Block diagram of a typical ZL10310-based Free to Air TV Adaptor

## 3.0 Typical Digital Television (DTV) Receiver

Figure 2 shows a typical Free to Air TV receiver block diagram employing a ZL10310 DTV-SoC device. In its minimal configuration, the ZL10310 DTV-SoC device only requires a single 64 Mbit SDRAM, an audio DAC, and a Flash ROM, which are in addition to a DVB-T tuner front end and a 10-bit analog to digital converter.

The Terrestrial Tuner section performs an independent down conversion of the received DVB-T signal from the Antenna, to an IF frequency in the range of 30MHz to 57MHz, dependent on television system (typically 36.17MHz Center Frequency, with ±4MHz span). The analogue IF is then converted to the digital domain, with a 10-bit ADC, clocked at 20.48MHz and the resulting Digital output is centered on 15.69MHz. This Digital signal is applied to the ZL10310 via the ADC IN[9:0] input pins, in the form of a 10-bit parallel signal.

The ZL10310 converts the digitized IF from a Terrestrial TV Tuner into an MPEG-2 Transport Stream, which can be optionally de-scrambled (if CA scrambling is used by the broadcaster), and de-multiplexed into separate Packetised Elementary Streams (PES), which are routed to the MPEG Audio and Video decoders, and SI data to the PowerPC 405<sup>TM</sup> subsystem.

Decoded Video can then be mixed and optionally scaled with On-Screen Display (OSD) Graphics generated by the DTV application software. The resultant combination of video and graphics are then routed to the PAL/NTSC Digital ENCoders (DENCs) for display on the TV via the on-chip 10-bit video DACs.

Decoded Audio is output directly from the audio decoder sub-system to the I<sup>2</sup>S and S/PDIF (Sony/Philips Digital InterFace) outputs.

## 4.0 Functional Blocks Overview

#### 4.1 Boot ROM

Program execution on the Power PC® normally starts from address 0xFFFFFFC after the internal reset has gone inactive. This would normally be an address in the external Flash ROM (enabled by BI\_CS0), but, by forcing the SGPIO2\_3 pin low during reset, it is possible to boot from the Internal 8k Boot ROM. The ZL10310 and ZL10311 devices contain an 8k Boot ROM containing code, which is executed under the noted conditions above following a complete system reset (i.e. when main power has been removed from the ZL10310 or ZL10311).

The code installed on the Boot ROM, allows the ZL10310/ZL10311 to undertake any of the following 4 functions after a complete reset:

- 1. Enter ISP (in-system programmable) mode, in which the software in the internal Boot ROM will try booting from an SPI or I<sup>2</sup>C EEPROM.

- 2. Try booting from an Atmel Serial Flash device (AT45xxxxx) first, if that fails then enter ISP mode.

- 3. Try booting from an asynchronous parallel flash device connected to the EBIU bus (CS0) first. If that fails, then try booting from SPI or I<sup>2</sup>C EEPROM or Serial Flash.

- 4. Enter debug/monitor mode in which a command prompt is available for debugging registers, downloading code, etc.

#### 4.2 Clock Generation Block

The ZL10310/ZL10311 devices use two separate external clock sources to provide all the clocks required; a 27MHz external Voltage Controlled crystal Oscillator (VCXO), and a 20.48MHz external Crystal Oscillator.

A standard 27MHz input to the systems PLL is supplied from an external VCXO. Outputs from this PLL are used to clock the various internal MPEG decoders, the PowerPC® micro controller system, and the external SDRAM. The frequency can be adjusted in the ppm range, using a voltage produced by the pulse width modulated frequency error signal, available from GPIO port GP29.

The 27MHz input also drives a separate audio PLL that is dedicated to providing 256/512 times the audio sampling rate for the audio decoder and external audio DAC.

The COFDM de-modulators have their own PLL driven from an internal 20.48MHz oscillator. An external crystal is required for this oscillator.

Data Sheet ZL10310/ZL10311

#### 4.3 Coded Orthogonal Frequency Division Multiplex (COFDM) Demodulator

The COFDM demodulator is used to demodulate a digitized COFDM modulated IF signal from the TV Tuner, and ultimately convert the resulting MPEG-2 Transport Stream to the MPEG-2 demultiplexer.

The Digitized IF is converted to a complex Baseband signal centered on zero frequency. It also removes adjacent channel interference prior to a Time-to-Frequency Fast Fourier Transform (FFT). The resulting signals are then sent to a digital re-timing block, symbol sync, carrier recovery, and timing recovery. An AGC signal, with a variable mark space ratio, is provided to control the signal levels in the tuner sections of the receiver. Forward Error Correction (FEC) is performed by Viterbi decoding of the convolutional coded data, followed by de-interleaving, Reed-Solomon decoding, and energy dispersal de-randomising. The output is MPEG-2 Transport Stream packets, in byte format.

The COFDM demodulator is fully compliant with the ETSI 300 744 and Digital Television Group (DTG) specifications. Key features are:

- FFT processor operates in 2k and 8k carrier mode.<sup>1</sup>

- · All hierarchical and non-hierarchical constellations.

- Automatic digital carrier recovery over a wide range of offsets without the need for AFC

- Automatic digital carrier recovery without the need for a VCXO

- Common phase error correction

- Channel correction using time and frequency filtering

- · Automatic co channel protection, frame sync, and fast channel re- acquisition

- · Internal controller handles all tracking and acquisition

- Viterbi decoding with code rates of 1/2, 2/3, 3/4, 5/6, 6/7, and 7/8

- · Automatic synchronization and code rate detection

- Constraint length K = 7

- · Trace back depth of 128

- · De-interleaver followed by DVB Reed Solomon error correction

- De-randomizer and common interface formatting

#### 4.4 MPEG Audio Decoder

The MPEG Audio Decoder produces dual channel outputs from MPEG -1 or MPEG -2 Transport Streams with a maximum rate of 640 kbit/sec. It supports sampling rates of 32, 44.1, and 48 KHz, plus the half rate options. All sampling rates, plus 512/256 Fs, are produced from an internal PLL. A version of the device is available which produces six channels of audio output for holders of the Dolby<sup>®</sup> Digital<sup>2</sup> License.

- · Decodes MPEG-1 and dual channel MPEG-2 audio

- Performs MPEG-1 audio parsing and MPEG-2 Packetised Elementary Stream (PES) audio parsing, or accepts audio elementary streams

- Supports 32kHz, 44.1 kHz, and 48 kHz sampling rates plus the half rate options

- All sampling rates, plus 512/256 Fs, derived from an internal PLL

- 64 step audio attenuation with smooth step transitions

- SPDIF output meeting IEC1937 specifications

- Re-locatable ancillary data region

- Audio Clip Mode

- Dolby<sup>®</sup> AC3 option<sup>2</sup>

<sup>1.</sup> For details on 8k carrier performance and use, please consult Zarlink Field Applications

<sup>2.</sup> The ZL10311 device is awaiting Dolby Certification

#### 4.5 MPEG-2 Video Decoder

The MPEG-2 Video Decoder provides complete decoding and synchronized playback of MPEG-2 MP@ML (Main Profile at Main Level) video streams. It supports the decoding of still pictures as well as moving video, with error concealment when necessary. A command driven local controller minimizes the amount of application software needed to control the decoding / channel change process.

The decoder accepts PES from the Transport De-multiplexer, with average rates of up to 15 Mbps. PES header parsing supports the extraction of Presentation Time Stamp (PTS) values, which are then used by the audio/ video synchronization hardware. PES or ES streams can be directly decoded from SDRAM in the Video Clip mode of operation.

#### Feature summary:

- Packetised MPEG-2 MP @ ML video streams from the transport demultiplexer or from SDRAM

- MPEG-1 video (ES) streams from SDRAM

- Sustained bit rates from 1.5 Mbps to 15 Mbps.

- Local processor driven by commands from the application processor

- · Sophisticated error concealment based on the use of stored motion vectors from the previous row

- Supports the decoding of still images

- Automatic or manual image re-sizing

- Conversion of MPEG-1, 24 Hz progressive scan, pictures to 60 Hz interlaced (3:2 pull-down)

#### 4.6 PowerPC 405<sup>TM</sup> Processor

An integrated PowerPC 405<sup>TM</sup> processor core is provided for applications and control software, and this provides approx. 150 Drhystone MIPS with a clock of 108 MHz.

It has instruction and data caches with lock down facilities such that defined areas can be used as general purpose ram. The processor has its own internal bus to which is attached the caches, all the peripherals, and a DMA controller. Code can thus be executed, using internal resources, whilst the MPEG decoders are using the SDRAM.

This processor bus is also connected to an auxiliary external bus, which is used for Flash code transfer during the power on routine, and for Flash write operations. PCMCIA, and IDE data transfers also use this bus to provide data and address signals, but their respective control signals have dedicated pins. A bridge to the internal multi-master bus provides software access to the external SDRAM.

All internal and external memory is in a unified address space, and a DMA controller supports high speed data transfers. Controllers are provided for two smart cards, an RS232 modem, a serial Codec, an I<sup>2</sup>C master, a synchronous serial port, and an IRDA interface. Individual bit I/O is also supported.

#### **Key Features:**

- PowerPC 405<sup>TM</sup> Processor Core running at 108 MHz

- Integrated instruction and data caches (16k/16k) with lock down

- Integrated set top box peripheral controllers

- Four channel DMA controller for peripheral and data transfers

- Dedicated internal processor bus with its own SDRAM controller and auxiliary bus

- Bridge to the decoder multi-master bus and shared SDRAM

- · Real Time Counters

- Watch dog timer

- · Interrupt Controller

Data Sheet ZL10310/ZL10311

#### 4.7 Transport Engine

The ZL10310/ZL10311 devices contain a dedicated hardware implementation of an MPEG/DVB transport stream de-multiplexer, with the configuration of this hardware controlled by application software. Included in the hardware are synchronization, Packet Identifier (PID) filtering, clock recovery, de-scrambling, and table section filtering. PID filtered packets are stored in a local buffer, which can hold up to 10 packets before they are moved to the decoders or to memory queues in SDRAM. The queues are used for the tables containing system information. Packets for three destinations can be moved concurrently out of the buffer.

The hardware acts in conjunction with a Transport Assist Processor, and the resultant hardware/software combination gives increased adaptability and extended processing capability. Further parsing and filtering is possible, and interrupts can be generated to notify the processor when a given condition has been met. The transport assist processor can then read and manipulate packets whilst they are still in the transport packet buffer. It can then allow data to pass through to SDRAM or the decoders, or can record status information and optionally interrupt the application.

#### Key Features:

- 32 PID values can be used to filter the transport stream

- · Flexible, hardware based, section filtering

- 64, 4 byte, filter blocks.

- Filter blocks can be cascaded to provide deep filtering when necessary

- · Hardware Cyclical Redundancy Check (CRC) checking

- · Captured data is transferred to one of thirty two queues in SDRAM

- · Options to transfer complete transport packets with or without headers, or sections

- · Adaptation fields can be delivered to a separate queue

- · Hardware to extract PCR values with option for software filtering to remove long term jitter

- · Comprehensive error detection hardware

- · Integrated DVB descrambler

#### 4.8 Video Display System

The Video Display System provides multi-layered video. This features the On-Screen Display (OSD) for menuing and MHEG-5, the Decoded Video Presentation system, and a Video Blending capability to merge the OSD and Video.

The On-Screen Display system is designed to meet or exceed the specifications of major European broadcasters. The final image on the screen is constructed from five separate planes using a fixed display hierarchy. The screen hierarchy consists of:

- 1. Cursor plane (Top)

- 2. Region-based graphics plane (typically used for EPG and System menus)

- 3. Video plane

- 4. Still image plane (typically used for MHEG-5)

- 5. Background plane

All planes, apart from the background plane, can be separately enabled. The graphics and image planes are region based, and driven by means of bitmaps controlled by a link-list processor. They can operate independently, but have nearly identical operational controls. The size of a bitmap region can vary between 4 pixels wide by 2 pixels deep, and 1K pixels wide and 1K pixels deep. The color resolution of a pixel within a region can be defined by 2, 4, 8, or 16 bits. The 16-bit option is for direct colors; the other options use color look up tables.

The Video Presentation system is used to scale and process a decoded Video signal. Decoded Video is stored in Field Stores contained in external SDRAM memory. Prior to display it can be automatically scaled from the original resolution and aspect ratio up to PAL or NTSC full screen size. If the encoded image has a 16:9 aspect ratio, but the display has a 4:3 aspect ratio, then any horizontal scaling factor necessary to fill the screen must be adjusted by

a further factor of 4/3. Alternatively, a factor of 3/4 can be applied vertically (letter box mode). Video is displayed at the standard PAL or NTSC field rates. Synchronization signals for video presentation can be provided by either the video decoder itself (master mode), or the decoder can slave to incoming signals.

The Video Blending System is used to blend the outputs from separate Digital Encoded Video (DENC) blocks for the Video and OSD systems on-chip:

- 1. RGB Red Green Blue

- 2. Y U/V

- 3. CVBS Chroma Video Blanking and Sync

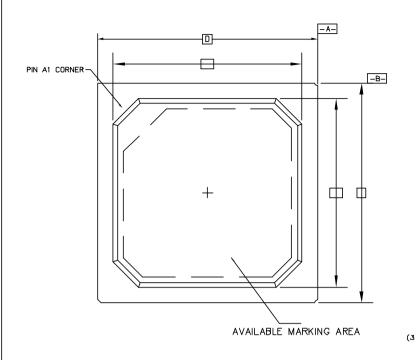

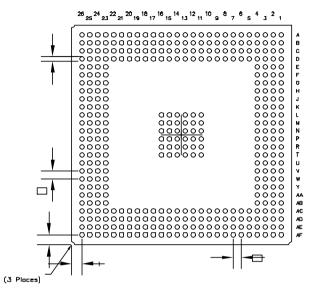

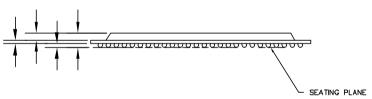

#### 5.0 Physical Specification

The device is contained in a 388-ball Enhanced Plastic Ball-Grid Array (388 EPBGA) package:

- Body Size: 27mm x 27mm

- · Ball Count: 388 (includes 36 Thermal Balls)

- Ball Pitch: 1.0mm

- Ball Matrix: 26 x 26 (partially populated with a 6 x 6 GND matrix in the centre)

- · Ball Diameter 0.60mm

- Total Package Thickness 2.65mm

Package is viewed from the top side (i.e. through top of the package). Note ball A1 is non-chamfered corner.

Figure 3 - Package View and Ball Positions

#### 6.0 ZL10310/ZL10311 388-pin Package Pin Descriptions

This section explains the ZL10310 and ZL10311 device pin functions. The following tables are segmented by signal functions. Many of the pins listed below have multiple functions, and in these cases there is information on how the multiplexed function connects to the pin.

Many references are made to register settings throughout the Pin Descriptions. The details of the ZL10310 and ZL10311 registers can be found in the Hardware Design Manual for the ZL103xx family of Integrated Digital Television Processors (Publication DM5797), available to customers on request, subject to NDA.

#### 6.1 Pin Types

- An Input Type with no designator indicates that the signal must be produced by a device using 3.3V outputs, and ESD protection is provided. There is no internal pull up, so unused inputs should be tied high or low.

- Pin Type indicates that the pin can be programmed with control bits to be used as an input or an output.

- B Pin Type indicates that the pin function can alternate between an input and output depending on the use at that instant i.e. it is Bi-directional. Out characteristics are the same as an Out pin.

- OD is an open drain Output.

- O is a standard 3.3 V, 65 ohm, output, unless otherwise specified. DC drive is 8.2mA/5.4mA @ VH/VL respectively. Maximum slew rate is 75mA/ns, unless otherwise specified.

- 5V is a 5V tolerant Input or Output. An Input Type with a 5V designator indicates that the input tolerates 5V signals. There is no internal pull up.

#### 6.2 Front End Interfaces

| Pin Name  | Pin<br>No. | Function                 | Pin<br>Type | Description                                                                                                                   | Notes |

|-----------|------------|--------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------|-------|

| ADCCLK    | R02        | ADCCLK                   | 0           | Sampling Clock Output to External Tuner IF Analog to Digital Converter. Clock = 20.48MHz.                                     |       |

| AGC[0]    | L02        | Tuner AGC control        | O 5V        | Master AGC Control Output to External TV Tuner                                                                                | 1     |

| AGC[1]    | M03        | Tuner AGC control offset | O 5V        | Secondary AGC Control Output to External TV Tuner. Used to provide a differential AGC feed to external TV Tuner, if required. | 1     |

| GPP[0]    | L01        | Tuner_SCL                | O 5V        | External TV Tuner Control Bus - Clock Output                                                                                  | 1, 6  |

| GPP[1]    | N04        | Tuner_SDA                | B 5V        | External TV Tuner Control Bus - Data Input/Output.                                                                            | 1, 6  |

| EXT_IN[0] | K01        | ED1_MDO[7]<br>(MSB)      | I           | External Demodulator 1 Digital Input -<br>Data Bit 7 (MSB)                                                                    | 5, 7  |

|           |            | DV2_IN_DATA[7]<br>(MSB)  | I           | Reserved                                                                                                                      | 7     |

|           |            | RW_TDO                   | 0           | Debug Interface - JTAG TDO (Data Out)                                                                                         | 3     |

| Pin Name  | Pin<br>No. | Function                | Pin<br>Type | Description                                                                                                                              | Notes   |

|-----------|------------|-------------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------|---------|

| EXT_IN[1] | K02        | ED1_MDO[6]              | I 5V        | External Demodulator 1 Digital Input - Data Bit 6                                                                                        | 1, 5, 7 |

|           |            | RW_TDI                  | I 5V        | Debug Interface - JTAG TDI (Data In)                                                                                                     | 1, 3    |

|           |            | DA_SER_DATAI            | I 5V        | Digital Audio Serial Data Input. Main left and right serial audio data at a rate of 64fs. Signal routed through to GP12 (not bonded out) | 1, 4    |

| EXT_IN[2] | J01        | ED1_MDO[5]              | I           | External Demodulator 1 Digital Input - Data Bit 5                                                                                        | 5, 7    |

|           |            | DV2_IN_DATA[6]          | 1           | Reserved                                                                                                                                 | 7       |

|           |            | RW_HALT                 | I           | Debug Interface - JTAG Halt                                                                                                              | 3       |

| EXT_IN[3] | L03        | ED1_MDO[4]              | I           | External Demodulator 1 Digital Input - Data Bit 4                                                                                        | 5, 7    |

|           |            | DV2_IN_DATA[5]          | I           | Reserved                                                                                                                                 | 7       |

|           |            | RW_TMS                  | I           | Debug Interface - JTAG TMS                                                                                                               | 3       |

| EXT_IN[4] | J02        | ED1_MDO[3]              | I           | External Demodulator 1 Digital Input - Data Bit 3                                                                                        | 5, 7    |

|           |            | DV2_IN_DATA[4]          | 1           | Reserved                                                                                                                                 | 7       |

|           |            | RW_TCK                  | 1           | Debug Interface - JTAG TCK                                                                                                               | 3       |

| EXT_IN[5] | L04        | ED1_MDO[2]              | I           | External Demodulator 1 Digital Input - Data Bit 2                                                                                        | 5, 7    |

|           |            | DV2_IN_DATA[3]          | I           | Reserved                                                                                                                                 | 7       |

|           |            | Test[0]                 | I           | Test Mode A - Test Pin 0                                                                                                                 |         |

| EXT_IN[6] | K03        | ED1_MDO[1]              | I           | External Demodulator 1 Digital Input - Data Bit 1                                                                                        | 5, 7    |

|           |            | DV2_IN_DATA[2]          | I           | Reserved                                                                                                                                 | 7       |

|           |            | Test[1]                 | I           | Test Mode A - Test Pin 1                                                                                                                 |         |

| EXT_IN[7] | H02        | ED1_MDO[0]<br>(LSB)     | I           | External Demodulator 1 Digital Input - Data Bit 0 (LSB)                                                                                  | 5, 7    |

|           |            | DV2_IN_DATA[1]          | I           | Reserved                                                                                                                                 | 7       |

|           |            | Test[2]                 | I           | Test Mode A - Test Pin 2                                                                                                                 |         |

| EXT_IN[8] | G01        | ED1_MVAL                | I           | External Demodulator 1 Digital Input - Data Valid Input                                                                                  | 5       |

|           |            | DV2_IN_DATA[0]<br>(LSB) | I           | Reserved                                                                                                                                 | 7       |

|           |            | Test[3]                 | I           | Test Mode A - Test Pin 3                                                                                                                 |         |

| EXT_IN[9] | J03        | ED1_MCLK                | I           | External Demodulator 1 Digital Input - Clock Input                                                                                       | 5       |

|           |            | DV2_Pixel_Clk           | I           | Reserved                                                                                                                                 |         |

|           |            | Test[4]                 | I           | Test Mode A - Test Pin 4                                                                                                                 |         |

| Pin Name  | Pin<br>No. | Function                | Pin<br>Type | Description                                             | Notes   |

|-----------|------------|-------------------------|-------------|---------------------------------------------------------|---------|

| ADC_IN[0] | V03        | COFDM_ADCIN[8]<br>(MSB) | I           | COFDM Digital Input from Ext. ADC - Data Bit 8 (MSB)    | 2, 5, 7 |

|           |            | DV2_IN_DATA[7]<br>(MSB) | I           | Reserved (when EXT_IN[0] used for JTAG in Debug)        | 7       |

|           |            | ED2_MDO[7]<br>(MSB)     | I           | External Demodulator 2 Digital Input - Data Bit 7 (MSB) | 7       |

| ADC_IN[1] | W03        | COFDM_ADCIN[7]          | I           | COFDM Digital Input from Ext. ADC - Data Bit 7          | 2, 5, 7 |

|           |            | ED2_MDO[6]              | I           | External Demodulator 2 Digital Input - Data Bit 6       |         |

| ADC_IN[2] | AA02       | COFDM_ADCIN[6]          | I           | COFDM Digital Input from Ext. ADC - Data Bit 6          | 2, 5, 7 |

|           |            | DV2_IN_DATA[6]          | I           | Reserved (when EXT_IN[2] used for JTAG in Debug)        | 7       |

|           |            | ED2_MDO[5]              | I           | External Demodulator 2 Digital Input - Data Bit 5       | 7       |

| ADC_IN[3] | AB01       | COFDM_ADCIN[5]          | I           | COFDM Digital Input from Ext. ADC - Data Bit 5          | 2, 5, 7 |

|           |            | DV2_IN_DATA[5]          | I           | Reserved (when EXT_IN[3] used for JTAG in Debug)        | 7       |

|           |            | ED2_MDO[4]              | I           | External Demodulator 2 Digital Input - Data Bit 4       | 7       |

| ADC_IN[4] | Y03        | COFDM_ADCIN[4]          | I           | COFDM Digital Input from Ext. ADC - Data Bit 4          | 2, 5, 7 |

|           |            | DV2_IN_DATA[4]          | I           | Reserved (when EXT_IN[4] used for JTAG in Debug)        | 7       |

|           |            | ED2_MDO[3]              | I           | External Demodulator 2 Digital Input - Data Bit 3       | 7       |

| ADC_IN[5] | AB02       | COFDM_ADCIN[3]          | I           | COFDM Digital Input from Ext. ADC - Data Bit 3          | 2, 5, 7 |

|           |            | DV2_IN_DATA[3]          | I           | Reserved (when EXT_IN[5] used for JTAG in Debug)        | 7       |

|           |            | ED2_MDO[2]              | I           | External Demodulator 2 Digital Input - Data Bit 2       | 7       |

| ADC_IN[6] | AC01       | COFDM_ADCIN[2]          | I           | COFDM Digital Input from Ext. ADC - Data Bit 2          | 2, 5, 7 |

|           |            | DV2_IN_DATA[2]          | I           | Reserved                                                | 7       |

|           |            | ED2_MDO[1]              | I           | External Demodulator 2 Digital Input - Data Bit 1       | 7       |

| ADC_IN[7] | AA04       | COFDM_ADCIN[1]          | I           | COFDM Digital Input from Ext. ADC - Data Bit 1          | 2, 5, 7 |

|           |            | DV2_IN_DATA[1]          | I           | Reserved                                                | 7       |

|           |            | ED2_MDO[0]<br>(LSB)     | I           | External Demodulator 2 Digital Input - Data Bit 0 (LSB) | 7       |

| Pin Name  | Pin<br>No. | Function                | Pin<br>Type | Description                                                | Notes   |

|-----------|------------|-------------------------|-------------|------------------------------------------------------------|---------|

| ADC_IN[8] | AA03       | COFDM_ADCIN[0]<br>(LSB) | I           | COFDM Digital Input from Ext. ADC -<br>Data Bit 0 (LSB)    | 2, 5, 7 |

|           |            | DV2_IN_DATA[0]<br>(LSB) | I           | Reserved                                                   | 7       |

|           |            | ED2_MOVAL               | I           | External Demodulator 1 Digital Input -<br>Data Valid Input |         |

| ADC_IN[9] | AC02       | DV2_IN_Pixel_Clk        | I           | Reserved                                                   |         |

|           |            | ED2_MOCLK               | I           | External Demodulator 1 Digital Input - Clock Input         |         |

- Note 1: 5V tolerant connection to allow use of 5V Tuner devices

- Note 2: Multiplex setup with COFDM Register Bit 0 = '1'

- Note 3: Multiplex setup with CICSEL3 Register Bits 9:11 = '111'

- Note 4: Multiplex setup with CICSEL3 Register Bit 6 = '1', and GPIS2 Register Bits 24:25 = '01'

- Note 5: Multiplex setup with COFDM Register Bit 0 = '0'

- Note 6: External pull-up to Tuner Vdd PSU required on GPPx lines.

- Note 7: The ADC\_IN [0:9] and EXT\_IN [0:9] inputs on the Front End interface are configured as "Big Endian". This means that bit [0] is the Most Significant Bit (MSB) for the multiplexed functions mapped to that pin.

- Note 8: When the ADC\_IN [0:9] and EXT\_IN [0:9] pins are used to provide various alternative inputs within one application, then each set of inputs must have a tri-state buffer. The enables for these buffers should then be controlled by general purpose I/O pins.

#### 6.3 Video DAC Outputs

| Pin Name      | Pin No. | Pin<br>Type | Description                                            | Notes |

|---------------|---------|-------------|--------------------------------------------------------|-------|

| DAC_OP0       | AE15    | 0           | Video Triple-DAC 1 output 1.                           | 1, 2  |

| DAC_OP1       | AD15    | 0           | Video Triple-DAC 1 output 2.                           | 1, 2  |

| DAC_OP2       | AD13    | 0           | Video Triple-DAC 1 output 3.                           | 1, 2  |

| DAC_OP3       | AD10    | 0           | Video Triple-DAC 2 output 1.                           | 1, 2  |

| DAC_OP4       | AF06    | 0           | Video Triple-DAC 2 output 2.                           | 1, 2  |

| DAC_OP5       | AF10    | 0           | Video Triple-DAC 2 output 3.                           | 1, 2  |

| DAC1_CREF_OUT | AF11    | 0           | De-coupling for triple DAC 1 - to GND                  |       |

| DAC1_GREF_OUT | AF17    | 0           | De-coupling for triple DAC 1 - to AVDD                 |       |

| DAC1_RREF_OUT | AE13    | 0           | Gain control for triple DAC 1.                         | 3     |

| DAC1_VREF_IN  | AE14    | I           | Voltage reference input (1.2V) for Video Triple-DAC 1. | 4     |

| DAC2_CREF_OUT | AE11    | 0           | De-coupling for triple DAC 2 - to GND                  |       |

| DAC2_GREF_OUT | AF05    | 0           | De-coupling for triple DAC 2 - to AVDD                 |       |

| DAC2_RREF_OUT | AE09    | 0           | Gain control for triple DAC 2.                         | 3     |

| DAC2_VREF_IN  | AF07    | I           | Voltage reference input (1.2V) for Video Triple-DAC 2  | 4     |

Note 1: Video outputs capable of driving between 37.5ohm and 75ohm loads.

- Note 2: Triple DAC output can be setup using the DENCMUX register to output any of the following types of video signal: RGB, CVBS, Y U/V

- Note 3: Gain set using Current Adjust resistor to GND. Typically need 392ohms for a DAC load of 37.5ohms.

- Note 4: Apply external reference (1.2V) when internal reference is not in use.

#### 6.4 SDRAM Interfaces

The ZL10310 and ZL10311 devices have 2 independent SDRAM interfaces. The main SDRAM interface is SDRAM1 which is used as the main memory space for both the PowerPC® processor and Video/Audio decoding. If required a separate processor-only SDRAM interface can be used; this is the optional SDRAM0 interface.

All the signals for the SDRAM1 and SDRAM0 interfaces are configured as "Big Endian", which signifies that bit [0] on both the Address and Data buses is the Most Significant Bit (MSB).

| Pin Name     | Pin No. | Pin<br>Type | Description                       | Notes |

|--------------|---------|-------------|-----------------------------------|-------|

| SD1_ADDR[00] | D24     | 0           | SDRAM1 Bus - Address Bit 0 (MSB)  |       |

| SD1_ADDR[01] | F26     | 0           | SDRAM1 Bus - Address Bit 1        |       |

| SD1_ADDR[02] | F25     | 0           | SDRAM1 Bus - Address Bit 2        |       |

| SD1_ADDR[03] | E25     | 0           | SDRAM1 Bus - Address Bit 3        |       |

| SD1_ADDR[04] | E26     | 0           | SDRAM1 Bus - Address Bit 4        |       |

| SD1_ADDR[05] | D26     | 0           | SDRAM1 Bus - Address Bit 5        |       |

| SD1_ADDR[06] | L23     | 0           | SDRAM1 Bus - Address Bit 6        |       |

| SD1_ADDR[07] | C26     | 0           | SDRAM1 Bus - Address Bit 7        |       |

| SD1_ADDR[08] | A25     | 0           | SDRAM1 Bus - Address Bit 8        |       |

| SD1_ADDR[09] | B23     | 0           | SDRAM1 Bus - Address Bit 9        |       |

| SD1_ADDR[10] | B24     | 0           | SDRAM1 Bus - Address Bit 10       |       |

| SD1_ADDR[11] | C23     | 0           | SDRAM1 Bus - Address Bit 11       |       |

| SD1_ADDR[12] | C25     | 0           | SDRAM1 Bus - Address Bit 12       |       |

| SD1_ADDR[13] | D25     | 0           | SDRAM1 Bus - Address Bit 13 (LSB) |       |

| SD1_DATA[00] | N24     | В           | SDRAM1 Bus - Data Bit 0 (MSB)     |       |

| SD1_DATA[01] | N26     | В           | SDRAM1 Bus - Data Bit 1           |       |

| SD1_DATA[02] | M25     | В           | SDRAM1 Bus - Data Bit 2           |       |

| SD1_DATA[03] | T23     | В           | SDRAM1 Bus - Data Bit 3           |       |

| SD1_DATA[04] | L25     | В           | SDRAM1 Bus - Data Bit 4           |       |

| SD1_DATA[05] | K26     | В           | SDRAM1 Bus - Data Bit 5           |       |

| SD1_DATA[06] | K24     | В           | SDRAM1 Bus - Data Bit 6           |       |

| SD1_DATA[07] | J25     | В           | SDRAM1 Bus - Data Bit 7           |       |

| SD1_DATA[08] | J24     | В           | SDRAM1 Bus - Data Bit 8           |       |

| Pin Name     | Pin No. | Pin<br>Type | Description                                                                                | Notes |

|--------------|---------|-------------|--------------------------------------------------------------------------------------------|-------|

| SD1_DATA[09] | K25     | В           | SDRAM1 Bus - Data Bit 9                                                                    |       |

| SD1_DATA[10] | L26     | В           | SDRAM1 Bus - Data Bit 10                                                                   |       |

| SD1_DATA[11] | L24     | В           | SDRAM1 Bus - Data Bit 11                                                                   |       |

| SD1_DATA[12] | M26     | В           | SDRAM1 Bus - Data Bit 12                                                                   |       |

| SD1_DATA[13] | M24     | В           | SDRAM1 Bus - Data Bit 13                                                                   |       |

| SD1_DATA[14] | N25     | В           | SDRAM1 Bus - Data Bit 14                                                                   |       |

| SD1_DATA[15] | P25     | В           | SDRAM1 Bus - Data Bit 15 (LSB)                                                             |       |

| SD1_DQMH     | H25     | 0           | SDRAM1 Bus - Data Bus Mask High. Active High                                               |       |

| SD1_DQML     | J26     | 0           | SDRAM1 Bus - Data Bus Mask Low. Active High                                                |       |

| nSD1_RAS     | G25     | 0           | SDRAM1 Bus - Row Address Strobe. Active Low.<br>Also known as SDRAM 1 Command Bit 2 (MSB). |       |

| nSD1_CAS     | G24     | 0           | SDRAM1 Bus - Column Address Strobe. Active Low. Also known as SDRAM 1 Command Bit 1.       |       |

| nSD1_WE      | H24     | 0           | SDRAM1 Bus - Write Enable. Active Low.<br>Also known as SDRAM 1 Command Bit 0 (LSB).       |       |

| SD1_CLK      | G26     | 0           | SDRAM1 Bus - Clock Output                                                                  | 1     |

| nSD1_CS0     | F24     | 0           | SDRAM1 Bus - Chip Select 0. Active Low                                                     |       |

| SD0_ADDR[00] | AC26    | 0           | SDRAM0 Bus. Address bit 0 (MSB)                                                            |       |

| SD0_ADDR[01] | AC24    | 0           | SDRAM0 Bus. Address bit 1                                                                  |       |

| SD0_ADDR[02] | AB25    | 0           | SDRAM0 Bus. Address bit 2                                                                  |       |

| SD0_ADDR[03] | AB26    | 0           | SDRAM0 Bus. Address bit 3                                                                  |       |

| SD0_ADDR[04] | AB24    | 0           | SDRAM0 Bus. Address bit 4                                                                  |       |

| SD0_ADDR[05] | AA24    | 0           | SDRAM0 Bus. Address bit 5                                                                  |       |

| SD0_ADDR[06] | AA25    | 0           | SDRAM0 Bus. Address bit 6                                                                  |       |

| SD0_ADDR[07] | Y26     | 0           | SDRAM0 Bus. Address bit 7                                                                  |       |

| SD0_ADDR[08] | Y25     | 0           | SDRAM0 Bus. Address bit 8                                                                  |       |

| SD0_ADDR[09] | V24     | 0           | SDRAM0 Bus. Address bit 9                                                                  |       |

| SD0_ADDR[10] | W24     | 0           | SDRAM0 Bus. Address bit 10                                                                 |       |

| SD0_ADDR[11] | Y24     | 0           | SDRAM0 Bus. Address bit 11                                                                 |       |

| SD0_ADDR[12] | AA26    | 0           | SDRAM0 Bus. Address bit 12                                                                 |       |

| SD0_ADDR[13] | AA23    | 0           | SDRAM0 Bus. Address bit 13 (LSB)                                                           |       |

| SD0_DATA[00] | AE18    | В           | SDRAM0 Bus - Data Bit 0 (MSB)                                                              |       |

| Pin Name     | Pin No. | Pin<br>Type | Description                                                                             | Notes |

|--------------|---------|-------------|-----------------------------------------------------------------------------------------|-------|

| SD0_DATA[01] | AD19    | В           | SDRAM0 Bus - Data Bit 1                                                                 |       |

| SD0_DATA[02] | AD20    | В           | SDRAM0 Bus - Data Bit 2                                                                 |       |

| SD0_DATA[03] | AF20    | В           | SDRAM0 Bus - Data Bit 3                                                                 |       |

| SD0_DATA[04] | AD21    | В           | SDRAM0 Bus - Data Bit 4                                                                 |       |

| SD0_DATA[05] | AE21    | В           | SDRAM0 Bus - Data Bit 5                                                                 |       |

| SD0_DATA[06] | AE22    | В           | SDRAM0 Bus - Data Bit 6                                                                 |       |

| SD0_DATA[07] | AF23    | В           | SDRAM0 Bus - Data Bit 7                                                                 |       |

| SD0_DATA[08] | AD23    | В           | SDRAM0 Bus - Data Bit 8                                                                 |       |

| SD0_DATA[09] | AD22    | В           | SDRAM0 Bus - Data Bit 9                                                                 |       |

| SD0_DATA[10] | AF22    | В           | SDRAM0 Bus - Data Bit 10                                                                |       |

| SD0_DATA[11] | AF21    | В           | SDRAM0 Bus - Data Bit 11                                                                |       |

| SD0_DATA[12] | AC21    | В           | SDRAM0 Bus - Data Bit 12                                                                |       |

| SD0_DATA[13] | AE20    | В           | SDRAM0 Bus - Data Bit 13                                                                |       |

| SD0_DATA[14] | AE19    | В           | SDRAM0 Bus - Data Bit 14                                                                |       |

| SD0_DATA[15] | AF18    | В           | SDRAM0 Bus - Data Bit 15 (LSB)                                                          |       |

| SD0_DQMH     | AE24    | 0           | SDRAM0 Bus - Data Bus Mask High. Active High                                            |       |

| SD0_DQML     | AD18    | 0           | SDRAM0 Bus - Data Bus Mask Low. Active High                                             |       |

| nSD0_RAS     | AD25    | 0           | SDRAM0 Bus - Row Address Strobe. Active Low.  Also known as SDRAM0 Command Bit 2 (MSB). |       |

| nSD0_CAS     | AF24    | 0           | SDRAM0 Bus - Column Address Strobe. Active Low.<br>Also known as SDRAM0 Command Bit 1.  |       |

| nSD0_WE      | AE23    | 0           | SDRAM0 Bus - Write Enable. Active Low.  Also known as SDRAM0 Command Bit 0 (LSB).       |       |

| SD0_CLK      | AE26    | 0           | SDRAM0 Bus - Clock Output                                                               | 1     |

| nSD0_CS0     | AD26    | 0           | SDRAM0 Bus - Chip Select 0. Active Low                                                  |       |

Note 1: SD0\_CLK / SD1\_CLK output is 50ohm impedance with 130ma/ns slew rate

#### 6.5 Bit Stream Interfaces

The ZL10310 and ZL10311 devices have a fully DVB-compatible byte-wide Common Interface, which is a bitstream data Input/Output bus. There are multiplexed functions on these pins, and included is information on how to access these multiplexed signals. The multiplexed functions include access to Address/Data Bits of the Auxiliary External Bus (configured on this interface to access PCMCIA (PC) Cards), RISC Trace debug ports, Simplified GPIO Bus 1 and Smart Card Interface 1.

The Data pins for Output (MOD[0:7]) and Input (MID[0:7]) are configured as "Big Endian". This means that bit [0] is the Most Significant Bit (MSB) for the Common Interface and Auxiliary Bus signals.

The provision of options, and the avoidance of the need for external pull ups, precludes the use of 5 volt tolerant inputs. The use of a 5-volt smart card would thus require external level translators.

| Pin<br>Name | Pin<br>No. | Function               | Pin<br>Type | Description                                                                        | Notes |

|-------------|------------|------------------------|-------------|------------------------------------------------------------------------------------|-------|

| MOD[0]      | T02        | CIO_MOD[0] (MSB)       | 0           | Common Interface Output - Data Bit 0 [MSB]                                         | 1     |

|             |            | RESET_4                | 0           | Bit 4 output from RESET Register.  Also mapped to PCMCIA interface Address Bit 25. | 2     |

| MOD[1]      | R01        | CIO_MOD[1]             | 0           | Common Interface Output - Data Bit 1                                               | 1     |

|             |            | RESET_3                | 0           | Bit 3 output from RESET Register. (PCMCIA Address 24)                              | 2     |

| MOD[2]      | P03        | CIO_MOD[2]             | 0           | Common Interface Output - Data Bit 2                                               | 1     |

|             |            | BI_ADDR_8              | 0           | Auxiliary External Bus - Address Bit 8 (PCMCIA Address 23)                         | 2     |

|             |            | RT_CLK                 | 0           | RISC Trace Port Clock Output                                                       | 3     |

| MOD[3]      | P02        | CIO_MOD[3]             | 0           | Common Interface Output - Data Bit 3                                               | 1     |

|             |            | BI_ADDR_9              | 0           | Auxiliary External Bus - Address Bit 9 (PCMCIA Address 22)                         | 2     |

|             |            | RT_TS6 /<br>RT_DATA[7] | 0           | RISC Trace Port 6 (Debug) /<br>RISC Trace Data Bit 7 (Debug)                       | 3     |

| MOD[4]      | P01        | CIO_MOD[4]             | 0           | Common Interface Output - Data Bit 4                                               | 1     |

|             |            | BI_ADDR_10             | 0           | Auxiliary External Bus - Address Bit 10 (PCMCIA Address 21)                        | 2     |

|             |            | RT_TS5 /<br>RT_DATA[6] | 0           | RISC Trace Port 5 (Debug) /<br>RISC Trace Data Bit 6 (Debug)                       | 3     |

| MOD[5]      | N02        | CIO_MOD[5]             | 0           | Common Interface Output - Data Bit 5                                               | 1     |

|             |            | BI_ADDR_11             | 0           | Auxiliary External Bus - Address Bit 11 (PCMCIA Address 20)                        | 2     |

|             |            | RT_TS4 /<br>RT_DATA[5] | 0           | RISC Trace Port 4 (Debug) /<br>RISC Trace Data Bit 5 (Debug)                       | 3     |

| MOD[6]      | M01        | CIO_MOD[6]             | 0           | Common Interface Output - Data Bit 6                                               | 1     |

|             |            | SGPIO1_4               | Ю           | Simplified General Purpose<br>Input / Output Bus 1 - Bit 4                         | 4     |

|             |            | SC1_VCC_CMND           | 0           | Smart Card 1 Interface - Vcc Enable Output                                         | 5     |

|             |            | BI_ADDR_12             | 0           | Auxiliary External Bus - Address Bit 12 (PCMCIA Address 19)                        | 2     |

|             |            | RT_TS3 /<br>RT_DATA[4] | 0           | RISC Trace Port 3 (Debug) / RISC Trace Data Bit 4 (Debug)                          | 3     |

| Pin<br>Name | Pin<br>No. | Function                | Pin<br>Type | Description                                                                                                     | Notes |

|-------------|------------|-------------------------|-------------|-----------------------------------------------------------------------------------------------------------------|-------|

| MOD[7]      | M02        | CIO_MOD[7]              | 0           | Common Interface Output - Data Bit 7 (LSB)                                                                      | 1     |

|             |            | SGPIO1_0                | Ю           | Simplified General Purpose<br>Input / Output Bus 1 - Bit 0                                                      | 4     |

|             |            | SC1_IO                  | В           | Smart Card 1 Interface - Data I/O                                                                               | 5     |

|             |            | BI_ADDR_13              | 0           | Auxiliary External Bus - Address Bit 13 (PCMCIA Address 18)                                                     | 2     |

|             |            | RT_TS20 /<br>RT_DATA[3] | 0           | RISC Trace Port 20 (Debug) /<br>RISC Trace Data Bit 3 (Debug)                                                   | 3     |

| MOVAL       | T01        | CIO_MVAL                | 0           | Common Interface Output - Data Valid Indicator.  Data Valid for the Current Clock Cycle for  Transmission.      | 1     |

|             |            | SGPIO1_2                | Ю           | Simplified General Purpose<br>Input / Output Bus 1 - Bit 2                                                      | 4     |

|             |            | SC1_DETECT              | I           | Smart Card 1 Interface - Detect Input                                                                           | 5     |

|             |            | BI_ADDR_15              | 0           | Auxiliary External Bus - Address Bit 15 (PCMCIA Address 16)                                                     | 2     |

|             |            | RT_TS10 /<br>RT_DATA[2] | 0           | RISC Trace Port 10 (Debug) /<br>RISC Trace Data Bit 2 (Debug)                                                   | 3     |

| MOSTRT      | R03        | CIO_MSTRT               | 0           | Common Interface Output - Packet Start Indicator. Identifies the first byte in a transport packet of 188 bytes. | 1     |

|             |            | SGPIO1_3                | Ю           | Simplified General Purpose<br>Input / Output Bus 1 - Bit 3                                                      | 4     |

|             |            | SC1_RESET               | 0           | Smart Card 1 Interface - Reset Output                                                                           | 5     |

|             |            | BI_ADDR_14              | 0           | Auxiliary External Bus - Address Bit 14 (PCMCIA Address 17)                                                     | 2     |

|             |            | RT_TS2E /<br>RT_DATA[1] | 0           | RISC Trace Port 2E (Debug) /<br>RISC Trace Data Bit 1 (Debug)                                                   | 3     |

| MOCLK       | N03        | CIO_MCLK                | 0           | Common Interface Output - Bitstream Clock.                                                                      | 1     |

|             |            | SGPIO1_1                | Ю           | Simplified General Purpose<br>Input / Output Bus 1 - Bit 1                                                      | 4     |

|             |            | SC1_CLK                 | 0           | Smart Card 1 Interface - Clock Output                                                                           | 5     |

|             |            | BI_ADDR_16              | 0           | Auxiliary External Bus - Address Bit 16 (PCMCIA Address 15)                                                     | 2     |

|             |            | RT_TS1E /<br>RT_DATA[0] | 0           | RISC Trace Port 1E (Debug) /<br>RISC Trace Data Bit 0 (Debug)                                                   | 3     |

| Pin<br>Name | Pin<br>No. | Function              | Pin<br>Type | Description                                                                                                    | Notes |

|-------------|------------|-----------------------|-------------|----------------------------------------------------------------------------------------------------------------|-------|

| MID[0]      | Y02        | CII_MDATA[0]<br>(MSB) | I           | Common Interface Input - Bit 0 (MSB)                                                                           | 1, 6  |

|             |            | BI_DATA[0] (MSB)      | I           | Auxiliary External Bus - Data Bit 0 (MSB) (PCMCIA Data 15)                                                     | 2, 6  |

| MID[1]      | Y01        | CII_MDATA[1]          | I           | Common Interface Input - Bit 1                                                                                 | 1, 6  |

|             |            | BI_DATA[1]            | I           | Auxiliary External Bus - Data Bit 1 (PCMCIA Data 14)                                                           | 2, 6  |

| MID[2]      | T04        | CII_MDATA[2]          | I           | Common Interface Input - Bit 2                                                                                 | 1, 6  |

|             |            | BI_DATA[2]            | I           | Auxiliary External Bus - Data Bit 2 (PCMCIA Data 13)                                                           | 2, 6  |

| MID[3]      | U03        | CII_MDATA[3]          | I           | Common Interface Input - Bit 3                                                                                 | 1, 6  |

|             |            | BI_DATA[3]            | I           | Auxiliary External Bus - Data Bit 3 (PCMCIA Data 12)                                                           | 2, 6  |

| MID[4]      | V01        | CII_MDATA[4]          | I           | Common Interface Input - Bit 4                                                                                 | 1, 6  |

|             |            | BI_DATA[4]            | I           | Auxiliary External Bus - Data Bit 4 (PCMCIA Data 11)                                                           | 2, 6  |

| MID[5]      | V02        | CII_MDATA[5]          | I           | Common Interface Input - Bit 5                                                                                 | 1, 6  |

|             |            | BI_DATA[5]            | I           | Auxiliary External Bus - Data Bit 5 (PCMCIA Data 10)                                                           | 2, 6  |

| MID[6]      | U01        | CII_MDATA[6]          | I           | Common Interface Input - Bit 6                                                                                 | 1, 6  |

|             |            | BI_DATA[6]            | I           | Auxiliary External Bus - Data Bit 6 (PCMCIA Data 9)                                                            | 2, 6  |

| MID[7]      | T03        | CII_MDATA[7] (LSB)    | I           | Common Interface Input - Bit 7 (LSB)                                                                           | 1, 6  |

|             |            | BI_DATA[7] (LSB)      | I           | Auxiliary External Bus - Data Bit 7 (LSB) (PCMCIA Data 8)                                                      | 2, 6  |

| MISTRT      | U02        | CII_MSTRT             | I           | Common Interface Input - Packet Start Indicator. Identifies the first byte in a transport packet of 188 bytes. |       |

| MICLK       | W02        | CII_MCLK              | I           | Common Interface Input - Bitstream Clock.                                                                      |       |

| MIVAL       | AA01       | CII_MVAL              | I           | Common Interface Input - Data Valid Indicator.  Data Valid for the Current Clock Cycle for  Transmission.      |       |

Note 1: Multiplex setup with PORTMUX Register Bits [11:10] = '00'

Note 2: Multiplex setup with PORTMUX Register Bits [11:10] = '10'

Note 3: Multiplex setup with PORTMUX Register Bits [11:10] = '11'

Note 4: Multiplex setup with PORTMUX Register Bits [11:10] = '01' & CICSEL3 Register Bit 2 = '0'. Also if BI\_DATA[7] = '0' at Reset.

Note 5: Multiplex setup with PORTMUX Register Bits [11:10] = '01' & CICSEL3 Register Bit 2 = '1'. Also if BI\_DATA[7] = '1' at Reset.

Note 6: Data Inputs MID [0:7] should be connected to GND or Vdd if NOT required.

ZL10310/ZL10311

#### 6.6 Auxiliary External Bus

The ZL1031 and ZL10311 devices have an Auxiliary External Bus, which can be configured as an IDE interface to external Hard-Disk Drives and other ATAPI devices. The Auxiliary Bus can also offer a standard interface to external memory chips, such as Flash ROM etc. There are multiplexed functions on these pins, and included is information on how to access these multiplexed signals. The multiplexed functions include access to the DVB Common Interface Address Bus.

The Data and Address pins for the Auxiliary External Bus are configured as "Big Endian". This means that Data bit [0] and Address Bit [9] are the Most Significant Bits (MSB).

| Pin Name    | Pin<br>No. | Function              | Pin<br>Type | Description                                         | Notes |

|-------------|------------|-----------------------|-------------|-----------------------------------------------------|-------|

| BI_ADDR[09] | A05        | BI_ADDR[09]<br>(MSB)  | 0           | Auxiliary External Bus - Address Bit 9 (MSB)        | 1     |

|             |            | nBI_CS5               | 0           | Auxiliary External Bus - Chip Select 5. Active Low. | 2     |

| BI_ADDR[10] | A13        | BI_ADDR[10]           | 0           | Auxiliary External Bus - Address Bit 10             |       |

| BI_ADDR[11] | A15        | BI_ADDR[11]           | 0           | Auxiliary External Bus - Address Bit 11             |       |

| BI_ADDR[12] | C14        | BI_ADDR[12]           | 0           | Auxiliary External Bus - Address Bit 12             |       |

| BI_ADDR[13] | D14        | BI_ADDR[13]           | 0           | Auxiliary External Bus - Address Bit 13             |       |

| BI_ADDR[14] | B16        | BI_ADDR[14]           | 0           | Auxiliary External Bus - Address Bit 14             | 3     |

|             |            | nIDE_iowr             | 0           | IDE IO write signal. Active Low.                    | 4     |

|             |            | nDVB_CI_iowr          | 0           | DVB Common Interface IO write signal                | 5     |

| BI_ADDR[15] | A17        | BI_ADDR[15]           | 0           | Auxiliary External Bus - Address Bit 15             | 3     |

|             |            | nIDE_iord             | 0           | IDE IO read signal. Active Low.                     | 4     |

|             |            | nDVB_CI_iord          | 0           | DVB Common Interface IO read signal                 | 5     |

| BI_ADDR[16] | B17        | BI_ADDR[16]           | 0           | Auxiliary External Bus - Address Bit 16             |       |

| BI_ADDR[17] | A18        | BI_ADDR[17]           | 0           | Auxiliary External Bus - Address Bit 17             | 6     |

|             |            | DVB_CI_A[14]<br>(MSB) | 0           | DVB Common Interface Address Bit 14 (MSB)           | 5     |

| BI_ADDR[18] | C16        | BI_ADDR[18]           | 0           | Auxiliary External Bus - Address Bit 18             | 6     |

|             |            | DVB_CI_A[13]          | 0           | DVB Common Interface Address Bit 13                 | 5     |

| BI_ADDR[19] | B18        | BI_ADDR[19]           | 0           | Auxiliary External Bus - Address Bit 19             | 6     |

|             |            | DVB_CI_A[12]          | 0           | DVB Common Interface Address Bit 12                 | 5     |

| BI_ADDR[20] | D16        | BI_ADDR[20]           | 0           | Auxiliary External Bus - Address Bit 20             | 6     |

|             |            | DVB_CI_A[11]          | 0           | DVB Common Interface - Address Bit 11               | 5     |

| BI_ADDR[21] | C17        | BI_ADDR[21]           | 0           | Auxiliary External Bus - Address Bit 21             | 6     |

|             |            | DVB_CI_A[10]          | 0           | DVB Common Interface - Address Bit 10               | 5     |

| Pin Name    | Pin<br>No. | Function                       | Pin<br>Type | Description                                                             | Notes |

|-------------|------------|--------------------------------|-------------|-------------------------------------------------------------------------|-------|

| BI_ADDR[22] | B19        | BI_ADDR[22]                    | 0           | Auxiliary External Bus - Address Bit 22                                 | 6     |

|             |            | DVB_CI_A[9]                    | 0           | DVB Common Interface - Address Bit 9                                    | 5     |

| BI_ADDR[23] | A21        | BI_ADDR[23]                    | 0           | Auxiliary External Bus - Address Bit 23                                 | 6     |

|             |            | DVB_CI_A[8]                    | 0           | DVB Common Interface - Address Bit 8                                    | 5     |

| BI_ADDR[24] | C19        | BI_ADDR[24]                    | 0           | Auxiliary External Bus - Address Bit 24                                 | 6     |

|             |            | DVB_CI_A[7]                    | 0           | DVB Common Interface - Address Bit 7                                    | 5     |

| BI_ADDR[25] | C20        | BI_ADDR[25]                    | 0           | Auxiliary External Bus - Address Bit 25                                 | 6     |

|             |            | DVB_CI_A[6]                    | 0           | DVB Common Interface - Address Bit 6                                    | 5     |

| BI_ADDR[26] | B21        | BI_ADDR[26]                    | 0           | Auxiliary External Bus - Address Bit 26                                 | 6     |

|             |            | DVB_CI_A[5]                    | 0           | DVB Common Interface - Address Bit 5                                    | 5     |

| BI_ADDR[27] | C21        | BI_ADDR[27]                    | 0           | Auxiliary External Bus - Address Bit 27                                 | 6     |

|             |            | DVB_CI_A[4]                    | 0           | DVB Common Interface - Address Bit 4                                    | 5     |

| BI_ADDR[28] | B22        | BI_ADDR[28]                    | 0           | Auxiliary External Bus - Address Bit 28                                 | 6     |

|             |            | DVB_CI_A[3]                    | 0           | DVB Common Interface - Address Bit 3                                    | 5     |

| BI_ADDR[29] | A23        | BI_ADDR[29]                    | 0           | Auxiliary External Bus - Address Bit 29                                 | 6     |

|             |            | DVB_CI_A[2]                    | 0           | DVB Common Interface - Address Bit 2                                    | 5     |

| BI_ADDR[30] | C22        | BI_ADDR[30]                    | 0           | Auxiliary External Bus - Address Bit 30                                 | 6     |

|             |            | DVB_CI_A[1]                    | 0           | DVB Common Interface - Address Bit 1                                    | 5     |

| BI_ADDR[31] | A24        | BI_ADDR[31]<br>(LSB) / BI_WBE1 | 0           | Auxiliary External Bus - Address Bit 31 (LSB) / Write Byte Enable Bit 1 | 6     |

|             |            | DVB_CI_A[0]<br>(LSB)           | 0           | DVB Common Interface Address Bit 0 (LSB)                                | 5     |

| BI_DATA[00] | G02        | BI_DATA[00]<br>(MSB)           | 0           | Auxiliary External Bus - Data Bit 0 (MSB)                               |       |

| BI_DATA[01] | F01        | BI_DATA[01]                    | 0           | Auxiliary External Bus - Data Bit 1                                     |       |

| BI_DATA[02] | H03        | BI_DATA[02]                    | 0           | Auxiliary External Bus - Data Bit 2                                     |       |

| BI_DATA[03] | G03        | BI_DATA[03]                    | 0           | Auxiliary External Bus - Data Bit 3                                     |       |

| BI_DATA[04] | F02        | BI_DATA[04]                    | 0           | Auxiliary External Bus - Data Bit 4                                     |       |

| BI_DATA[05] | E01        | BI_DATA[05]                    | 0           | Auxiliary External Bus - Data Bit 5                                     |       |

| BI_DATA[06] | F03        | BI_DATA[06]                    | 0           | Auxiliary External Bus - Data Bit 6                                     |       |

| BI_DATA[07] | E02        | BI_DATA[07]                    | 0           | Auxiliary External Bus - Data Bit 7                                     |       |

| BI_DATA[08] | D01        | BI_DATA[08]                    | 0           | Auxiliary External Bus - Data Bit 8                                     |       |

| Pin Name    | Pin<br>No. | Function                | Pin<br>Type | Description                                                                                                    | Notes |

|-------------|------------|-------------------------|-------------|----------------------------------------------------------------------------------------------------------------|-------|

| BI_DATA[09] | F04        | BI_DATA[09]             | 0           | Auxiliary External Bus - Data Bit 9                                                                            |       |

| BI_DATA[10] | E03        | BI_DATA[10]             | 0           | Auxiliary External Bus - Data Bit 10                                                                           |       |

| BI_DATA[11] | D02        | BI_DATA[11]             | 0           | Auxiliary External Bus - Data Bit 11                                                                           |       |

| BI_DATA[12] | C01        | BI_DATA[12]             | 0           | Auxiliary External Bus - Data Bit 12                                                                           |       |

| BI_DATA[13] | B01        | BI_DATA[13]             | 0           | Auxiliary External Bus - Data Bit 13                                                                           |       |

| BI_DATA[14] | C02        | BI_DATA[14]             | 0           | Auxiliary External Bus - Data Bit 14                                                                           |       |