# **LXT917/916** Multi-Port Hub Repeaters for Managed 10BASE-T Applications

# **General Description**

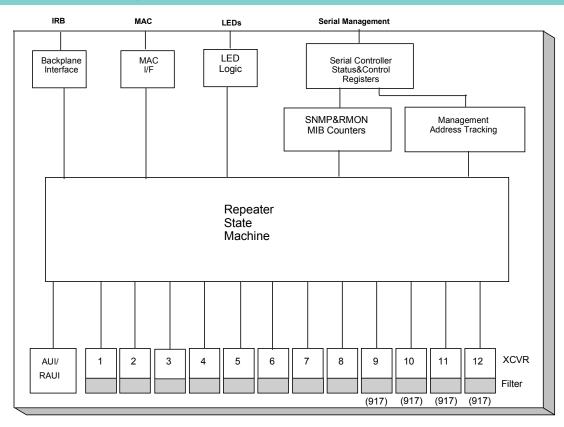

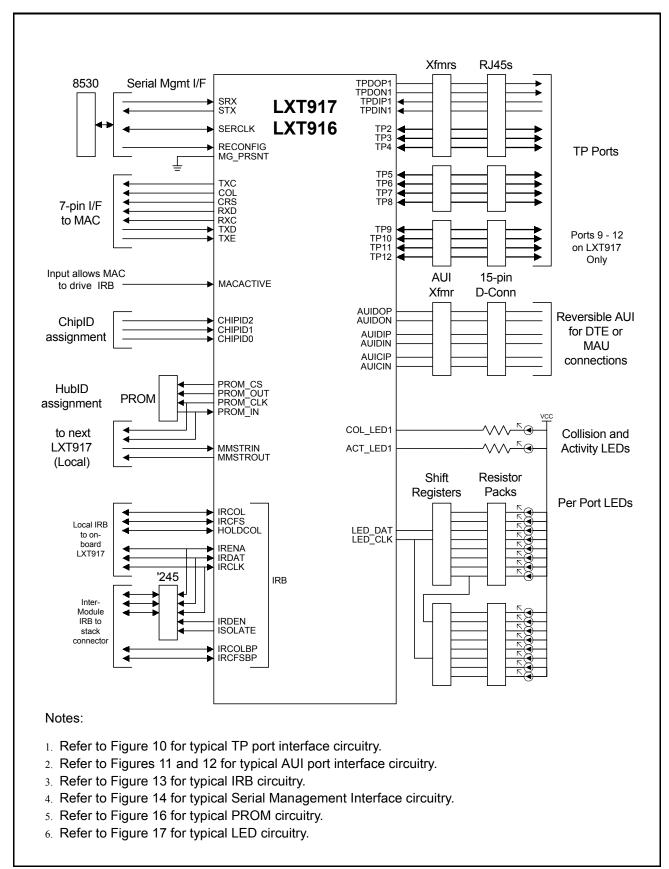

The LXT917 is a fully manageable, 12-port Ethernet repeater. Using mixed-signal technology, this single IC provides direct support for RMON and for the Repeater MIB using on-chip 32-bit counters. A high-speed serial management interface provides complete control over all device operations as well as access to the counters. An inter-repeater backplane allows multiple devices to be cascaded into a single logical repeater. This backplane has been specifically designed to aid in the development of systems with multiple modules, for stackable- and modular-hub applications.

The LXT917 provides twelve 10BASE-T ports, a reversible 10BASE-5 port (AUI), and a 7-pin MAC Interface. All 10BASE-T ports are outfitted with integrated filters. The reversible AUI port can function either as a DTE or as a MAU.

The LXT916 is an eight-port version of the LXT917 with all the same functionality.

## **Features**

Targeted for manageable 10 Mbit repeater and router/hub applications, and remote access systems

- Eight or twelve 10BASE-T ports with Integrated Filters

- · Hardware assist for RMON and the Repeater MIB

- Reversible AUI port

- · Cascadable digital backplane

- 7-pin MAC interface supports bridging and advanced management applications

- · High-speed serial management interface

- Two address-tracking registers per port

- · Source Address matching function

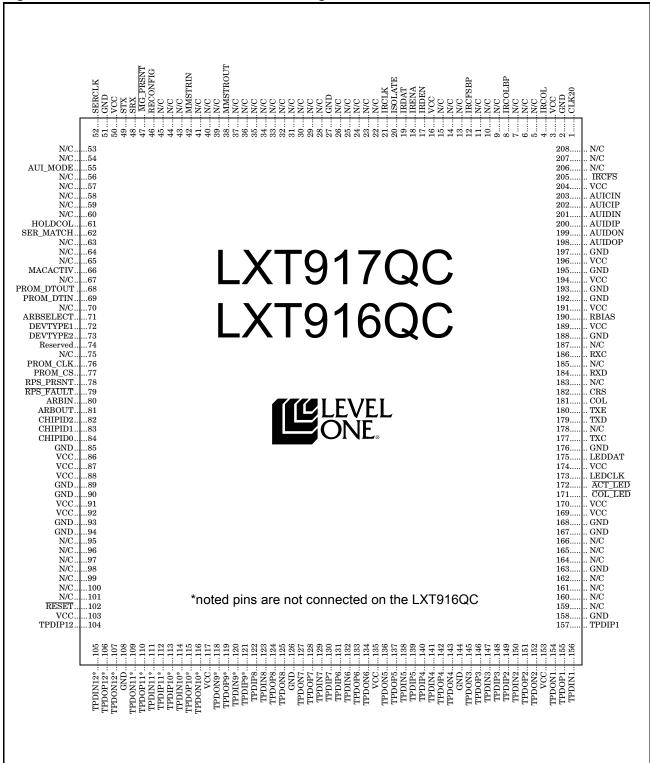

- 208-pin PQFP

- 0-70°C Temperature Range

# **LXT917 Block Diagram**

## PIN ASSIGNMENTS AND SIGNAL DESCRIPTIONS

Figure 1: LXT917QC and LXT916QC Pin Assignments

**Table 1: Twisted-Pair Port Signal Descriptions**

| Pin                                                                                          | Symbol                                                                                                                  | Туре          | Description                                                                                                                                                                                                             |

|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 155, 154<br>151, 152<br>146, 145<br>142, 143<br>137, 136<br>133, 134<br>128, 127<br>124, 125 | TPDOP1, TPDON1 TPDOP2, TPDON2 TPDOP3, TPDON3 TPDOP4, TPDON4 TPDOP5, TPDON5 TPDOP6, TPDON6 TPDOP7, TPDON7 TPDOP8, TPDON8 | Analog Output | <b>Twisted-Pair Data Outputs - Ports 1 through 8.</b> These pins are the positive and negative outputs from the respective twisted-pair port line drivers.                                                              |

| 157, 156<br>149, 150<br>148, 147<br>140, 141<br>139, 138<br>131, 132<br>130, 129<br>122, 123 | TPDIP1, TPDIN1 TPDIP2, TPDIN2 TPDIP3, TPDIN3 TPDIP4, TPDIN4 TPDIP5, TPDIN5 TPDIP6, TPDIN6 TPDIP7, TPDIN7 TPDIP8, TPDIN8 | Analog Input  | <b>Twisted-Pair Data Inputs - Ports 1 through 8.</b> These pins are the positive and negative inputs to the respective twisted-pair ports.                                                                              |

| 119, 118<br>115, 116<br>110, 109<br>106, 107                                                 | TPDOP9, TPDON9 TPDOP1, TPDON10 TPDOP11, TPDON11 TPDOP12, TPDON12                                                        | Analog Output | <b>Twisted-Pair Data Outputs - Ports 9 through 12.</b> These pins are the positive and negative outputs from the respective twisted-pair port line drivers.  On the 916, ports 9 through 12 should be left unconnected. |

| 121, 120<br>113, 114<br>112, 111<br>104, 105                                                 | TPDIP9, TPDIN9 TPDIP10, TPDIN10 TPDIP11, TPDIN11 TPDIP12, TPDIN12                                                       | Analog Input  | Twisted-Pair Data Inputs - Ports 9 through 12. These pins are the positive and negative inputs to the respective twisted-pair ports.  On the LXT916, ports 9 through 12 should be left unconnected.                     |

**Table 2: AUI Port Signal Descriptions**

| Pin    | Symbol                         | Туре            | Description                                                                                                                                                                                                           |  |

|--------|--------------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 55     | AUI_MODE                       | TTL Input<br>PD | AUI Mode Select. Low = Normal Mode (DTE).<br>High = Reverse Mode (MAU)                                                                                                                                                |  |

| 198    | AUIDOP                         | Analog          | AUI Data Outputs. Positive and negative data outputs for the AUI port. In normal (DTE) mode, connect to pins 3 and 10 of the AUI D-connector. In reverse (MAU) mode, connect to pins 5 and 12 of the AUI D-connector. |  |

| 199    | AUIDON                         | Output          |                                                                                                                                                                                                                       |  |

| 200    | AUIDIP                         | Analog          | AUI Data Inputs. Positive and negative data inputs for the AUI port. In normal (DTE) mode, connect to pins 5 and 12 of the AUI D-connector. In reverse (MAU) mode, connect to pins 3 and 10 of the AUI D-connector.   |  |

| 201    | AUIDIN                         | Input           |                                                                                                                                                                                                                       |  |

| 202    | AUICIP                         | Tri-State,      | AUI Collision Inputs. In normal (DTE) mode these pins are the positive and negative collision inputs for the AUI port. In reverse (MAU) mode these pins are outputs.                                                  |  |

| 203    | AUICIN                         | Analog, I/O     |                                                                                                                                                                                                                       |  |

| 1. PD= | PD = Input contains pull-down. |                 |                                                                                                                                                                                                                       |  |

**Table 3: Inter-Repeater Backplane Signal Descriptions**

| Pin | Symbol  | Туре                                          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|-----|---------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

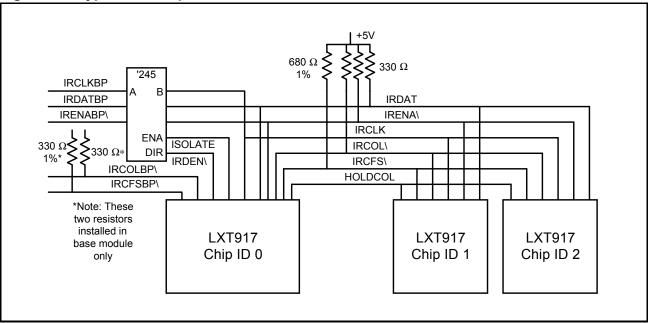

| 17  | IRDEN   | Open-Drain<br>Output                          | <b>IRB Driver Enable.</b> This output provides directional control for an external bi-directional transceiver ('245) used to buffer the IRBs in multi-module applications. It must be pulled up by 330 $\Omega$ resistors. When there are multiple devices on one module, tie all $\overline{\text{IRDEN}}$ outputs together. If $\overline{\text{IRDEN}}$ is tied directly to the DIR pin on a '245, attach the on-board IRDAT, IRCLK and $\overline{\text{IRENA}}$ signals to the "B" side of the '245, and connect the off-board signals to the "A" side of the '245. |  |

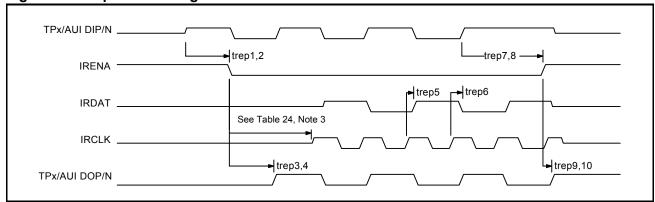

| 18  | IRENA   | CMOS I/O<br>Open Drain                        | Inter-Repeater Backplane Enable. This active low output indicates carrier presence on the IRB. When the IRB is idle, a 330 $\Omega$ pull-up resistor pulls the IRENA output High. When there are multiple devices, tie all IRENA outputs together. This signal may be buffered between modules.                                                                                                                                                                                                                                                                          |  |

| 19  | IRDAT   | CMOS I/O<br>Open Drain                        | <b>IRB Data.</b> This bidirectional signal carries data on the IRB. Data is driven and sampled on the rising edge of IRCLK. This signal must be pulled up by a 330 $\Omega$ resistor. Between modules, this signal can be buffered.                                                                                                                                                                                                                                                                                                                                      |  |

| 20  | ISOLATE | Output                                        | <b>Isolate Enable.</b> This output allows one LXT917/916 per module the ability to enable or disable an external bidirectional transceiver ('245). Attach the output to the Enable input of the '245. The output is driven High (disable) to isolate the IRB.                                                                                                                                                                                                                                                                                                            |  |

| 21  | IRCLK   | CMOS I/O<br>TriState<br>Schmitt Trigger<br>#2 | <b>IRB Clock.</b> This bi-directional, non-continuous, 10 MHz clock is recovered from received network traffic. During idle periods, this output is high-impedanced. Schmitt triggering is used to increase noise immunity, therefore full rail-to-rail signals are required. Between modules, buffering may be used on this signal.                                                                                                                                                                                                                                     |  |

| 4   | IRCOL   | CMOS I/O<br>Open Drain                        | <b>IRB Collision.</b> This output is driven low to indicate that a collision has occurred. When there is no collision, a 330 $\Omega$ pull-up resistor (required) on the output pulls it High. This signal is intended only to be used between devices on the same module; it may not be buffered.                                                                                                                                                                                                                                                                       |  |

| 8   | IRCOLBP | CMOS I/O<br>Open Drain<br>NC                  | IRB Collision-BackPlane. This active Low output has the same function as $\overline{\text{IRCOL}}$ , but is used between modules. Attach this signal only from the device with ChipID = 0 to the backplane or connector, without buffering. The output must be pulled up by one 330Ω resistor per system.                                                                                                                                                                                                                                                                |  |

| 205 | IRCFS   | Analog,<br>I/O                                | <b>IRB Collision Force Sense.</b> This three-state analog output indicates that a transmit collision has occurred when it is driven Low. It must be pulled up with a 680 $\Omega$ , 1% resistor. This signal is intended only to be used between devices on the same module; it may not be buffered.                                                                                                                                                                                                                                                                     |  |

| 12  | IRCFSBP | Analog I/O,<br>N/C                            | <b>IRB Collision Force Sense-BackPlane.</b> This output has exactly the same function as $\overline{IRCFS}$ , but is used between modules. Attach this signal only from the device with ChipID = 0 to the backplane or connector, <b>without buffering</b> . This output must be pulled up by one 330 $\Omega$ , 1% resistor per system.                                                                                                                                                                                                                                 |  |

<sup>1.</sup> PU = Input contains pull-up.

PD = Input contains pull-down.

NC = No Clamp. Pad will not clamp input in the absence of power.

Even if the IRB is not used, required pull-up resistors must be installed as listed above.

Table 3: Inter-Repeater Backplane Signal Descriptions-continued

| Pin | Symbol   | Туре                  | Description                                                                                                                                                                                                                                                                                                       |

|-----|----------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 61  | HOLDCOL  | TTL Tri-state I/O, PD | <b>Hold Collision.</b> This active High signal is driven by the device with ChipID = 0 to extend a non-local transmit collision to other devices on the same module. The HOLDCOL signals from different modules should NOT be attached together.                                                                  |

| 42  | MMSTRIN  | TTL Input,<br>NC      | Management Master In. The MMSTR daisy chain ensures that collisions will be counted correctly in multi-module applications. Attach the MMSTRIN input of each device to the MMSTROUT output of the previous device. Ground MMSTRIN of the first or only device.                                                    |

| 38  | MMSTROUT | Output,<br>NC         | <b>Management Master Out</b> . MMSTR daisy chain output. In hot-swap applications, a 1 $k\Omega$ - 3 $k\Omega$ resistor can be used as a by-pass between MMSTRIN and MMSTROUT.                                                                                                                                    |

| 66  | MACACTIV | TTL Input,<br>PD      | MAC Active. This active High input allows external Ethernet controllers to directly drive the Inter Repeater Backplane. When the controller asserts MACACTIV, the LXT917 drives the IRCOL, IRCOLBP, IRCFS and IRCFSBP signals on behalf of the controller. If any of these inputs are unused, tie them to ground. |

**Table 4: MAC Interface Signal Descriptions**

| Pin    | Symbol         | Туре             | Description                                                                                                                                                      |

|--------|----------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

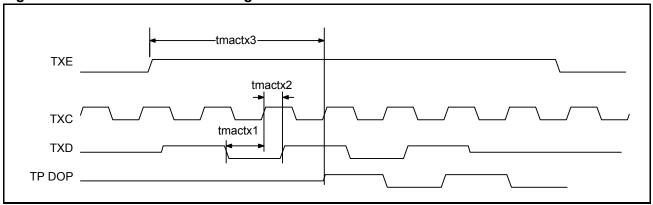

| 177    | TXC            | Output           | <b>Transmit Clock.</b> This 10 MHz continuous output is derived from the 20 MHz input clock.                                                                     |

| 179    | TXD            | TTL Input,<br>PD | <b>Transmit Data.</b> External controllers use this input to transmit data to the LXT917. The device samples TXD on the rising edge of TXC, when TXE is High.    |

| 180    | TXE            | TTL Input,<br>PD | <b>Transmit Enable</b> External controllers drive this input High to indicate that data is being transmitted on the TXD pin. Tie this input Low if it is unused. |

| 181    | COL            | Output           | <b>Collision</b> . The LXT917 drives this signal High to indicate that a collision has occurred.                                                                 |

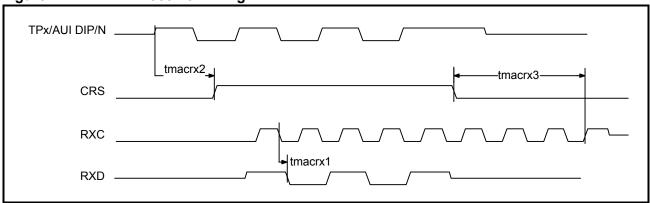

| 182    | CRS            | Output           | <b>Carrier Sense.</b> The LXT917 drives this signal High to indicate that valid data is present on RXD.                                                          |

| 184    | RXD            | Output           | <b>Receive Data.</b> The LXT917 transmits received data to the controller on this output. Data is driven on the falling edge of RXC.                             |

| 186    | RXC            | Output           | <b>Receive Clock.</b> This is a non-continuous 10 MHz clock that the LXT917 recovers from the network when traffic is actively being received.                   |

| 1. PD= | Input contains | pull-down.       |                                                                                                                                                                  |

PU = Input contains pull-up.

PD = Input contains pull-down.

NC = No Clamp. Pad will not clamp input in the absence of power.

Even if the IRB is not used, required pull-up resistors must be installed as listed above.

Table 5: Serial Management Interface Signal Descriptions

| Pin   | Symbol             | Type                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------|--------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 46    | RECONFIG           | TTL Input,<br>NC        | <b>Reconfigure</b> . This input controls the driving of the clock signal on the high-speed serial management interface (SERCLK). When this input is High, the LXT917 drives SERCLK with a 625 kHz output. When this input is Low, SER-CLK is an input to the LXT917. In addition, a Low-to-High transition on RECONFIG causes the LXT917 to drive 13 continuous 0's on the serial management bus, causing a re-arbitration to occur. |

| 47    | MG_PRSNT           | TTL Input<br>NC         | <b>Manager Present</b> . This signal is sensed at power up. If it is High, it indicates that no local manager is present, and the 917 enables all ports and sets all LEDs to operate in "hardware mode". If it is Low, indicating that a manager is present, the 917 disables all ports, pending control of network manager.                                                                                                         |

| 48    | SRX                | TTL Input               | <b>Serial Receive.</b> Receive data input for high-speed serial management interface. Must be tied to STX externally. SRX is sampled on the rising edge of SERCLK.                                                                                                                                                                                                                                                                   |

| 49    | STX                | Open Drain<br>Output    | <b>Serial Transmit.</b> Transmit data output for high-speed serial management interface. Must be tied to SRX externally. Data transmitted on STX is compared with data received on SRX. In the event of a mismatch, STX is put in the high impedance state. STX is driven on the falling edge of SERCLK.                                                                                                                             |

| 52    | SERCLK             | Tri-State<br>TTL Output | <b>Serial Clock.</b> Clock for serial management interface. Depending on RECONFIG, this pin is either a 625 kHz output or a 0 to 1 MHz input.                                                                                                                                                                                                                                                                                        |

| 1. NC | = No Clamp. Pad wi | ll not clamp input      | in the absence of power.                                                                                                                                                                                                                                                                                                                                                                                                             |

**Table 6: LED Signal Descriptions**

| Pin    | Symbol                        | Туре                     | Description                                                             |  |  |

|--------|-------------------------------|--------------------------|-------------------------------------------------------------------------|--|--|

| 171    | COL_LED                       | Open-Drain<br>Output, PU | Collision LED Driver. This output provides up to 10 mA of sink current. |  |  |

| 172    | ACT_LED                       | Open-Drain<br>Output, PU | Activity LED Driver. This output provides up to 10 mA of sink current.  |  |  |

| 173    | LED_CLK                       | Output                   | LED Clock. Clock for LED serial data output.                            |  |  |

| 175    | LED_DAT                       | Output                   | LED Data. Serial data output for LED data.                              |  |  |

| 1. PU= | 1. PU = Pad contains pull-up. |                          |                                                                         |  |  |

**Table 7: PROM Interface Signal Descriptions**

| Pin       | Symbol                | Туре                        | Description                                                                        |

|-----------|-----------------------|-----------------------------|------------------------------------------------------------------------------------|

| 76        | PROM_CLK              | TTL Input, Tri-State Output | PROM Clock. 1 MHz clock for reading PROM data.                                     |

| 77        | PROM_CS               | Tri-State Output, PD        | PROM Chip Select.                                                                  |

| 68        | PROM_OUT              | Tri-State Output, PD        | PROM Data Output.                                                                  |

| 69        | PROM_IN               | TTL Input                   | <b>PROM Data Input.</b> If a PROM is not used, this input can be tied Low or High. |

| 1. PD = 1 | Input contains pull-d | own.                        |                                                                                    |

**Table 8: Power Supply and Indication Signal Descriptions**

| Pin                                                                                                             | Symbol    | Туре         | Description                                                                                                                                                                                                                                        |

|-----------------------------------------------------------------------------------------------------------------|-----------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3, 16, 50,<br>86-88,<br>91-92,<br>103, 117,<br>135, 153,<br>169-170,<br>174, 189,<br>191, 194,<br>196, 204      | VCC       | Power        | <b>Power Supply Inputs.</b> Each of these pins must be connected to a common +5 VDC power supply. A de-coupling capacitor to digital ground should be supplied for every one of these pins.                                                        |

| 2, 27<br>51, 85<br>89-90<br>93-94<br>108<br>126, 144<br>158, 163<br>167-168,<br>176, 188<br>192-193<br>195, 197 | GND       | Power        | <b>Ground.</b> Connect each of these pins to digital ground.  Note: the LXT917 does NOT require separate digital and analog grounds.                                                                                                               |

| 190                                                                                                             | RBIAS     | Analog       | <b>RBias</b> . Connect this pin to ground through a 22 k $\Omega$ , 1% resistor. Note: Do NOT route any other signals near or around this resistor.                                                                                                |

| 78                                                                                                              | RPS_PRSNT | TTL<br>Input | Redundant Power Supply. Active High input indicates presence of redundant power supply. The state of this input and the RPS_FAULT input is reflected in the RPS LED bit in the serial LED output (refer to Tables 10 and 11). Tie Low if not used. |

| 79                                                                                                              | RPS_FAULT | TTL<br>Input | <b>Redundant Power Supply Fault</b> . Active Low input indicates redundant power supply fault. Tie High if not used.                                                                                                                               |

**Table 9: Miscellaneous Signal Descriptions**

| Pin | Symbol    | Туре                              | Description                                                                                                                                                                                                                                                                                                                                                                                              |

|-----|-----------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | CLK20     | CMOS Input,<br>Schmitt Trigger #1 | 20 MHz System Clock. Drive with CMOS levels.                                                                                                                                                                                                                                                                                                                                                             |

| 62  | SER_MATCH | Output                            | <b>Hub ID Match.</b> Active High. The device with ChipID = 0 asserts this signal whenever it detects a message on the serial bus which matches the local Hub ID.                                                                                                                                                                                                                                         |

| 71  | ARBSELECT | TTL Input, PU                     | <b>Arbitration Select</b> . If this pin is pulled Low, Arbitration Mechanism #1 is disabled, only Arbitration Mechanism #2 will be available. If this pin is pulled High, both mechanisms will be enabled. If Arbitration Mechanism #1 is enabled, the device with ChipID = 0 will transmit an "Arbitration Request" message every 2-3 ms on the serial management interface until a Hub ID is assigned. |

<sup>4.</sup> NC = No Clamp. Pad will not clamp input in the absence of power.

PU = Input contains pull-up.

PD = Input contains pull-down.

# LXT917/916 Multi-Port Hub Repeaters

Table 9: Miscellaneous Signal Descriptions-continued

| Pin                                                                                                                                                                          | Symbol                        | Туре                                         | Description                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 72<br>73                                                                                                                                                                     | DEVTYPE1<br>DEVTYPE2          | TTL Input, PD<br>TTL Input, PU               | <b>Device Type 1 and 2.</b> Used to identify product type.<br>Set DEVTYPE(2:1) = 00 for the LXT916.<br>Set DEVTYPE(2:1) = 01 for the LXT917.                                                                                                                                                                                                                                                                        |

| 80                                                                                                                                                                           | ARBIN                         | Tri-State Input,<br>PD, NC                   | <b>Arbitration In/Out</b> . Daisy chain hub ID arbitration mechanism #2. If used, tie ARBIN to ARBOUT of the previous device, and to                                                                                                                                                                                                                                                                                |

| 81                                                                                                                                                                           | ARBOUT                        | Output, NC                                   | ground of the first/only device. If unused, tie ARBIN High.                                                                                                                                                                                                                                                                                                                                                         |

| 82<br>83<br>84                                                                                                                                                               | CHIPID2<br>CHIPID1<br>CHIPID0 | TTL Input                                    | <b>Chip ID.</b> These pins assign unique ChipIDs to as many as eight devices on a single module. One device on each module must be assigned ChipID=0.                                                                                                                                                                                                                                                               |

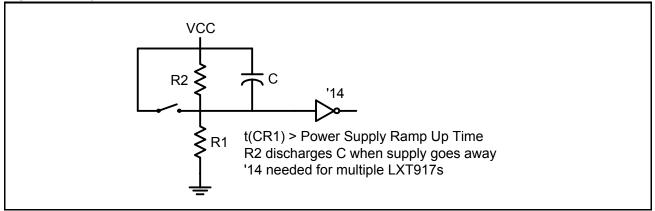

| 102                                                                                                                                                                          | RESET                         | CMOS Input,<br>Schmitt Trigger #1,<br>PU, NC | <b>Reset</b> . This active Low input causes internal circuits and state machines to reset, but does not affect counters or address tracking registers. On power-up, devices should not be brought out of reset until the power supply has stabilized and reached 4.5 volts. When there are multiple devices, it is recommended that all be supplied by a common reset that is driven by an 'LS14 or similar device. |

| 74                                                                                                                                                                           | RESERVED                      | -                                            | <b>Reserved</b> . Reserved for future application development. <i>Leave this pin unconnected</i> .                                                                                                                                                                                                                                                                                                                  |

| 5-7<br>9-11<br>13-15<br>22-26<br>28-37<br>39-41<br>43-45<br>53-54<br>56-60<br>63-65<br>67<br>70<br>75<br>95-101<br>159-162<br>164-166<br>178<br>183<br>185<br>187<br>206-208 | No Connect                    | -                                            | No Connects. Leave these pins unconnected.                                                                                                                                                                                                                                                                                                                                                                          |

PU = Input contains pull-up.

PD = Input contains pull-down.

NC = No Clamp. Pad will not clamp input in the absence of power.

# **FUNCTIONAL DESCRIPTION**

## **INTRODUCTION**

The LXT917 is ideally suited for managed 10 Megabit Ethernet repeater solutions. This device furnishes a complete 12-port repeater with built-in support for RMON and the Repeater MIB. The LXT917 supplies 10BASE-T Ethernet ports with integrated filters, a reversible AUI port, and a 7-pin MAC Interface. In addition, the device furnishes an Inter Repeater Backplane (IRB) and a serial management interface, both of which support multiple devices for cascaded repeater applications. The LXT916 is identical to the LXT917 except that it provides 8 10BASE-T ports, not 12. Unless specifically noted, all references to the LXT917 also apply to the LXT916.

#### 10BASE-T Ports

The LXT917 provides 10BASE-T ports with integrated filters. Level One's patented filter technology helps facilitate low-cost systems which meet EMI requirements. Refer to Table 1 for 10BASE-T port pin assignments and signal descriptions.

#### **AUI Port**

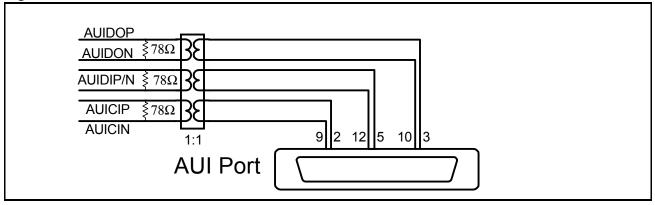

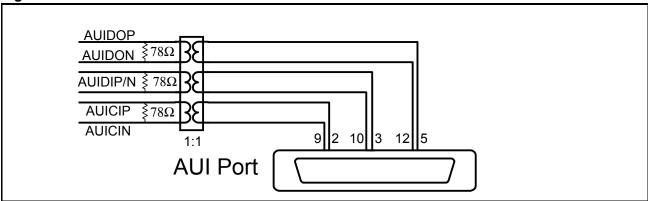

The LXT917 provides a reversible AUI interface that can function either as a DTE or as a MAU. When this interface functions as a MAU, it supports remote-office and embedded-hub applications (such as file servers) by allowing integration of the LXT917 to existing PHY interfaces. The mode of operation is selected externally through the AUI\_MODE pin. Refer to Table 2 for AUI port pin assignments and signal descriptions.

#### Inter-Repeater Backplane

The LXT917 easily accommodates stackable and modular hub architectures through the Inter-Repeater Backplane, which allows multiple devices to function as one logical repeater. For example, typical LXT917 stack designs accomodate as many as 192 10BASE-T ports. Refer to Table 3 for IRB pin assignments and signal descriptions.

#### 7-pin MAC Interface

The LXT917 provides a 7-pin MAC Interface, which can be interfaced to an Ethernet controller. Refer to Table 4 for MAC I/F pin assignments and signal descriptions.

#### **Serial Management Interface**

Multiple devices can easily be managed through the highspeed serial management interface. This synchronous interface operates at rates up to 1 Mbps, and uses an HDLC-like zero-bit insertion protocol. This interface provides access to the RMON and Repeater MIB variables as well as complete control over all device functions and visibility of all status registers. Refer to Table 5 for serial management bus pin assignments and signal descriptions.

## **Management Support**

The LXT917 supports RMON and the Repeater MIB using on-chip 32-bit counters. Counters are provided for each port, including the MAC port, and for the interface as a whole. Interface counters include all of the RMON Statistics group and Repeater MIB Total Octets and Transmit Collisions. Per-port counters include:

| Readable Frames  | Readable Octets  | FCS Errors     |

|------------------|------------------|----------------|

| Alignment Errors | FramesTooLong    | ShortEvents    |

| Runts            | Collisions       | LateEvents     |

| VeryLongEvents   | DataRateMismatch | AutoPartitions |

| Broadcast        | Multicast        | SA Changes     |

## **Source Address Management Functions**

The LXT917 provides Source Address Management functions for all ports. Each port has two source-address tracking registers. The rptrAddrTrackNewLastSrcAddress register is always free-running and contains the source address of the last valid packet received from the port. The Authorized Address Register operates in three states: free-run, lock-on-next or lock. This register can track source addresses or lock on an address that has been assigned by the network manager or that it has previously tracked. Once this register is locked, subsequent Source Address changes on a port cause the device to set the corresponding bits in the SA Change Detection Register and the Interrupt Status Register.

The LXT917 also provides a Source Address Tracking Function. Supplied with a 48-bit Ethernet Source Address, this function identifies all ports that sourced that Source Address.

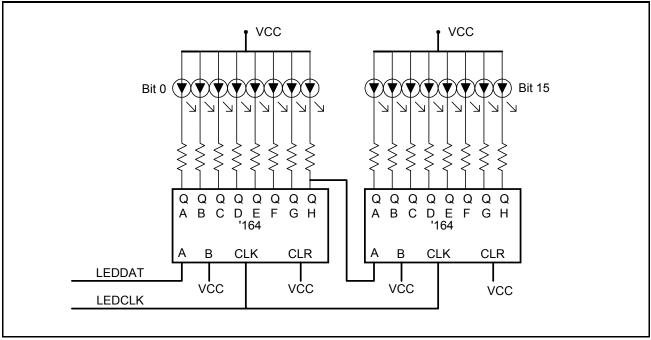

### **LED Interface**

The serial LED interface (data and clock) supplies link and partition status for each of the TP ports, status for the AUI port, and miscellaneous functions. The device directly provides activity and collision LEDs. Refer to Table 6 for LED Interface pin assignments and signal descriptions.

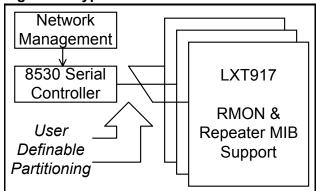

Figure 2: Typical Application Block Diagram

## **REQUIREMENTS**

#### **Power**

The LXT917 requires a single +5V power supply, and a single ground reference. Separate analog and digital grounds are NOT required. Refer to Table 8 for power and ground pin assignments.

#### Clock

The LXT917 requires a continuous 20 MHz clock input, driven with CMOS levels.

#### **RBIAS**

The LXT917 requires a 1% 22 k $\Omega$  resistor connecting its RBIAS input to ground.

#### Reset

At power up, the reset input must be held low until VCC reaches at least 4.5V. An 'LS14 or equivalent should be used to drive reset if there are multiple 917 devices.

#### **PROM**

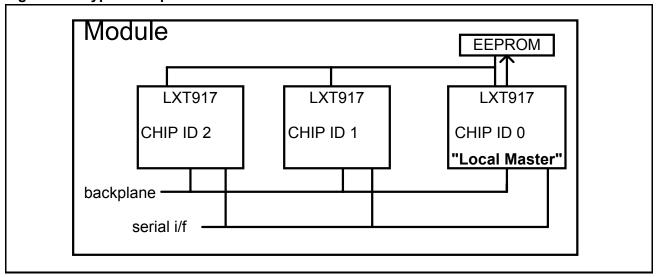

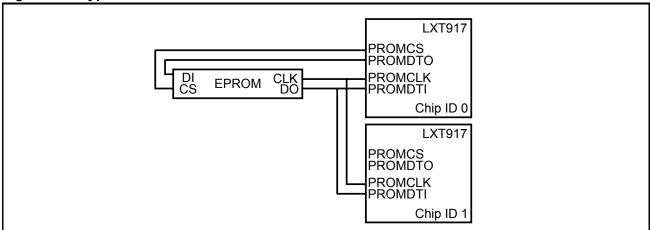

The LXT917 requires an external, auto-incrementing PROM, which is used to supply a 48-bit ID at power-up. If the PROM is not available, the PROM data input signal must be tied either high or low. Multiple devices on the same module can share a single common PROM. Refer to Table 7 for PROM interface pin assignments and signal descriptions.

#### Chip ID

Each LXT917 on a module requires a unique 3-bit Chip ID value asserted on these pins in order for the serial management bus to function correctly. Exactly one and only one LXT917 on each module must be assigned ChipID = 0.

#### MMSTRIN/MMSTROUT

In multiple device applications, the Management Master daisy chain (MMSTRIN/MMSTROUT) ensures that collisions are correctly counted . Connect the MMSTRIN input to the MMSTROUT output of the previous device, even across module boundaries. Ground the MMSTRIN input of the first/only device in the system. In hot-swap applications, resistive bypassing can be used, with a value between 1 and 3  $k\Omega.$

## REPEATER OPERATION

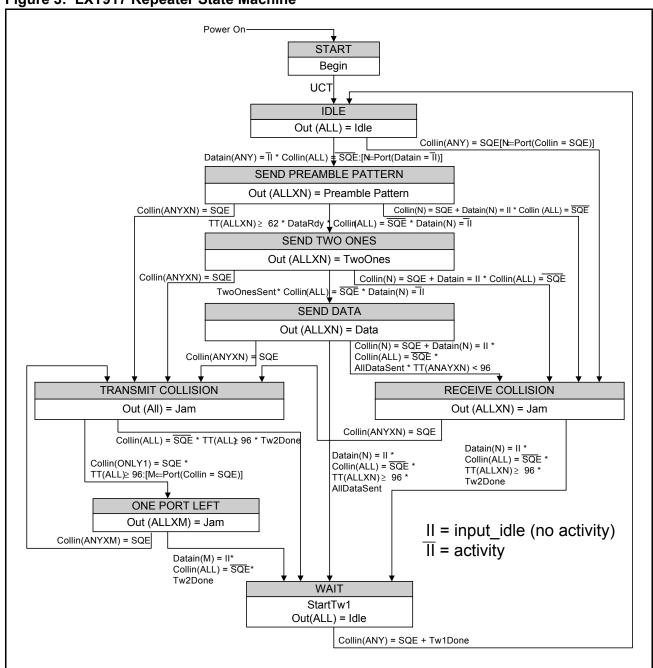

LXT917 repeater operation is controlled by the state machine shown in Figure 3. When the LXT917 detects activity at any input, it begins generating preamble to all other outputs. Once 62 bits of preamble have been transmitted, and a start-of-frame delimiter (SFD) has been received, the device begins repeating the received packet to all outputs. An internal fifo provides buffering. Operation continues until the receiver goes idle, or until the jabber timer is exceeded.

If activity is detected simultaneously at two or more inputs, the LXT917 enters the transmit collision state. The device sends a jam signal to all ports on the repeater for 96 bit times. A jam signal continues to be sent to all ports as long as two or more inputs are active. If activity simultaneously ceases at all inputs, the device returns to the idle state. If activity continues at only one input, the device enters the one-port-left state. In that state, the LXT917 continues to transmit a jam signal to all ports *except* to the one that has the active input. Once this activity ceases, the repeater returns to the idle state.

If the AUI port is functioning as the DTE, and an external MAU activates the CI inputs while the port is active, the device enters the receive collision state. The LXT917 sends a jam signal to all ports (except the AUI port) for at least 96 bit times and until all activity ceases.

In multiple-device configurations, all devices participate in data exchange and the various collision states via the Inter Repeater Backplane.

## **Exception Conditions**

#### **Fragment Extension**

Any received activity shorter than 96 bits (also known as a fragment) will be extended so that it is at least 96 bits long. On the Inter Repeater Backplane, a fragment extension will look like a receive collision, however it will not be counted as a collision.

#### Packets with no SFD

Packets with no start-of-frame delimiter will be repeated to all ports as a long preamble pattern with no SFD. These packets will be counted as "fragments" by the management counters, no matter how long they are.

#### Packets with too early SFD

Any packet with less than 40 bits of preamble will cause the internal fifo to overflow, causing invalid packets to be transmitted to all ports. If the EFIFOERR bit in the Master Configuration register is set when this occurs, a transmit collision will be generated.

#### **Manchester Code Violations**

If the EMCV bit in the Master Configuration register is set, an input packet with Manchester Code Violations will be treated as a transmit collision. If this bit is clear (default), incoming packets with this type of error will simply be repeated to all ports. Note that a packet that does not have a proper end-of-frame marker (2 bit times high with no transitions) will also be flagged as having a Manchester Code Violation.

#### **Data Rate Mismatches**

Severe data rate mismatches will cause the internal fifo to underflow or overflow. Depending on the state of the EFIFOERR bit, these conditions can be treated either as transmit collision, or simply passed along as bad data.

Figure 3: LXT917 Repeater State Machine

#### **Port Functions**

#### Jabber (all ports)

If any input port is active for more than 5 ms, the device will automatically terminate all transmit activity for at least 96 bit times. This will give waiting ports an opportunity to access the network. A port that is continuously babbling will constantly collide with other ports, and will eventually be isolated by the autopartitioning function.

#### Auto-partitioning (all ports)

Any port that causes 32 consecutive collisions will be partitioned as shown in Figure 4. A port will also be partitioned if it continues to be active for more than 100 us after a collision has occurred. Once a port is partitioned, data received from that port is not repeated, until the port is re-connected. There are two re-connection algorithms. The normal algorithm allows a port to be reconnected if a packet can be successfully transmitted or received from the port. The alternative algorithm allows re-connection only if a packet can be successfully transmitted to the port. For re-connection to occur, at least 512 bit times of nonidle, non-collision activity must occur. Once this happens, the port is re-connected after the activity stops. The activity that causes the re-connection is not repeated.

#### Link Integrity Function (10BASE-T ports only)

The device supports the Link Integrity function, which is used to determine if a 10BASE-T connection is working. The function can be enabled on a port-by-port basis. When enabled, the device looks for Link Integrity Pulses from each of the 10BASE-T ports. When these pulses are received from a port, it is put into the "Link Up" state, enabling transmissions to the port, and vice versa. If the Link Integrity function is disabled, the port is forced into the Link Up state. The device generates Link Pulses to all ports, regardless of the Link State of any port or whether the Link Function is enabled or disabled.

# Polarity Detection and Correction (10BASE-T ports only)

The device can detect reversed polarity on any 10BASE-T port and internally correct for it. This function can also be disabled on a port-by-port basis.

#### **SQE Mask (AUI Port only)**

Ethernet MAU devices (also known as transceivers) typically generate an SQE signal (also called heartbeat) on the CI inputs after each data transmission to the MAU. This function is normally supposed to be disabled when a MAU is attached to a repeater, but often times this is overlooked. The result can be a collision at the end of each packet transmitted. An SQE Mask function is provided to overcome this problem. When the Mask is set, SQE heartbeat signals from external MAU's will not be passed on as collisions.

#### **Reverse AUI Mode**

In the reverse mode, the AUI interface operates as a MAU rather than as a DTE. This allows it to directly interface to an LXT901/904/907. In this mode, the following apply:

- <sup>1</sup> The CI pins function as outputs.

- The MaskSQE function determines whether or not the device generates SQE/heartbeat after each successful transmission to the device.

- The AUIDI pins continue to function as inputs, and the AUIDO pins continue to function as outputs. If these signals are being brought out to an external connector, they must be physically swapped from their normal positions (Refer to Figures 11 and 12.)

- The device will loopback data presented at the AUIDI inputs to the AUIDO outputs.

#### Reduced Squelch (10BASE-T ports only)

The squelch threshold on the 10BASE-T receivers can be lowered. This allows the device to detect weaker than normal signals, and can be used to support cables longer than 100m. It also makes the device more sensitive to cross-talk and other noise, and must be used with great care.

Figure 4: LXT917 Partition State Machine Begin **COUNT CLEAR** CC(X) = 0Datain(X) = DIPresent(X) Collin(X) = CIPresent(X) DIPresent(X) = II \*

CIPresent(X) = SQE **COLLISION COUNT IDLE** Datain(X) = DIPresent(X) Collin(X) = CIPresent(X)PARTITION WAIT  $DIPresent(X) = \overline{II} + CIPresent(X) = SQE$ Datain(X) = II  $Collin(X) = \overline{SQE}$ WATCH FOR COLLISION  $DIPresent(X) = II *CIPresent(X) = \overline{SQE}$ StartTw5 Datain(X) = DIPresent(X) Collin(X) = CIPresent(X) **PARTITION HOLD** DIPresent(X) = II \* Datain(X) = II $Collin(X) = \overline{SQE}$  $CIPresent(X) = \overline{SQE}$ Tw5Done \* DIPresent(X) = II \*

CIPresent(X) = SQE CIPresent(X) = SQE $DIPresent(X) = \overline{II} + CIPresent(X) = SQE$ COLLSION COUNT INCREMENT PARTITION COLLISION WATCH CC(X) = CC(X) + 1Datain(X) = DIPresent(X)Datain(X) = II  $Collin(X) = \overline{SQE}$ Collin(X) = CIPresent(X)StartTw6 StartTw5  $CC(X) \ge$  $\begin{array}{c} \text{DIPresent}(X) = \text{II *} \\ \text{CIPresent}(X) = \overline{\text{SQE}} * \\ \text{CC}(\underline{X}) < \text{CCLimit *} \end{array}$ CCLimit + (Tw6Done \* CIPresent(X) = DIPresent(X) = IICIPresent(X) = SQE)SQE CIPresent = SQE Tw6Done Tw5Done \* DIPresent(X) = II \*  $CIPresent(X) = \overline{SQE}$ WAIT TO RESTORE CC(X) = 0 $DIPresent(X) = II * CIPresent(X) = \overline{SQE}$

# **LED FUNCTIONS**

The LXT917 provides a serial LED output and two global LEDs. Two programmable blink rates are provided. Refer to Table 49 for details.

#### **Serial LEDs**

The LXT917 provides a serial LED interface which should be attached to an external shift register. This interface pro-

vides status LEDs for the 10BASE-T and AUI ports. It also provides a global fault LED, a redundant power supply (RPS) LED and a user definable LED. Refer to Figure 17 in the Application section, and to Tables 10 and 11 below for details on the serial LED interface.

## **Activity and Collision LEDs (global)**

These outputs can directly drive LEDs to indicate activity and collision status.

**Table 10: LED-DAT Serial Port Bit Assignments**

| <b>15</b> <sup>1</sup> | 14 | 13 | 12  | 11   | 10   | 9    | 8   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|------------------------|----|----|-----|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| RPS                    | GF | UD | AUI | TP12 | TP11 | TP10 | TP9 | TP8 | TP7 | TP6 | TP5 | TP4 | TP3 | TP2 | TP1 |

1. Bit 15 is shifted out first.

**Table 11: Serial LED Operational Modes**

| Bit  | Name           | SW Control                                                | H/W Control              |                                   |                 |  |  |  |

|------|----------------|-----------------------------------------------------------|--------------------------|-----------------------------------|-----------------|--|--|--|

|      |                |                                                           | On                       | Slow                              | Off             |  |  |  |

| 15   | RPS            | N/A                                                       | Present, No Fault        | Present & Fault                   | Any other state |  |  |  |

| 14   | Global Fault   | On, Off or Slow Blink via<br>Global LED Control Register, | N/A                      | Any Port Partitioned or RPS Fault | Any other state |  |  |  |

| 13   | User Definable | Address 181                                               | N/A                      |                                   |                 |  |  |  |

| 12   | AUI Port LEDs  | On, Off or Fast Blink, via                                | Enabled, Link            | Partitioned                       | Any other state |  |  |  |

| 11:0 | TP Port LEDs   | LED Control Register,<br>Address 176                      | Up, Not Parti-<br>tioned |                                   |                 |  |  |  |

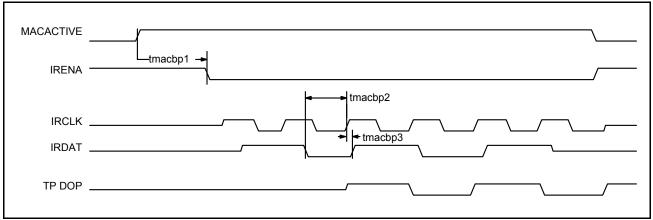

## **IRB OPERATION**

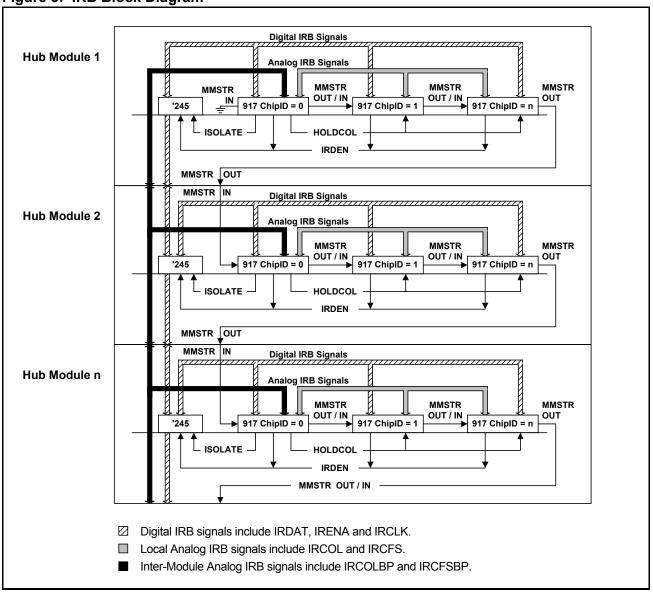

The Inter Repeater Backplane (IRB) allows multiple devices to operate as a single logical repeater, exchanging data collision status information. The IRB uses a combination of digital and analog signals as shown in Figure 5.

## **Data Handling**

Three signals -  $\overline{IRENA}$ , IRDAT and IRCLK - are used to transmit data. All of them can be buffered between modules. A fourth signal - IRDEN - provides directional control of this buffer. IRDAT,  $\overline{IRENA}$  and IRDEN need to be pulled high by 330  $\Omega$  resistors. During a collision, the LXT917 releases all four signals to prevent bus contention.

## **Collision Handling**

Four signals - IRCOL, IRCOLBP, IRCFS and IRCFSBP - handle collisions. IRCFS and IRCOL should be connected between all the devices on any module. IRCFSBP and IRCOLBP should be connected between modules, to the devices that have ChipID = 0.

#### **Collision States**

There are three repeater collision states:

- Receive Collision This occurs when an external transceiver detects a collision. On the LXT917, this can only happen on the AUI port.

- <sup>1</sup> Transmit Collision This occurs when two or more inputs become active at the same time.

- One Port Left This is a special state that can occur after a Transmit Collision, when only one port remains active. This state prevents dead-locks in multiple-repeater configurations.

#### **Collision Indications**

IRCOL and IRCOLBP go low to indicate any collision (receive, transmit or one-port-left). IRCFS and IRCFSBP are three-state signals which are used to detect when a transmit collision occurs. The three states are:

- <sup>1</sup> Idle (+5V). Indicates that no ports are active.

- Single drive (+2.8 volts). Indicates that exactly one port is active (normal data transmission, receive collision, or one-port-left).

- <sup>1</sup> Multiple-drive (0 volts). Indicates that two or more ports are active (transmit collision).

$\overline{\text{IRCFSBP}}$  indicates the number of active drivers across all the ports in a repeater stack.  $\overline{\text{IRCFS}}$  indicates the number of active drivers on the local board, and the first 96-bits of a non-local transmit collision (defined as a collision between a local port and a non-local port, or between two non-local ports). The state of  $\overline{\text{IRCFS}}$  is fed forward to  $\overline{\text{IRCFSBP}}$  by the device with ChipID = 0. To prevent dead-locks,  $\overline{\text{IRCFSBP}}$  is NOT fed back to  $\overline{\text{IRCFS}}$ . During non-local transmit collisions, the signal HOLDCOL is used to hold the local devices in the transmit collision state. Table 12 summarizes the use of these signals.

#### **Collision Hold (HOLDCOL)**

The LXT917 can produce a HOLDCOL signal to prevent dead-locks between IRCFS and IRCFSBP. The device with ChipID = 0 drives HOLDCOL high to indicate that a transmit collision is in progress, and that local devices should remain in the transmit collision state.

#### **MAC IRB Access**

The MACACTIV pin allows an external MAC or other digital ASIC to interface directly to the LXT917 IRB. When the MACACTIV pin is asserted, the LXT917 will drive the  $\overline{IRCFS}$  and  $\overline{IRCFSBP}$  signals on behalf of the external device, allowing it to participate in the transmit collision detection function of  $\overline{IRCFSBP}$ .

#### IRB Isolation

The ISOLATE output is provided to control the enable pins of external bidirectional transceivers. In multi-module applications, it can be used to isolate one module from the rest of the system. Only one device can control this signal. The output state of this pin is controlled by the Isolate bit in the Master Configuration Register.

#### MMSTRIN / MMSTROUT

This daisy chain is provided for correct gathering of statistics in multiple-device configurations. In multiple-module applications, this daisy chain must be maintained across modules. In stand-alone applications, or for the first device in a chain, the MMSTRIN input must be pulled Low in order for the management counters to work correctly.

Table 12: IRCOL and IRCFS Condition Indications

| Condition                                                    | IRCOLBP | IRCOL | IRCFSBP | IRCFS       |

|--------------------------------------------------------------|---------|-------|---------|-------------|

| Idle                                                         | High    | High  | High    | High        |

| Local Data                                                   | High    | High  | Mid     | Mid         |

| Non-Local Data                                               | High    | High  | Mid     | High        |

| Local RxCol or OPL <sup>1</sup>                              | Low     | Low   | Mid     | Mid         |

| Non-local RxCol/OPL <sup>1</sup>                             | Low     | Low   | Mid     | High        |

| Local TxCol or first 96 bits of non-local TxCol <sup>2</sup> | Low     | Low   | Low     | Low         |

| Non-local TxCol after 96 bits <sup>2</sup>                   | Low     | Low   | Low     | Mid or High |

<sup>1.</sup> Receive Collision (RxCol) and One Port Left (OPL) conditions have identical bus characteristics and can be differentiated only by timing. Fragment extensions are generally treated as receive collisions.

Figure 5: IRB Block Diagram

<sup>2.</sup> Manchester code violations and fifo overruns are generally treated as transmit collisions.

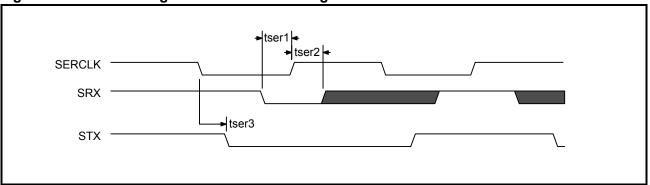

# SERIAL MANAGEMENT I/F

The serial management interface provides access to Repeater MIB variables, RMON Statistics attributes and status and control information. A network manager can access the interface through a simple serial communications controller. The interface is designed to be used in a multi-drop configuration, allowing multiple LXT917 devices to be managed from one common line.

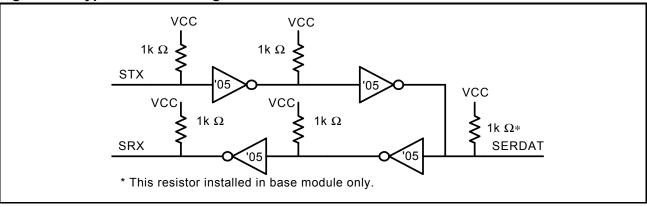

The interface consists of a data input line (SRX), data output line (STX) and a clock (SERCLK), and can operate up to 1 Mbps. The interface operates on a simple command response model, with the network manager as the master and the LXT917 devices as slaves. Figure 6 is a simplified view of typical serial management interface architecture.

Figure 6: Typical Serial I/F Architecture

Figure 7: Serial Management Frame Format

#### **CRC** Start Data Stop Idle Header Idle (2 bytes) Flag Flag Hub ID Chip ID Cmd Length Address 7 bits 5 bits 12 bits 3 bits 5 bits

**Table 13: Serial Management Frame Message Fields**

| Message              | Description                                                                                       |  |  |  |  |  |  |

|----------------------|---------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Start or Stop Flag   | "01111110". Protocol requires zero insertion after any five consecutive "1's" in the data stream. |  |  |  |  |  |  |

| Hub ID               | Identifies module or sub-system. Assigned by one of two arbitration mechanisms at power-up.       |  |  |  |  |  |  |

| Chip ID              | Identifies one of eight modules on a system. Assigned by 3 external pins on each device.          |  |  |  |  |  |  |

| Command              | Identifies the particular operation being performed (see Table 14)                                |  |  |  |  |  |  |

| Length               | Specifies number of registers to be transferred (1 to 127). Maximum is 2 per write, 127 per read. |  |  |  |  |  |  |

| Address              | Specifies address of register or register block to be transferred.                                |  |  |  |  |  |  |

| All fields are trans | All fields are transmitted LSB first.                                                             |  |  |  |  |  |  |

#### **Serial Clock**

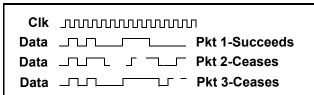

SERCLK is a bidirectional pin; direction control is provided by the RECONFIG input. If RECONFIG is High, the LXT917 will drive SERCLK at 625 kHz. If RECONFIG is Low, SERCLK is an input, between 0 and 1 MHz. There is no lower bound to how slow the interface can operate. The clock can be stopped after each operation, as long as an idle (ten 1's in a row) is transmitted first.

#### Serial Data I/O

The serial data pins, SRX and STX, should be tied together. The SRX input is compared with the STX output. If a mismatch occurs, STX goes to a high impedance. STX is driven on the falling edge of SERCLK. SRX is sampled on the rising edge.

## **Management Format**

Normally the network manager directs read and write operations to a specific LXT917 device using a two-part address consisting of HubID and ChipID. The interface allows up to 127 32-bit registers to be read at one time. Up to two registers can be written at a time.

The interface uses a simple frame format, which is shown in Figure 7. All frames begin and end with a flag of consisting of "01111110". All fields are transmitted LSB first. Zero-bit stuffing is required if more than five 1's in a row appear in the header, data or CRC fields. In addition, all operations directed to the device must be followed by an idle (ten 1's in a row), and the first operation must be preceded with an idle.

**Table 14: Serial Management Instruction Set**

| Command<br>Value | Name            | Usage               | Normally<br>Sent By | Description                                                                            |

|------------------|-----------------|---------------------|---------------------|----------------------------------------------------------------------------------------|

| 18 (Hex)         | Write           | Normal Ops          | Network Mgr         | Used to write up to 2 registers (8 bytes) at a time.                                   |

| 04 (Hex)         | Read            | Normal Ops          | Network Mgr         | Used to read up to 127 registers at a time.                                            |

| 08 (Hex)         | RequestID       | Arbitration         | LXT917              | Requests Hub ID. Repeated periodically.                                                |

| 00 (Hex)         | ConfigChg       | Arbitration         | LXT917              | Notifies system of configuration change (hot swap).<br>Requests new arbitration phase. |

| 10 (Hex)         | Re-arbitrate    | Arbitration         | Network Mgr         | Re-starts arbitration                                                                  |

| 14 (Hex)         | Assign HubID    | Arbitration Mech. 2 | Network Mgr         | Assigns Hub ID to device with ARBIN=0 and ARBOUT = 1 (top of chain)                    |

| 0C (Hex)         | Set Arbout to 1 | Arbitration Mech. 2 | Network Mgr         | Commands specific device to set ARBOUT to 1.                                           |

| 1C (Hex)         | Set Arbout to 0 | Arbitration Mech. 2 | Network Mgr         | Commands specific device to set ARBOUT to 0                                            |

| 02 (Hex)         | DevID           | Config              | Network Mgr         | Generic command for reading device type (no register address needed).                  |

**Table 15: Typical Serial Management Packets**

|                              | Contents of Fields in Serial Management Packet |              |          |              |              |                            |  |  |  |  |

|------------------------------|------------------------------------------------|--------------|----------|--------------|--------------|----------------------------|--|--|--|--|

| Message                      | Hub ID                                         | Chip ID      | Command  | Length       | Address      | Data                       |  |  |  |  |

| Write                        | User Defined                                   | User Defined | 18 (Hex) | 01 or 02     | User Defined | User Defined               |  |  |  |  |

| Read Request                 | User Defined                                   | User Defined | 04 (Hex) | 01 to 7F Hex | User Defined | Null                       |  |  |  |  |

| Read Response                | 00000                                          | 000          | 04 (Hex) | Echo         | Echo         | Data Values                |  |  |  |  |

| Assign Hub ID (Arb Method 1) | 11111                                          | 111          | 18 (Hex) | 02           | 188 Hex      | Formatted per<br>Table 51  |  |  |  |  |

| Assign Hub ID (Arb Method 2) | 11111                                          | 111          | 14 (Hex) | 01           | 0            | Hub ID (LSB)<br>and 27 0's |  |  |  |  |

| Set Arbout to 1              | User Defined                                   | User Defined | 0C (Hex) | 00           | 0            | Null                       |  |  |  |  |

| Set Arbout to 0              | User Defined                                   | User Defined | 1C (Hex) | 00           | 0            | Null                       |  |  |  |  |

| Arb Request                  | 00000                                          | 000          | 08 (Hex) | 02           | 190          | PROM ID                    |  |  |  |  |

| Re-Arbitrate                 | 11111                                          | 111          | 10 (Hex) | 00           | 0            | Null                       |  |  |  |  |

| Request<br>Device ID         | User Defined                                   | User Defined | 02 (Hex) | 01           | 0            | Null                       |  |  |  |  |

| Device ID<br>Response        | 00000                                          | 000          | 02 (Hex) | 01           | 185          | Formatted per Table 50     |  |  |  |  |

| Config Change                | 13 0's                                         | •            | •        |              | •            |                            |  |  |  |  |

#### **Address Arbitration**

Each device has a two part address, consisting of a HubID and a ChipID. The ChipID is assigned the input pins CHIPID<2:0>. The HubID is assigned through one of two arbitration mechanisms.

#### Arbitration Mechanism #1 - EPROM method

This method requires that a PROM be located on each module, and that the ARBSELECT pin (71) not be pulled Low. At power-up, the device with ChipID = 0reads a 48-bit ID from the PROM. All other devices on the module listen in and also record this ID. The device with ChipID = 0 then transmits "Arbitration Request Messages" on the Serial Management Interface every 2-3 milliseconds. The request messages from two modules may collide; if this happens a resolution scheme ensures that only one message will win (see Figure 8). The network manager responds to each request with a message that includes the 48-bit ID and the HubID. All devices hear this message, but only those that match the 48-bit ID receive the HubID as their own. Once the HubID is assigned, the device with ChipID=0 stops sending request messages. It is possible for response messages to be lost due to collisions with request messages.

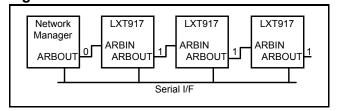

#### Arbitration Mechanism #2 - Chain method

In this method, all of the devices are daisy-chained using the ARBIN and ARBOUT pins. This scenario is shown in Figure 9. The ARBIN input of the first device is directly connected to an output of the network manager. At power-up all the devices drive their ARBOUT outputs High while the network manager drives the ARBIN input to the first device Low. The manager transmits a special "Assign Hub ID" message which is recognized only by the device with ARBIN = Low and ARBOUT = High. The network manager then sends a command addressed to this device which commands it to set its ARBOUT pin Low. This cycle repeats until all devices have been assigned a HubID.

Figure 8: Arbitration Mechanism #1 - Collision Resolution

#### Address Re-arbitration

There are two mechanisms for address re-arbitration following a configuration change, such as a hot-swap of a module:

- Device power up At power-up, the LXT917 normally sends out a "Configuration Change" message (all 0's) on the bus, which causes re-arbitration.

- The network manager can direct or re-start arbitration at any time by sending the "Re-arbitrate" command.

# Source Address Utility Functions

## **Source Address Tracking Function**

Each port has two source address tracking registers. The rptrAddrTrackNewLastSrcAddress register for each port continuously tracks the source addresses of packets emanating from that port. The Authorized Address Register operates in three modes: it can free run, lock, or lock on the next packet. In any mode, it can always be updated by network management.

## **Source Address Matching Function**

The LXT917 has a Source Address Matching Function to discover which port or ports sourced packets with a particular Source Address. The input to the function is an Ethernet Address; the output is a register which identifies any ports that sourced packets with that Source Address.

Figure 9: Arbitration Mechanism #2

# **APPLICATION INFORMATION**

# **MAGNETICS INFORMATION**

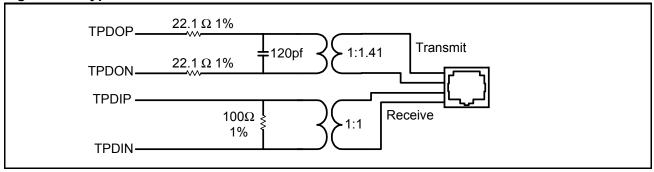

The LXT917 requires a 1:1 ratio for the TP receive transformers and a 1:1.41 ratio for the TP transmit transformers. Table 16 lists suitable transformers by manufacturer and part number. This information was valid as of the printing date of this document. Before committing to a specific component, designers should contact the manufacturer for current product specifications, and should test and validate the magnetics for the specific application to verify that system requirements are met.

## LAYOUT REQUIREMENTS

#### The Twisted Pair Interface

The layout of the twisted-pair port is critical in complex designs. Run the traces directly from the LXT917 to the discrete termination components (located close to the transformers).

The transformer isolation voltage should be rated at  $2 \, kV$  to protect the circuitry from static voltages across the connectors and cables. The traces running from the transformers to the connector should run in close pairs directly to the connector. Be careful not to cross the transmit and receive pairs. One way to avoid this problem is to run the receive

pairs on the component side and the transmit pairs on the solder side. Careful planning during the schematic and layout stages can avoid these problems.

The PCB layout should have no ground or power planes between the transformers and the connectors. The data signals should be the only traces in this area. Place the chassis ground for the connectors near the edge of the PCB, away from the signals, connecting the connector shield with the chassis.

#### The RBIAS Pin

The RBIAS signal sets the levels for the output drivers. Any emissions or common mode noise entering the device here could be measured on the twisted pair output signals.

The LXT917 requires a 22  $k\Omega$ , 1% resistor directly connected between the RBIAS pin and ground. These traces should be as short as possible. The ground traces from adjacent GND pins should come directly off of the device to enclose the resistor and pin forming a shielded area between the RBIAS connection and other signals on the PCB.

## TYPICAL APPLICATION CIRCUITRY

Figures 10 through 17 show typical LXT917 application circuitry. Table 17 summarizes signal operation of the three AUI signal pairs in the two modes (normal and reversed).

Table 16: Suggested Magnetics List<sup>1</sup>

| Manufacturer | Quad Transmit              | Quad Receive               | Quad Tx/Rx (Octal)                        |

|--------------|----------------------------|----------------------------|-------------------------------------------|

| BEL          | S553-5999-02               | S553-5999-03               |                                           |

| HALO         | TD54-1006L1<br>TG54-1006N2 | TD01-1006L1<br>TG01-1006N2 | TG44-S010NX<br>TG45-S010NX<br>TG46-S010NX |

| Nanopulse    | 5976                       | 5977                       |                                           |

| Kappa        | TP4003P                    | TP497P101                  |                                           |

| PCA          | EPE6009                    | EPE6010                    |                                           |

| TDK          | TLA-3T107                  | TLA-3T106                  |                                           |

| VALOR        | PT4116                     | PT4117                     |                                           |

<sup>1.</sup> Before committing to a specific component, designers should contact the manufacturer for current product specifications, and should test and validate the magnetics for the specific application to verify that system requirements are met.

Figure 10: Typical 10BASE-T Port Interface

Figure 11: Normal AUI Circuit

Figure 12: Reversed AUI Circuit

Table 17: AUI Signals - Direction and Pin-Out

| L      | (T917 | AUI Connector Pin # |          |  |  |

|--------|-------|---------------------|----------|--|--|

| Signal | Pin#  | Normal              | Reversed |  |  |

| DOP    | 198   | 3                   | 5        |  |  |

| DON    | 199   | 10                  | 12       |  |  |

| DIP    | 200   | 5                   | 3        |  |  |

| DIN    | 201   | 12                  | 10       |  |  |

| CIP    | 202   | 2                   | 2        |  |  |

| CIN    | 203   | 9                   | 9        |  |  |

Figure 13: Typical IRB Implementation

Figure 14: Typical Serial Management Interface Connections

Figure 15: Typical Chip ID Architecture

Figure 16: Typical EPROM Circuit

Figure 17: Typical Serial LED Interface Circuit

Figure 18: Typical Reset Circuit

# **TEST SPECIFICATIONS**

#### Note

Minimum and maximum values in Tables 18 through 28 and Figures 19 through 23 represent the performance specifications of the LXT917/916 and are guaranteed by test except, where noted, by design.

**Table 18: Absolute Maximum Ratings**

| Parameter             | Symbol | Min  | Max  | Units |

|-----------------------|--------|------|------|-------|

| Supply voltage        | Vcc    | -0.3 | 6    | V     |

| Operating temperature | Тор    | 0    | 70   | °C    |

| Storage temperature   | Tst    | -65  | +150 | °C    |

#### **CAUTION**

Exceeding these values may cause permanent damage. Functional operation under these conditions is not implied.

Exposure to maximum rating conditions for extended periods may affect device reliability.

**Table 19: Operating Conditions**

| Parameter                               | Symbol | Min  | Тур | Max  | Units | Test Conditions |

|-----------------------------------------|--------|------|-----|------|-------|-----------------|

| Recommended supply voltage <sup>1</sup> | Vcc    | 4.75 | 5.0 | 5.25 | V     |                 |

| Recommended operating temperature       | Тор    | 0    | 1   | 70   | °C    |                 |

| VCC current                             | Icc    | -    | 400 | _    | mA    |                 |

<sup>1.</sup> Voltages with respect to ground unless otherwise specified.

Table 20: I/O Electrical Characteristics (Over Recommended Range)

| Parameter          | Sym | Min     | Typ <sup>1</sup> | Max | Units | Test Conditions          |

|--------------------|-----|---------|------------------|-----|-------|--------------------------|

| Input Low voltage  | VIL | _       | 1                | 0.8 | V     | TTL inputs               |

|                    |     | _       | 1                | 2.0 | V     | CMOS inputs <sup>2</sup> |

|                    |     | _       | 1                | 1.0 | V     | Schmitt Trigger #1       |

|                    |     | _       | 1                | 1.0 | V     | Schmitt Trigger #2       |

| Input High voltage | Vih | 2.0     | 1                | 1   | V     | TTL inputs               |

|                    |     | Vcc-2.0 | 1                | ı   | V     | CMOS inputs <sup>2</sup> |

|                    |     | Vcc-1.0 | -                | -   | V     | Schmitt Trigger #1       |

|                    |     | Vcc-2.0 | 1                | -   | V     | Schmitt Trigger #2       |

| Hysteresis voltage | _   | 1.0     |                  |     | V     | Schmitt Trigger #1       |

|                    |     | 0.5     | _                | _   | V     | Schmitt Trigger #2       |

$<sup>1. \ \ \, \</sup>text{Typical values are at 25 °C and are for design aid only; not guaranteed and not subject to production testing.}$

<sup>2.</sup> Does not apply to IRB pins. Refer to Table 23 for IRB I/O characteristics.