# MOS INTEGRATED CIRCUIT μPD44324082, 44324092, 44324182, 44324362

## 36M-BIT DDRII SRAM 2-WORD BURST OPERATION

#### Description

The  $\mu$ PD44324082 is a 4,194,304-word by 8-bit, the  $\mu$ PD44324092 is a 4,194,304-word by 9-bit, the  $\mu$ PD44324182 is a 2,097,152-word by 18-bit and the  $\mu$ PD44324362 is a 1,048,576-word by 36-bit synchronous double data rate static RAM fabricated with advanced CMOS technology using full CMOS six-transistor memory cell.

The  $\mu$ PD44324082,  $\mu$ PD44324092,  $\mu$ PD44324182 and  $\mu$ PD44324362 integrate unique synchronous peripheral circuitry and a burst counter. All input registers controlled by an input clock pair (K and /K) are latched on the positive edge of K and /K.

These products are suitable for application which require synchronous operation, high speed, low voltage, high density and wide bit configuration.

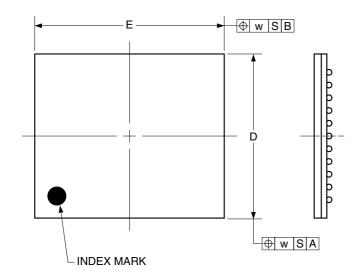

These products are packaged in 165-pin PLASTIC FBGA.

#### **Features**

- 1.8 ± 0.1 V power supply and HSTL I/O

- DLL circuitry for wide output data valid window and future frequency scaling

- Pipelined double data rate operation

- Common data input/output bus

- Two-tick burst for low DDR transaction size

- Two input clocks (K and /K) for precise DDR timing at clock rising edges only

- Two output clocks (C and /C) for precise flight time and clock skew matching-clock and data delivered together to receiving device

- Internally self-timed write control

- Clock-stop capability with μs restart

- User programmable impedance output

- ★ Fast clock cycle time: 3.3 ns (300 MHz), 4.0 ns (250 MHz), 5.0 ns (200 MHz)

- Simple control logic for easy depth expansion

- JTAG boundary scan

The information in this document is subject to change without notice. Before using this document, please confirm that this is the latest version. Not all products and/or types are available in every country. Please check with an NEC Electronics sales representative for availability and additional information.

## **★** Ordering Information

| Part number                | Cycle<br>Time<br>ns | Clock<br>Frequency<br>MHz | Organization (word x bit) | Core Supply<br>Voltage<br>V | I/O<br>Interface | Package         |

|----------------------------|---------------------|---------------------------|---------------------------|-----------------------------|------------------|-----------------|

| μPD44324082F5-E33-EQ2 Note | 3.3                 | 300                       | 4 M x 8-bit               | 1.8 ± 0.1                   | HSTL             | 165-pin PLASTIC |

| μPD44324082F5-E40-EQ2      | 4.0                 | 250                       |                           |                             |                  | FBGA (13 x 15)  |

| μPD44324082F5-E50-EQ2      | 5.0                 | 200                       |                           |                             |                  |                 |

| μPD44324092F5-E33-EQ2 Note | 3.3                 | 300                       | 4 M x 9-bit               |                             |                  |                 |

| μPD44324092F5-E40-EQ2      | 4.0                 | 250                       |                           |                             |                  |                 |

| μPD44324092F5-E50-EQ2      | 5.0                 | 200                       |                           |                             |                  |                 |

| μPD44324182F5-E33-EQ2 Note | 3.3                 | 300                       | 2 M x 18-bit              |                             |                  |                 |

| μPD44324182F5-E40-EQ2      | 4.0                 | 250                       |                           |                             |                  |                 |

| μPD44324182F5-E50-EQ2      | 5.0                 | 200                       |                           |                             |                  |                 |

| μPD44324362F5-E33-EQ2 Note | 3.3                 | 300                       | 1 M x 36-bit              | 1                           |                  |                 |

| μPD44324362F5-E40-EQ2      | 4.0                 | 250                       |                           |                             |                  |                 |

| μPD44324362F5-E50-EQ2      | 5.0                 | 200                       |                           |                             |                  |                 |

Note Under development

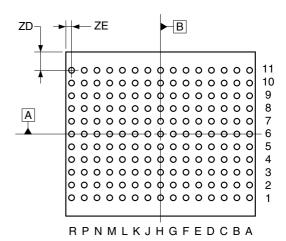

## **Pin Configurations**

/xxx indicates active low signal.

## **165-pin PLASTIC FBGA (13 x 15)** (Top View) [*µ*PD44324082F5-EQ2]

|   | 1    | 2    | 3    | 4     | 5           | 6   | 7           | 8    | 9    | 10   | 11  |

|---|------|------|------|-------|-------------|-----|-------------|------|------|------|-----|

| Α | /CQ  | Vss  | Α    | R, /W | /NW1        | /K  | NC          | /LD  | Α    | Α    | CQ  |

| В | NC   | NC   | NC   | Α     | NC          | К   | /NW0        | Α    | NC   | NC   | DQ3 |

| С | NC   | NC   | NC   | Vss   | Α           | Α   | Α           | Vss  | NC   | NC   | NC  |

| D | NC   | NC   | NC   | Vss   | Vss         | Vss | Vss         | Vss  | NC   | NC   | NC  |

| E | NC   | NC   | DQ4  | VDDQ  | Vss         | Vss | Vss         | VDDQ | NC   | NC   | DQ2 |

| F | NC   | NC   | NC   | VDDQ  | <b>V</b> DD | Vss | <b>V</b> DD | VDDQ | NC   | NC   | NC  |

| G | NC   | NC   | DQ5  | VDDQ  | <b>V</b> DD | Vss | <b>V</b> DD | VDDQ | NC   | NC   | NC  |

| н | /DLL | VREF | VDDQ | VDDQ  | <b>V</b> DD | Vss | <b>V</b> DD | VDDQ | VDDQ | VREF | ZQ  |

| J | NC   | NC   | NC   | VDDQ  | <b>V</b> DD | Vss | <b>V</b> DD | VDDQ | NC   | DQ1  | NC  |

| K | NC   | NC   | NC   | VDDQ  | <b>V</b> DD | Vss | <b>V</b> DD | VDDQ | NC   | NC   | NC  |

| L | NC   | DQ6  | NC   | VDDQ  | Vss         | Vss | Vss         | VDDQ | NC   | NC   | DQ0 |

| M | NC   | NC   | NC   | Vss   | Vss         | Vss | Vss         | Vss  | NC   | NC   | NC  |

| N | NC   | NC   | NC   | Vss   | Α           | Α   | Α           | Vss  | NC   | NC   | NC  |

| Р | NC   | NC   | DQ7  | Α     | Α           | С   | Α           | Α    | NC   | NC   | NC  |

| R | TDO  | тск  | Α    | Α     | Α           | /C  | Α           | Α    | Α    | тмѕ  | TDI |

Α : Address inputs **TMS** : IEEE 1149.1 Test input DQ0 to DQ7 : Data inputs / outputs TDI : IEEE 1149.1 Test input /LD : Synchronous load TCK : IEEE 1149.1 Clock input TDO R, /W : Read Write input : IEEE 1149.1 Test output /NW0, /NW1 : Nibble Write data select  $V_{\mathsf{REF}}$ : HSTL input reference input

K, /K : Input clock  $V_{DD}$ : Power Supply C, /C : Output clock  $V_{DD}Q$ : Power Supply CQ, /CQ Vss : Echo clock : Ground

ZQ : Output impedance matching NC : No connection

/DLL : DLL disable

#### Remarks 1. Refer to Package Drawing for the index mark.

2. 2A and 7A are expansion addresses: 2A for 72Mb and 7A for 144Mb.

## 165-pin PLASTIC FBGA (13 x 15) (Top View) [μPD44324092F5-EQ2]

| _ | 1    | 2           | 3                 | 4           | 5           | 6           | 7           | 8    | 9    | 10   | 11  |

|---|------|-------------|-------------------|-------------|-------------|-------------|-------------|------|------|------|-----|

| Α | /CQ  | <b>V</b> ss | Α                 | R, /W       | NC          | /K          | NC          | /LD  | Α    | Α    | CQ  |

| В | NC   | NC          | NC                | Α           | NC          | K           | /BW0        | Α    | NC   | NC   | DQ4 |

| С | NC   | NC          | NC                | <b>V</b> ss | Α           | Α           | Α           | Vss  | NC   | NC   | NC  |

| D | NC   | NC          | NC                | <b>V</b> ss | Vss         | Vss         | Vss         | Vss  | NC   | NC   | NC  |

| Ε | NC   | NC          | DQ5               | VDDQ        | Vss         | Vss         | Vss         | VDDQ | NC   | NC   | DQ3 |

| F | NC   | NC          | NC                | VDDQ        | <b>V</b> DD | <b>V</b> ss | <b>V</b> DD | VDDQ | NC   | NC   | NC  |

| G | NC   | NC          | DQ6               | VDDQ        | <b>V</b> DD | <b>V</b> ss | <b>V</b> DD | VDDQ | NC   | NC   | NC  |

| н | /DLL | VREF        | V <sub>DD</sub> Q | VDDQ        | <b>V</b> DD | Vss         | <b>V</b> DD | VDDQ | VDDQ | VREF | ZQ  |

| J | NC   | NC          | NC                | VDDQ        | <b>V</b> DD | <b>V</b> ss | <b>V</b> DD | VDDQ | NC   | DQ2  | NC  |

| K | NC   | NC          | NC                | VDDQ        | <b>V</b> DD | Vss         | <b>V</b> DD | VDDQ | NC   | NC   | NC  |

| L | NC   | DQ7         | NC                | VDDQ        | Vss         | Vss         | Vss         | VDDQ | NC   | NC   | DQ1 |

| М | NC   | NC          | NC                | <b>V</b> ss | <b>V</b> ss | <b>V</b> ss | Vss         | Vss  | NC   | NC   | NC  |

| N | NC   | NC          | NC                | <b>V</b> ss | Α           | Α           | Α           | Vss  | NC   | NC   | NC  |

| Р | NC   | NC          | DQ8               | Α           | Α           | С           | Α           | Α    | NC   | NC   | DQ0 |

| R | TDO  | тск         | Α                 | A           | Α           | /C          | Α           | Α    | Α    | TMS  | TDI |

Α : Address inputs **TMS** : IEEE 1149.1 Test input DQ0 to DQ8 : Data inputs / outputs TDI : IEEE 1149.1 Test input /LD : Synchronous load TCK : IEEE 1149.1 Clock input R,/W : IEEE 1149.1 Test output : Read Write input TDO /BW0 : Byte Write data select  $V_{\mathsf{REF}}$ : HSTL input reference input

K, /K : Input clock  $V_{DD}$ : Power Supply C, /C : Output clock  $V_{DD}Q$ : Power Supply CQ, /CQ : Echo clock Vss : Ground ZQ : Output impedance matching NC : No connection

/DLL : DLL disable

## Remarks 1. Refer to Package Drawing for the index mark.

2. 2A and 7A are expansion addresses: 2A for 72Mb and 7A for 144Mb.

## 165-pin PLASTIC FBGA (13 x 15) (Top View) [μPD44324182F5-EQ2]

|   | 1    | 2    | 3    | 4     | 5           | 6   | 7           | 8    | 9    | 10   | 11  |

|---|------|------|------|-------|-------------|-----|-------------|------|------|------|-----|

| Α | /CQ  | Vss  | Α    | R, /W | /BW1        | /K  | NC          | /LD  | Α    | Α    | CQ  |

| В | NC   | DQ9  | NC   | Α     | NC          | K   | /BW0        | Α    | NC   | NC   | DQ8 |

| С | NC   | NC   | NC   | Vss   | Α           | Α0  | Α           | Vss  | NC   | DQ7  | NC  |

| D | NC   | NC   | DQ10 | Vss   | Vss         | Vss | Vss         | Vss  | NC   | NC   | NC  |

| Ε | NC   | NC   | DQ11 | VDDQ  | Vss         | Vss | Vss         | VDDQ | NC   | NC   | DQ6 |

| F | NC   | DQ12 | NC   | VDDQ  | <b>V</b> DD | Vss | <b>V</b> DD | VDDQ | NC   | NC   | DQ5 |

| G | NC   | NC   | DQ13 | VDDQ  | <b>V</b> DD | Vss | <b>V</b> DD | VDDQ | NC   | NC   | NC  |

| н | /DLL | VREF | VDDQ | VDDQ  | <b>V</b> DD | Vss | <b>V</b> DD | VDDQ | VDDQ | VREF | ZQ  |

| J | NC   | NC   | NC   | VDDQ  | <b>V</b> DD | Vss | <b>V</b> DD | VDDQ | NC   | DQ4  | NC  |

| K | NC   | NC   | DQ14 | VDDQ  | <b>V</b> DD | Vss | <b>V</b> DD | VDDQ | NC   | NC   | DQ3 |

| L | NC   | DQ15 | NC   | VDDQ  | Vss         | Vss | Vss         | VDDQ | NC   | NC   | DQ2 |

| M | NC   | NC   | NC   | Vss   | Vss         | Vss | Vss         | Vss  | NC   | DQ1  | NC  |

| N | NC   | NC   | DQ16 | Vss   | Α           | Α   | Α           | Vss  | NC   | NC   | NC  |

| Р | NC   | NC   | DQ17 | Α     | Α           | С   | Α           | Α    | NC   | NC   | DQ0 |

| R | TDO  | тск  | Α    | Α     | Α           | /C  | Α           | Α    | Α    | тмѕ  | TDI |

A0, A : Address inputs **TMS** : IEEE 1149.1 Test input DQ0 to DQ17 : Data inputs / outputs TDI : IEEE 1149.1 Test input /LD : Synchronous load TCK : IEEE 1149.1 Clock input R,/W : Read Write input TDO : IEEE 1149.1 Test output /BW0, /BW1 : Byte Write data select  $V_{\mathsf{REF}}$ : HSTL input reference input

K, /K : Input clock  $V_{DD}$ : Power Supply C, /C : Output clock  $V_{DD}Q$ : Power Supply CQ, /CQ : Echo clock Vss : Ground ZQ : Output impedance matching NC : No connection

/DLL : DLL disable

## Remarks 1. Refer to Package Drawing for the index mark.

- ★ 2. 2A and 7A are expansion addresses: 2A for 72Mb and 7A for 144Mb.

- 3. 2A is internally unconnected.

## 165-pin PLASTIC FBGA (13 x 15) (Top View) [μPD44324362F5-EQ2]

| _ | 1    | 2           | 3                 | 4           | 5           | 6   | 7           | 8    | 9    | 10          | 11   |

|---|------|-------------|-------------------|-------------|-------------|-----|-------------|------|------|-------------|------|

| Α | /CQ  | <b>V</b> ss | Α                 | R, /W       | /BW2        | /K  | /BW1        | /LD  | Α    | <b>V</b> ss | CQ   |

| В | NC   | DQ27        | DQ18              | Α           | /BW3        | K   | /BW0        | A    | NC   | NC          | DQ8  |

| С | NC   | NC          | DQ28              | <b>V</b> ss | Α           | Α0  | Α           | Vss  | NC   | DQ17        | DQ7  |

| D | NC   | DQ29        | DQ19              | Vss         | Vss         | Vss | Vss         | Vss  | NC   | NC          | DQ16 |

| Е | NC   | NC          | DQ20              | VDDQ        | Vss         | Vss | Vss         | VDDQ | NC   | DQ15        | DQ6  |

| F | NC   | DQ30        | DQ21              | VDDQ        | <b>V</b> DD | Vss | <b>V</b> DD | VDDQ | NC   | NC          | DQ5  |

| G | NC   | DQ31        | DQ22              | VDDQ        | <b>V</b> DD | Vss | <b>V</b> DD | VDDQ | NC   | NC          | DQ14 |

| н | /DLL | VREF        | V <sub>DD</sub> Q | VDDQ        | <b>V</b> DD | Vss | <b>V</b> DD | VDDQ | VDDQ | VREF        | ZQ   |

| J | NC   | NC          | DQ32              | VDDQ        | <b>V</b> DD | Vss | <b>V</b> DD | VDDQ | NC   | DQ13        | DQ4  |

| Κ | NC   | NC          | DQ23              | VDDQ        | <b>V</b> DD | Vss | <b>V</b> DD | VDDQ | NC   | DQ12        | DQ3  |

| L | NC   | DQ33        | DQ24              | VDDQ        | Vss         | Vss | Vss         | VDDQ | NC   | NC          | DQ2  |

| М | NC   | NC          | DQ34              | Vss         | Vss         | Vss | Vss         | Vss  | NC   | DQ11        | DQ1  |

| N | NC   | DQ35        | DQ25              | Vss         | Α           | Α   | Α           | Vss  | NC   | NC          | DQ10 |

| Р | NC   | NC          | DQ26              | Α           | Α           | С   | Α           | Α    | NC   | DQ9         | DQ0  |

| R | TDO  | тск         | Α                 | Α           | Α           | /C  | A           | Α    | Α    | тмѕ         | TDI  |

A0, A : Address inputs **TMS** : IEEE 1149.1 Test input DQ0 to DQ35 : Data inputs / outputs TDI : IEEE 1149.1 Test input /LD : Synchronous load TCK : IEEE 1149.1 Clock input R,/W : Read Write input TDO : IEEE 1149.1 Test output /BW0 to /BW3 : Byte Write data select  $V_{\mathsf{REF}}$ : HSTL input reference input

K, /K : Input clock  $V_{DD}$ : Power Supply C, /C : Output clock  $V_{DD}Q$ : Power Supply CQ, /CQ : Echo clock Vss : Ground ZQ : Output impedance matching NC : No connection

/DLL : DLL disable

## Remarks 1. Refer to Package Drawing for the index mark.

**2.** 2A and 10A are expansion addresses: 10A for 72Mb and 2A for 144Mb.

## Pin Identification

| Symbol       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A0<br>A      | Synchronous Address Inputs: These inputs are registered and must meet the setup and hold times around the rising edge of K. All transactions operate on a burst of two words (one clock period of bus activity). A0 is used as the lowest order address bit permitting a random starting address within the burst operation. These inputs are ignored when device is deselected.                                                                                                                                                      |

| DQ0 to DQxx  | Synchronous Data IOs: Input data must meet setup and hold times around the rising edges of K and /K. Output data is synchronized to the respective C and /C data clocks or to K and /K if C and /C are tied to HIGH.  x8 device uses DQ0 to DQ7.  x9 device uses DQ0 to DQ8.  x18 device uses DQ0 to DQ17.  x36 device uses DQ0 to DQ35.                                                                                                                                                                                              |

| /LD          | Synchronous Load: This input is brought LOW when a bus cycle sequence is to be defined. This definition includes address and read/write direction. All transactions operate on a burst of 2 data (one clock period of bus activity).                                                                                                                                                                                                                                                                                                  |

| R, /W        | Synchronous Read/Write Input: When /LD is LOW, this input designates the access type (READ when R, /W is HIGH, WRITE when R, /W is LOW) for the loaded address. R, /W must meet the setup and hold times around the rising edge of K.                                                                                                                                                                                                                                                                                                 |

| /BWx<br>/NWx | Synchronous Byte Writes (Nibble Writes on x8): When LOW these inputs cause their respective byte or nibble to be registered and written during WRITE cycles. These signals must meet setup and hold times around the rising edges of K and /K for each of the two rising edges comprising the WRITE cycle. See Pin Configurations for signal to data relationships.                                                                                                                                                                   |

| K, /K        | Input Clock: This input clock pair registers address and control inputs on the rising edge of K, and registers data on the rising edge of K and the rising edge of /K. /K is ideally 180 degrees out of phase with K. All synchronous inputs must meet setup and hold times around the clock rising edges.                                                                                                                                                                                                                            |

| C, /C        | Output Clock: This clock pair provides a user controlled means of tuning device output data. The rising edge of /C is used as the output timing reference for first output data. The rising edge of C is used as the output reference for second output data. Ideally, /C is 180 degrees out of phase with C. C and /C may be tied HIGH to force the use of K and /K as the output reference clocks instead of having to provide C and /C clocks. If tied HIGH, C and /C must remain HIGH and not be toggled during device operation. |

| CQ, /CQ      | Synchronous Echo Clock Outputs. The rising edges of these outputs are tightly matched to the synchronous data outputs and can be used as a data valid indication. These signals run freely and do not stop when Q tristates.                                                                                                                                                                                                                                                                                                          |

| ZQ           | Output Impedance Matching Input: This input is used to tune the device outputs to the system data bus impedance. DQ and CQ output impedance are set to 0.2 x RQ, where RQ is a resistor from this bump to ground. This pin cannot be connected directly to GND or left unconnected.                                                                                                                                                                                                                                                   |

| /DLL         | DLL Disable: When LOW, this input causes the DLL to be bypassed for stable low frequency operation.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| TMS<br>TDI   | IEEE 1149.1 Test Inputs: 1.8V I/O levels. These balls may be left Not Connected if the JTAG function is not used in the circuit.                                                                                                                                                                                                                                                                                                                                                                                                      |

| TCK          | IEEE 1149.1 Clock Input: 1.8V I/O levels. This pin must be tied to Vss if the JTAG function is not used in the circuit.                                                                                                                                                                                                                                                                                                                                                                                                               |

| TDO          | IEEE 1149.1 Test Output: 1.8V I/O level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| VREF         | HSTL Input Reference Voltage: Nominally V <sub>DD</sub> Q/2. Provides a reference voltage for the input buffers.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| VDD          | Power Supply: 1.8V nominal. See DC Characteristics and Operating Conditions for range.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| VDDQ         | Power Supply: Isolated Output Buffer Supply. Nominally 1.5V. 1.8V is also permissible. See DC Characteristics and Operating Conditions for range.                                                                                                                                                                                                                                                                                                                                                                                     |

| Vss          | Power Supply: Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| NC           | No Connect: These signals are internally connected and appear in the JTAG scan chain as the logic level applied to the ball sites. These signals may be connected to ground to improve package heat dissipation.                                                                                                                                                                                                                                                                                                                      |

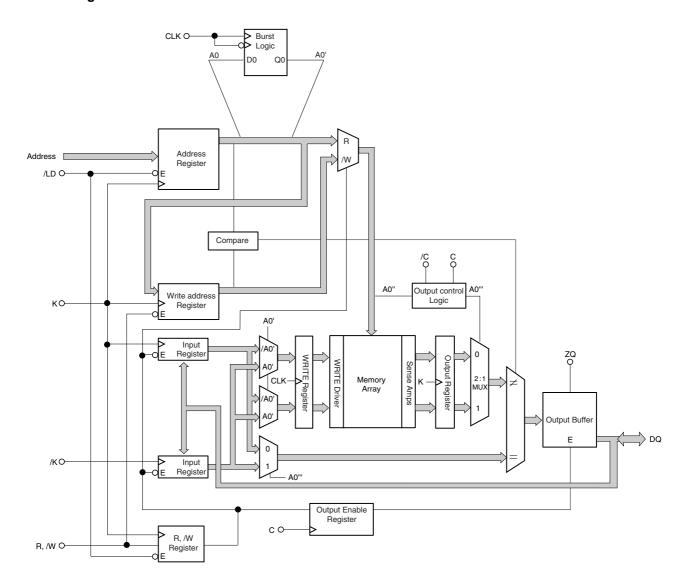

## **Block Diagram**

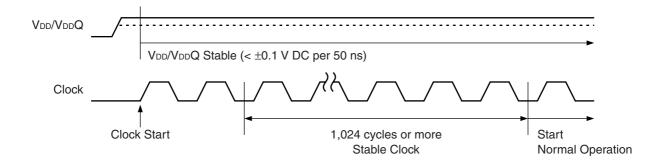

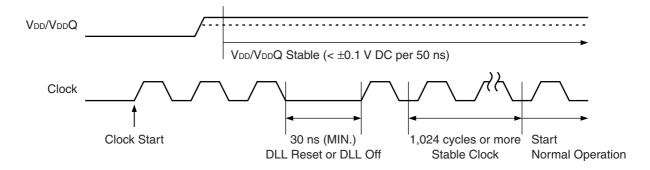

#### ★ Power-on Sequence

The following two timing charts show the recommended power-on sequence, i.e., when starting the clock after  $V_{DD}/V_{DD}Q$  stable and when starting the clock before  $V_{DD}/V_{DD}Q$  stable.

#### 1. Clock starts after VDD/VDDQ stable

#### 2. Clock starts before VDD/VDDQ stable

#### **Burst Sequence**

#### **Linear Burst Sequence Table**

## [ $\mu$ PD44324182, $\mu$ PD44324362]

|                            | A0 | A0 |

|----------------------------|----|----|

| External Address           | 0  | 1  |

| 1st Internal Burst Address | 1  | 0  |

#### **Truth Table**

| Operation                             | /LD | R, /W | CLK               | D              | DQ               |           |           |  |

|---------------------------------------|-----|-------|-------------------|----------------|------------------|-----------|-----------|--|

| WRITE cycle                           | L   | L     | $L\toH$           | Dat            | Data in          |           |           |  |

| Load address, input write data on two |     |       |                   |                | Input data D(A1) |           | D(A2)     |  |

| consecutive K and /K rising edge      |     |       |                   |                | Input clock      | K(t+1) ↑  | /K(t+1) ↑ |  |

| READ cycle                            | L   | Н     | $L\toH$           | Data out       |                  |           |           |  |

| Load address, read data on two        |     |       |                   |                | Output data      | Q(A1)     | Q(A2)     |  |

| consecutive C and /C rising edge      |     |       |                   |                | Output clock     | /C(t+1) ↑ | C(t+2) ↑  |  |

| NOP (No operation)                    | Н   | Х     | $L \rightarrow H$ | High-Z         |                  |           |           |  |

| STANDBY(Clock stopped)                | Х   | Х     | Stopped           | Previous state |                  |           |           |  |

**Remarks 1.** H: High level, L: Low level,  $\times$ : don't care,  $\uparrow$ : rising edge.

- 2. Data inputs are registered at K and /K rising edges. Data outputs are delivered at C and /C rising edges except if C and /C are HIGH then Data outputs are delivered at K and /K rising edges.

- **3.** All control inputs in the truth table must meet setup/hold times around the rising edge (LOW to HIGH) of K. All control inputs are registered during the rising edge of K.

- 4. This device contains circuitry that will ensure the outputs will be in high impedance during power-up.

- **5.** Refer to state diagram and timing diagrams for clarification.

- **6.** A1 refers to the address input during a WRITE or READ cycle. A2 refers to the next internal burst address in accordance with the linear burst sequence.

- 7. It is recommended that K = /K = C = /C when clock is stopped. This is not essential but permits most rapid restart by overcoming transmission line charging symmetrically.

## **Byte Write Operation**

## [*µ*PD44324082]

| Operation        | K                 | /K      | /NW0 | /NW1 |

|------------------|-------------------|---------|------|------|

| Write DQ0 to DQ7 | $L\toH$           | 1       | 0    | 0    |

|                  | _                 | $L\toH$ | 0    | 0    |

| Write DQ0 to DQ3 | $L \rightarrow H$ | ı       | 0    | 1    |

|                  | _                 | $L\toH$ | 0    | 1    |

| Write DQ4 to DQ7 | $L \rightarrow H$ | ı       | 1    | 0    |

|                  | _                 | $L\toH$ | 1    | 0    |

| Write nothing    | $L \rightarrow H$ | ı       | 1    | 1    |

|                  | _                 | $L\toH$ | 1    | 1    |

**Remark** H: High level, L: Low level,  $\rightarrow$ : rising edge.

## [µPD44324092]

| Operation        | K                 | /K                | /BW0 |

|------------------|-------------------|-------------------|------|

| Write DQ0 to DQ8 | $L \rightarrow H$ | _                 | 0    |

|                  | _                 | $L \rightarrow H$ | 0    |

| Write nothing    | $L \rightarrow H$ | _                 | 1    |

|                  | _                 | $L \rightarrow H$ | 1    |

**Remark** H: High level, L: Low level,  $\rightarrow$ : rising edge.

#### [*µ*PD44324182]

| Operation         | K                 | /K                | /BW0 | /BW1 |

|-------------------|-------------------|-------------------|------|------|

| Write DQ0 to DQ17 | $L \rightarrow H$ | 1                 | 0    | 0    |

|                   | -                 | $L\toH$           | 0    | 0    |

| Write DQ0 to DQ8  | $L \rightarrow H$ | . 1               | 0    | 1    |

|                   | _                 | $L\toH$           | 0    | 1    |

| Write DQ9 to DQ17 | $L \rightarrow H$ | 1                 | 1    | 0    |

|                   | _                 | $L \rightarrow H$ | 1    | 0    |

| Write nothing     | $L \rightarrow H$ | ı                 | 1    | 1    |

|                   | _                 | $L \rightarrow H$ | 1    | 1    |

**Remark** H : High level, L : Low level,  $\rightarrow$  : rising edge.

## [*µ*PD44324362]

| [μι ΒττοΣτοοΣ]     |                   |                   |      |      |      |      |

|--------------------|-------------------|-------------------|------|------|------|------|

| Operation          | K                 | /K                | /BW0 | /BW1 | /BW2 | /BW3 |

| Write DQ0 to DQ35  | $L \rightarrow H$ | _                 | 0    | 0    | 0    | 0    |

|                    | _                 | $L \rightarrow H$ | 0    | 0    | 0    | 0    |

| Write DQ0 to DQ8   | $L \rightarrow H$ | _                 | 0    | 1    | 1    | 1    |

|                    | _                 | $L \rightarrow H$ | 0    | 1    | 1    | 1    |

| Write DQ9 to DQ17  | $L \rightarrow H$ | _                 | 1    | 0    | 1    | 1    |

|                    | _                 | $L \rightarrow H$ | 1    | 0    | 1    | 1    |

| Write DQ18 to DQ26 | $L \rightarrow H$ | _                 | 1    | 1    | 0    | 1    |

|                    | _                 | $L \rightarrow H$ | 1    | 1    | 0    | 1    |

| Write DQ27 to DQ35 | $L \rightarrow H$ | _                 | 1    | 1    | 1    | 0    |

|                    | _                 | $L \rightarrow H$ | 1    | 1    | 1    | 0    |

| Write nothing      | $L \rightarrow H$ | _                 | 1    | 1    | 1    | 1    |

|                    | _                 | $L\toH$           | 1    | 1    | 1    | 1    |

$\textbf{Remark} \quad \text{H}: \text{High level, L}: \text{Low level,} \rightarrow : \text{rising edge}.$

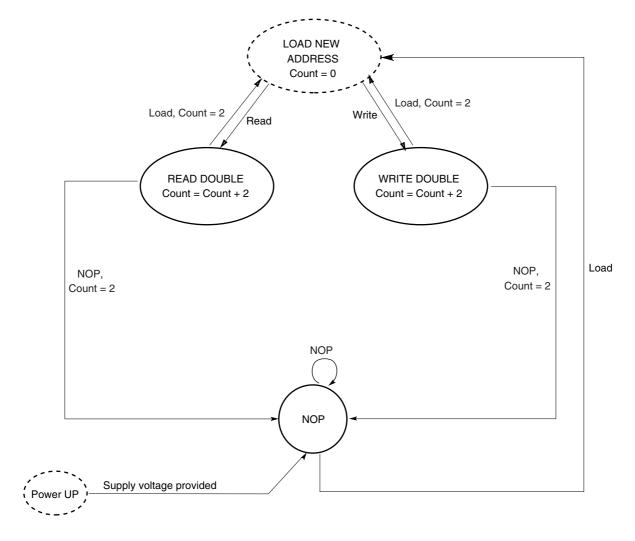

#### **Bus Cycle State Diagram**

**Remarks 1.** A0 is internally advanced in accordance with the burst order table.

Bus cycle is terminated after burst count = 2.

2. State machine control timing sequence is controlled by K.

#### **Electrical Specifications**

#### **Absolute Maximum Ratings**

| Parameter                     | Symbol | Conditions | MIN.        | TYP. | MAX.                    | Unit |

|-------------------------------|--------|------------|-------------|------|-------------------------|------|

| Supply voltage                | VDD    |            | -0.5        |      | +2.5                    | V    |

| Output supply voltage         | VDDQ   |            | -0.5        |      | VDD                     | V    |

| Input voltage                 | VIN    |            | -0.5        |      | VDD + 0.5 (2.5 V MAX.)  | V    |

| Input / Output voltage        | VI/O   |            | -0.5        |      | VDDQ + 0.5 (2.5 V MAX.) | V    |

| Operating ambient temperature | TA     |            | 0           |      | 70                      | °C   |

| Storage temperature           | Tstg   |            | <b>–</b> 55 |      | +125                    | °C   |

Caution Exposing the device to stress above those listed in Absolute Maximum Ratings could cause permanent damage. The device is not meant to be operated under conditions outside the limits described in the operational section of this specification. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability.

#### Recommended DC Operating Conditions (TA = 0 to 70 °C)

| Parameter                | Symbol   | Conditions | MIN.       | TYP. | MAX.                    | Unit | Note |

|--------------------------|----------|------------|------------|------|-------------------------|------|------|

| Supply voltage           | VDD      |            | 1.7        |      | 1.9                     | V    |      |

| Output supply voltage    | VDDQ     |            | 1.4        |      | VDD                     | V    | 1    |

| High level input voltage | VIH (DC) |            | VREF + 0.1 |      | V <sub>DD</sub> Q + 0.3 | V    | 1, 2 |

| Low level input voltage  | VIL (DC) |            | -0.3       |      | VREF - 0.1              | V    | 1, 2 |

| Clock input voltage      | Vin      |            | -0.3       |      | V <sub>DD</sub> Q + 0.3 | V    | 1, 2 |

| Reference voltage        | VREF     |            | 0.68       |      | 0.95                    | V    |      |

Notes 1. During normal operation, VDDQ must not exceed VDD.

2. Power-up:  $V_{IH} \le V_{DD}Q + 0.3 \text{ V}$  and  $V_{DD} \le 1.7 \text{ V}$  and  $V_{DD}Q \le 1.4 \text{ V}$  for  $t \le 200 \text{ ms}$

## Recommended AC Operating Conditions (TA = 0 to 70 °C)

| Parameter                | Symbol   | Conditions | MIN.       | TYP. | MAX.       | Unit | Note |

|--------------------------|----------|------------|------------|------|------------|------|------|

| High level input voltage | VIH (AC) |            | VREF + 0.2 |      | -          | V    | 1    |

| Low level input voltage  | VIL (AC) |            | -          |      | VREF - 0.2 | V    | 1    |

**Note 1.** Overshoot:  $V_{IH (AC)} \le V_{DD} + 0.7 \text{ V}$  for  $t \le TKHKH/2$

Undershoot: VIL (AC)  $\geq$  - 0.5 V for  $t \leq$  TKHKH/2

Control input signals may not have pulse widths less than TKHKL (MIN.) or operate at cycle rates less than TKHKH (MIN.).

DC Characteristics (T<sub>A</sub> = 0 to  $70^{\circ}$ C, V<sub>DD</sub> =  $1.8 \pm 0.1 \text{ V}$ )

| Parameter                 | Symbol   | Test condition                         |      | MIN.        | TYP. | MAX.   |       | Unit  | Note |      |

|---------------------------|----------|----------------------------------------|------|-------------|------|--------|-------|-------|------|------|

|                           |          |                                        |      |             |      | x8, x9 | x18   | x36   |      |      |

| Input leakage current     | lu       |                                        |      | -2          | _    |        | +2    |       | μΑ   |      |

| I/O leakage current       | llo      |                                        |      | -2          | -    |        | +2    |       | μΑ   |      |

| Operating supply current  | IDD      | $VIN \le VIL \text{ or } VIN \ge VIH,$ | -E33 |             |      | 750    | 1,050 | 1,200 | mA   |      |

| (Read Write cycle)        |          | II/O = 0 mA                            | -E40 |             |      | 650    | 900   | 1,000 |      |      |

|                           |          | Cycle = MAX.                           | -E50 |             |      | 550    | 750   | 850   |      |      |

| Standby supply current    | ISB1     | $VIN \le VIL \text{ or } VIN \ge VIH,$ | -E33 |             |      |        | 550   |       | mA   |      |

| (NOP)                     |          | II/O = 0 mA                            | -E40 |             |      |        | 500   |       |      |      |

|                           |          | Cycle = MAX.                           | -E50 |             |      |        | 400   |       |      |      |

| High level output voltage | VOH(Low) | IOH  ≤ 0.1 mA                          |      | VDDQ - 0.2  | _    |        | VDDQ  |       | V    | 3, 4 |

|                           | Vон      | Note1                                  |      | VDDQ/2-0.12 | _    | VDI    | Q/2+0 | ).12  | V    | 3, 4 |

| Low level output voltage  | VOL(Low) | IoL ≤ 0.1 mA                           |      | Vss         | _    |        | 0.2   |       | V    | 3, 4 |

|                           | Vol      | Note2                                  |      | VDDQ/2-0.12 | _    | VDI    | Q/2+0 | ).12  | ٧    | 3, 4 |

**Notes 1.** Outputs are impedance-controlled. | IoH | = (VDDQ/2)/(RQ/5) for values of 175  $\Omega \le RQ \le 350 \ \Omega$ .

- 2. Outputs are impedance-controlled. IoL =  $(V_{DD}Q/2)/(RQ/5)$  for values of 175  $\Omega \le RQ \le 350 \ \Omega$ .

- 3. AC load current is higher than the shown DC values.

- 4. HSTL outputs meet JEDEC HSTL Class I and Class II standards.

## Capacitance (TA = 25 °C, f = 1MHz)

| Parameter                  | Symbol | Test conditions | MIN. | TYP. | MAX. | Unit |

|----------------------------|--------|-----------------|------|------|------|------|

| Input capacitance          | Cin    | VIN = 0 V       |      | 4    | 5    | pF   |

| Input / Output capacitance | CI/O   | VI/O = 0 V      |      | 6    | 7    | pF   |

| Clock Input capacitance    | Cclk   | Vclk = 0 V      |      | 5    | 6    | pF   |

**Remark** These parameters are periodically sampled and not 100% tested.

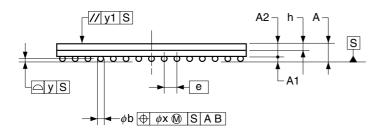

## AC Characteristics (T<sub>A</sub> = 0 to 70 °C, $V_{DD}$ = 1.8 ± 0.1 V)

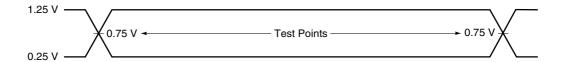

#### **AC Test Conditions**

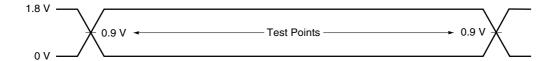

## Input waveform (Rise / Fall time ≤ 0.3 ns)

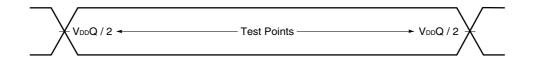

## **Output waveform**

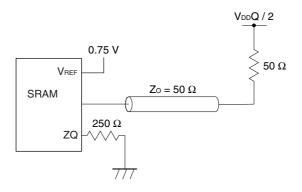

## **Output load condition**

Figure 1. External load at test

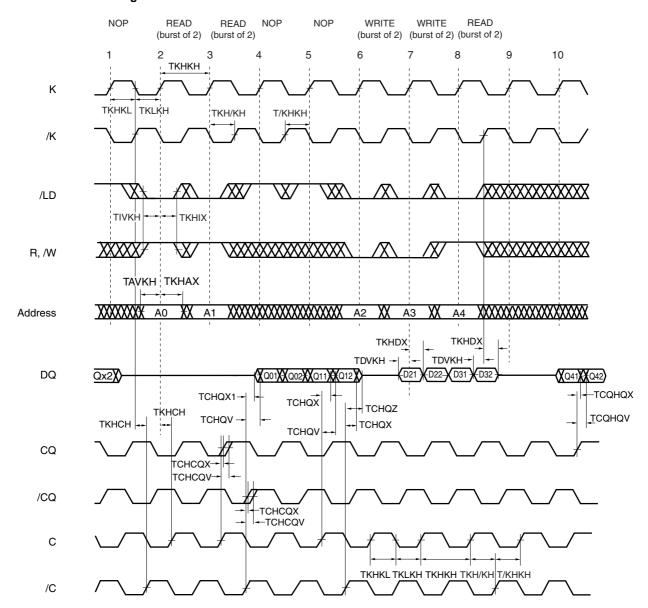

## **Read and Write Cycle**

| Param                         | neter                                   | Symbol    | -E:    |      | -E4    |      | -E5    |      | Unit  | Note |

|-------------------------------|-----------------------------------------|-----------|--------|------|--------|------|--------|------|-------|------|

|                               |                                         |           | (300   | · '  | (250 l |      | (200 l |      |       |      |

|                               |                                         |           | MIN.   | MAX. | MIN.   | MAX. | MIN.   | MAX. |       |      |

| Clock                         |                                         |           |        | ī    | ī      | ı    | ī      | Γ    | 1     |      |

| Average Clock cycle           | Average Clock cycle time (K, /K, C, /C) |           | 3.3    | 8.4  | 4.0    | 8.4  | 5.0    | 8.4  | ns    | 1    |

| Clock phase jitter (K         | , /K, C, /C)                            | TKC var   |        | 0.2  | _      | 0.2  | _      | 0.2  | ns    | 2    |

| Clock HIGH time (K,           | /K, C, /C)                              | TKHKL     | 1.32   | _    | 1.6    | -    | 2.0    | _    | ns    |      |

| Clock LOW time (K,            | /K, C, /C)                              | TKLKH     | 1.32   | _    | 1.6    | -    | 2.0    | _    | ns    |      |

| Clock to /clock (K→/          | K., C→/C.)                              | TKH /KH   | 1.49   | _    | 1.8    | -    | 2.2    | _    | ns    |      |

| Clock to /clock (/K→          | K., /C→C.)                              | T /KHKH   | 1.49   | _    | 1.8    | -    | 2.2    | _    | ns    |      |

| Clock to data clock           | 250 to 300 MHz                          | TKHCH     | 0      | 1.45 | _      | _    | _      | -    | ns    |      |

| (K→C., /K→/C.)                | 200 to 250 MHz                          |           | 0      | 1.8  | 0      | 1.8  | _      | -    |       |      |

|                               | 167 to 200 MHz                          |           | 0      | 2.3  | 0      | 2.3  | 0      | 2.3  | 1     |      |

|                               | 133 to 167 MHz                          |           | 0      | 2.8  | 0      | 2.8  | 0      | 2.8  |       |      |

|                               | < 133 MHz                               |           | 0      | 3.55 | 0      | 3.55 | 0      | 3.55 |       |      |

| DLL lock time (K, C)          |                                         | TKC lock  | 1,024  | _    | 1,024  | -    | 1,024  | -    | Cycle | 3    |

| K static to DLL reset         |                                         | TKC reset | 30     | _    | 30     | _    | 30     | _    | ns    |      |

|                               |                                         | _         |        |      |        |      |        |      |       |      |

| Output Times                  |                                         |           |        |      |        |      |        |      |       |      |

| C, /C HIGH to outpu           | t valid                                 | TCHQV     | _      | 0.45 | _      | 0.45 | _      | 0.45 | ns    |      |

| C, /C HIGH to outpu           | t hold                                  | TCHQX     | - 0.45 | _    | - 0.45 | _    | - 0.45 | _    | ns    |      |

| C, /C HIGH to echo            | clock valid                             | TCHCQV    | _      | 0.45 | _      | 0.45 | _      | 0.45 | ns    |      |

| C, /C HIGH to echo            | clock hold                              | TCHCQX    | - 0.45 | _    | - 0.45 | _    | - 0.45 | _    | ns    |      |

| CQ, /CQ HIGH to ou            | itput valid                             | TCQHQV    | _      | 0.27 | _      | 0.3  | _      | 0.35 | ns    | 4    |

| CQ, /CQ HIGH to ou            | tput hold                               | TCQHQX    | - 0.27 | _    | - 0.3  | _    | - 0.35 | _    | ns    | 4    |

| C HIGH to output Hi           | gh-Z                                    | TCHQZ     | _      | 0.45 | _      | 0.45 | _      | 0.45 | ns    |      |

| C HIGH to output Lo           | w-Z                                     | TCHQX1    | - 0.45 | _    | - 0.45 | _    | - 0.45 | _    | ns    |      |

| ·                             |                                         |           |        |      |        |      |        |      | •     |      |

| Setup Times                   |                                         | 1         |        |      |        |      |        |      |       |      |

| Address valid to K ri         | sing edge                               | TAVKH     | 0.4    | _    | 0.5    | _    | 0.6    | _    | ns    | 5    |

| Synchronous load in           | put (/LD),                              | TIVKH     | 0.4    | _    | 0.5    | _    | 0.6    | _    | ns    | 5    |

| read write input (R, /        | W) valid to                             |           |        |      |        |      |        |      |       |      |

| K rising edge                 |                                         |           |        |      |        |      |        |      |       |      |

| Data inputs and write         | e data select                           | TDVKH     | 0.3    | _    | 0.35   | _    | 0.4    | _    | ns    | 5    |

| inputs (/BWx, /NWx)           | inputs (/BWx, /NWx) valid to            |           |        |      |        |      |        |      |       |      |

| K, /K rising edge             |                                         |           |        |      |        |      |        |      |       |      |

|                               |                                         | _         |        |      |        |      |        |      |       |      |

| Hold Times                    |                                         |           |        |      |        |      |        |      |       |      |

| K rising edge to address hold |                                         | TKHAX     | 0.4    | _    | 0.5    | _    | 0.6    | _    | ns    | 5    |

| K rising edge to              |                                         | TKHIX     | 0.4    | _    | 0.5    | _    | 0.6    | _    | ns    | 5    |

| synchronous load in           | put (/LD),                              |           |        |      |        |      |        |      |       |      |

| read write input (R, /        | W) hold                                 |           |        |      |        |      |        |      |       |      |

| K, /K rising edge to          | data inputs and                         | TKHDX     | 0.3    | _    | 0.35   | -    | 0.4    | _    | ns    | 5    |

| write data select inpo        | uts (/BWx, /NWx)                        |           |        |      |        |      |        |      |       |      |

| hold                          |                                         |           |        |      |        |      |        |      |       |      |

- **Notes 1.** The device will operate at clock frequencies slower than TKHKH(MAX.).

- 2. Clock phase jitter is the variance from clock rising edge to the next expected clock rising edge.

- 3. V<sub>DD</sub> slew rate must be less than 0.1 V DC per 50 ns for DLL lock retention.

- DLL lock time begins once V<sub>DD</sub> and input clock are stable.

- It is recommended that the device is kept inactive during these cycles.

- **4.** Echo clock is very tightly controlled to data valid / data hold. By design, there is a  $\pm$  0.1 ns variation from echo clock to data. The data sheet parameters reflect tester guardbands and test setup variations.

- **5.** This is a synchronous device. All addresses, data and control lines must meet the specified setup and hold times for all latching clock edges.

#### **Remarks 1.** This parameter is sampled.

- **2.** Test conditions as specified with the output loading as shown in AC Test Conditions unless otherwise noted.

- 3. Control input signals may not be operated with pulse widths less than TKHKL (MIN.).

- **4.** If C, /C are tied HIGH, K, /K become the references for C, /C timing parameters.

- **5.** V<sub>DD</sub>Q is 1.5 V DC.

#### **Read and Write Timing**

Remarks 1. Q01 refers to output from address A0.

Q02 refers to output from the next internal burst address following A0, etc.

- 2. Outputs are disable (high impedance) one clock cycle after a NOP.

- The second NOP cycle is not necessary for correct device operation; however, at high clock frequencies it may be required to prevent bus contention.

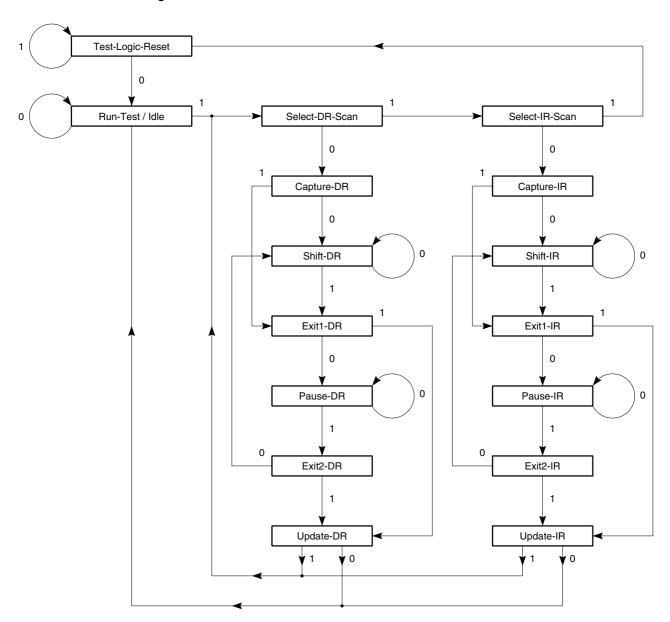

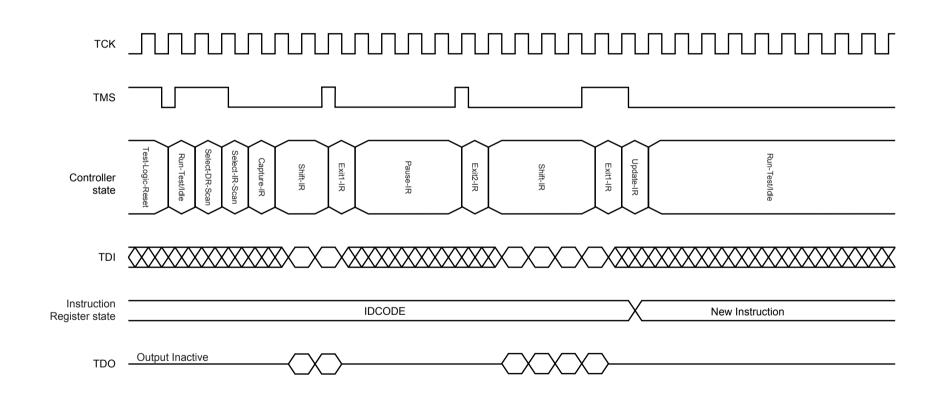

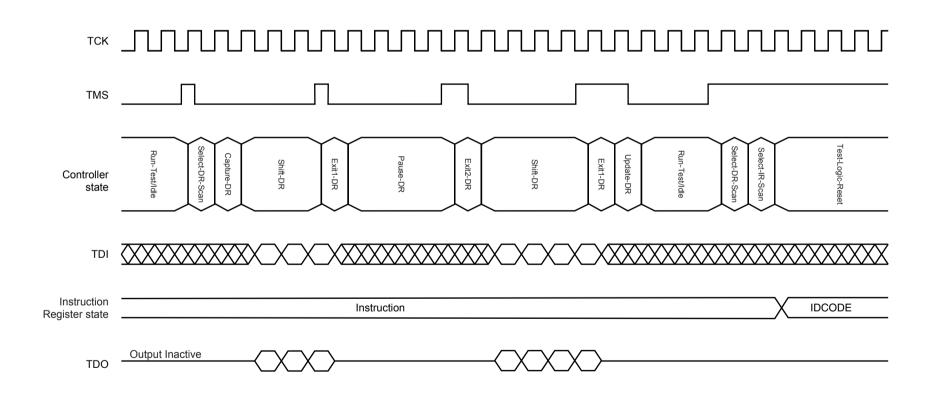

## **JTAG Specification**

These products support a limited set of JTAG functions as in IEEE standard 1149.1.

## **Test Access Port (TAP) Pins**

| Pin name | Pin assignments | Description                                                                                                                                                                                                                                                             |  |  |  |  |  |

|----------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| TCK      | 2R              | Test Clock Input. All input are captured on the rising edge of TCK and all outputs propagate from the falling edge of TCK.                                                                                                                                              |  |  |  |  |  |

| TMS      | 10R             | Test Mode Select. This is the command input for the TAP controller state machine.                                                                                                                                                                                       |  |  |  |  |  |

| TDI      | 11R             | Test Data Input. This is the input side of the serial registers placed between TDI and TDO. The register placed between TDI and TDO is determined by the state of the TAP controller state machine and the instruction that is currently loaded in the TAP instruction. |  |  |  |  |  |

| TDO      | 1R              | Test Data Output. Output changes in response to the falling edge of TCK. This is the output side of the serial registers placed between TDI and TDO.                                                                                                                    |  |  |  |  |  |

**Remark** The device does not have TRST (TAP reset). The Test-Logic Reset state is entered while TMS is held high for five rising edges of TCK. The TAP controller state is also reset on the SRAM POWER-UP.

JTAG DC Characteristics ( $T_A = 0$  to  $70^{\circ}$ C,  $V_{DD} = 1.8 \pm 0.1$  V, unless otherwise noted)

| Parameter                  | Symbol | Conditions                              | MIN. | TYP. | MAX.    | Unit | Note |

|----------------------------|--------|-----------------------------------------|------|------|---------|------|------|

| JTAG Input leakage current | lц     | $0 \text{ V} \leq V_{IN} \leq V_{DD}$   | -5.0 | -    | +5.0    | μΑ   |      |

| JTAG I/O leakage current   | ILO    | $0 \text{ V} \leq V_{IN} \leq V_{DD}Q,$ | -5.0 | -    | +5.0    | μΑ   |      |

|                            |        | Outputs disabled                        |      |      |         |      |      |

| JTAG input high voltage    | ViH    |                                         | 1.3  | -    | VDD+0.3 | ٧    |      |

| JTAG input low voltage     | VIL    |                                         | -0.3 | -    | +0.5    | ٧    |      |

| JTAG output high voltage   | Voh1   | Ioнc   = 100 μA                         | 1.6  | -    | _       | ٧    |      |

|                            | VOH2   | Іонт   = 2 mA                           | 1.4  | _    | _       | ٧    |      |

| JTAG output low voltage    | Vol1   | IoLC = 100 μA                           | _    | _    | 0.2     | ٧    |      |

|                            | VOL2   | IOLT = 2 mA                             | _    | -    | 0.4     | ٧    |      |

## **JTAG AC Test Conditions**

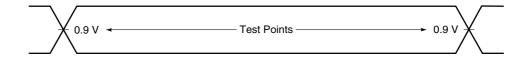

## Input waveform (Rise / Fall time ≤ 1 ns)

## **Output waveform**

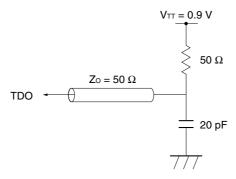

## **Output load**

Figure 2. External load at test

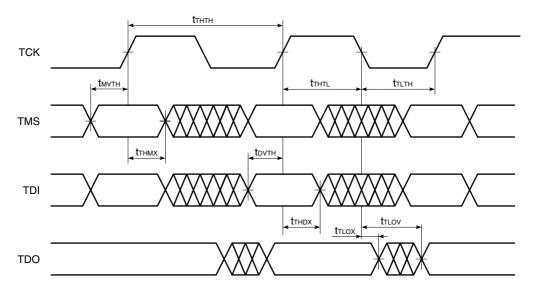

## JTAG AC Characteristics (T<sub>A</sub> = 0 to 70 °C)

| Parameter               | Symbol        | Conditions | MIN. | TYP. | MAX. | Unit | Note |

|-------------------------|---------------|------------|------|------|------|------|------|

| Clock                   |               |            |      |      |      |      |      |

| Clock cycle time        | tтнтн         |            | 100  | _    | _    | ns   |      |

| Clock frequency         | <b>f</b> TF   |            | _    | _    | 10   | MHz  |      |

| Clock high time         | tтнт∟         |            | 40   | _    | _    | ns   |      |

| Clock low time          | tтьтн         |            | 40   | _    | _    | ns   |      |

| Output time             |               |            |      |      |      |      |      |

| TCK low to TDO unknown  | <b>t</b> TLOX |            | 0    | _    | _    | ns   |      |

| TCK low to TDO valid    | <b>t</b> TLOV |            | _    | _    | 20   | ns   |      |

| TDI valid to TCK high   | tоvтн         |            | 10   | _    | _    | ns   |      |

| TCK high to TDI invalid | tтнох         |            | 10   | -    | _    | ns   |      |

| Setup time              | 1             |            |      |      |      |      |      |

| TMS setup time          | <b>t</b> м∨тн |            | 10   | _    | _    | ns   |      |

| Capture setup time      | tcs           |            | 10   | _    | _    | ns   |      |

| Hold time               | 7             |            |      |      |      |      |      |

| TMS hold time           | tтнмх         |            | 10   | _    | _    | ns   |      |

| Capture hold time       | tсн           |            | 10   | _    | _    | ns   |      |

## **JTAG Timing Diagram**

## Scan Register Definition (1)

| Register name        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Instruction register | The instruction register holds the instructions that are executed by the TAP controller when it is moved into the run-test/idle or the various data register state. The register can be loaded when it is placed between the TDI and TDO pins. The instruction register is automatically preloaded with the IDCODE instruction at power-up whenever the controller is placed in test-logic-reset state.                                                                                                                                                                                                              |

| Bypass register      | The bypass register is a single bit register that can be placed between TDI and TDO. It allows serial test data to be passed through the RAMs TAP to another device in the scan chain with as little delay as possible.                                                                                                                                                                                                                                                                                                                                                                                              |

| ID register          | The ID Register is a 32 bit register that is loaded with a device and vendor specific 32 bit code when the controller is put in capture-DR state with the IDCODE command loaded in the instruction register. The register is then placed between the TDI and TDO pins when the controller is moved into shift-DR state.                                                                                                                                                                                                                                                                                              |

| Boundary register    | The boundary register, under the control of the TAP controller, is loaded with the contents of the RAMs I/O ring when the controller is in capture-DR state and then is placed between the TDI and TDO pins when the controller is moved to shift-DR state. Several TAP instructions can be used to activate the boundary register.  The Scan Exit Order tables describe which device bump connects to each boundary register location. The first column defines the bit's position in the boundary register. The second column is the name of the input or I/O at the bump and the third column is the bump number. |

## Scan Register Definition (2)

| Register name        | Bit size | Unit |  |

|----------------------|----------|------|--|

| Instruction register | 3        | bit  |  |

| Bypass register      | 1        | bit  |  |

| ID register          | 32       | bit  |  |

| Boundary register    | 109      | bit  |  |

## **ID Register Definition**

| Part number | Organization | ID [31:28] vendor revision no. | ID [27:12] part no. | ID [11:1] vendor ID no. | ID [0] fix bit |

|-------------|--------------|--------------------------------|---------------------|-------------------------|----------------|

| μPD44324082 | 4M x 8       | XXXX                           | 0000 0000 0011 1101 | 0000010000              | 1              |

| μPD44324092 | 4M x 9       | XXXX                           | 0000 0000 0011 1110 | 0000010000              | 1              |

| μPD44324182 | 2M x 18      | XXXX                           | 0000 0000 0011 1111 | 0000010000              | 1              |

| μPD44324362 | 1M x 36      | XXXX                           | 0000 0000 0100 0000 | 00000010000             | 1              |

#### **SCAN Exit Order**

| Bit |     | Bump |     |      |     |

|-----|-----|------|-----|------|-----|

| no. | x8  | x9   | x18 | x36  | ID  |

| 1   |     | /(   | С   |      | 6R  |

| 2   |     | (    | )   |      | 6P  |

| 3   |     | A    | 4   |      | 6N  |

| 4   |     | A    | 4   |      | 7P  |

| 5   |     | A    | 4   |      | 7N  |

| 6   |     | A    | A   |      | 7R  |

| 7   |     | A    | 4   |      | 8R  |

| 8   |     | A    | 4   |      | 8P  |

| 9   |     | A    | 4   |      | 9R  |

| 10  | NC  | DQ0  | DQ0 | DQ0  | 11P |

| 11  | NC  | NC   | NC  | DQ9  | 10P |

| 12  | NC  | NC   | NC  | NC   | 10N |

| 13  | NC  | NC   | NC  | NC   | 9P  |

| 14  | NC  | NC   | DQ1 | DQ11 | 10M |

| 15  | NC  | NC   | NC  | DQ10 | 11N |

| 16  | NC  | NC   | NC  | NC   | 9M  |

| 17  | NC  | NC   | NC  | NC   | 9N  |

| 18  | DQ0 | DQ1  | DQ2 | DQ2  | 11L |

| 19  | NC  | NC   | NC  | DQ1  | 11M |

| 20  | NC  | NC   | NC  | NC   | 9L  |

| 21  | NC  | NC   | NC  | NC   | 10L |

| 22  | NC  | NC   | DQ3 | DQ3  | 11K |

| 23  | NC  | NC   | NC  | DQ12 | 10K |

| 24  | NC  | NC   | NC  | NC   | 9J  |

| 25  | NC  | NC   | NC  | NC   | 9K  |

| 26  | DQ1 | DQ2  | DQ4 | DQ13 | 10J |

| 27  | NC  | NC   | NC  | DQ4  | 11J |

| 28  | ZQ  |      |     | 11H  |     |

| 29  | NC  | NC   | NC  | NC   | 10G |

| 30  | NC  | NC   | NC  | NC   | 9G  |

| 31  | NC  | NC   | DQ5 | DQ5  | 11F |

| 32  | NC  | NC   | NC  | DQ14 | 11G |

| 33  | NC  | NC   | NC  | NC   | 9F  |

| 34  | NC  | NC   | NC  | NC   | 10F |

| 35  | DQ2 | DQ3  | DQ6 | DQ6  | 11E |

| 36  | NC  | NC   | NC  | DQ15 | 10E |

| Bit         Signal → Mex         Bump           no.         x8         x9         x18         x36         ID           37         NC         NC         NC         NC         10D           38         NC         NC         NC         NC         9E           39         NC         NC         DQT         DQT         10C           40         NC         NC         NC         DQT         11D           41         NC         NC         NC         NC         9C           42         NC         NC         NC         NC         9D           43         DQ3         DQ4         DQ8         DQ8         11B           44         NC         NC         NC         NC         9B           46         NC         NC         NC         NC         10B           47         TC         NC         NC         NC         10B           47         TC         NC         NC         NC         9B           50         TC         NC         NC         NC         9B           51         TC         NC         NC         NC         NC                                                                                                          |     |             |      |      |      |     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------|------|------|------|-----|

| 37         NC         NC         NC         NC         10D           38         NC         NC         NC         NC         9E           39         NC         NC         DQ7         DQ17         10C           40         NC         NC         NC         DQ16         11D           41         NC         NC         NC         NC         9D           42         NC         NC         NC         NC         9D           43         DQ3         DQ4         DQ8         DQ8         11B           44         NC         NC         NC         DQ7         11C           45         NC         NC         NC         PB           46         NC         NC         NC         NC         9B           46         NC         NC         NC         NC         10B           47         TC         TC         NC         NC         10B         9A           48         A         A         A         VS         10A                                                                                           | Bit | Signal name |      |      | Bump |     |

| 38         NC         NC         NC         DQT         DQT         10C           39         NC         NC         DQT         DQT         10C           40         NC         NC         NC         DQT         11D           41         NC         NC         NC         NC         9C           42         NC         NC         NC         NC         9D           43         DQ3         DQ4         DQ8         DQ8         11B           44         NC         NC         NC         DQ7         11C           45         NC         NC         NC         9B           46         NC         NC         NC         NC         10B           47         TC         TC         NC         NC         10B         NC                                                                     | no. | x8          | x9   | x18  | x36  | ID  |

| 39         NC         NC         DQ7         DQ16         11D           40         NC         NC         DQ16         11D           41         NC         NC         NC         QC           42         NC         NC         NC         NC         9D           43         DQ3         DQ4         DQ8         DQ8         11B           44         NC         NC         NC         DQ7         11C           45         NC         NC         NC         DQ7         11C           45         NC         NC         NC         PB           46         NC         NC         NC         NC         10B           47         TO         TO         NC         NC         10B           49         TO         TO         NC         NC         10A         8B           51         TO         TO         NC                                                                                         | 37  | NC          | NC   | NC   | NC   | 10D |

| 40         NC         NC         NC         DQ16         11D           41         NC         NC         NC         NC         9C           42         NC         NC         NC         NC         9D           43         DQ3         DQ4         DQ8         DQ8         11B           44         NC         NC         NC         DQ7         11C           45         NC         NC         NC         DQ8         9B           46         NC         NC         NC         NC         10B           47         TCUT         TUT         11A         48         A         A         A         NC         NC         10B           47         TUT         TUT         TUT         9A         10A         49         11A         48         A         A         A         NC         NC         10A         9A         9A         10A         6C         10A         9A         9A         9A         10A         6C         9A         10A         9C         7A         7A         9A         10A         9B         10A         9C         7A         7A         9B         7A         7A                                                          | 38  | NC          | NC   | NC   | NC   | 9E  |

| 41         NC         NC         NC         NC         9C           42         NC         NC         NC         NC         9D           43         DQ3         DQ4         DQ8         DQ8         11B           44         NC         NC         NC         DQ7         11C           45         NC         NC         NC         DQ8         10B           46         NC         NC         NC         NC         10B           47         TO         TO         NC         10B           48         A         A         A         Vss         10A           49         TO         TO         NC                                                                       | 39  | NC          | NC   | DQ7  | DQ17 | 10C |

| 42       NC       NC       NC       9D         43       DQ3       DQ4       DQ8       DQ8       11B         44       NC       NC       NC       DQ7       11C         45       NC       NC       NC       DQ7       11C         46       NC       NC       NC       NC       10B         47       TOTA       NC       NC       NC       10A         48       A       A       A       Vss       10A         49       TOTA       NC       NC       NC       NC         50       TOTA       NC       NC       NC       NC       NC         52       A       A       AO       AO       AC       AC       NC                                                                                                                                                                        | 40  | NC          | NC   | NC   | DQ16 | 11D |

| 43         DQ3         DQ4         DQ8         DQ8         11B           44         NC         NC         NC         DQ7         11C           45         NC         NC         NC         NC         10B           46         NC         NC         NC         10B           47         TC         TC         11A           48         A         A         A         Vss         10A           49         TA         TA         PS         10A           50         TA         TA         AO         AO         6C           51         TA         A         AO         AO         6C           52         A         A         AO         AO         6C           53         TUT         TUT         RA         AO         AO         6C           53         NC         NC         NC         /BW1         7A         AA         AO         6C         7B         AB                                                                                      | 41  | NC          | NC   | NC   | NC   | 9C  |

| 44         NC         NC         NC         DQ7         11C           45         NC         NC         NC         NC         10B           46         NC         NC         NC         10B           47         TCU         TU         11A           48         A         A         A         Vss         10A           49         TA         TA         SB         SB           50         TA         TA         AO         AC         GC           52         A         A         AO         AO         GC           53         T/LD         TA         SB         A         AG         AC         GC           54         NC         NC         NC         /BW1         7A         AC         AC         SB         AC         AG         AG <td>42</td> <td>NC</td> <td>NC</td> <td>NC</td> <td>NC</td> <td>9D</td> | 42  | NC          | NC   | NC   | NC   | 9D  |

| 45       NC       NC       NC       NC       10B         46       NC       NC       NC       10B         47       TC       TC       NC       11A         48       A       A       A       Vss       10A         49       TA       TS       10A       8B         51       TA       TS       TC       8B         51       TA       A       AO       AO       6C         53       TL       T       8A         54       NC       NC       NC       /BW1       7A         55       /NW0       /BW0       /BW0       /BW0       7B         56       TK       K       6B       6B       6B         57       NC       NC       NC       /BW3       5B         59       /NW1       NC       /BW1       /BW2       5A         60       TX       W       /BW1       /BW2       5A         61       TA       T       5C       4A         61       TA       T       5C       4A         62       TA       T       4A       4A <td< td=""><td>43</td><td>DQ3</td><td>DQ4</td><td>DQ8</td><td>DQ8</td><td>11B</td></td<>                                                                                                                                              | 43  | DQ3         | DQ4  | DQ8  | DQ8  | 11B |

| 46       NC       NC       NC       NC       10B         47       CU       U       11A         48       A       A       A       Vss       10A         49       A       A       A       A       A         50       A       A       AO       AO       6C         52       A       A       AO       AO       6C         53       A       A       AO       AO       6C         54       NC       NC       NC       /BW1       7A         55       /NW0       /BW0       /BW0       /BW0       7B         56       K       K       GB       GB         57       NW1       NC       NC       /BW3       5B         59       /NW1       NC       /BW1       /BW2       5A         60       R       W       /BW1       /BW2       5A         61       A       NC       /BW1       /BW2       5A         62       A       A       A       A       A       A         63       A       A       A       A       A       A         6                                                                                                                                                                                                                                | 44  | NC          | NC   | NC   | DQ7  | 11C |

| 47       CU       111A         48       A       A       A       Vss       10A         49       A       A       A       9A         50       A       A       A0       A0       6C         51       A       A       A0       A0       6C         52       A       A       A0       A0       6C         53       JU       BW       BW       7A         54       NC       NC       NC       BW       7A         55       JNW0       JBW0       JBW0       7B         56       K       GB       6B       7B       6B         57       JW       NC       NC       JBW3       5B         59       JNW1       NC       JBW1       JBW2       5A         60       R       JW       JBW2       5A         61       A       A       A       A       A         61       A       JBW3       A       A       A       A         61       A       JBW3       A       A       A       A       A       A       A       A       A       A                                                                                                                                                                                                                                  | 45  | NC          | NC   | NC   | NC   | 9B  |

| 48       A       A       Vss       10A         49       A       A       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N                                                                                                                                                                              | 46  | NC          | NC   | NC   | NC   | 10B |

| 49       A       SB         50       A       A       RB         51       A       A       AO       AO       6C         52       A       A       AO       AO       6C         53       JLU       BA       AA       AA       ABA       AA       AA       AA       ABA         54       NC       NC       NC       /BW1       7A       ABA       ABA <td< td=""><td>47</td><td></td><td>С</td><td>Q</td><td></td><td>11A</td></td<>                                    | 47  |             | С    | Q    |      | 11A |

| 50       A       A       A0       A0       6C         51       A       A       A0       A0       6C         52       A       A       A0       A0       6C         53       JLU       BA       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A       A </td <td>48</td> <td>Α</td> <td>Α</td> <td>Α</td> <td>Vss</td> <td>10A</td>                                                                                                    | 48  | Α           | Α    | Α    | Vss  | 10A |

| 51         J         J         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         A         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B                                                 | 49  |             | A    | Α    |      | 9A  |