PMC-1991129

ISSUE 7

**DUAL GIGABIT ETHERNET CONTROLLER**

## **PM3386**

## S/UNI-2xGE

# DUAL GIGABIT ETHERNET CONTROLLER

# **DATASHEET**

PROPRIETARY AND CONFIDENTIAL

RELEASED

ISSUE 7: JULY 2001

PMC-1991129

ISSUE 7

**DUAL GIGABIT ETHERNET CONTROLLER**

## **REVISION HISTORY**

| Issue<br>No. | Issue Date | Originator         | Details of Change                                               |  |  |  |  |  |  |

|--------------|------------|--------------------|-----------------------------------------------------------------|--|--|--|--|--|--|

| 7            | July 2001  | Karen              | Release to Production Datasheet                                 |  |  |  |  |  |  |

|              |            | Leandro            | Updated DC Characteristics with qualified values                |  |  |  |  |  |  |

|              |            |                    | Added SERDES Mode                                               |  |  |  |  |  |  |

|              |            |                    | Added GMII/TBI Mode                                             |  |  |  |  |  |  |

|              |            |                    | Modified timing contained within SERDES<br>Transmit Data Timing |  |  |  |  |  |  |

|              |            |                    | Modified timing contained within SERDES Received Data Timing    |  |  |  |  |  |  |

| 6            | Feb 2001   | Karen<br>Leandro   | Added to register descriptions.                                 |  |  |  |  |  |  |

| 5            | Dec 2000   | Karen<br>Leandro   | Updated register defaults                                       |  |  |  |  |  |  |

| 4            | June 2000  | Stuart<br>Robinson | Added pinout and register section.                              |  |  |  |  |  |  |

| 3            | May 2000   | Stuart<br>Robinson | Included Timing Diagrams                                        |  |  |  |  |  |  |

| 2            | Nov 1999   | Stuart<br>Robinson | Preliminary release                                             |  |  |  |  |  |  |

| 1            | Sept 1999  | Stuart<br>Robinson | Created Document.                                               |  |  |  |  |  |  |

5

6

7

8

9

10

10.1

**CONTENTS**

ISSUE 7

#### **DUAL GIGABIT ETHERNET CONTROLLER**

| • • • • • • • • • • • • • • • • • • • • |               |                      |   |  |  |  |  |  |  |

|-----------------------------------------|---------------|----------------------|---|--|--|--|--|--|--|

| 1                                       | DEFI          | DEFINITIONS          |   |  |  |  |  |  |  |

| 2                                       | FEAT          | URES                 | 3 |  |  |  |  |  |  |

|                                         | 2.1           | GENERAL              | 3 |  |  |  |  |  |  |

|                                         | 2.2           | LINE SIDE INTERFACE  | 3 |  |  |  |  |  |  |

|                                         | 2.3           | GIGABIT ETHERNET MAC | 4 |  |  |  |  |  |  |

|                                         | 2.4           | FLOW CONTROL         | 4 |  |  |  |  |  |  |

|                                         | 2.5           | STATISTICS           | 4 |  |  |  |  |  |  |

| 3                                       | APPLICATIONS5 |                      |   |  |  |  |  |  |  |

| 4                                       | REFERENCES6   |                      |   |  |  |  |  |  |  |

APPLICATION EXAMPLES ...... 7

BLOCK DIAGRAM ...... 10

DESCRIPTION ...... 12

PIN DIAGRAM ...... 15

10.2 ENHANCED GIGABIT MEDIA ACCESS CONTROL (EGMAC) .. 44

10.2.1 EGMAC GENERAL ...... 44

10.2.2 EGMAC EGRESS DIRECTION...... 44

10.2.5 EGMAC AUTO-NEGOTIATION 48

SUBLAYER...... 46

10.2.4 EGMAC FLOW CONTROL - MAC CONTROL

ISSUE 7

|    |      | 10.2.6 EGMAC ADDRESS FILTER LOGIC                               | 48  |

|----|------|-----------------------------------------------------------------|-----|

|    | 10.3 | MANAGEMENT STATISTICS (MSTAT)                                   | 48  |

|    | 10.4 | POS-PHY LEVEL 3 PHYSICAL LAYER INTERFACE                        | 49  |

|    |      | 10.4.1 POS-PHY LEVEL 3 GENERAL                                  | 49  |

|    |      | 10.4.2 POS-PHY LEVEL 3 INGRESS PHYSICAL LAYER INTERFACE (PL3IP) | 49  |

|    |      | 10.4.3 POS-PHY LEVEL 3 EGRESS PHYSICAL LAYER INTERFACE (PL3EP)  | 50  |

|    | 10.5 | MICROPROCESSOR INTERFACE                                        | 51  |

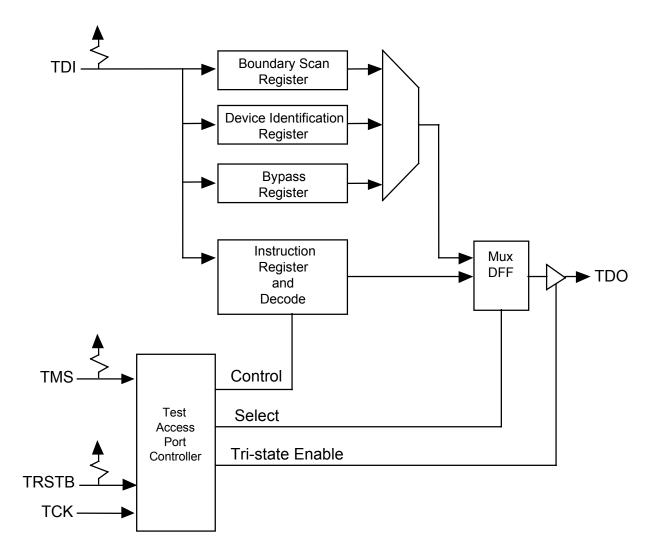

|    | 10.6 | JTAG TEST ACCESS PORT INTERFACE                                 | 51  |

| 11 | NOR  | MAL MODE REGISTER DESCRIPTION                                   | 52  |

| 12 | TEST | FEATURES DESCRIPTION                                            | 234 |

|    | 12.1 | JTAG TEST PORT                                                  | 235 |

| 13 | OPEF | RATION                                                          | 236 |

|    | 13.1 | POWER ON SEQUENCE                                               | 236 |

|    | 13.2 | SYSTEM RESET                                                    | 236 |

|    | 13.3 | GMII VS. SERDES CONFIGURATION                                   | 237 |

|    | 13.4 | SYSTEM CLOCKING                                                 | 237 |

|    |      | 13.4.1 PHY-LINK FREQUENCY SELECTION                             | 237 |

|    |      | 13.4.2 GMII MODE CLOCKING                                       | 237 |

|    |      | 13.4.3 SERDES MODE CLOCKING                                     | 238 |

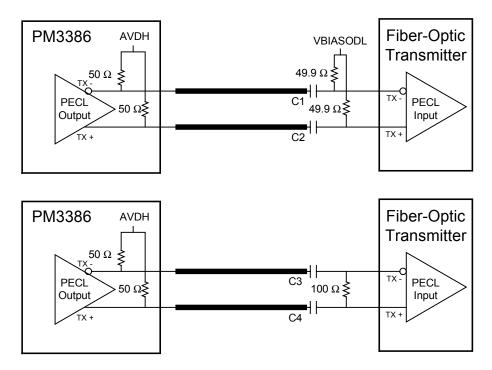

|    | 13.5 | INTERFACING TO ODL                                              | 238 |

|    | 13.6 | GMII INTERFACING                                                | 239 |

|    | 13.7 | TBI INTERFACING                                                 | 240 |

|    | 13.8 | ENABLING AND DISABLING DATA FLOWS                               | 241 |

|    |      |                                                                 |     |

ISSUE 7

|       | 13.8.1 EI | NABLING AND DISABLING INGRESS DATA FLOW | . 241 |

|-------|-----------|-----------------------------------------|-------|

|       | 13.8.2 EI | NABLING AND DISABLING EGRESS DATA FLOW  | . 241 |

| 13.9  | REGIST    | ER ACCESS PROCEDURES                    | . 241 |

|       | 13.9.1 PI | L3IP REGISTER ACCESS PROCEDURE          | . 242 |

|       | 13.9.2 PI | L3EP REGISTER ACCESS PROCEDURE          | . 242 |

|       | 13.9.3 E  | GMAC REGISTER ACCESS PROCEDURE          | . 242 |

| 13.10 | FRAME     | DATA AND BYTE FORMAT                    | . 243 |

| 13.11 | SERDES    | S LOOPBACK                              | . 244 |

| 13.12 | GMII LO   | OPBACK                                  | . 244 |

| 13.13 | IFG MAN   | NIPULATION                              | . 245 |

| 13.14 | FRAME     | LENGTH SUPPORT                          | . 245 |

| 13.15 | TRANSI    | IIT PADDING AND CRC GENERATION          | . 246 |

| 13.16 | MII OPE   | RATIONS                                 | . 248 |

|       | 13.16.1   | MII READ ACCESS                         | . 248 |

|       | 13.16.2   | MII WRITE ACCESS                        | . 248 |

| 13.17 | AUTO-N    | EGOTIATION                              | . 248 |

|       | 13.17.1   | MONITORING AUTO-NEGOTIATION             | . 250 |

|       | 13.17.2   | MODIFYING AUTO-NEGOTIATION              | . 250 |

|       | 13.17.3   | CONTROL OF AUTO-NEGOTIATION             | . 250 |

| 13.18 | TX_ER A   | ASSERTION CRITERIA                      | . 250 |

| 13.19 | FRAME     | FILTERING                               | . 251 |

|       | 13.19.1   | GROUP MULTICAST ADDRESS FILTERING       | . 251 |

|       | 13.19.2   | EXACT MATCH FILTER PROGRAM OPTIONS      | . 252 |

|       | 13.19.3   | EXACT MATCH FILTER OPERATION            | . 253 |

14

15

16

17

18

| 100115 7 | DUAL GIGARIT STUERNET CONTROLLER |

|----------|----------------------------------|

| ISSUE 7  | DUAL GIGABIT ETHERNET CONTROLLER |

| 13.19.4 ADDRESS FILTER ACCEPT / DISCARD       |  |  |  |  |  |  |  |  |

|-----------------------------------------------|--|--|--|--|--|--|--|--|

| EVALUATION 253                                |  |  |  |  |  |  |  |  |

| 13.19.5 ADDRESS FILTER PROGRAMMING 254        |  |  |  |  |  |  |  |  |

| 13.20 PAUSE FLOW CONTROL                      |  |  |  |  |  |  |  |  |

| 13.20.1 INTERNAL FIFO FLOW CONTROL 257        |  |  |  |  |  |  |  |  |

| 13.20.2 EXTERNAL SIDE-BAND PAUSE REQUEST 257  |  |  |  |  |  |  |  |  |

| 13.20.3 EXTERNAL HOST BASED PAUSE REQUEST 258 |  |  |  |  |  |  |  |  |

| 13.20.4 RECEPTION OF 802.3 PAUSE FRAMES 258   |  |  |  |  |  |  |  |  |

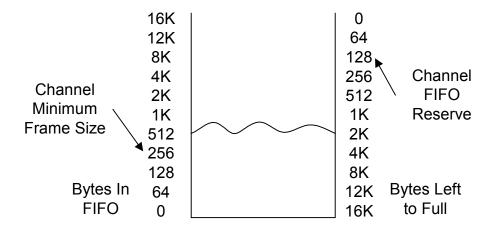

| 13.21 INGRESS POS-PHY BUFFER THRESHOLDS258    |  |  |  |  |  |  |  |  |

| 13.22 EGRESS POS-PHY BUFFER THRESHOLDS 260    |  |  |  |  |  |  |  |  |

| 13.23 POS-PHY PARITY SELECTION                |  |  |  |  |  |  |  |  |

| 13.24 POS-PHY FRAME BURST SIZES               |  |  |  |  |  |  |  |  |

| 13.25 INTERRUPT HANDLING                      |  |  |  |  |  |  |  |  |

| 13.26 JTAG SUPPORT                            |  |  |  |  |  |  |  |  |

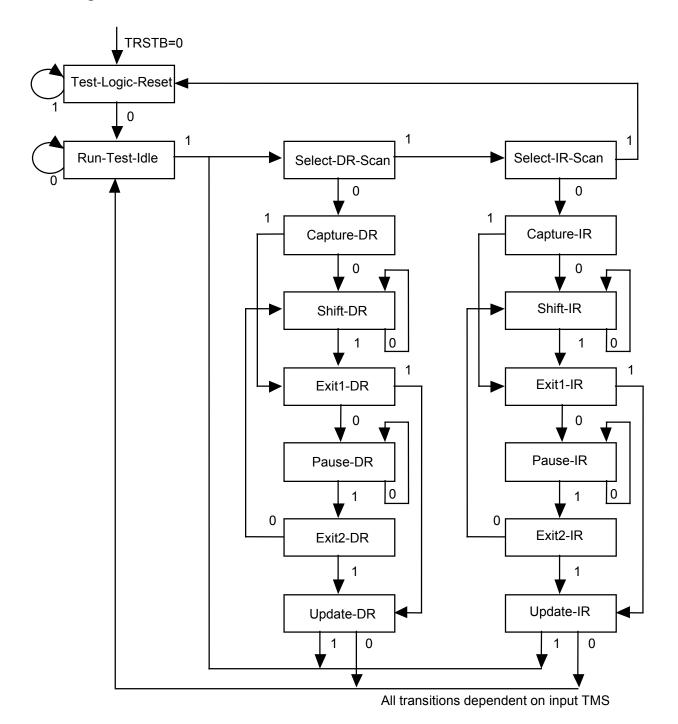

| 13.26.1 TAP CONTROLLER                        |  |  |  |  |  |  |  |  |

| 13.27 FIELD GUIDE TO FIRST PACKET             |  |  |  |  |  |  |  |  |

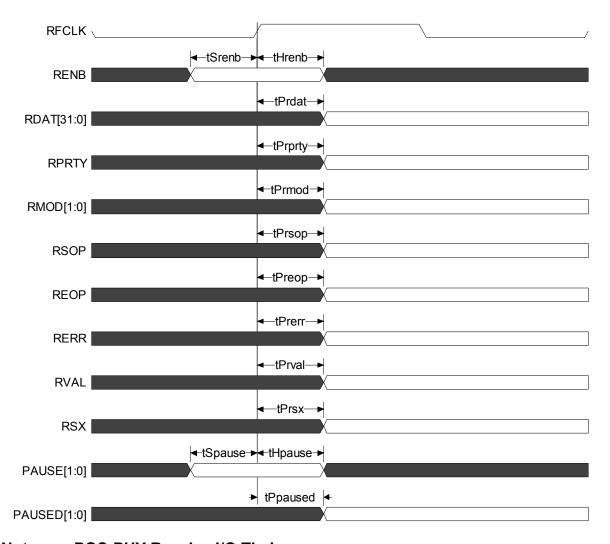

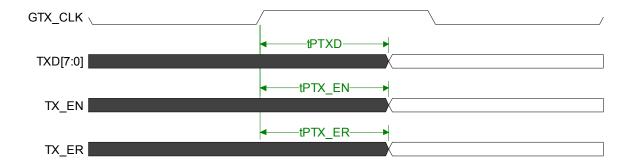

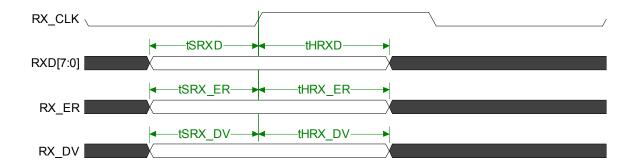

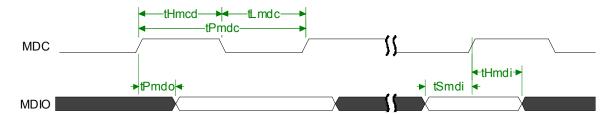

| FUNCTIONAL TIMING                             |  |  |  |  |  |  |  |  |

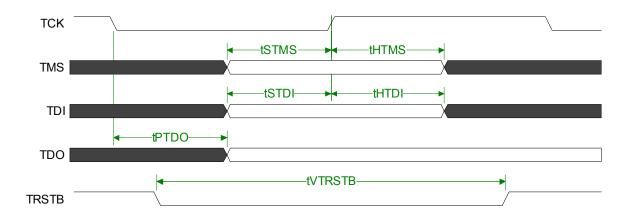

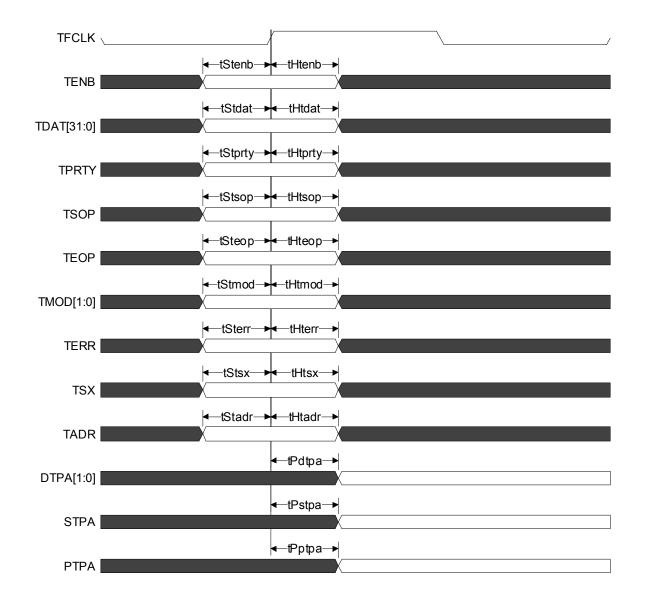

| 14.1 POS-PHY LEVEL 3 INTERFACE                |  |  |  |  |  |  |  |  |

| 14.2 GMII INTERFACE                           |  |  |  |  |  |  |  |  |

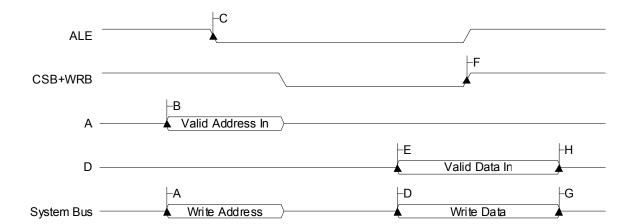

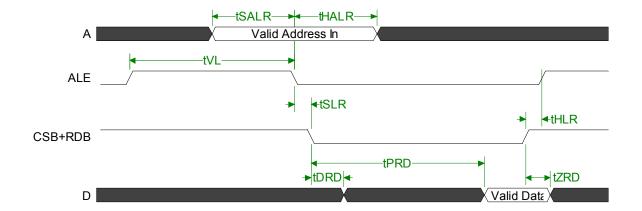

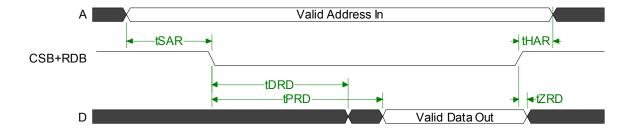

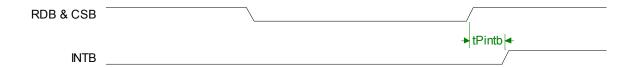

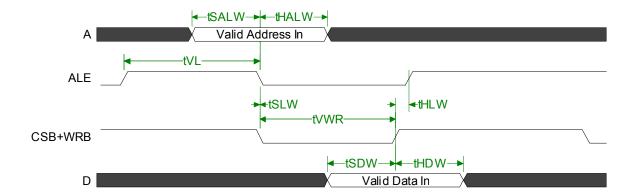

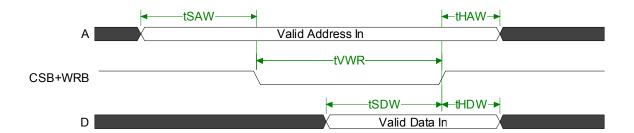

| 14.3 MICROPROCESSOR INTERFACE                 |  |  |  |  |  |  |  |  |

| ABSOLUTE MAXIMUM RATINGS                      |  |  |  |  |  |  |  |  |

| D.C. CHARACTERISTICS                          |  |  |  |  |  |  |  |  |

| INTERFACE TIMING CHARACTERISTICS              |  |  |  |  |  |  |  |  |

| ORDERING AND THERMAL INFORMATION              |  |  |  |  |  |  |  |  |

| ORDERING AND THERMAL INFORMATION 304          |  |  |  |  |  |  |  |  |

RELEASED

DATASHEET

PMC-1991129

ISSUE 7

PM3386

DUAL GIGABIT ETHERNET CONTROLLER

ISSUE 7

DUAL GIGABIT ETHERNET CONTROLLER

## 1 DEFINITIONS

| CSMA/CD           | Carrier Sense Multiple Access with Collision Detection.              |

|-------------------|----------------------------------------------------------------------|

| 1000BASE-T        | IEEE 802.3-1998 Physical Layer specification for 1000 Mb/s           |

| 1000DAGE-1        | CSMA/CD LAN using four pairs of Category 5 balanced copper           |

|                   | cabling.                                                             |

| 1000BASE-SX       | IEEE 802.3-1998 using short wavelength laser devices over            |

| TOOOD/TOL OX      | multimode fiber                                                      |

| 1000BASE-LX       | IEEE 802.3-1998 using long wavelength laser devices over             |

| TOOOD/ TOE EX     | multimode and single-mode fiber.                                     |

| Auto-Negotiation  | The algorithm that allows two devices at either end of a link        |

| / tato regulation | segment to negotiate common data service functions.                  |

| Base Page         | The first 16-bit message exchanged during IEEE 802.3-1998            |

| 3.2.2.3           | Auto-Negotiation.                                                    |

| Comma             | The seven-bit sequence that is part of an 8B/10B code-group          |

|                   | that is used for the purpose of code-group alignment.                |

| Comma-            | The seven-bit sequence (1100000) of an encoded data                  |

|                   | stream.                                                              |

| Comma+            | The seven-bit sequence (0011111) of an encoded data stream.          |

| Data Frame        | Consists of Destination Address, Source Address, Length              |

|                   | Field, logical link control (LLC) Data, PAD, and Frame Check         |

|                   | Sequence.                                                            |

| DTE               | Any source or destination of data connected to the local area        |

|                   | network.                                                             |

| EOF               | End of frame.                                                        |

| EOP               | End of packet                                                        |

| Even Parity       | The count of the number of 1's in the data word of n bits. If        |

|                   | there are an odd number of 1s, then the parity bit will be a 1 so    |

|                   | that including the parity bit, the number of 1s are an even          |

| _                 | number.                                                              |

| Frame             | Same as Data Frame                                                   |

| Full Duplex       | A mode of operation that supports simultaneous                       |

|                   | communication between a pair of stations, provided that the          |

|                   | Physical Layer is capable of supporting simultaneous                 |

| 0.111             | transmission and reception without interference.                     |

| GMII              | Gigabit Media Independent Interface.                                 |

| IPG               | Inter-Packet Gap (IPG): A delay or time gap between                  |

|                   | CSMA/CD physical packets intended to provided interframe             |

|                   | recovery time for other CSMA/CD sublayers and for the                |

| MID               | Physical Medium.  Management Information Page (MIR): A repository of |

| MIB               | Management Information Base (MIB): A repository of                   |

|                   | information to describe the operation of specific network            |

|                   | device.                                                              |

ISSUE 7 DUAL GIGABIT ETHERNET CONTROLLER

| MAC             | Media Access Control (MAC): The data link sublayer that is responsible for transferring data to and from the Physical |

|-----------------|-----------------------------------------------------------------------------------------------------------------------|

|                 | · ·                                                                                                                   |

| B 411           | Layer.                                                                                                                |

| MII             | Media independent Interface (MII): A transparent signal                                                               |

|                 | interface at the bottom of the Reconciliation sublayer.                                                               |

| Next Page       | General class of pages optionally transmitted by Auto-                                                                |

|                 | Negotiation able devices following the base page word                                                                 |

|                 | negotiation.                                                                                                          |

| Nibble          | A group of four data bits. The unit of exchange on the MII.                                                           |

| Packet          | The logical unit of data transferred across the POS-PHY Level                                                         |

|                 | 3 interface. This generally corresponds to the Data Frame as                                                          |

|                 | defined previously, although the CRC may or may not be                                                                |

|                 | present in the POS-PHY Level 3 egress direction.                                                                      |

| Physical Packet | Consists of a Data Frame as defined previously, preceded by                                                           |

|                 | the Preamble and the Start Frame Delimiter, encoded, as                                                               |

|                 | appropriate, for the Physical Layer (PHY) type.                                                                       |

| POS-PHY         | SATURN compatible Packet over SONET interface                                                                         |

|                 | specification for physical layer devices. POS-PHY level 3                                                             |

|                 | defines an interface for bit rates up to and including 2.488                                                          |

|                 | Gbit/s.                                                                                                               |

| PL3             | Short hand notation for the POS-PHY Level 3 term.                                                                     |

| Odd Parity      | The count of the number of 1's in the data word of n bits. If                                                         |

|                 | there are an odd number of 1s, then the parity bit will be a 0 so                                                     |

|                 | that including the parity bit, the number of 1s are an odd                                                            |

|                 | number                                                                                                                |

| SOF             | Start of Frame.                                                                                                       |

| SOP             | Start of Packet.                                                                                                      |

|                 |                                                                                                                       |

**DUAL GIGABIT ETHERNET CONTROLLER**

#### 2 FEATURES

#### 2.1 General

- Two port full-duplex Gigabit Ethernet Controller with an industry standard POS-PHY Level 3 system interface.

- Provides direct connect to optics via two internal Serializer/Deserializer (SERDES)

- Provides connection to copper Gigabit Ethernet physical layer devices via two GMII interfaces.

- Incorporates dual SERDES, compatible to IEEE 802.3 1998 PMA physical layer specification.

- Provides on-chip data recovery and clock synthesis.

- Supports dual IEEE 802.3 -1998 GMII interfaces for connection to copper Gigabit Ethernet physical layer devices.

- Provides dual standard IEEE 802.3 Gigabit Ethernet MACs for frame verification.

- Enables frame filtering on 8 unicast or 64 multicast entries.

ISSUE 7

- Internal 16k byte egress and 64k byte ingress FIFOs per channel to accommodate system latencies.

- Incorporates SATURN POS-PHY Level 3 32-bit System Interface clocked up to 104 MHz (32 bit mode only).

- Line side loopback capability for system level diagnostic capability.

- Includes 16 bit generic microprocessor interface for device initialization, control, register and per port statistics access.

- Provides a standard 5 signal P1149.1 JTAG test port for boundary scan board test purposes.

- Low power 1.8V CMOS device with 3.3V TTL compatible digital inputs (5V TTL compatible microprocessor inputs) and 3.3V CMOS/TTL compatible digital outputs within a 352 pin 27mm by 27mm UBGA package.

- Industrial temperature range (-40°C to +85°C).

#### 2.2 Line Side Interface

- SERDES interface provides 2 differential pairs at 1250 MHz for connection to electrical optical modules.

- GMII interface provides 8 bit wide TX & RX data interfaces at 125 MHz with control signals for connection to copper Gigabit Ethernet physical layer devices.

- Allows selection between SERDES and GMII interface on a per channel basis.

**DUAL GIGABIT ETHERNET CONTROLLER**

#### 2.3 Gigabit Ethernet MAC

- Verifies frame integrity (i.e. FCS and length checks).

- Erred frames can be filtered or passed to higher layer device.

ISSUE 7

- Automatic Base page Auto-Negotiation, extended Auto-Negotiation (Next Page) supported via host.

- Egress Ethernet physical frame encapsulation (pad to min size, add preamble, IFG and CRC generation).

- Supports Ethernet 2.0, IEEE 802.3 LLC and IEEE 802.3 SNAP/LLC encoding formats and VLAN tagged frames.

- Provides 8 unicast exact-match address filters to filter frames based on DA or SA with optional VID.

- Each address filter can be programmed to indicate whether to accept or discard based on a match.

- Provides a 64 group multicast address filter.

- Supports 64 byte minimum size frames and jumbo frames up to 9.6K bytes.

- Programmable Inter-packet gap (IPG).

- System side loopback through GMAC for diagnostic capability.

#### 2.4 Flow Control

- Supports IEEE 802.3-1998 flow control at each Ethernet port if enabled.

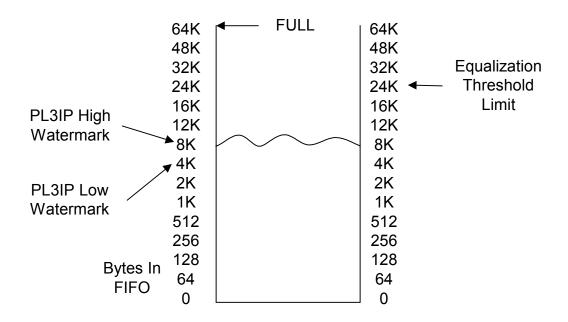

- Programmable watermarks for full/empty FIFO thresholds.

- Automatic generation of PAUSE frames based on FIFO fill levels.

- Upper layer device can flow control Ethernet ports using side-band or host signaling to cause generation of a PAUSE frame.

- Provides side-band Paused state indication to upstream devices.

- Loss-less flow control on all valid frames up to 9.6k bytes.

#### 2.5 Statistics

- 40 bit counters are used to ensure rollover compliance with IEEE 802.3–1998.

- Minimum 58 minutes before rollover.

- Provides port statistic counters needed to support the standard 802.3-1998, SNMP, and RMON Management Information Base (MIB) implementations.

ISSUE 7

**DUAL GIGABIT ETHERNET CONTROLLER**

## 3 APPLICATIONS

- Core Routers

- Edge Routers

- Enterprise Edge Routers

- Multi-Service Switches/Routers

- SONET/SDH Transport Muxes

**DUAL GIGABIT ETHERNET CONTROLLER**

#### 4 REFERENCES

- IEEE 802.3-1998 Carrier Sense Multiple Access with Collision Detection (CSMA/CD) Access Method and Physical Layer Specifications

- PMC-980495 SATURN Compatible Interface For Packet Over SONET Physical Layer And Link Layer Devices (Level 3)

- RFC 1757 Remote Network Monitoring Management Information Base

- RFC 1213 Management Information Base for Network Management of TCP/IPbased internets: MIB-II

- RFC 2233 The Interfaces Group MIB using SMIv2

ISSUE 7

RFC 2665 Definitions of Managed Objects for the Ethernet-like Interface Types

ISSUE 7

**DUAL GIGABIT ETHERNET CONTROLLER**

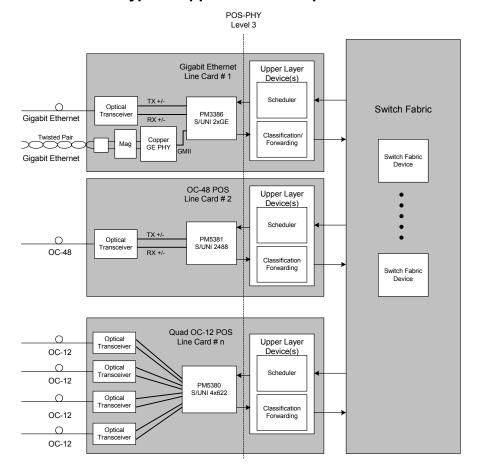

#### 5 APPLICATION EXAMPLES

The PM3386 S/UNI-2xGE is applicable to equipment implementing high density Gigabit Ethernet interfaces. The PM3386 is a dual channel SERDES and GMAC with embedded FIFOs that provides a high density and low power Gigabit Ethernet solution for direct connection to electrical optical modules. Alternatively, a GMII interface is provided for connection to copper Gigabit Ethernet physical layer devices.

On the system side, the POS-PHY Level 3 (32 bit synchronous FIFO style interface clocked up to 104 MHz) allows a common connection to higher layer devices. A common system interface simplifies multi-service equipment utilizing some or all of the following physical layer options:

- OC-48 POS/ATM

- 4xOC-12 POS/ATM

- 16xOC-3 POS/ATM

- Channelized POS/ATM

- High density DS3

- Gigabit Ethernet

The PM3386 is particularly suited for the following applications:

- Core Routers

- Edge Routers

- Enterprise Edge Routers

- Multi-Service Switches/Routers

- SONET/SDH Transport Muxes

These applications require various interfaces (Gigabit Ethernet, ATM, POS, DS3) which use the POS-PHY Level 3 interface. Service cards for various physical layer options can re-use upper layer devices and board design to improve time-to market. The use of Gigabit Ethernet within Internet points of presence (POPs), Super POPs and Transport POPs is increasing due to the requirement of inexpensive high-speed Layer 2 interconnect. Thus, connections between

PM3386

ISSUE 7

**DUAL GIGABIT ETHERNET CONTROLLER**

Edge Routers and Core Routers within a POP are provided via Gigabit Ethernet. Co-located server clusters are also connected via Gigabit Ethernet to POP routers. Similarly, Gigabit Ethernet is becoming the choice for connection between Enterprise Routers and Multi-Service switches. Transport equipment is looking to provide Ethernet directly over SONET/SDH for wide area transparent bridging.

In a typical application the S/UNI-2xGE performs data recovery on the Gigabit Ethernet stream, MAC level frame checks and sends the frame to an upper layer device (such as an IP processor) for forwarding via the POS-PHY level 3 interface. The S/UNI-2xGE maintains extensive statistics for SNMP and RMON applications. On egress, frames are formatted into physical frames with the proper inter-frame gap, preamble and start of frame delimiter. The physical packet is then serialized for transmission over an external electrical optical module. The initial configuration and ongoing control and monitoring of the S/UNI-2xGE are provided via a generic microprocessor interface. The following diagram shows a typical multi-service card application for the PM3386 S/UNI-2xGE with similar cards for OC48 and Quad OC-12 ports.

ISSUE 7

Figure 1 PM3386 Typical Application Example

**DUAL GIGABIT ETHERNET CONTROLLER**

#### 6 BLOCK DIAGRAM

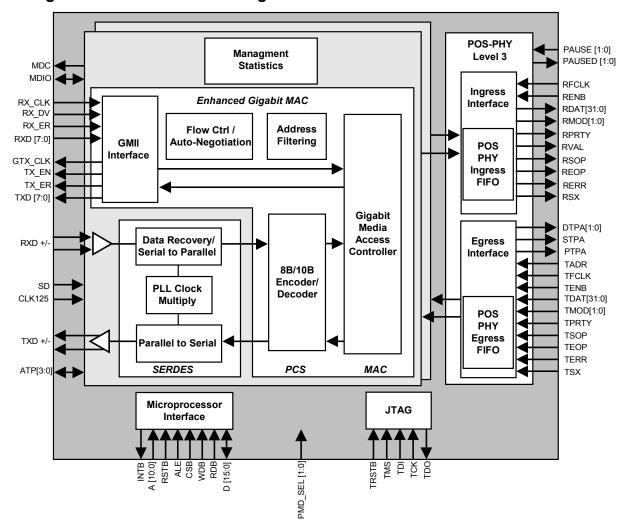

Figure 2 - PM3386 Dual Gigabit Ethernet to POS-PHY Level 3

ISSUE 7

ISSUE 7

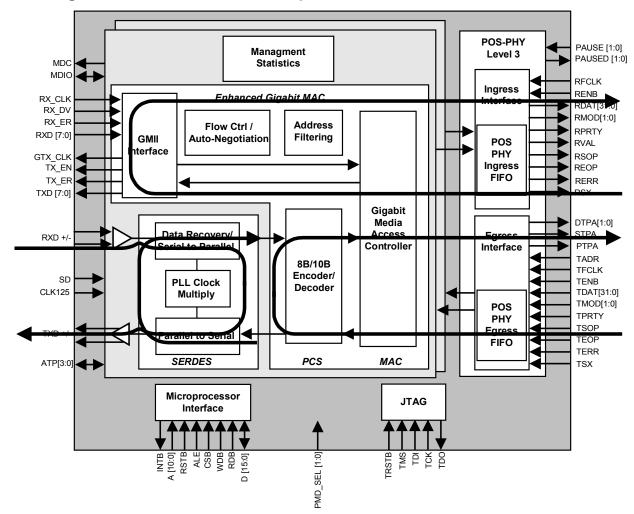

Figure 3 PM3386 Device Loop Back Paths

**ISSUE 7**

**DUAL GIGABIT ETHERNET CONTROLLER**

#### 7 DESCRIPTION

The PM3386 is a monolithic integrated circuit that implements a two port full duplex 1000 Mbit/s Gigabit Ethernet MAC data transport device. The PM3386 provides line interface connectivity provided by an on-chip SERDES and GMII functions and data transport to the up stream device via the industry standard POS-PHY Level 3 interface.

#### Serializer-Deserializer (SERDES)

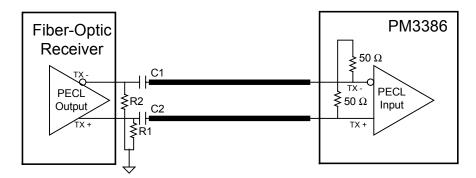

The PM3386 has two internal serializer-deserializer transceivers. The SERDES are IEEE 802.3-1998 Gigabit Ethernet compatible supporting gigabit data transfer flows. The SERDES is based on the X3T11 10 Bit specification. The PM3386 receives and transmits Gigabit Ethernet streams using a bit serial interface for direct connection to optical transceiver devices. The SERDES performs data recovery and serial to parallel conversion for connection to the Enhanced Gigabit Media Access Control block.

#### Gigabit Media Independent Interface (GMII)

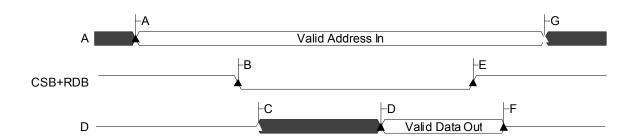

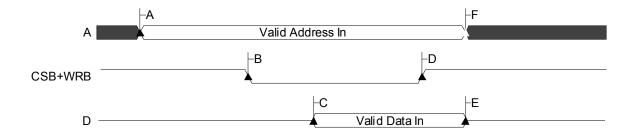

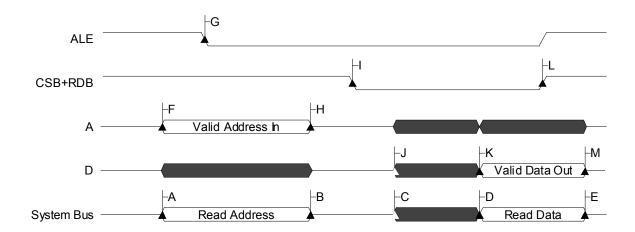

For Gigabit Ethernet over copper support, the PM3386 provides dual standard GMII interfaces. A copper Gigabit Ethernet physical layer device can be connected to the PM3386 via this interface.

#### **Enhanced Gigabit Media Access Control (EGMAC)**

The Enhanced Gigabit Media Access Control (EGMAC) block provides an integrated IEEE 802.3-1998 Gigabit Ethernet Media Access Control (MAC) supporting high performance 1000Base capability. The EGMAC has line side interfaces for connection to internal (SERDES) and external Gigabit PHY via GMII on each Gigabit Ethernet port. The Enhanced Gigabit MAC (EGMAC) incorporates all of the Gigabit Ethernet MAC functions including Auto-Negotiation, statistics, and the MAC Control Sub-layer that adheres to IEEE 802.3-1998 providing support for PAUSE control frames. The EGMAC provides basic frame integrity checks to validate incoming frames. The EGMAC also provides simple line rate ingress address filtering support via 8 exact-match MAC address and VID unicast filters, one 64-bin hash-based multicast filter, and the ability to filter or accept matched frames on a per instance programmable fashion. All inquires for filtering are done at line rate with no system latency introduced for look up cycles.

DUAL GIGABIT ETHERNET CONTROLLER

PM3386

ISSUE 7

#### Management Statistics (MSTAT)

The PM3386 also incorporates a rich set of per port RMON, SNMP, and Etherlike Management Information Base counters. Deep statistical counters are used for management counts providing a minimum rollover time of greater than 58 minutes. All counts are easily managed via the Management Statistics (MSTAT) block.

#### POS-PHY Level 3 Interface (PL3)

The PM3386 can connect to a single upper layer device through a POS-PHY Level 3 Interface. The POS-PHY Level 3 interface is a 32-bit wide interface with a clock rate from 60 to 104 MHz. POS-PHY Level 3 was developed with the cooperation of the SATURN Development Group to cover all application bit rates up to and including 3.2 Gbit/s. This interface provides standards support for interoperation between the PM3386, a multiple PHY layer device, connecting to one Link Layer device. The interface stresses simplicity of operation to allow forward migration to more elaborate PHY and Link Layer devices. The POS-PHY interface contains 64KB receive and 16KB transmit FIFOs per channel. These FIFOs contain programmable thresholds specifying full and empty conditions.

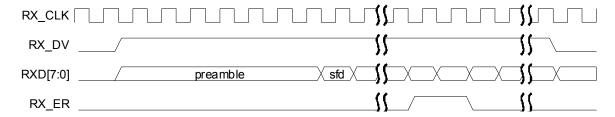

#### **Receive Direction**

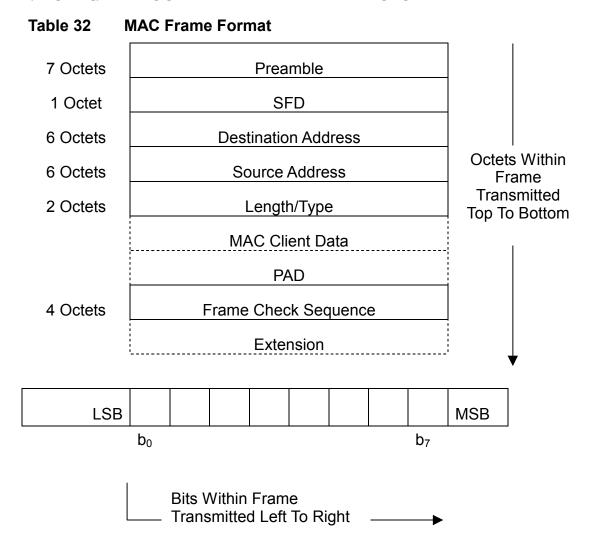

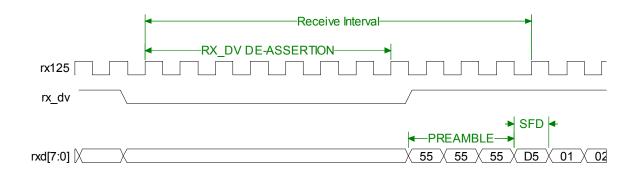

In the receive direction, the PM3386 can be configured to use the internal SERDES or the GMII interface on a per channel basis. For SERDES operation, a Gigabit Ethernet bit stream is received from an external optical transceiver. The data is recovered and converted from serial to parallel data for connection to the EGMAC block. The EGMAC terminates the 8B/10B line codes and performs frame integrity checks (frame length, FCS etc). For GMII operation, the physical packet is sourced from an external copper physical layer device to the PM3386 via the GMII interface (8 bits clocked at 125 MHz). The EGMAC accepts the 8 bit data and performs frame integrity checks once the complete frame is received. The EGMAC can optionally filter erred frames.

Statistics are updated and the frame is sent to the POS-PHY Level 3 interface. The FIFO's in the POS-PHY interface accommodate system latencies and allows for loss-less flow control up to 9.6k bytes. The received frames are then read through the POS-PHY Level 3 (32 bits clocked from 60-104 MHz) system side interface.

#### **Transmit Direction**

In the transmit direction, packets to be transmitted are written into the POS-PHY TX FIFO through the POS-PHY Level 3 interface (32 bits clocked from 60-104

PM3386

ISSUE 7

**DUAL GIGABIT ETHERNET CONTROLLER**

MHz) from the upper layer device. The channel is selected by the upper layer device and is indicated in-band on the POS-PHY interface. The EGMAC builds a properly formatted Ethernet physical packet (padding to minimum size and inserting the preamble, start of frame delimiter (SFD) and the inter-packet gap (IPG)). Statistics are updated and the physical packet is sent to the SERDES or the GMII interface.

For SERDES operation, the EGMAC encodes the physical packet using 8B/10B encoding and passes the physical packet to the SERDES block. The SERDES performs parallel to serial conversion using an internally synthesized 1250 MHz clock. The bit stream is sent to an external optical transceiver for transmission over fiber cable. For GMII operation, the EGMAC sends the physical packet byte by byte across the GMII interface (8 bits clocked at 125 MHz) to an external copper Gigabit Ethernet physical layer device. The copper Gigabit Ethernet physical layer device then transmits the physical packet over copper cable.

#### Flow Control

Flow control is handled in the EGMAC block. When a PAUSE control frame is received, the PM3386 will optionally terminate transmission (after the current frame is sent) and assert the appropriate channel side band flow control output to indicate the paused condition. The received PAUSE control frame can be optionally filtered or passed to the link layer device via the POS-PHY Level 3 interface.

PAUSE control frames are transmitted either under link layer control using channel side band flow control inputs, under link layer control transparent to the PM3386, host based PAUSE frame control or under internal control based on receive FIFO levels. All four methods can provide for loss-less flow control.

#### General

The PM3386 is configured, controlled and monitored via a generic 16-bit microprocessor bus interface. The PM3386 also provides a standard 5 signal IEEE 1149.1 JTAG test port for boundary scan board test purposes.

The PM3386 is implemented in low power, +1.8 Volt, CMOS technology with 5V TTL compatible digital inputs and 3.3V TTL/CMOS compatible digital outputs. The PM3386 is packaged in a 352-pin UBGA package.

**DUAL GIGABIT ETHERNET CONTROLLER**

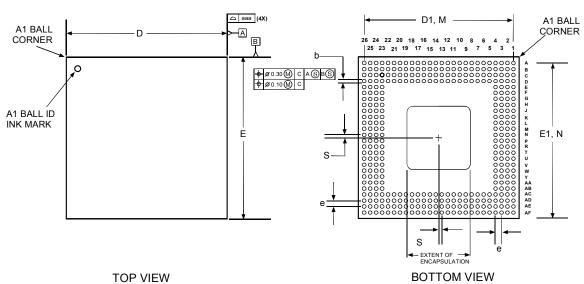

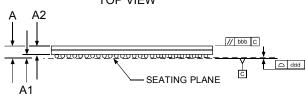

#### 8 PIN DIAGRAM

The PM3386 is packaged in a 352-pin Ultra Ball Grid Array (UBGA) having a body size of 27mm by 27mm.

Table 1 PM3386 Pin Diagram

ISSUE 7

| 26                | 25           | 24           | 23          | 22           | 21          | 20          | 19           | 18            | 17           | 16           | 15            | 14        | 13   | 12   | 11                  | 10        | 9         | 8         | 7           | 6           | 5         | 4            | 3            | 2            | 1            |    |

|-------------------|--------------|--------------|-------------|--------------|-------------|-------------|--------------|---------------|--------------|--------------|---------------|-----------|------|------|---------------------|-----------|-----------|-----------|-------------|-------------|-----------|--------------|--------------|--------------|--------------|----|

| VSS               | VSS          | NC           | RXD1<br>[2] | RXD1<br>[6]  | RX_E<br>R1  | TX_E<br>N1  | TXD1<br>[5]  | TXD1<br>[2]   | VSSQ         | ALE          | CSB           | VSS       | VSS  | A[6] | A[3]                | A[1]      | D[13<br>] | D[10<br>] | D[7]        | D[4]        | D[1]      | TDI          | NC           | VSS          | VSS          | A  |

| VSS               | VDDO         | VSS          | NC          | RXD1<br>[3]  | RXD1<br>[7] | RX_C<br>LK1 | TX_E<br>R1   | TXD1<br>[4]   | TXD1<br>[1]  | INTB         | RDB           | A[9]      | A[8] | A[5] | A[2]                | D[15<br>] | D[11<br>] | D[8]      | D[5]        | D[2]        | TMS       | NC           | VSS          | VDDO         | VSS          | В  |

| VSS               | VSS          | VDDO         | NC          | RXD1<br>[0]  | RXD1<br>[4] | RX_D<br>V1  | GTX_<br>CLK1 | TXD1<br>[7]   | TXD1<br>[3]  | TXD1<br>[0]  | WRB           | A[10<br>] | A[7] | A[4] | A[0]                | D[12<br>] | D[9]      | D[6]      | D[3]        | TCK         | TRST<br>B | NC           | VDDO         | VSS          | NC           | C  |

| VSS               | VSS          | VDDO         | VDDO        | NC           | RXD1<br>[1] | RXD1<br>[5] | VDDI         | VDDO          | TXD1<br>[6]  | VDDI         | VDDQ          | NC        | VDDO | VDDI | D[14<br>]           | VDDI      | NC        | VDDO      | D[0]        | TDO         | NC        | VDDO         | NC           | NC           | NC           | D  |

| VSS               | NC           | VDDO         | NC          |              |             |             |              |               |              |              |               |           |      |      |                     |           |           |           |             |             |           | NC           | NC           | NC           | NC           | E  |

| <mark>VSSQ</mark> | PMD_<br>SEL1 | VDDI         | VDDI        |              |             |             |              |               |              |              |               |           |      |      |                     |           |           |           |             |             |           | NC           | NC           | NC           | RDAT<br>[0]  | F  |

| VSS               | CLK1<br>25   | VDDQ         | AVDL        |              |             |             |              |               |              |              |               |           |      |      |                     |           |           |           |             |             |           | NC           | RSTB         | RDAT<br>[1]  | VDDI         | G  |

| AVDH              | AVDQ         | AVDL         | AVDL        |              |             |             |              |               |              |              |               |           |      |      |                     |           |           |           |             |             |           | VDDO         | RDAT<br>[2]  | RDAT<br>[3]  | RDAT<br>[6]  | H  |

| VSS               | RXSD<br>1    | AVDH         | VDDO        |              |             |             |              |               |              |              |               |           |      |      |                     |           |           |           |             |             |           | NC           | RDAT<br>[4]  | RDAT<br>[7]  | VSSQ         | J  |

| RXD1<br>+         | RXD1         | AVDL         | AVDL        |              |             |             |              |               |              | _            | _             |           | _    |      |                     |           |           |           |             |             |           | RDAT<br>[5]  | RDAT<br>[8]  | RDAT<br>[9]  | RDAT<br>[11] | K  |

| VSS               | ZA.          | L A          | NC          |              | 1 /         | 1           |              |               |              | /            | $\setminus$ / | '/L       |      |      |                     |           |           |           |             |             |           | VDDQ         | RDAT         | RDAT<br>[12] | RDAT<br>[13] | L  |

| TXD1<br>-         | TX           |              | <b>7</b>    | ]/           | ][          | ]/          | $\bigcap$    | $\bigcup_{i}$ | $ \wedge $   | 1            | ۱ ۱           | $/\Gamma$ | 1//  | 7/[  | $\setminus \Gamma$  | ١П        |           |           |             |             |           | VDDI         | RDAT<br>[14] | RDAT<br>[15] | RDAT<br>[16] | M  |

| AVDL              | 7A           | A)           |             |              |             |             |              |               | ()           |              | \ \           | $/ \perp$ |      | /    | ۸ ۷ ،               | ٧/        |           |           |             |             |           | VDDO         | RDAT         | RDAT<br>[18] | VSS          | N  |

| AVDL              | AV.          | ار           |             | $/ \langle$  | 7           | 7           |              |               |              |              |               | / L       | ]/   | 7    | $\bigcup \setminus$ | $\bigcup$ |           |           |             |             |           |              | RDAT<br>[20] | RDAT<br>[19] | VSS          | P  |

| RXD0<br>-         | RXD0<br>+    | RXSD<br>0    | AVDH        |              | _ `         | _ `         |              |               |              |              |               | _         | - `  |      |                     | _         |           |           |             |             |           | VDDI         | RDAT<br>[24] | RDAT<br>[23] | RDAT<br>[22] | R  |

| vss               | AVDL         | AVDL         | VDDO        |              |             |             |              |               |              |              |               |           |      |      |                     |           |           |           |             |             |           | RDAT<br>[30] | RDAT<br>[28] | RDAT<br>[26] | RDAT<br>[25] | Т  |

| TXD0<br>+         | TXD0<br>-    | AVDH         | NC          |              |             |             |              |               |              |              |               |           |      |      |                     |           |           |           |             |             |           | RSX          | RPRT<br>Y    | RDAT<br>[29] | RDAT<br>[27] | U  |

| VSS               | NC           | PMD_<br>SEL0 | VDDI        |              |             |             |              |               |              |              |               |           |      |      |                     |           |           |           |             |             |           | VDDO         | RERR         | REOP         | RDAT<br>[31] | V  |

| TXD0<br>[3]       | TXD0<br>[2]  | TXD0         | TXD0        |              |             |             |              |               |              |              |               |           |      |      |                     |           |           |           |             |             |           | VDDI         | RVAL         | RMOD<br>[1]  | RFCL<br>K    | W  |

| VSS               | TXD0<br>[5]  | TXD0<br>[4]  | VDDO        |              |             |             |              |               |              |              |               |           |      |      |                     |           |           |           |             |             |           | PAUS<br>E1   | PAUS<br>ED0  | RSOP         | RMOD<br>[0]  | Y  |

| NC                | TXD0         | TXD0         | VDDI        |              |             |             |              |               |              |              |               |           |      |      |                     |           |           |           |             |             |           | NC           | VDDQ         | PAUS<br>ED1  | RENB         | AA |

| VSS               | NC           | VDDO         | NC          |              |             |             |              |               |              |              |               |           |      |      |                     |           |           |           |             |             |           | NC           | NC           | VSSQ         | PAUS<br>E0   | AB |

| VSS               | VSS          | VDDO         | VDDO        | VDDI         | RX_C<br>LK0 | VDDI        | VDDO         | NC            | TDAT         | VDDI         | VDDQ          | VDDO      | NC   | TDAT | VDDI                | TDAT      | VDDO      | VDDI      | TMOD<br>[1] | VDDI        | NC        | VDDO         | NC           | NC           |              | AC |

| VSS               | VSS          | VDDO         | NC          | GTX_<br>CLK0 |             | RXD0<br>[4] | RXD0         | MDC           |              | TDAT         | TDAT          | TDAT      | TDAT | TDAT | TDAT<br>[8]         |           | TDAT      | TENB      | TEOP        | TMOD<br>[0] | STPA      | NC           | VDDO         | VSS          | NC           | AD |

| VSS               | VDDO         | VSS          | TX_E<br>N0  | RX_D<br>V0   | RXD0<br>[5] | _           | MDIO         | TDAT          | TDAT<br>[26] | TDAT         | TDAT<br>[20]  | TDAT      | TDAT | TDAT | TDAT                |           | TDAT      | TDAT      | TSX         | TPRT<br>Y   | TADR      | DTPA<br>[1]  | VSS          | VDDO         | VSS          | ΑE |

| VSS               | VSS          | TX_E<br>R0   | RX_E        | RXD0         | RXD0        |             | TDAT         | TDAT          | TDAT<br>[24] | TDAT<br>[22] | VSSQ          |           | VSS  | TDAT | TDAT                | TDAT      | TDAT      | TDAT      | TFCL<br>K   |             | TERR      |              | DTPA<br>[0]  | VSS          | VSS          | AF |

**DUAL GIGABIT ETHERNET CONTROLLER**

## 9 PIN DESCRIPTION

## Table 2 - Serial Line Side Interface Signals

ISSUE 7

| Pin Name | Туре          | Pin No. | Function                                                                                                                                                                                                       |  |  |  |  |  |  |

|----------|---------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| CLK125   | Schmitt       | G25     | PHY Reference Clock (Port 0)                                                                                                                                                                                   |  |  |  |  |  |  |

|          | Input         |         | 125 MHz reference clock used to generate GTX_CLK0 or GTX_CLK1 during GMII mode. The Clock Synthesis Unit uses this clock as it's input reference during SERDES mode.                                           |  |  |  |  |  |  |

|          |               |         | Please refer to the Operations section for a discussion of clock mode selection interfacing issues.                                                                                                            |  |  |  |  |  |  |

| RXD0+    | Differential  | R25     | Receive Differential Data (Port 0)                                                                                                                                                                             |  |  |  |  |  |  |

| RXD0-    | PECL<br>Input | R26     | These PECL inputs (RXD0+/-) contain the 8B/10B bit serial receive stream. The receive data is recovered from the RXD0+/- bit stream.                                                                           |  |  |  |  |  |  |

| RXSD0    | Input         | R24     | Receive Signal Detect (Port 0)                                                                                                                                                                                 |  |  |  |  |  |  |

|          |               |         | RXSD0 indicates the presence of valid receive signal power from the Optical Physical Medium Dependent Device. A logic level high indicates the presence of valid data. A logic low indicates a loss of signal. |  |  |  |  |  |  |

| RXD1+    | Differential  | K26     | Receive Differential Data (Port 1)                                                                                                                                                                             |  |  |  |  |  |  |

| RXD1-    | PECL<br>Input | K25     | The PECL inputs RXD1+/- contain the 8B/10B bit serial receive stream. The receive data is recovered from the RXD1+/- bit stream.                                                                               |  |  |  |  |  |  |

ISSUE 7

DUAL GIGABIT ETHERNET CONTROLLER

| Pin Name | Туре             | Pin No. | Function                                                                                                                                                                                                       |

|----------|------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RXSD1    | Input            | J25     | Receive Signal Detect (Port 1)                                                                                                                                                                                 |

|          |                  |         | RXSD1 indicates the presence of valid receive signal power from the Optical Physical Medium Dependent Device. A logic level high indicates the presence of valid data. A logic low indicates a loss of signal. |

| TXD0+    | Differential     | U26     | Transmit Differential Data (Port 0)                                                                                                                                                                            |

| TXD0-    | PECL<br>Output   | U25     | The PECL outputs TXD0+/- contain the 1.25 Gbit/s transmit stream. The TXD0+/- outputs are driven using the CSU clock.                                                                                          |

| TXD1+    | Differential     | M25     | Transmit Differential Data (Port 1)                                                                                                                                                                            |

| TXD1-    | PECL<br>Output   | M26     | The PECL outputs TXD1+/- contain the 1.25 Gbit/s transmit stream. The TXD1+/- outputs are driven using the CSU clock.                                                                                          |

| ATP0     | Bi-              | M24     | Receive and Transmit Analog Test Ports                                                                                                                                                                         |

| ATP1     | Directional CMOS | M23     | The ATP[1:0] pins are used for manufacturing testing only and should be tied to analog ground.                                                                                                                 |

## Table 3 -Gigabit Media Independent Interface (GMII)

| Signal Name | Direction | Pin No. | Function                                                                     |

|-------------|-----------|---------|------------------------------------------------------------------------------|

| GTX_CLK0    | Output    | AD22    | GMII Transmit Clock (Port 0)                                                 |

|             |           |         | 125 MHz reference clock supplied by the PM3386.                              |

| TXD0[0]     | Output    | W24     | GMII Transmit Data (Port 0)                                                  |

| TXD0[1]     |           | W23     | Byte-wide transmit data is output on these                                   |

| TXD0[2]     |           | W25     | pins synchronously to the PHY device.                                        |

| TXD0[3]     |           | W26     | The least significant bit, TXD0[0] is the first bit transferred on the line. |

| TXD0[4]     |           | Y24     | This signal is updated on the rising edge of                                 |

| TXD0[5]     |           | Y25     | GTX_CLK0.                                                                    |

| TXD0[6]     |           | AA24    |                                                                              |

| TXD0[7]     |           | AA25    |                                                                              |

ISSUE 7

| Signal Name | Direction | Pin No. | Function                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------|-----------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TX_EN0      | Output    | AE23    | Transmit Enable (Port 0)                                                                                                                                                                                                                                                                                                                                                                 |

|             |           |         | When in GMII mode this signal is an active high signal asserted when valid data is present on the TXD0[7:0] and TX_ER0 pins. This signal is updated on the rising edge of GTX_CLK0.                                                                                                                                                                                                      |

|             |           |         | When in SERDES mode this signal enables operation of the external transmitter. When asserted (default active low) it indicates the potential presence of valid transmit data. When de-asserted indicates the absence of valid transmit data. Note that while in SERDES mode the polarity of this signal is programmable to support interoperability with differing optical transmitters. |

| TX_ER0      | Output    | AF24    | GMII Transmit Coding Error (Port 0)                                                                                                                                                                                                                                                                                                                                                      |

|             |           |         | Active high signal asserted when an error is detected during transmission. Please refer to the Operations section for a full listing of error conditions reported by the PM3386 using the TX_ER0 output.                                                                                                                                                                                 |

|             |           |         | This signal is updated on the rising edge of GTX_CLK0.                                                                                                                                                                                                                                                                                                                                   |

| RX_CLK0     | Schmitt   | AC21    | GMII Receive Clock (Port 0)                                                                                                                                                                                                                                                                                                                                                              |

|             | Input     |         | 125 MHz GMII reference clock received from the PHY device.                                                                                                                                                                                                                                                                                                                               |

| RXD0[0]     | Input     | AF20    | GMII Receive Data (Port 0)                                                                                                                                                                                                                                                                                                                                                               |

| RXD0[1]     |           | AD19    | Byte-wide receive data is input on these                                                                                                                                                                                                                                                                                                                                                 |

| RXD0[2]     |           | AE20    | pins synchronously from the PHY device.                                                                                                                                                                                                                                                                                                                                                  |

| RXD0[3]     |           | AF21    | The least significant bit, RXD0[0] is expected to contain the first bit received on                                                                                                                                                                                                                                                                                                      |

| RXD0[4]     |           | AD20    | the line.                                                                                                                                                                                                                                                                                                                                                                                |

| RXD0[5]     |           | AE21    | This signal is synchronized to RX_CLK0.                                                                                                                                                                                                                                                                                                                                                  |

| RXD0[6]     |           | AF22    |                                                                                                                                                                                                                                                                                                                                                                                          |

| RXD0[7]     |           | AD21    |                                                                                                                                                                                                                                                                                                                                                                                          |

ISSUE 7

| Signal Name | Direction | Pin No. | Function                                                                                      |

|-------------|-----------|---------|-----------------------------------------------------------------------------------------------|

| RX_DV0      | Input     | AE22    | GMII Receive Data Valid (Port 0)                                                              |

|             |           |         | Active high signal asserted when valid data is present on the RXD0[7:0] and RX_ER0 pins.      |

|             |           |         | This signal is synchronized to RX_CLK0.                                                       |

| RX_ER0      | Input     | AF23    | GMII Receive Error (Port 0)                                                                   |

|             |           |         | Active high signal asserted when there has been an error during the received physical packet. |

|             |           |         | This signal is synchronized to RX_CLK0.                                                       |

| GTX_CLK1    | Output    | C19     | GMII Transmit Clock (Port 1)                                                                  |

|             |           |         | 125 MHz reference clock supplied by the PM3386.                                               |

| TXD1[0]     | Output    | C16     | GMII Transmit Data (Port 1)                                                                   |

| TXD1[1]     |           | B17     | Byte-wide transmit data is output on these                                                    |

| TXD1[2]     |           | A18     | pins synchronously to the PHY device.                                                         |

| TXD1[3]     |           | C17     | The least significant bit, TXD1[0] is the first bit transferred on the line.                  |

| TXD1[4]     |           | B18     | This signal is updated on the rising edge of                                                  |

| TXD1[5]     |           | A19     | GTX_CLK1.                                                                                     |

| TXD1[6]     |           | D17     |                                                                                               |

| TXD1[7]     |           | C18     |                                                                                               |

ISSUE 7

| Signal Name | Direction | Pin No. | Function                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------|-----------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TX_EN1      | Output    | A20     | Transmit Enable (Port 1)                                                                                                                                                                                                                                                                                                                                                                 |

|             |           |         | When in GMII mode this signal is an active high signal asserted when valid data is present on the TXD1[7:0] and TX_ER1 pins. This signal is updated on the rising edge of GTX_CLK1.                                                                                                                                                                                                      |

|             |           |         | When in SERDES mode this signal enables operation of the external transmitter. When asserted (default active low) it indicates the potential presence of valid transmit data. When de-asserted indicates the absence of valid transmit data. Note that while in SERDES mode the polarity of this signal is programmable to support interoperability with differing optical transmitters. |

| TX_ER1      | Output    | B19     | GMII Transmit Coding Error (Port 1)                                                                                                                                                                                                                                                                                                                                                      |

|             |           |         | Active high signal asserted when an error is detected during transmission. Please refer to the Operations section for a full listing of error conditions reported by the PM3386 using the TX_ER1 output. This signal is updated on the rising edge of GTX_CLK1.                                                                                                                          |

| RX_CLK1     | Schmitt   | B20     | GMII Receive Clock (Port 1)                                                                                                                                                                                                                                                                                                                                                              |

|             | Input     |         | 125 MHz GMII reference clock received from the PHY device.                                                                                                                                                                                                                                                                                                                               |

| RXD1[0]     | Input     | C22     | GMII Receive Data (Port 1)                                                                                                                                                                                                                                                                                                                                                               |

| RXD1[1]     |           | D21     | Byte-wide receive data is input on these                                                                                                                                                                                                                                                                                                                                                 |

| RXD1[2]     |           | A23     | pins synchronously from the PHY device.                                                                                                                                                                                                                                                                                                                                                  |

| RXD1[3]     |           | B22     | The least significant bit, RXD1[0] is expected to contain the first bit received on                                                                                                                                                                                                                                                                                                      |

| RXD1[4]     |           | C21     | the line.                                                                                                                                                                                                                                                                                                                                                                                |

| RXD1[5]     |           | D20     | This signal is synchronized to RX_CLK1.                                                                                                                                                                                                                                                                                                                                                  |

| RXD1[6]     |           | A22     |                                                                                                                                                                                                                                                                                                                                                                                          |

| RXD1[7]     |           | B21     |                                                                                                                                                                                                                                                                                                                                                                                          |

ISSUE 7

**DUAL GIGABIT ETHERNET CONTROLLER**

| Signal Name | Direction             | Pin No. | Function                                                                                                                                                                                                                                        |

|-------------|-----------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RX_DV1      | Input                 | C20     | GMII Receive Data Valid (Port 1)                                                                                                                                                                                                                |

|             |                       |         | Active high signal asserted when valid data is present on the RXD1[7:0] and RX_ER1 pins.                                                                                                                                                        |

|             |                       |         | This signal is synchronized to RX_CLK1                                                                                                                                                                                                          |

| RX_ER1      | Input                 | A21     | GMII Receive Error (Port 1)                                                                                                                                                                                                                     |

|             |                       |         | Active high signal asserted when there has been an error during the received physical packet.                                                                                                                                                   |

|             |                       |         | This signal is synchronized to RX_CLK1.                                                                                                                                                                                                         |

| MDC         | Output                | AD18    | MII Management Data Clock                                                                                                                                                                                                                       |

|             |                       |         | MDC provides the MII reference clock for communication between the PM3386 and other transceivers.                                                                                                                                               |

| MDIO        | I/O                   | AE19    | MII Management Data                                                                                                                                                                                                                             |

|             | Internal<br>pull-down |         | When configured as an input, the external PHY supplies status during MII Management read cycles. When configured as an output, the PM3386 supplies control during MII Management write/read cycles and data during MII Management write cycles. |

|             |                       |         | Data values on the MDIO pin are updated and sampled on the rising edge of MDC.                                                                                                                                                                  |

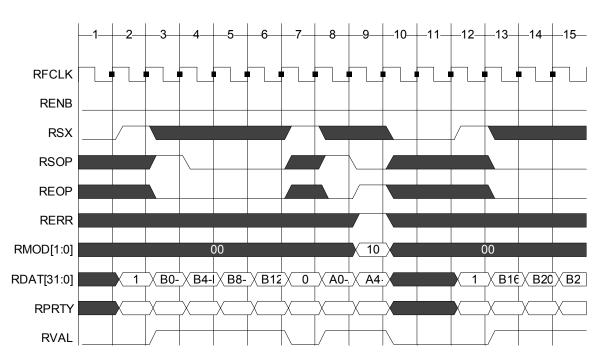

#### Table 4 -POS-PHY Level 3 Transmit Interface

| Signal Name | Direction | Pin No. | Function                                                                                                                                      |

|-------------|-----------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| TFCLK       | Schmitt   | AF7     | POS-PHY Transmit FIFO Write Clock                                                                                                             |

|             | Input     |         | TFCLK is used to synchronize data transfer transactions between the higher layer device and the PM3386. TFCLK cycles at a 60 to 104 MHz rate. |

PMC-Sierra, Inc.

DATASHEET

PMC-1991129

ISSUE 7

| Signal Name          | Direction | Pin No.      | Function                                                                         |

|----------------------|-----------|--------------|----------------------------------------------------------------------------------|

| TDAT[0]              | Input     | AE8          | POS-PHY Transmit Packet Data Bus                                                 |

| TDAT[1]              |           | AD9          | This bus carries the packet octets that are                                      |

| TDAT[2]              |           | AC10         | written to the selected transmit FIFO and                                        |

| TDAT[3]              |           | AF8          | the in-band port address to select the                                           |

| TDAT[4]              |           | AE9          | desired transmit FIFO. The TDAT bus is                                           |

| TDAT[5]              |           | AD10         | considered valid only when TENB is simultaneously asserted.                      |

| TDAT[6]              |           | AF9<br>AE10  |                                                                                  |

| TDAT[7] TDAT[8]      |           | AD11         | When a 32-bit interface is used, data must be transmitted in big endian order on |

| TDAT[0]              |           | AF10         | TDAT[31:0].                                                                      |

| TDAT[10]             |           | AE11         | TDAT[31:0] is sampled on the rising edge                                         |

| TDAT[11]             |           | AC12         | of TFCLK.                                                                        |

| TDAT[12]             |           | AF11         |                                                                                  |

| TDAT[13]             |           | AD12         |                                                                                  |

| TDAT[14]             |           | AE12         |                                                                                  |

| TDAT[15]             |           | AF12         |                                                                                  |

| TDAT[16]             |           | AD13         |                                                                                  |

| TDAT[17]             |           | AE13         |                                                                                  |

| TDAT[18]             |           | AE14         |                                                                                  |

| TDAT[19]             |           | AD14         |                                                                                  |

| TDAT[20]             |           | AE15         |                                                                                  |

| TDAT[21]             |           | AD15         |                                                                                  |

| TDAT[22]             |           | AF16         |                                                                                  |

| TDAT[23]             |           | AE16         |                                                                                  |

| TDAT[24]             |           | AF17         |                                                                                  |

| TDAT[25]             |           | AD16         |                                                                                  |

| TDAT[26]             |           | AE17         |                                                                                  |

| TDAT[27]             |           | AF18         |                                                                                  |

| TDAT[28]             |           | AD17         |                                                                                  |

| TDAT[29]             |           | AE18<br>AF19 |                                                                                  |

| TDAT[30]<br>TDAT[31] |           | AC17         |                                                                                  |

| וטאוןטון             |           | AC17         |                                                                                  |

PMC-Sierra, Inc.

DATASHEET

PMC-1991129

ISSUE 7

| Signal Name | Direction | Pin No. | Function                                                                                                                                                                                                                   |

|-------------|-----------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|