# CY8C25122, CY8C26233, CY8C26443, CY8C26643 Device Data Sheet for Silicon Revision D

8-Bit Programmable System-on-Chip (PSoC™) Microcontrollers

1

The CY8C25122/CY8C26233/CY8C26443/CY8C26643 family of Programmable System-on-Chip (PSoC™) microcontrollers replaces multiple MCU-based system components with one single-chip, programmable device. A PSoC microcontroller includes a fast CPU, Flash program memory, and SRAM data memory with configurable analog and digital peripheral blocks in a range of convenient pin-outs and memory sizes. The driving force behind this innovative Programmable System-on-Chip comes from user configurability of analog and digital arrays: the PSoC blocks.

# Powerful Harvard Architecture Processor with Fast Multiply/Accumulate

- M8C processor instruction set

- Processor speeds to 24 MHz

- Register speed memory transfers

- Flexible addressing modes

- Bit manipulation on I/O and memory

- 8x8 multiply, 32-bit accumulate

## Flexible On-Chip Memory

- Flash program storage, 4K to 16K bytes, depending on device

- 50,000 erase/write cycles

- 256 bytes SRAM data storage

- In-System Serial Programming (ISSP<sup>TM</sup>)

- Partial Flash updates

- Flexible protection modes

- EEPROM emulation in Flash, up to 2,304 bytes

#### Programmable System-on-Chip (PSoC<sup>™</sup>) Blocks

- On-chip, user configurable analog and digital peripheral blocks

- PSoC blocks can be used individually or in combination

- 12 Analog PSoC blocks provide:

- ■Up to 11 bit Delta-Sigma ADC

- ■Up to 8 bit Successive Approximation ADC

- ■Up to 12 bit Incremental ADC

- ■Up to 10 bit DAC

- ■Programmable gain amplifier

- ■Programmable filters

- ■Differential comparators

- 8 Digital PSoC blocks provide:

- •Multipurpose timers: event timing, real-time clock, pulse width modulation (PWM) and PWM with deadband

- ■CRC modules

- ■Full-duplex UARTs

- ■SPI<sup>™</sup> master or slave configuration

- ■Flexible clocking sources for analog PSoC blocks

#### **Programmable Pin Configurations**

- Schmitt trigger TTL I/O pins

- Logic output drive to 25 mA with internal pull-up or pull-down resistors, High Z, or strong driver

- Interrupt on pin change

- Analog output drive to 40 mA

#### Precision, Programmable Clocking

- Internal 24/48 MHz Oscillator (+/- 2.5%, no external components)

- External 32.768 kHz Crystal Oscillator (optional precision source for PLL)

- Internal Low Speed Oscillator for Watchdog and Sleep

#### **Dedicated Peripherals**

- Watchdog and Sleep Timers

- Low Voltage Detection with user-configurable threshold voltages

- On-chip voltage reference

# Fully Static CMOS Devices using advanced Flash technology

- Low power at high speed

- Operating voltage from 3.0 to 5.25 V

- Operating voltage down to 1.0 V using on-chip switch mode voltage pump

- Wide temperature range: -40 °C to + 85 °C

#### **Complete Development Tools**

- Powerful integrated development environment (PSoC<sup>™</sup> Designer)

- Low-cost, in-circuit emulator and programmer

Cypress MicroSystems, Inc. 22027 17th Avenue SE Suite 201

Bothell, WA 98021 Phone: 877.751.6100

Fax: 425.939.0999

### http://www.cypressmicro.com/ http://www.cypress.com/aboutus/sales\_locations.cfm support@cypressmicro.com

© Cypress MicroSystems, Inc. 2000-2002. All rights reserved. PSoC TM (Programmable System-on-Chip) is a trademark of Cypress MicroSystems, Inc. All other trademarks or registered trademarks referenced herein are property of the respective corporations. The information contained herein is subject to change without notice. Cypress MicroSystems assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress MicroSystems product. Nor does it convey or imply any license under patent or other rights. Cypress MicroSystems does not authorize its products for use as critical components in life support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress MicroSystems' products in life-support system applications implies that the manufacturer assumes all risk of such use and in doing so, indemnifies Cypress MicroSystems against all charges.

## **Table of Contents**

| 1.0 Functional Overview                        | 14 |

|------------------------------------------------|----|

| 1.1 Key Features                               | 14 |

| 1.2 Pin-out Descriptions                       | 15 |

| 2.0 CPU Architecture                           | 19 |

| 2.1 Introduction                               | 19 |

| 2.2 CPU Registers                              | 20 |

| 2.3 Addressing Modes                           | 21 |

| 2.4 Instruction Set Summary                    | 25 |

| 3.0 Memory Organization                        | 26 |

| 3.1 Flash Program Memory Organization          | 26 |

| 3.2 RAM Data Memory Organization               | 26 |

| 4.0 Register Organization                      | 26 |

| 4.1 Introduction                               | 26 |

| 4.2 Register Bank 0 Map                        | 27 |

| 4.3 Register Bank 1 Map                        | 28 |

| 5.0 I/O Ports                                  | 29 |

| 5.1 Introduction                               | 29 |

| 6.0 I/O Registers                              | 31 |

| 6.1 Port Data Registers                        | 31 |

| 6.2 Port Interrupt Enable Registers            | 31 |

| 6.3 Port Global Select Registers               | 32 |

| 7.0 Clocking                                   | 35 |

| 7.1 Oscillator Options                         | 35 |

| 7.2 System Clocking Signals                    | 38 |

| 8.0 Interrupts                                 | 42 |

| 8.1 Overview                                   | 42 |

| 8.2 Interrupt Control Architecture             | 44 |

| 8.3 Interrupt Vectors                          | 44 |

| 8.4 Interrupt Masks                            | 45 |

| 8.5 Interrupt Vector Register                  |    |

| 8.6 GPIO Interrupt                             |    |

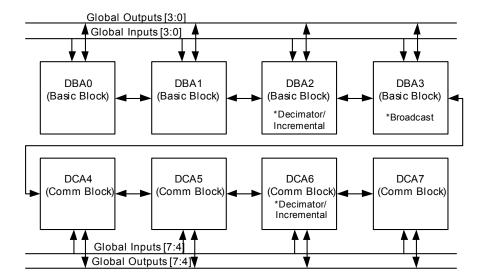

| 9.0 Digital PSoC Blocks                        | 48 |

| 9.1 Introduction                               |    |

| 9.2 Digital PSoC Block Bank 1 Registers        |    |

| 9.3 Digital PSoC Block Bank 0 Registers        |    |

| 9.4 Global Inputs and Outputs                  |    |

| 9.5 Available Programmed Digital Functionality |    |

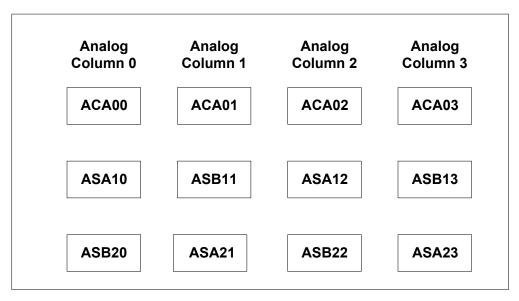

| 10.0 Analog PSoC Blocks                        |    |

| 10.1 Introduction                              |    |

| 10.2 Analog System Clocking Signals            |    |

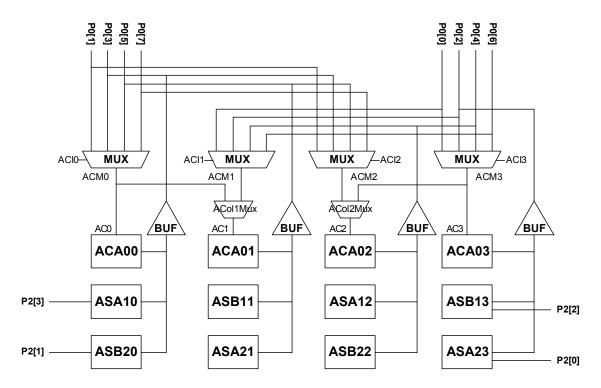

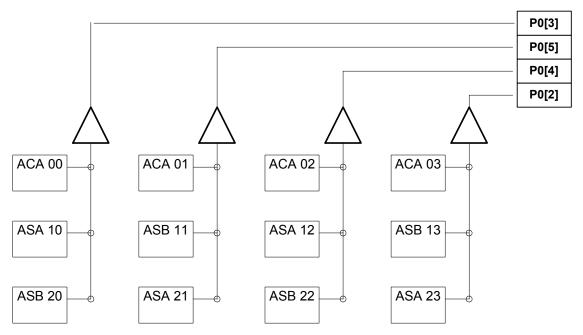

| 10.3 Array of Analog PSoC Blocks               | 72 |

| 10.4 Analog Reference and Bias Control         |    |

| 10.5 AGND, REFHI, REFLO                        |    |

| 10.6 Analog PSoC Block Clocking Options        |    |

| 10.7 Analog Clock Select Register              | 75 |

| 10.8 Analog Continuous Time PSoC Blocks                | 78  |

|--------------------------------------------------------|-----|

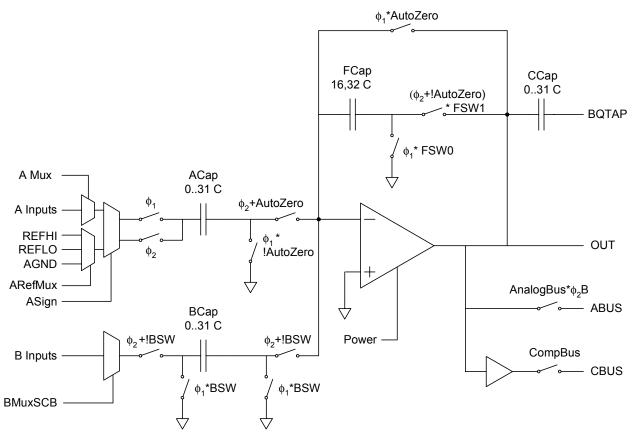

| 10.9 Analog Switch Cap Type A PSoC Blocks              | 83  |

| 10.10 Analog Switch Cap Type B PSoC Blocks             | 92  |

| 10.11 Analog Comparator Bus                            | 99  |

| 10.12 Analog Synchronization                           | 99  |

| 10.13 Analog I/O                                       |     |

| 10.14 Analog Modulator                                 | 104 |

| 10.15 Analog PSoC Block Functionality                  | 105 |

| 10.16 Temperature Sensing Capability                   | 106 |

| 11.0 Special Features of the CPU                       | 107 |

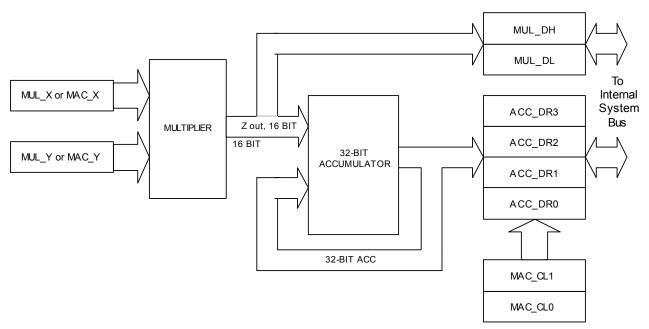

| 11.1 Multiplier/Accumulator                            | 107 |

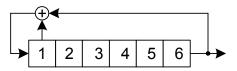

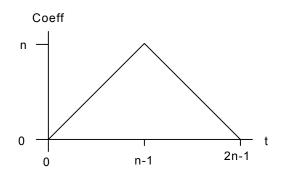

| 11.2 Decimator                                         | 110 |

| 11.3 Reset                                             | 112 |

| 11.4 Sleep States                                      | 114 |

| 11.5 Supply Voltage Monitor                            | 116 |

| 11.6 Switch Mode Pump                                  |     |

| 11.7 Internal Voltage Reference                        | 118 |

| 11.8 Supervisor ROM/System Supervisor Call Instruction | 118 |

| 11.9 Flash Program Memory Protection                   | 120 |

| 11.10 Programming Requirements and Step Descriptions   | 120 |

| 11.11 Programming Wave Forms                           | 122 |

| 11.12 Programming File Format                          | 122 |

| 12.0 Development Tools                                 | 123 |

| 12.1 Overview                                          |     |

| 12.2 Integrated Development Environment Subsystems     |     |

| 12.3 Hardware Tools                                    |     |

| 13.0 DC and AC Characteristics                         |     |

| 13.1 Absolute Maximum Ratings                          |     |

| 13.2 DC Characteristics                                |     |

| 13.3 AC Characteristics                                | 136 |

| 14.0 Packaging Information                             |     |

| 14.1 Thermal Impedances per Package                    |     |

| 15.0 Ordering Guide                                    |     |

| 16.0 Document Revision History                         | 148 |

## List of Tables

| Table 1: Device Family Key Features                    | 14 |

|--------------------------------------------------------|----|

| Table 2: Pin-out 8 Pin                                 | 15 |

| Table 3: Pin-out 20 Pin                                |    |

| Table 4: Pin-out 28 Pin                                |    |

| Table 5: Pin-out 44 Pin                                |    |

| Table 6: Pin-out 48 Pin                                |    |

| Table 7: CPU Registers and Mnemonics                   | 19 |

| Table 8: Flags Register                                |    |

| Table 9: Accumulator Register (CPU_A)                  | 20 |

| Table 10: Index Register (CPU_X)                       | 21 |

| Table 11: Stack Pointer Register (CPU_SP)              | 21 |

| Table 12: Program Counter Register (CPU_PC)            |    |

| Table 13: Source Immediate                             |    |

| Table 14: Source Direct                                |    |

| Table 15: Source Indexed                               |    |

| Table 16: Destination Direct                           |    |

| Table 17: Destination Indexed                          |    |

| Table 18: Destination Direct Immediate                 |    |

| Table 19: Destination Indexed Immediate                |    |

| Table 20: Destination Direct Direct                    |    |

| Table 21: Source Indirect Post Increment               |    |

| Table 22: Destination Indirect Post Increment          |    |

| Table 23: Instruction Set Summary (Sorted by Mnemonic) |    |

| Table 24: Flash Program Memory Map                     |    |

| Table 25: RAM Data Memory Map                          |    |

| Table 26: Bank 0                                       |    |

| Table 27: Bank 1                                       |    |

| Table 28: Port Data Registers                          |    |

| Table 29: Port Interrupt Enable Registers              |    |

| Table 30: Port Global Select Registers                 |    |

| Table 31: Port Drive Mode 0 Registers                  |    |

| Table 32: Port Drive Mode 1 Registers                  |    |

| Table 33: Port Interrupt Control 0 Registers           |    |

| Table 34: Port Interrupt Control 1 Registers           |    |

| Table 35: Internal Main Oscillator Trim Register       |    |

| Table 36: Internal Low Speed Oscillator Trim Register  |    |

| Table 37: External Crystal Oscillator Trim Register    |    |

| Table 38: Typical Package Capacitances                 |    |

| Table 39: System Clocking Signals and Definitions      |    |

| Table 40: Oscillator Control 0 Register                |    |

| Table 41: Oscillator Control 1 Register                |    |

| Table 42: 24V1/24V2 Frequency Selection                |    |

| Table 43: Interrupt Vector Table                       |    |

| Table 44: General Interrupt Mask Register              |    |

| Table 45: Digital PSoC Block Interrupt Mask Register   | 46 |

| Table 46: Interrupt Vector Register                                                 | 46  |

|-------------------------------------------------------------------------------------|-----|

| Table 47: Digital Basic Type A/ Communications Type A Block xx Function Register    |     |

| Table 48: Digital Basic Type A / Communications Type A Block xx Input Register      |     |

| Table 49: Digital Function Data Input Definitions                                   |     |

| Table 50: Digital Basic Type A / Communications Type A Block xx Output Register     | 53  |

| Table 51: Digital Function Outputs                                                  |     |

| Table 52: Digital Basic Type A / Communications Type A Block xx Data Register 0,1,2 | 54  |

| Table 53: R/W Variations per User Module Selection                                  |     |

| Table 54: Digital Basic Type A / Communications Type A Block xx Control Register 0  | 55  |

| Table 55: Digital Basic Type A/Communications Type A Block xx Control Register 0    |     |

| Table 56: Digital Communications Type A Block xx Control Register 0                 | 57  |

| Table 57: Digital Communications Type A Block xx Control Register 0                 | 58  |

| Table 58: Digital Communications Type A Block xx Control Register 0                 |     |

| Table 59: Global Input Assignments                                                  | 60  |

| Table 60: Global Output Assignments                                                 |     |

| Table 61: Analog System Clocking Signals                                            |     |

| Table 62: Analog Reference Control Register                                         |     |

| Table 63: Analog Column Clock Select Register                                       | 74  |

| Table 64: Analog Clock Select Register                                              |     |

| Table 65: Analog Continuous Time Block xx Control 0 Register                        |     |

| Table 66: Analog Continuous Time Block xx Control 1 Register                        |     |

| Table 67: Analog Continuous Time Type A Block xx Control 2 Register                 |     |

| Table 68: Analog Switch Cap Type A Block xx Control 0 Register                      |     |

| Table 69: Analog Switch Cap Type A Block xx Control 1 Register                      |     |

| Table 70: Analog Switch Cap Type A Block xx Control 2 Register                      |     |

| Table 71: Analog Switch Cap Type A Block xx Control 3 Register                      |     |

| Table 72: Analog Switch Cap Type B Block xx Control 0 Register                      |     |

| Table 73: Analog Switch Cap Type B Block xx Control 1 Register                      |     |

| Table 74: Analog Switch Cap Type B Block xx Control 2 Register                      |     |

| Table 75: Analog Switch Cap Type B Block xx Control 3 Register                      |     |

| Table 76: Analog Comparator Control Register                                        |     |

| Table 77: Analog Frequency Relationships                                            |     |

| Table 78: Analog Synchronization Control Register                                   |     |

| Table 79: Analog Input Select Register                                              |     |

| Table 80: Analog Output Buffer Control Register                                     |     |

| Table 81: Analog Modulator Control Register                                         |     |

| Table 82: Multiply Input X Register                                                 |     |

| Table 83: Multiply Input Y Register                                                 |     |

| Table 84: Multiply Result High Register                                             |     |

| Table 85: Multiply Result Low Register                                              |     |

| Table 86: Accumulator Result 1 / Multiply/Accumulator Input X Register              |     |

| Table 87: Accumulator Result 0 / Multiply/Accumulator Input Y Register              |     |

| Table 88: Accumulator Result 3 / Multiply/Accumulator Clear 0 Register              |     |

| Table 89: Accumulator Result 2 / Multiply/Accumulator Clear 1 Register              |     |

| Table 90: Decimator/Incremental Control Register                                    |     |

| Table 91: Decimator Data High Register                                              |     |

| Table 92: Decimator Data Low Register                                               |     |

| Table 93: Processor Status and Control Register                                     |     |

| Table 94: Reset WDT Register                                                        |     |

| Table 95: Voltage Monitor Control Register                                          |     |

| Table 96: Bandgap Trim Register                                                     |     |

| Table 97: CY8C25122, CY8C26233, CY8C26443, CY8C26643 (256 Bytes of SRAM)            |     |

| Table 98: Table Read for Supervisory Call Functions                                 |     |

| Table 99: Flash Program Memory Protection                                           | 120 |

| Table 100: Programmer Requirements                             | 120 |

|----------------------------------------------------------------|-----|

| Table 101: Absolute Maximum Ratings                            | 125 |

| Table 102: Temperature Specifications                          |     |

| Table 103: DC Operating Specifications                         | 127 |

| Table 104: 5V DC Operational Amplifier Specifications          | 128 |

| Table 105: 3.3V DC Operational Amplifier Specifications        | 129 |

| Table 106: DC Analog Input Pin with Multiplexer Specifications | 130 |

| Table 107: DC Analog Input Pin to SC Block Specifications      | 130 |

| Table 108: 5V DC Analog Output Buffer Specifications           | 130 |

| Table 109: 3.3V DC Analog Output Buffer Specifications         | 131 |

| Table 110: DC Switch Mode Pump Specifications                  | 132 |

| Table 111: 5V DC Analog Reference Specifications               | 133 |

| Table 112: 3.3V DC Analog Reference Specifications             | 134 |

| Table 113: DC Analog PSoC Block Specifications                 |     |

| Table 114: DC Programming Specifications                       | 135 |

| Table 115: AC Operating Specifications                         | 136 |

| Table 116: 5V AC Operational Amplifier Specifications          | 137 |

| Table 117: 3.3V AC Operational Amplifier Specifications        | 138 |

| Table 118: 5V AC Analog Output Buffer Specifications           | 139 |

| Table 119: 3.3V AC Analog Output Buffer Specifications         | 139 |

| Table 120: AC Programming Specifications                       | 140 |

| Table 121: Thermal Impedances                                  | 146 |

| Table 122: Ordering Guide                                      | 147 |

| Table 123: Document Revision History                           | 148 |

## **List of Figures**

| Figure 1: Block Diagram                                    | 13 |

|------------------------------------------------------------|----|

| Figure 2: CY8C25122                                        |    |

| Figure 3: CY8C26233                                        | 15 |

| Figure 4: 26443 PDIP/SOIC/SSOP                             | 16 |

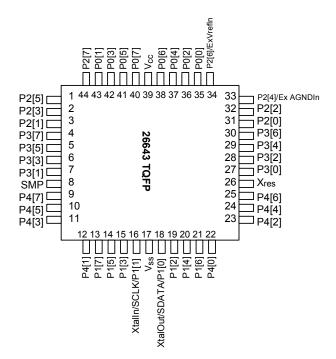

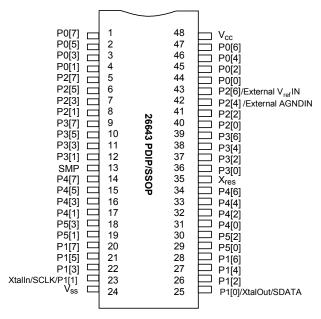

| Figure 5: 26643 TQFP                                       | 17 |

| Figure 6: 26643 PDIP/SSOP                                  | 18 |

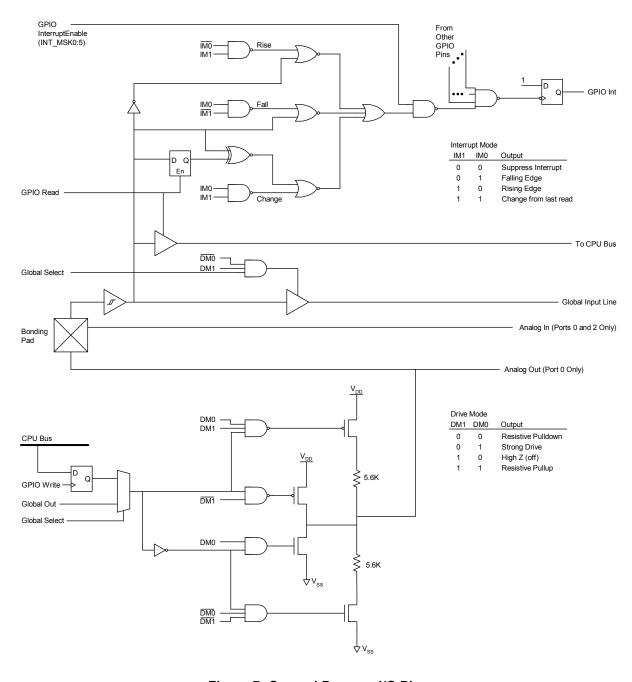

| Figure 7: General Purpose I/O Pins                         | 30 |

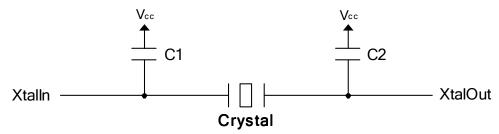

| Figure 8: External Crystal Oscillator Connections          | 37 |

| Figure 9: PSoC MCU Clock Tree of Signals                   |    |

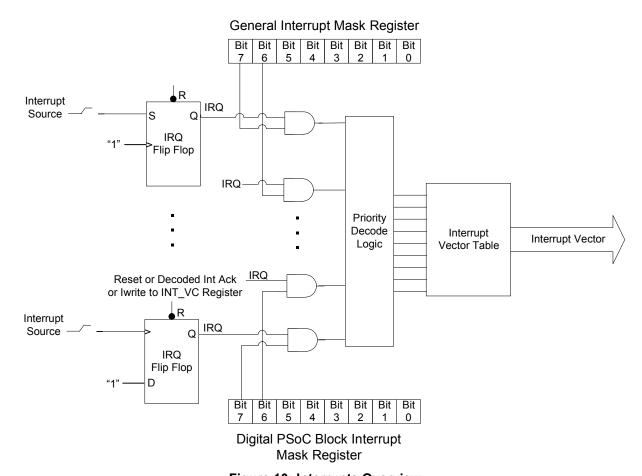

| Figure 10: Interrupts Overview                             | 43 |

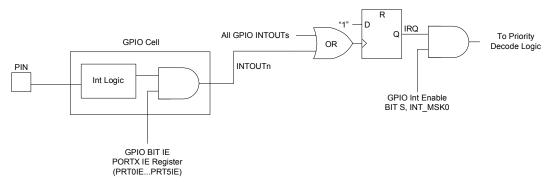

| Figure 11: GPIO Interrupt Enable Diagram                   |    |

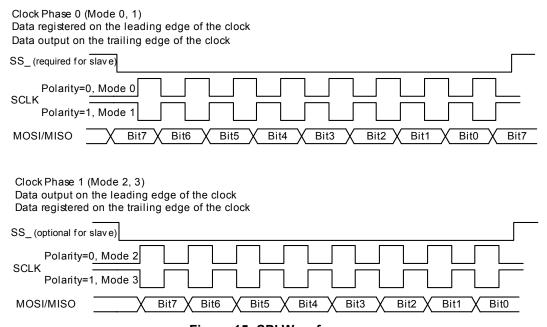

| Figure 12: Digital Basic and Digital Communications PSoC B |    |

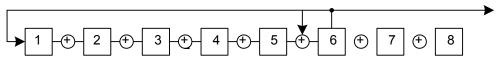

| Figure 13: Polynomial LFSR                                 |    |

| Figure 14: Polynomial PRS                                  |    |

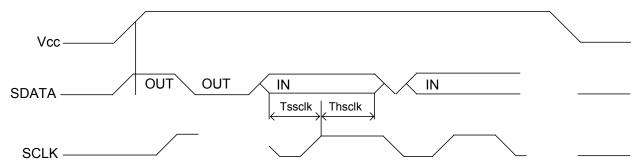

| Figure 15: SPI Waveforms                                   |    |

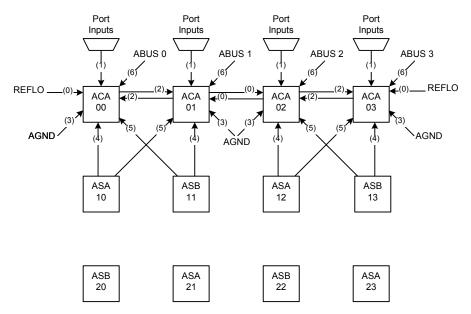

| Figure 16: Array of Analog PSoC Blocks                     |    |

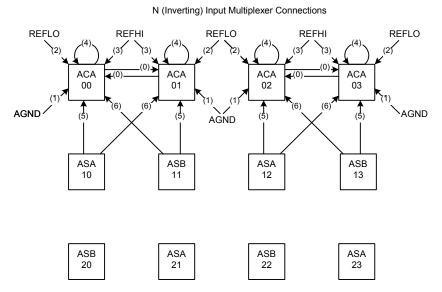

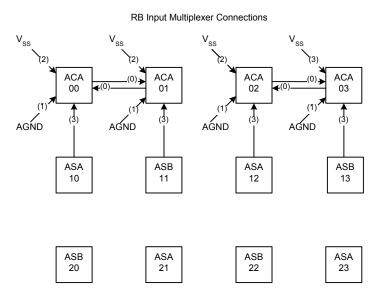

| Figure 17: NMux Connections                                |    |

| Figure 18: PMux Connections                                |    |

| Figure 19: RBotMux Connections                             |    |

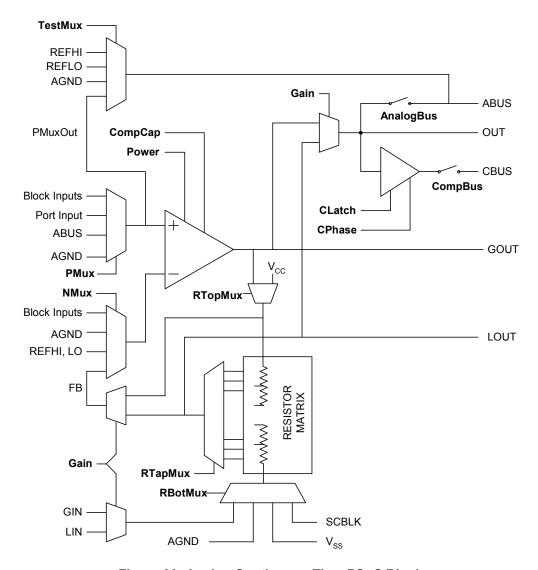

| Figure 20: Analog Continuous Time PSoC Blocks              |    |

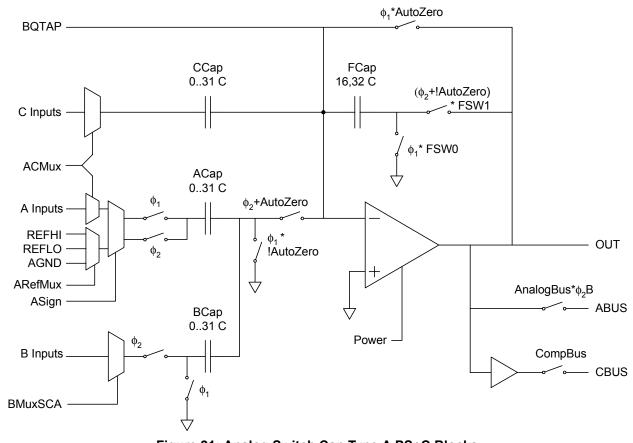

| Figure 21: Analog Switch Cap Type A PSoC Blocks            |    |

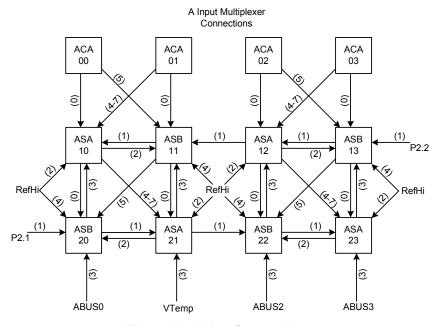

| Figure 22: AMux Connections                                |    |

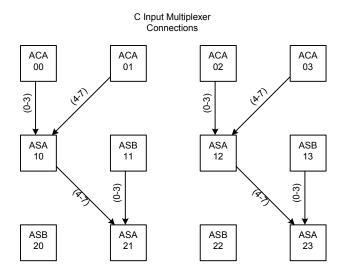

| Figure 23: CMux Connections                                |    |

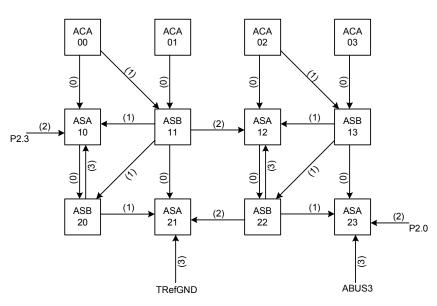

| Figure 24: BMuxSCA/SCB Connections                         |    |

| Figure 25: Analog Switch Cap Type B PSoC Blocks            |    |

| Figure 26: Analog Input Muxing                             |    |

| Figure 27: Analog Output Buffers                           |    |

| Figure 28: Multiply/Accumulate Block Diagram               |    |

| Figure 29: Decimator Coefficients                          |    |

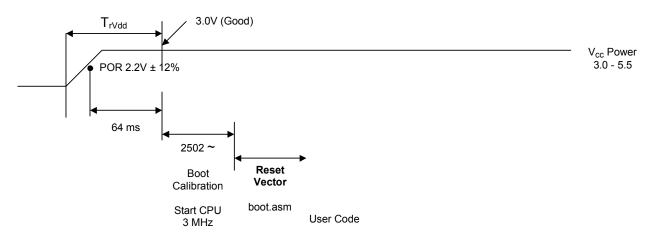

| Figure 30: Execution Reset                                 |    |

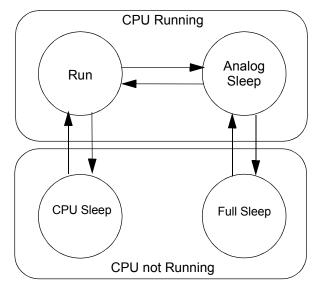

| Figure 31: Three Sleep States                              |    |

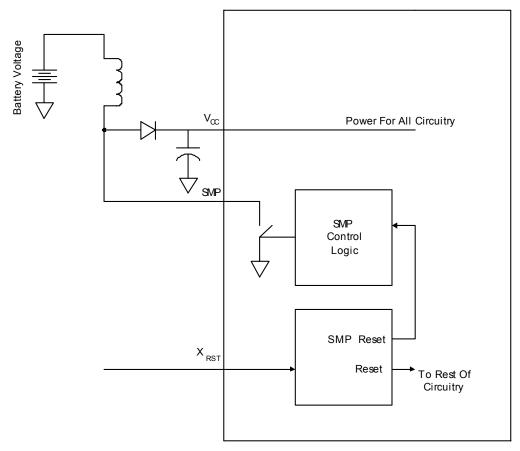

| Figure 32: Switch Mode Pump                                |    |

| Figure 33: Programming Wave Forms                          |    |

| Figure 34: PSoC Designer Functional Flow                   |    |

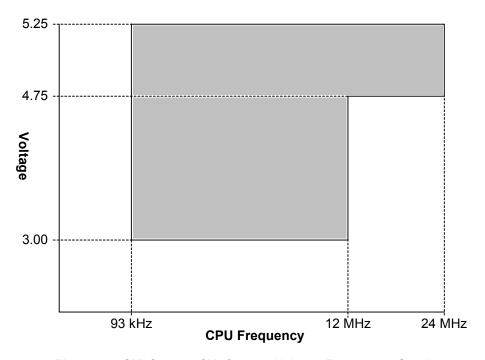

| Figure 35: CY8C25xxx/CY8C26xxx Voltage Frequency Grap      |    |

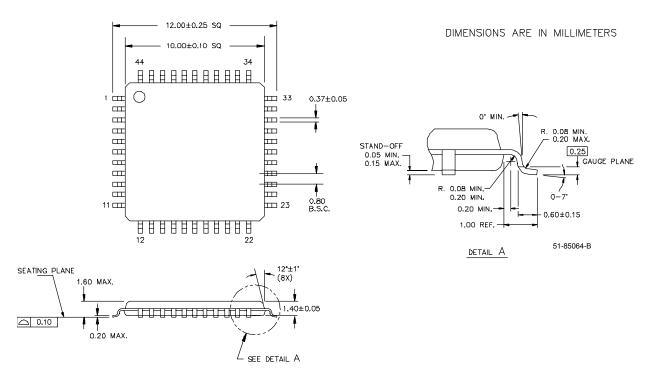

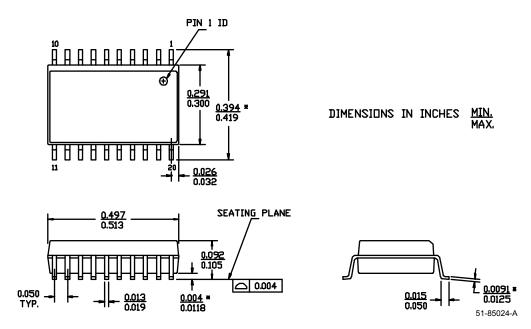

| Figure 36: 44-Lead Thin Plastic Quad Flat Pack A44         |    |

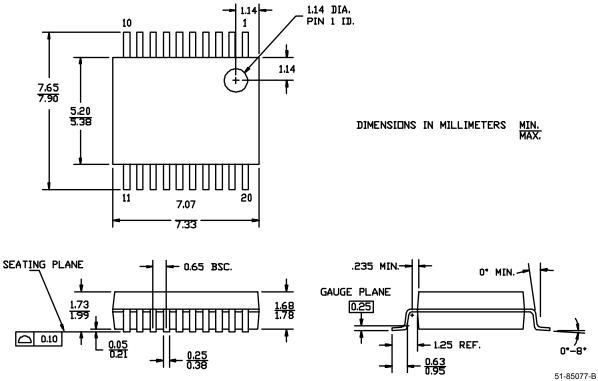

| Figure 37: 20-Pin Shrunk Small Outline Package O20         |    |

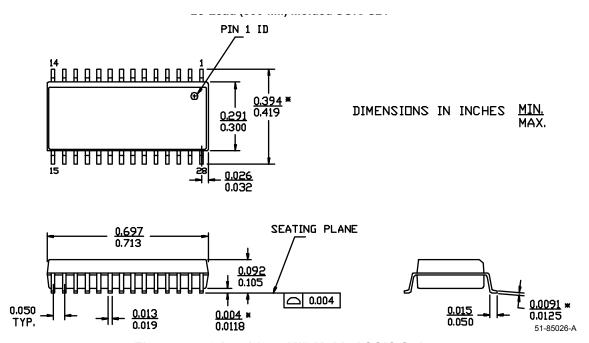

| Figure 38: 28-Lead (210-Mil) Shrunk Small Outline Package  |    |

| Figure 39: 48-Lead Shrunk Small Outline Package O48        |    |

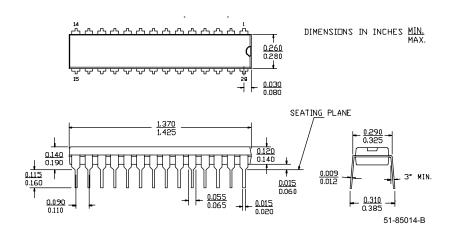

| Figure 40: 20-Lead (300-Mil) Molded DIP P5                 |    |

| Figure 41: 28-Lead (300-Mil) Molded DIP P21                |    |

| Figure 42: 48-Lead (600-Mil) Molded DIP P25                |    |

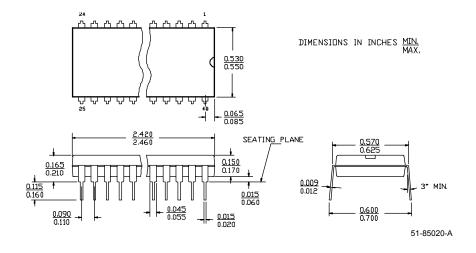

| Figure 43: 20-Lead (300-Mil) Molded SOIC S5                |    |

| Figure 44: 28-Lead (300-Mil) Molded SOIC S21               |    |

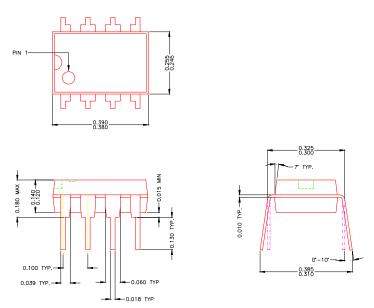

| Figure 45: 8-Lead (300-Mil) Molded DIP                     |    |

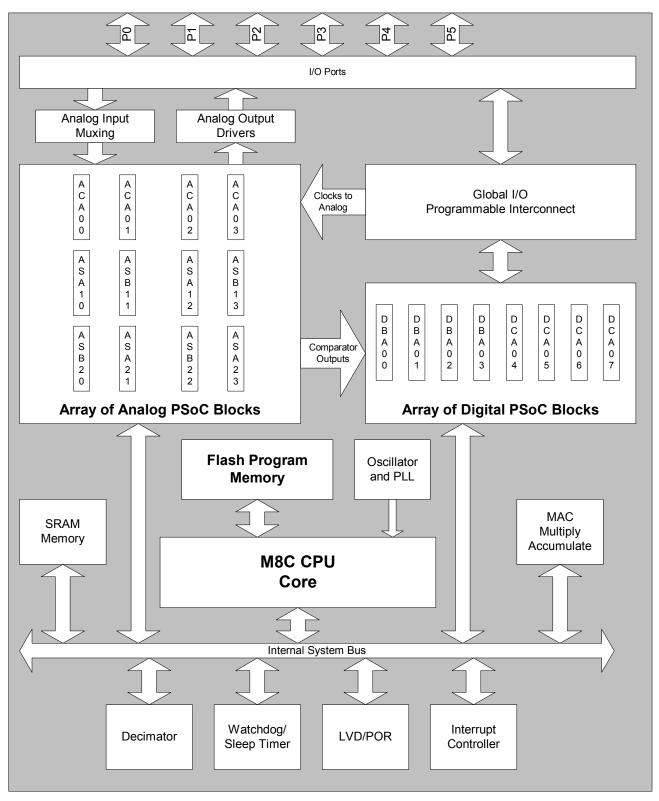

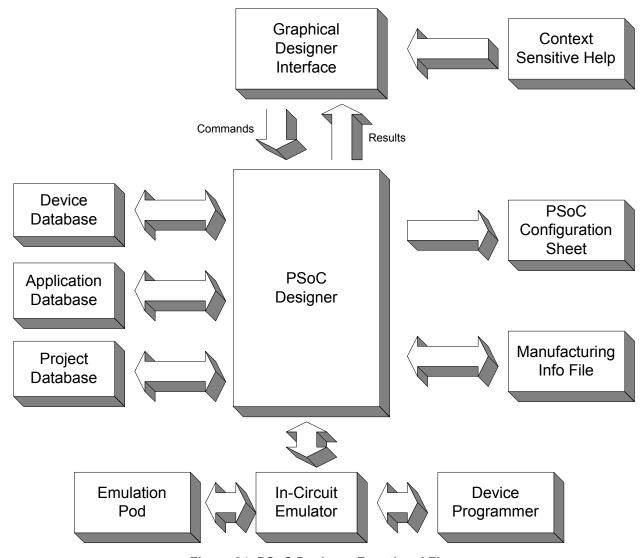

Figure 1: Block Diagram

#### 1.0 Functional Overview

The CPU heart of this next generation family of micro-controllers is a high performance, 8-bit, M8C Harvard architecture microprocessor. Separate program and memory busses allow for faster overall throughput. Processor clock speeds to 24 MHz are available. The processor may also be run at lower clock speeds for powersensitive applications. A rich instruction set allows for efficient low-level language support.

All devices in this family include both analog and digital configurable peripherals (PSoC blocks). These blocks enable the user to define unique functions during configuration of the device. Included are twelve analog PSoC blocks and eight digital PSoC blocks. Potential applications for the digital PSoC blocks are timers, counters, UARTs, CRC generators, PWMs, and other functions. The analog PSoC blocks can be used for SAR ADCs, Multi-slope ADCs, programmable gain amplifiers, programmable filters, DACs, and other functions. Higher order User Modules such as modems, complex motor controllers, and complete sensor signal chains can be created from these building blocks. This allows for an unprecedented level of flexibility and integration in microcontroller-based systems.

A Multiplier/Accumulator (MAC) is available on all devices in this family. The MAC is implemented on this device as a peripheral that is mapped into the register space. When an instruction writes to the MAC input registers, the result of an 8x8 multiply and a 32-bit accumulate are available to be read from the output registers on the next instruction cycle.

The number of general purpose I/Os available in this family of parts range from 6 to 44. Each of these I/O pins has a variety of programmable options. In the output

mode, the user can select the drive strength desired. Any pin can serve as an interrupt source, and can be selected to trigger on positive edges, negative edges, or any change. Digital signal sources can be routed directly from a pin to the digital PSoC blocks. Some pins have additional capability to route analog signals to the analog PSoC blocks.

Multiple oscillator options are available for use in clocking the CPU, analog PSoC blocks and digital PSoC blocks. These options include an internal main oscillator running at 48/24 MHz, an external crystal oscillator for use with a 32.768 kHz watch crystal, and an internal low-speed oscillator for use in clocking the PSoC blocks and the Watchdog/Sleep timer. User selectable clock divisors allow for optimizing code execution speed and power trade-offs.

The different device types in this family provide various amounts of code and data memory. The code space ranges in size from 4K to 16K bytes of user programmable Flash memory. This memory can be programmed serially in either a programming Pod or on the user board. The endurance on the Flash memory is 50,000 erase/write cycles. The data space is 256 bytes of user SRAM.

A powerful and flexible protection model secures the user's sensitive information. This model allows the user to selectively lock blocks of memory for read and write protection. This allows partial code updates without exposing proprietary information.

Devices in this family range from 8 pins through 48 pins in PDIP, SOIC and SSOP packages.

## 1.1 Key Features

Table 1: Device Family Key Features

|                           | CY8C25122       | CY8C26233       | CY8C26443       | CY8C26643       |

|---------------------------|-----------------|-----------------|-----------------|-----------------|

| Operating Frequency       | 93.7kHz - 24MHz | 93.7kHz - 24MHz | 93.7kHz - 24MHz | 93.7kHz - 24MHz |

| Operating Voltage         | 3.0 - 5.25V     | 3.0 - 5.25V     | 3.0 - 5.25V     | 3.0 - 5.25V     |

| Program Memory (KBytes)   | 4               | 8               | 16              | 16              |

| Data Memory (Bytes)       | 256             | 256             | 256             | 256             |

| Digital PSoC Blocks       | 8               | 8               | 8               | 8               |

| Analog PSoC Blocks        | 12              | 12              | 12              | 12              |

| I/O Pins                  | 6               | 16              | 24              | 40/44           |

| External Switch Mode Pump | No              | Yes             | Yes             | Yes             |

| Available Packages        | 8 PDIP          | 20 PDIP         | 28 PDIP         | 48 PDIP         |

|                           |                 | 20 SOIC         | 28 SOIC         | 48 SSOP         |

|                           |                 | 20 SSOP         | 28 SSOP         | 44 TQFP         |

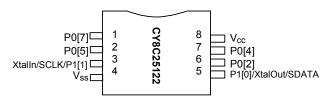

## 1.2 Pin-out Descriptions

Table 2: Pin-out 8 Pin

| Name  | I/O   | Pin | Description                     |

|-------|-------|-----|---------------------------------|

| P0[7] | I/O   | 1   | Port 0[7] (Analog Input)        |

| P0[5] | I/O   | 2   | Port 0[5] (Analog Input/Output) |

| P1[1] | I/O   | 3   | Port 1[1] / Xtalln / SCLK       |

| Vss   | Power | 4   | Ground                          |

| P1[0] | I/O   | 5   | Port 1[0] / XtalOut / SDATA     |

| P0[2] | I/O   | 6   | Port 0[2] (Analog Input/Output) |

| P0[4] | I/O   | 7   | Port 0[4] (Analog Input/Output) |

| Vcc   | Power | 8   | Supply Voltage                  |

Figure 2: CY8C25122

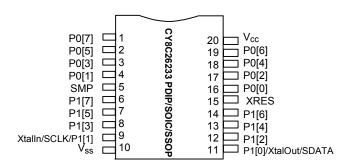

Table 3: Pin-out 20 Pin

| Name  | I/O   | Pin | Description                     |

|-------|-------|-----|---------------------------------|

| P0[7] | I/O   | 1   | Port 0[7] (Analog Input)        |

| P0[5] | I/O   | 2   | Port 0[5] (Analog Input/Output) |

| P0[3] | I/O   | 3   | Port 0[3] (Analog Input/Output) |

| P0[1] | I/O   | 4   | Port 0[1] (Analog Input)        |

| SMP   | 0     | 5   | Switch Mode Pump                |

| P1[7] | I/O   | 6   | Port 1[7]                       |

| P1[5] | I/O   | 7   | Port 1[5]                       |

| P1[3] | I/O   | 8   | Port 1[3]                       |

| P1[1] | I/O   | 9   | Port 1[1] / Xtalln / SCLK       |

| Vss   | Power | 10  | Ground                          |

| P1[0] | I/O   | 11  | Port 1[0] / XtalOut / SDATA     |

| P1[2] | I/O   | 12  | Port 1[2]                       |

| P1[4] | I/O   | 13  | Port 1[4]                       |

| P1[6] | I/O   | 14  | Port 1[6]                       |

| XRES  | 1     | 15  | External Reset                  |

| P0[0] | I/O   | 16  | Port 0[0] (Analog Input)        |

| P0[2] | I/O   | 17  | Port 0[2] (Analog Input/Output) |

| P0[4] | I/O   | 18  | Port 0[4] (Analog Input/Output) |

| P0[6] | I/O   | 19  | Port 0[6] (Analog Input)        |

| Vcc   | Power | 20  | Supply Voltage                  |

Figure 3: CY8C26233

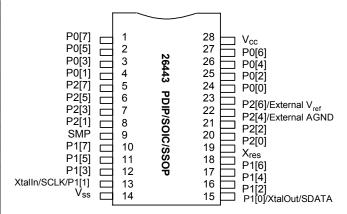

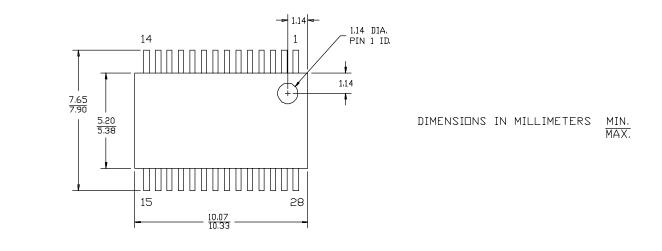

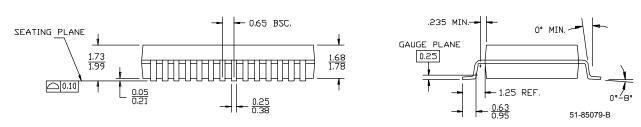

Table 4: Pin-out 28 Pin

| Name  | I/O   | Pin | Description                              |

|-------|-------|-----|------------------------------------------|

| P0[7] | I/O   | 1   | Port 0[7] (Analog Input)                 |

| P0[5] | I/O   | 2   | Port 0[5] (Analog Input/ Output)         |

| P0[3] | I/O   | 3   | Port 0[3] (Analog Input/ Output)         |

| P0[1] | I/O   | 4   | Port 0[1] (Analog Input)                 |

| P2[7] | I/O   | 5   | Port 2[7]                                |

| P2[5] | I/O   | 6   | Port 2[5]                                |

| P2[3] | I/O   | 7   | Port 2[3] (Non-Multiplexed Analog Input) |

| P2[1] | I/O   | 8   | Port 2[1] (Non-Multiplexed Analog Input) |

| SMP   | 0     | 9   | Switch Mode Pump                         |

| P1[7] | I/O   | 10  | Port 1[7]                                |

| P1[5] | I/O   | 11  | Port 1[5]                                |

| P1[3] | I/O   | 12  | Port 1[3]                                |

| P1[1] | I/O   | 13  | Port 1[1] / Xtalln / SCLK                |

| Vss   | Power | 14  | Ground                                   |

| P1[0] | I/O   | 15  | Port 1[0] / XtalOut / SDATA              |

| P1[2] | I/O   | 16  | Port 1[2]                                |

| P1[4] | I/O   | 17  | Port 1[4]                                |

| P1[6] | I/O   | 18  | Port 1[6]                                |

| XRES  | 1     | 19  | External Reset                           |

| P2[0] | I/O   | 20  | Port 2[0] (Non-Multiplexed Analog Input) |

| P2[2] | I/O   | 21  | Port 2[2] (Non-Multiplexed Analog Input) |

| P2[4] | I/O   | 22  | Port 2[4] / External AGNDIn              |

| P2[6] | I/O   | 23  | Port 2[6] / External VREFIn              |

| P0[0] | I/O   | 24  | Port 0[0] (Analog Input)                 |

| P0[2] | I/O   | 25  | Port 0[2] (Analog Input/Output)          |

| P0[4] | I/O   | 26  | Port 0[4] (Analog Input/Output)          |

| P0[6] | I/O   | 27  | Port 0[6] (Analog Input)                 |

| Vcc   | Power | 28  | Supply Voltage                           |

Figure 4: 26443 PDIP/SOIC/SSOP

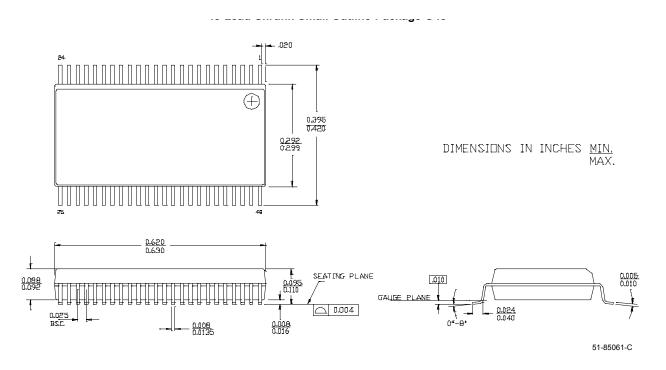

Table 5: Pin-out 44 Pin

| Name  | I/O   | Pin | Description                              |

|-------|-------|-----|------------------------------------------|

| P2[5] | I/O   | 1   | Port 2[5]                                |

| P2[3] | I/O   | 2   | Port 2[3] (Non-Multiplexed Analog Input) |

| P2[1] | I/O   | 3   | Port 2[1] (Non-Multiplexed Analog Input) |

| P3[7] | I/O   | 4   | Port 3[7]                                |

| P3[5] | I/O   | 5   | Port 3[5]                                |

| P3[3] | I/O   | 6   | Port 3[3]                                |

| P3[1] | I/O   | 7   | Port 3[1]                                |

| SMP   | 0     | 8   | Switch Mode Pump                         |

| P4[7] | I/O   | 9   | Port 4[7]                                |

| P4[5] | I/O   | 10  | Port 4[5]                                |

| P4[3] | I/O   | 11  | Port 4[3]                                |

| P4[1] | I/O   | 12  | Port 4[1]                                |

| P1[7] | I/O   | 13  | Port 1[7]                                |

| P1[5] | I/O   | 14  | Port 1[5]                                |

| P1[3] | I/O   | 15  | Port 1[3]                                |

| P1[1] | I/O   | 16  | Port 1[1] / Xtalln / SCLK                |

| Vss   | Power | 17  | Ground                                   |

| P1[0] | I/O   | 18  | Port 1[0] / XtalOut / SDATA              |

| P1[2] | I/O   | 19  | Port 1[2]                                |

| P1[4] | I/O   | 20  | Port 1[4]                                |

| P1[6] | I/O   | 21  | Port 1[6]                                |

| P4[0] | I/O   | 22  | Port 4[0]                                |

| P4[2] | I/O   | 23  | Port 4[2]                                |

| P4[4] | I/O   | 24  | Port 4[4]                                |

Table 5: Pin-out 44 Pin, continued

| P4[6] | I/O   | 25 | Port 4[6]                                |

|-------|-------|----|------------------------------------------|

| XRES  | I     | 26 | External Reset                           |

| P3[0] | I/O   | 27 | Port 3[0]                                |

| P3[2] | I/O   | 28 | Port 3[2]                                |

| P3[4] | I/O   | 29 | Port 3[4]                                |

| P3[6] | I/O   | 30 | Port 3[6]                                |

| P2[0] | I/O   | 31 | Port 2[0] (Non-Multiplexed Analog Input) |

| P2[2] | I/O   | 32 | Port 2[2] (Non-Multiplexed Analog Input) |

| P2[4] | I/O   | 33 | Port 2[4] / External AGNDIn              |

| P2[6] | I/O   | 34 | Port 2[6] / External VREFIn              |

| P0[0] | I/O   | 35 | Port 0[0] (Analog Input)                 |

| P0[2] | I/O   | 36 | Port 0[2] (Analog Input/Output)          |

| P0[4] | I/O   | 37 | Port 0[4] (Analog Input/Output)          |

| P0[6] | I/O   | 38 | Port 0[6] (Analog Input)                 |

| Vcc   | Power | 39 | Supply Voltage                           |

| P0[7] | I/O   | 40 | Port 0[7] (Analog Input)                 |

| P0[5] | I/O   | 41 | Port 0[5] (Analog Input/Output)          |

| P0[3] | I/O   | 42 | Port 0[3] (Analog Input/Output)          |

| P0[1] | I/O   | 43 | Port 0[1] (Analog Input)                 |

| P2[7] | I/O   | 44 | Port 2[7]                                |

Figure 5: 26643 TQFP

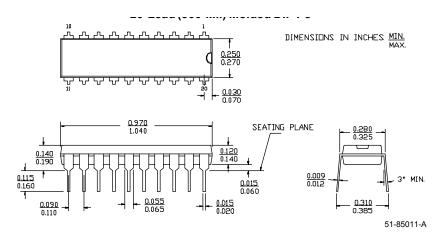

Table 6: Pin-out 48 Pin

| Name  | I/O   | Pin | Description                              |

|-------|-------|-----|------------------------------------------|

| P0[7] | I/O   | 1   | Port 0[7] (Analog Input)                 |

| P0[5] | I/O   | 2   | Port 0[5] (Analog Input/Output)          |

| P0[3] | I/O   | 3   | Port 0[3] (Analog Input/Output)          |

| P0[1] | I/O   | 4   | Port 0[1] (Analog Input)                 |

| P2[7] | I/O   | 5   | Port 2[7]                                |

| P2[5] | I/O   | 6   | Port 2[5]                                |

| P2[3] | I/O   | 7   | Port 2[3] (Non-Multiplexed Analog Input) |

| P2[1] | I/O   | 8   | Port 2[1] (Non-Multiplexed Analog Input) |

| P3[7] | I/O   | 9   | Port 3[7]                                |

| P3[5] | I/O   | 10  | Port 3[5]                                |

| P3[3] | I/O   | 11  | Port 3[3]                                |

| P3[1] | I/O   | 12  | Port 3[1]                                |

| SMP   | 0     | 13  | Switch Mode Pump                         |

| P4[7] | I/O   | 14  | Port 4[7]                                |

| P4[5] | I/O   | 15  | Port 4[5]                                |

| P4[3] | I/O   | 16  | Port 4[3]                                |

| P4[1] | I/O   | 17  | Port 4[1]                                |

| P5[3] | I/O   | 18  | Port 5[3]                                |

| P5[1] | I/O   | 19  | Port 5[1]                                |

| P1[7] | I/O   | 20  | Port 1[7]                                |

| P1[5] | I/O   | 21  | Port 1[5]                                |

| P1[3] | I/O   | 22  | Port 1[3]                                |

| P1[1] | I/O   | 23  | Port 1[1] / Xtalln / SCLK                |

| Vss   | Power | 24  | Ground                                   |

| P1[0] | I/O   | 25  | Port 1[0] / XtalOut / SDATA              |

| P1[2] | I/O   | 26  | Port 1[2]                                |

| P1[4] | I/O   | 27  | Port 1[4]                                |

| P1[6] | I/O   | 28  | Port 1[6]                                |

Table 6: Pin-out 48 Pin, continued

| P5[0] | I/O   | 29 | Port 5[0]                                |

|-------|-------|----|------------------------------------------|

| P5[2] | I/O   | 30 | Port 5[2]                                |

| P4[0] | I/O   | 31 | Port 4[0]                                |

| P4[2] | I/O   | 32 | Port 4[2]                                |

| P4[4] | I/O   | 33 | Port 4[4]                                |

| P4[6] | I/O   | 34 | Port 4[6]                                |

| XRES  | 1     | 35 | External Reset                           |

| P3[0] | I/O   | 36 | Port 3[0]                                |

| P3[2] | I/O   | 37 | Port 3[2]                                |

| P3[4] | I/O   | 38 | Port 3[4]                                |

| P3[6] | I/O   | 39 | Port 3[6]                                |

| P2[0] | I/O   | 40 | Port 2[0] (Non-Multiplexed Analog Input) |

| P2[2] | I/O   | 41 | Port 2[2] (Non-Multiplexed Analog Input) |

| P2[4] | I/O   | 42 | Port 2[4] / External AGNDIn              |

| P2[6] | I/O   | 43 | Port 2[6] / External VREFIn              |

| P0[0] | I/O   | 44 | Port 0[0] (Analog Input)                 |

| P0[2] | I/O   | 45 | Port 0[2] (Analog Input/Output)          |

| P0[4] | I/O   | 46 | Port 0[4] (Analog Input/Output)          |

| P0[6] | I/O   | 47 | Port 0[6] (Analog Input)                 |

| Vcc   | Power | 48 | Supply Voltage                           |

|       |       |    |                                          |

Figure 6: 26643 PDIP/SSOP

#### 2.0 CPU Architecture

#### 2.1 Introduction

This family of microcontrollers is based on a high performance, 8-bit, Harvard architecture microprocessor. Five registers control the primary operation of the CPU core. These registers are affected by various instructions, but are not directly accessible through the register space by the user. For more details on addressing with the register space, see section 4.0.

Table 7: CPU Registers and Mnemonics

| Register        | Mnemonic |

|-----------------|----------|

| Flags           | CPU_F    |

| Program Counter | CPU_PC   |

| Accumulator     | CPU_A    |

| Stack Pointer   | CPU_SP   |

| Index           | CPU_X    |

The 16 bit Program Counter Register (CPU\_PC) allows for direct addressing of the full 16 Kbytes of program memory space available in the largest members of this family. This forms one contiguous program space, and no paging is required.

The Accumulator Register (CPU\_A) is the general-purpose register that holds the results of instructions that specify any of the source addressing modes.

The Index Register (CPU\_X) holds an offset value that is used in the indexed addressing modes. Typically, this is used to address a block of data within the data memory space.

The Stack Pointer Register (CPU\_SP) holds the address of the current top-of-stack in the data memory space. It is affected by the PUSH, POP, LCALL, CALL, RETI, and

RET instructions, which manage the software stack. It can also be affected by the SWAP and ADD instructions.

The Flag Register (CPU\_F) has three status bits: Zero Flag bit [1]; Carry Flag bit [2]; Supervisory State bit [3]. The Global Interrupt Enable bit [0] is used to globally enable or disable interrupts. An extended I/O space address, bit [4], is used to determine which bank of the register space is in use. The user cannot manipulate the Supervisory State status bit [3]. The flags are affected by arithmetic, logic, and shift operations. The manner in which each flag is changed is dependent upon the instruction being executed (i.e., AND, OR, XOR... See Table 23 on page 25).

## 2.2 CPU Registers

## 2.2.1 Flags Register

The Flags Register can only be set or reset with logical instruction.

Table 8: Flags Register

| Bit #          | 7        | 6        | 5        | 4   | 3     | 2     | 1    | 0         |

|----------------|----------|----------|----------|-----|-------|-------|------|-----------|

| POR            | 0        | 0        | 0        | 0   | 0     | 0     | 1    | 0         |

| Read/<br>Write |          |          |          | RW  | R     | RW    | RW   | RW        |

| Bit Name       | Reserved | Reserved | Reserved | XIO | Super | Carry | Zero | Global IE |

Bit 7: Reserved

Bit 6: Reserved

Bit 5: Reserved

Bit 4: XIO Set by the user to select between the register banks

0 = Bank 0

1 = Bank 1

**Bit 3**: **Super** Indicates whether the CPU is executing user code or Supervisor Code. (This code cannot be accessed directly by the user and is not displayed in the ICE debugger.)

0 = User Code

1 = Supervisor Code

Bit 2: Carry Set by CPU to indicate whether there has been a carry in the previous logical/arithmetic operation

0 = No Carry

1 = Carry

Bit 1: Zero Set by CPU to indicate whether there has been a zero result in the previous logical/arithmetic operation

0 = Not Equal to Zero

1 = Equal to Zero

Bit 0: Global IE Determines whether all interrupts are enabled or disabled

0 = Disabled

1 = Enabled

#### 2.2.2 Accumulator Register

Table 9: Accumulator Register (CPU\_A)

| Bit #      | 7                   | 6                   | 5                   | 4                   | 3                   | 2                   | 1                   | 0                   |

|------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|

| POR        | 0                   | 0                   | 0                   | 0                   | 0                   | 0                   | 0                   | 0                   |

| Read/Write | System <sup>1</sup> |

| Bit Name   | Data [7]            | Data [6]            | Data [5]            | Data [4]            | Data [3]            | Data [2]            | Data [1]            | Data [0]            |

Bit [7:0]: Data [7:0] 8-bit data value holds the result of any logical/arithmetic instruction that uses a source addressing mode

1. System - not directly accessible by the user

#### 2.2.3 Index Register

Table 10: Index Register (CPU\_X)

| Bit #          | 7                   | 6                   | 5                   | 4                   | 3                   | 2                   | 1                   | 0                   |

|----------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|

| POR            | 0                   | 0                   | 0                   | 0                   | 0                   | 0                   | 0                   | 0                   |

| Read/<br>Write | System <sup>1</sup> |

| Bit Name       | Data [7]            | Data [6]            | Data [5]            | Data [4]            | Data [3]            | Data [2]            | Data [1]            | Data [0]            |

|                |                     |                     |                     |                     |                     |                     |                     |                     |

Bit [7:0]: Data [7:0] 8-bit data value holds an index for any instruction that uses an indexed addressing mode

1. System - not directly accessible by the user

## 2.2.4 Stack Pointer Register

Table 11: Stack Pointer Register (CPU\_SP)

| Bit #          | 7                   | 6                   | 5                   | 4                   | 3                   | 2                   | 1                   | 0                   |

|----------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|

| POR            | 0                   | 0                   | 0                   | 0                   | 0                   | 0                   | 0                   | 0                   |

| Read/<br>Write | System <sup>1</sup> |

| Bit Name       | Data [7]            | Data [6]            | Data [5]            | Data [4]            | Data [3]            | Data [2]            | Data [1]            | Data [0]            |

|                |                     |                     |                     |                     |                     |                     |                     |                     |

Bit [7:0]: Data [7:0] 8-bit data value holds a pointer to the current top-of-stack

## 2.2.5 Program Counter Register

Table 12: Program Counter Register (CPU\_PC)

| Bit #          | 15   | 14   | 13   | 12   | 11   | 10   | 9    | 8    | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|----------------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|

| POR            | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| Read/<br>Write | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

| Bit            | Data |

| Name           | [15] | [14] | [13] | [12] | [11] | [10] | [9]  | [8]  | [7]  | [6]  | [5]  | [4]  | [3]  | [2]  | [1]  | [0]  |

Bit [15:0]: Data [15:0] 16-bit data value is the low-order/high-order byte of the Program Counter

## 2.3 Addressing Modes

#### 2.3.1 Source Immediate

The result of an instruction using this addressing mode is placed in the A register, the F register, the SP register, or the X register, which is specified as part of the instruction opcode. Operand 1 is an immediate value that serves as a source for the instruction. Arithmetic instructions

require two sources. Instructions using this addressing mode are two bytes in length.

Table 13: Source Immediate

| Opcode      | Operand 1       |

|-------------|-----------------|

| Instruction | Immediate Value |

<sup>1.</sup> System - not directly accessible by the user

<sup>1.</sup> System - not directly accessible by the user

#### Examples:

; In this case, the immediate ; value of 7 is added with the ADD ;Accumulator, and the result ; is placed in the ;Accumulator. :In this case, the immediate MOV Χ, 8 ; value of 8 is moved to the X ;register. ; In this case, the immediate ; value of 9 is logically F, AND 9 ;ANDed with the F register ; and the result is placed in ;the F register.

#### 2.3.2 Source Direct

The result of an instruction using this addressing mode is placed in either the A register or the X register, which is specified as part of the instruction opcode. Operand 1 is an address that points to a location in either the RAM memory space or the register space that is the source for the instruction. Arithmetic instructions require two sources, the second source is the A register or X register specified in the opcode. Instructions using this addressing mode are two bytes in length.

Table 14: Source Direct

| Opcode      | Operand 1      |

|-------------|----------------|

| Instruction | Source Address |

#### Examples:

;In this case, the ; value in the RAM ; memory location at ;address 7 is added ADD Α, [7] ; with the Accumulator, ; and the result is ;placed in the ;Accumulator. ; In this case, the ; value in the register MOV Χ. REG[8] ; space at address 8 is ; moved to the  ${\tt X}$ ;register.

#### 2.3.3 Source Indexed

The result of an instruction using this addressing mode is placed in either the A register or the X register, which is specified as part of the instruction opcode. Operand 1 is added to the X register forming an address that points to a location in either the RAM memory space or the register space that is the source for the instruction. Arithmetic instructions require two sources, the second source is the A register or X register specified in the opcode. Instructions using this addressing mode are two bytes.

Table 15: Source Indexed

| Opcode      | Operand 1    |

|-------------|--------------|

| Instruction | Source Index |

#### Examples:

; In this case, the ; value in the memory ;location at address ADD A, [X+7];X + 7 is added with; the Accumulator, and ; the result is placed ; in the Accumulator. ; In this case, the ; value in the ;register space at VOM Χ, REG [X+8] ;address X + 8 is ; moved to the X ;register.

#### 2.3.4 Destination Direct

The result of an instruction using this addressing mode is placed within either the RAM memory space or the register space. Operand 1 is an address that points to the location of the result. The source for the instruction is either the A register or the X register, which is specified as part of the instruction opcode. Arithmetic instructions require two sources, the second source is the location specified by Operand 1. Instructions using this addressing mode are two bytes in length.

**Table 16: Destination Direct**

| Opcode      | Operand 1           |

|-------------|---------------------|

| Instruction | Destination Address |

#### Examples:

; In this case, the ; value in the memory ;location at address ;7 is added with the ;Accumulator, and the ADD [7], ;result is placed in ;the memory location ; at address 7. The ;Accumulator is ; unchanged. ; In this case, the ;Accumulator is moved ;to the register MOV REG[8], A ; space location at ; address 8. The ;Accumulator is ; unchanged.

#### 2.3.5 Destination Indexed

The result of an instruction using this addressing mode is placed within either the RAM memory space or the register space. Operand 1 is added to the X register forming the address that points to the location of the result. The source for the instruction is the A register. Arithmetic instructions require two sources, the second source is the location specified by Operand 1 added with the X register. Instructions using this addressing mode are two bytes in length.

Table 17: Destination Indexed

| Opcode      | Operand 1         |

|-------------|-------------------|

| Instruction | Destination Index |

#### Example:

;In this case, the value

;in the memory location

;at address X+7 is added

;with the Accumulator,

ADD [X+7], A ;and the result is placed

;in the memory location

;at address x+7. The

;Accumulator is

;unchanged.

#### 2.3.6 Destination Direct Immediate

The result of an instruction using this addressing mode is placed within either the RAM memory space or the register space. Operand 1 is the address of the result. The source for the instruction is Operand 2, which is an immediate value. Arithmetic instructions require two sources, the second source is the location specified by Operand 1. Instructions using this addressing mode are three bytes in length.

Table 18: Destination Direct Immediate

| Opcode      | Operand 1           | Operand 2       |

|-------------|---------------------|-----------------|

| Instruction | Destination Address | Immediate Value |

#### Examples:

;In this case, value in ;the memory location at ;address 7 is added to

ADD [7], 5 ;the immediate value of ;5, and the result is ;placed in the memory ;location at address 7.

;In this case, the ;immediate value of 6 is MOV REG[8], 6 ;moved into the register ;space location at ;address 8.

#### 2.3.7 Destination Indexed Immediate

The result of an instruction using this addressing mode is placed within either the RAM memory space or the register space. Operand 1 is added to the X register to form the address of the result. The source for the instruction is Operand 2, which is an immediate value. Arithmetic instructions require two sources, the second source is the location specified by Operand 1 added with the X register. Instructions using this addressing mode are three bytes in length.

Table 19: Destination Indexed Immediate

| Opcode      | Operand 1         | Operand 2       |

|-------------|-------------------|-----------------|

| Instruction | Destination Index | Immediate Value |

#### Examples:

; In this case, the ; value in the memory ;location at address ;X+7 is added with ADD [X+7], 5 ;the immediate value ; of 5, and the result ; is placed in the ; memory location at ;address X+7. ; In this case, the ;immediate value of 6 ;is moved into the MOV REG[X+8], 6 ;location in the ;register space at ;address X+8.

#### 2.3.8 Destination Direct Direct

The result of an instruction using this addressing mode is placed within the RAM memory. Operand 1 is the address of the result. Operand 2 is an address that points to a location in the RAM memory that is the source for the instruction. This addressing mode is only valid on the MOV instruction. The instruction using this addressing mode is three bytes in length.

**Table 20: Destination Direct Direct**

| Opcode      | Operand 1           | Operand 2      |

|-------------|---------------------|----------------|

| Instruction | Destination Address | Source Address |

#### Example:

;In this case, the value ;in the memory location at MOV [7], [8] ;address 8 is moved to the ;memory location at ;address 7.

#### 2.3.9 Source Indirect Post Increment

The result of an instruction using this addressing mode is placed in the Accumulator. Operand 1 is an address pointing to a location within the memory space, which contains an address (the indirect address) for the source of the instruction. The indirect address is incremented as part of the instruction execution. This addressing mode is only valid on the MVI instruction. The instruction using this addressing mode is two bytes in length. See **Section 7. Instruction Set** in *PSoC Designer: Assembly*

Language User Guide for further details on MVI instruction.

**Table 21: Source Indirect Post Increment**

| Opcode      | Operand 1              |

|-------------|------------------------|

| Instruction | Source Address Address |

#### Example:

;In this case, the value ;in the memory location at ;address 8 is an indirect ;address. The memory ;location pointed to by ;the indirect address is ;moved into the ;Accumulator. The ;indirect address is then ;incremented.

#### 2.3.10 Destination Indirect Post Increment

The result of an instruction using this addressing mode is placed within the memory space. Operand 1 is an address pointing to a location within the memory space, which contains an address (the indirect address) for the destination of the instruction. The indirect address is incremented as part of the instruction execution. The source for the instruction is the Accumulator. This addressing mode is only valid on the MVI instruction. The instruction using this addressing mode is two bytes in length.

**Table 22: Destination Indirect Post Increment**

| Opcode      | Operand 1                   |

|-------------|-----------------------------|

| Instruction | Destination Address Address |

#### Example:

;In this case, the

;value in the memory

;location at address 8

;is an indirect

;address. The

MVI [8], A ;Accumulator is moved

;into the memory

;location pointed to by

;the indirect address.

;The indirect address

;is then incremented.

## 2.4 Instruction Set Summary

Table 23: Instruction Set Summary (Sorted by Mnemonic)

| Opc        |        |       | Instruction Format        | Flags                                                                                                                            | Opc        | _      |       | Instruction Format   | Flags | Opc        |        |       | Instruction Format    | Flags |

|------------|--------|-------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------|------------|--------|-------|----------------------|-------|------------|--------|-------|-----------------------|-------|

| Opcode Hex | Cycles | Bytes |                           |                                                                                                                                  | Opcode Hex | Cycles | Bytes |                      |       | Opcode Hex | Cycles | Bytes |                       |       |

| 09         | 4      |       | ADC A, expr               | C, Z                                                                                                                             | 76         | 7      |       | INC [expr]           | C, Z  | 20         | 5      | 1     |                       |       |

| 0A         | 6      |       | ADC A, [expr]             | C, Z                                                                                                                             | 77         | 8      | 2     | INC [X+expr]         | C, Z  | 18         | 5      | 1     |                       | Z     |

| 0B         | 7      |       | ADC A, [X+expr]           | C, Z                                                                                                                             | Fx         | 13     | 2     | INDEX                | Z     | 10         | 4      | 1     |                       |       |

| 0C         | 7      |       | ADC [expr], A             | C, Z                                                                                                                             | Ex         | 7      | 2     | JACC                 |       | 08         | 4      | 1     | PUSH A                |       |

| 0D         | 8      | 2     | ADC [X+expr], A           | C, Z                                                                                                                             | Сх         | 5      | 2     | JC                   |       | 7E         | 10     | 1     | RETI                  | C, Z  |

| 0E         | 9      | 3     | ADC [expr], expr          | C, Z                                                                                                                             | 8x         | 5      | 2     | JMP                  |       | 7F         | 8      | 1     | RET                   |       |

| 0F         | 10     |       | ADC [X+expr], expr        | C, Z                                                                                                                             | Dx         | 5      | 2     | JNC                  |       | 6A         | 4      | 1     |                       | C, Z  |

| 01         | 4      |       | ADD A, expr               | C, Z                                                                                                                             | Вх         | 5      | 2     | JNZ                  |       | 6B         | 7      | 2     |                       | C, Z  |

| 02         | 6      | 2     | ADD A, [expr]             | C, Z                                                                                                                             | Ax         | 5      | 2     | JZ                   |       | 6C         | 8      | 2     |                       | C, Z  |

| 03         | 7      |       | ADD A, [X+expr]           | C, Z                                                                                                                             | 7C         | 13     | 3     |                      |       | 28         | 11     | 1     | 1                     | Z     |

| 04         | 7      |       | ADD [expr], A             | C, Z                                                                                                                             | 7D         | 7      | 3     |                      |       | 6D         | 4      | 1     |                       | C, Z  |

| 05         | 8      |       | ADD [X+expr], A           | C, Z                                                                                                                             | 4F         | 4      | 1     | MOV X, SP            | _     | 6E         | 7      | 2     |                       | C, Z  |

| 06         | 9      |       | ADD [expr], expr          | C, Z                                                                                                                             | 50         | 4      |       | MOV A, expr          | Z     | 6F         | 8      | 2     |                       | C, Z  |

| 07         | 10     |       | ADD [X+expr], expr        | C, Z                                                                                                                             | 51         | 5      | 2     | ,                    | Z     | 19         | 4      | 2     |                       | C, Z  |

| 38         | 5      |       | ADD SP, expr              |                                                                                                                                  | 52         | 6      | 2     | , ,                  | Z     | 1A         | 6      | 2     |                       | C, Z  |

| 21         | 4      |       | AND A, expr               | Z                                                                                                                                | 53         | 5      | 2     |                      |       | 1B         | 7      | 2     |                       | C, Z  |

| 22         | 6      |       | AND A, [expr]             | Z                                                                                                                                | 54         | 6      |       | MOV [X+expr], A      |       | 1C         | 7      | 2     |                       | C, Z  |

| 23         | 7      |       | AND A, [X+expr]           | Z                                                                                                                                | 55         | 8      |       | MOV [expr], expr     |       | 1D         | 8      | 2     |                       | C, Z  |

| 24         | 7      |       | AND [expr], A             | Z                                                                                                                                | 56         | 9      | 3     |                      |       | 1E         | 9      | 3     |                       | C, Z  |

| 25         | 8      |       | AND [X+expr], A           | Z                                                                                                                                | 57         | 4      |       | MOV X, expr          |       | 1F         | 10     | 3     |                       | C, Z  |

| 26         | 9      |       | AND [expr], expr          | Z                                                                                                                                | 58         | 6      | 2     |                      |       | 00         | 15     | 1     |                       |       |

| 27         | 10     |       | AND [X+expr], expr        | Z                                                                                                                                | 59         | 7      |       | MOV X, [X+expr]      |       | 11         | 4      | 2     |                       | C, Z  |

| 70         | 4      |       | AND F, expr               | C, Z                                                                                                                             | 5A         | 5      | 2     | L 1 2                |       | 12         | 6      | 2     |                       | C, Z  |

| 41         | 9      |       | AND reg[expr], expr       | Z                                                                                                                                | 5B         | 4      | 1     | ,                    | Z     | 13         | 7      | 2     |                       | C, Z  |

| 42         | 10     |       | AND reg[X+expr], expr     | Z                                                                                                                                | 5C         | 4      | 1     |                      |       | 14         | 7      | 2     |                       | C, Z  |

| 64         | 4      | 1     |                           | C, Z                                                                                                                             | 5D         | 6      | 2     |                      | Z     | 15         | 8      | 2     | 1 2                   | C, Z  |

| 65         | 7      | 2     | ASL [expr]                | C, Z                                                                                                                             | 5E         | 7      | 2     | MOV A, reg[X+expr]   | Z     | 16         | 9      | 3     |                       | C, Z  |

| 66         | 8      | 2     | ASL [X+expr]              | C, Z                                                                                                                             | 5F         | 10     | 3     |                      |       | 17         | 10     | 3     | L - P - P - P         | C, Z  |

| 67         | 4      | 1     | ASR A                     | C, Z                                                                                                                             | 60         | 5      |       | MOV reg[expr], A     |       | 4B         | 5      | 1     | - ,                   | Z     |

| 68         | 7      |       | ASR [expr]                | C, Z                                                                                                                             | 61         | 6      | 2     | MOV reg[X+expr], A   |       | 4C         | 7      | 2     |                       | Z     |

| 69         | 8      | 2     | ASR [X+expr]              | C, Z                                                                                                                             | 62         | 8      | 3     | MOV reg[expr], expr  |       | 4D         | 7      | 2     | SWAP X, [expr]        |       |

| 9x         | 11     | 2     |                           |                                                                                                                                  | 63         | 9      | 3     |                      |       | 4E         | 5      | 1     |                       | Z     |

| 39         | 5      | 2     | · · ·                     | if (A=B) Z=1                                                                                                                     | 3E         | 10     | 2     |                      | Z     | 47         | 8      | 3     |                       | Z     |

| 3A         | 7      | 2     | , L 1 3                   | if (A <b) c="1&lt;/td"><td>3F</td><td>10</td><td>2</td><td></td><td></td><td>48</td><td>9</td><td>3</td><td></td><td>Z</td></b)> | 3F         | 10     | 2     |                      |       | 48         | 9      | 3     |                       | Z     |

| 3B         | 8      | 2     | CMP A, [X+expr]           | , ,                                                                                                                              | 40         | 4      | 1     | NOP                  |       | 49         | 9      | 3     |                       | Z     |

| 3C         | 8      | 3     | CMP [expr], expr          |                                                                                                                                  | 29         | 4      | 2     | OR A, expr           | Z     | 4A         | 10     | 3     |                       | Z     |

| 3D         | 9      | 3     |                           |                                                                                                                                  | 2A         | 6      | 2     | OR A, [expr]         | Z     | 72         | 4      |       | XOR F, expr           | C, Z  |

| 73         | 4      | 1     | CPL A                     | Z                                                                                                                                | 2B         | 7      | 2     | OR A, [X+expr]       | Z     | 31         | 4      | 2     | XOR A, expr           | Z     |

| 78         | 4      | 1     | DEC A                     | C, Z                                                                                                                             | 2C         | 7      | 2     | OR [expr], A         | Z     | 32         | 6      | 2     | XOR A, [expr]         | Z     |

| 79         | 4      | 1     | DEC X                     | C, Z                                                                                                                             | 2D         | 8      | 2     | OR [X+expr], A       | Z     | 33         | 7      | 2     | XOR A, [X+expr]       | Z     |

| 7A         | 7      | 2     | DEC [expr]                | C, Z                                                                                                                             | 2E         | 9      | 3     | OR [expr], expr      | Z     | 34         | 7      |       | XOR [expr], A         | Z     |

| 7B         | 8      | 2     |                           | C, Z                                                                                                                             | 2F         | 10     | 3     | OR [X+expr], expr    | Z     | 35         | 8      |       | XOR [X+expr], A       | Z     |

| 30         | 9      | 1     | HALT                      |                                                                                                                                  | 43         | 9      | 3     | OR reg[expr], expr   | Z     | 36         | 9      | 3     | XOR [expr], expr      | Z     |

| 74         | 4      | 1     | INC A                     | C, Z                                                                                                                             | 44         | 10     | 3     | OR reg[X+expr], expr | Z     | 37         | 10     | 3     | XOR [X+expr], expr    | Z     |

| 75         | 4      | 1     | INC X                     | C, Z                                                                                                                             | 71         | 4      | 2     | OR F, expr           | C, Z  | 45         | 9      | 3     | XOR reg[expr], expr   | Z     |

|            | a: Int | Δrrii | pt acknowledge to Interru | int Vector table                                                                                                                 | = 13       | cvcl   | es.   |                      |       | 46         | 10     | 3     | XOR reg[X+expr], expr | Z     |

## 3.0 Memory Organization

## 3.1 Flash Program Memory Organization

Table 24: Flash Program Memory Map

| Address | Description                                |

|---------|--------------------------------------------|

| 0x0000  | Reset Vector                               |

| 0x0004  | Supply Monitor Interrupt Vector            |

| 0x0008  | DBA 00 PSoC Block Interrupt Vector         |

| 0x000C  | DBA 01 PSoC Block Interrupt Vector         |

| 0x0010  | DBA 02 PSoC Block Interrupt Vector         |

| 0x0014  | DBA 03 PSoC Block Interrupt Vector         |

| 0x0018  | DCA 04 PSoC Block Interrupt Vector         |

| 0x001C  | DCA 05 PSoC Block Interrupt Vector         |

| 0x0020  | DCA 06 PSoC Block Interrupt Vector         |

| 0x0024  | DCA 07 PSoC Block Interrupt Vector         |

| 0x0028  | Analog Column 0 Interrupt Vector           |

| 0x002C  | Analog Column 1 Interrupt Vector           |

| 0x0030  | Analog Column 2 Interrupt Vector           |

| 0x0034  | Analog Column 3 Interrupt Vector           |

| 0x0038  | GPIO Interrupt Vector                      |

| 0x003C  | Sleep Timer Interrupt Vector               |

| 0x0040  | On-Chip User Program Memory Starts<br>Here |

|         | ***                                        |

|         | ***                                        |

|         | ***                                        |

| 0x3FFF  | 16K Flash Maximum Depending on Version     |

## 3.2 RAM Data Memory Organization

The stack on this device grows from low addresses to high addresses. The Linker function within PSoC Designer locates the bottom of the stack after the end of Global Variables. This allows the stack to grow from just after the Global Variables until 0xFF. The stack will wrap back to 0x00 on an overflow condition.

Table 25: RAM Data Memory Map

| Address | Description                        |

|---------|------------------------------------|

| 0x00    | First General Purpose RAM Location |

| 0xXX    | General Purpose RAM                |

| 0xXY    | General Purpose RAM                |

| 0xXZ    | Last General Purpose RAM Location  |

| 0xYX    | Bottom of Hardware Stack           |

| 0xYY    |                                    |

| 0xFF    | Top of Hardware Stack              |

## 4.0 Register Organization

#### 4.1 Introduction

There are two register banks implemented on these devices. Each bank contains 256 addresses. The purpose of these register banks is to personalize and parameterize the on-chip resources as well as read and write data values.

The user selects between the two banks by setting the XIO bit in the CPU\_F Flag Register.

In some cases, the same register is available on either bank, for convenience. These registers (71h to 9fh) can be accessed from either bank.

Note: All register addresses not shown are reserved and should never be written. In addition, unused or reserved bits in any register should always be written to 0.

## 4.2 Register Bank 0 Map

Table 26: Bank 0

| Register<br>Name     | Address    | Data Sheet<br>Page | Access  | Register<br>Name     | Address    | Data Sheet<br>Page | Access   | Register<br>Name     | Address    | Page     | Data Sheet | Register                         | Address    | Data Sheet<br>Page | Access |

|----------------------|------------|--------------------|---------|----------------------|------------|--------------------|----------|----------------------|------------|----------|------------|----------------------------------|------------|--------------------|--------|

| •                    |            |                    | D\A/    |                      |            | et                 |          | _                    | •          |          |            |                                  | -          | et                 |        |

| PRT0DR<br>PRT0IE     | 00h<br>01h | 31<br>31           | RW<br>W |                      | 40h<br>41h |                    |          | ASA10CR0<br>ASA10CR1 |            | 86<br>88 | RV<br>RV   |                                  | C0h<br>C1h |                    |        |

| PRT0GS               | 02h        | 32                 | W       |                      | 42h        |                    |          | ASA10CR2             |            | 90       | RV         |                                  | C2h        |                    |        |

| Reserved             | 03h        | -                  |         |                      | 43h        |                    |          |                      | 83h        | 91       | RV         |                                  | C3h        |                    |        |