## CMOS PARALLEL-TO-SERIAL FIFO 256 x 16, 512 x 16, 1024 x 16

IDT72105 IDT72115 IDT72125

#### **FEATURES:**

- 25ns parallel port access time, 35ns cycle time

- · 45MHz serial output shift rate

- Wide x16 organization offering easy expansion

- Low power consumption (50mA typical)

- Least/Most Significant Bit first read selected by asserting the FL/DIR pin

- Four memory status flags: Empty, Full, Half-Full, and Almost-Empty/Almost-Full

- · Dual-Port zero fall-through architecture

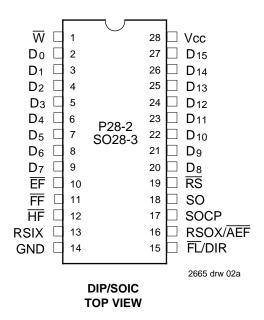

- Available in 28-pin 300 mil plastic DIP and 28-pin SOIC

- Industrial temperature range (-40oC to +85oC) is available, tested to military electrical specifications

#### **DESCRIPTION:**

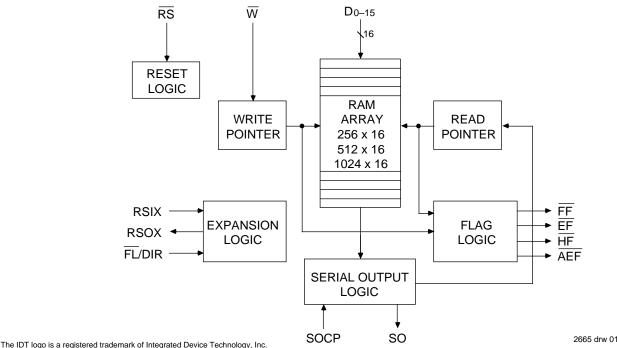

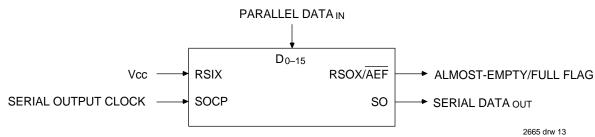

The IDT72105/72115/72125s are very high-speed, low-power, dedicated, parallel-to-serial FIFOs. These FIFOs possess a 16-bit parallel input port and a serial output port with 256, 512 and 1K word depths, respectively.

The ability to buffer wide word widths (x16) make these FIFOs ideal for laser printers, FAX machines, local area networks (LANs), video storage and disk/tape controller applications.

Expansion in width and depth can be achieved using multiple chips. IDT's unique serial expansion logic makes this possible using a minimum of pins.

The unique serial output port is driven by one data pin (SO) and one clock pin (SOCP). The Least Significant or Most Significant Bit can be read first by programming the DIR pin after a reset.

Monitoring the FIFO is eased by the availability of four status flags: Empty, Full, Half-Full and Almost-Empty/Almost-Full. The Full and Empty flags prevent any FIFO data overflow or underflow conditions. The Half-Full Flag is available in both single and expansion mode configurations. The Almost-Empty/Almost-Full Flag is available only in a single device mode.

The IDT72105/15/25 are fabricated using IDT's leading edge, submicron CMOS technology. Military grade product is manufactured in compliance with the latest revision of Mil-STD-883, Class B.

#### **FUNCTIONAL BLOCK DIAGRAM**

FAST is a trademark of National Semiconductor Co.

#### **PIN CONFIGURATION**

#### **PIN DESCRIPTIONS**

| Symbol   | Name                                                                 | 1/0 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------|----------------------------------------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D0-D15   | Inputs                                                               | I   | Data inputs for 16-bit wide data.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| RS       | Reset                                                                | _   | When $\overline{RS}$ is set low, internal READ and WRITE pointers are set to the first location of the RAM array. $\overline{FF}$ and $\overline{HF}$ go HIGH. $\overline{EF}$ and $\overline{AEF}$ go LOW. A reset is required before an initial WRITE after power-up. $\overline{W}$ must be high during the $\overline{RS}$ cycle. Also the First Load pin $(\overline{FL})$ is programmed only during Reset.                                                                     |

| W        | Write                                                                | _   | A write cycle is initiated on the falling edge of WRITE if the Full Flag (FF) is not set. Data set-up and hold times must be adhered to with respect to the rising edge of WRITE. Data is stored in the RAM array sequentially and independently of any ongoing read operation.                                                                                                                                                                                                      |

| SOCP     | Serial Output<br>Clock                                               | _   | A serial bit read cycle is initiated on the rising edge of SOCP if the Empty Flag (EF) is not set. In both Depth and Serial Word Width Expansion modes, all of the SOCP pins are tied together.                                                                                                                                                                                                                                                                                      |

| FL/DIR   | First Load/<br>Direction                                             | _   | This is a dual purpose input used in the width and depth expansion configurations. The First Load (FL) function is programmed only during Reset (RS) and a LOW on FL indicates the first device to be loaded with a byte of data. All other devices should be programmed HIGH. The Direction (DIR) pin controls shift direction after Reset and tells the device whether to read out the Least Significant or Most Significant bit first.                                            |

| RSIX     | Read Serial In Expansion                                             | I   | In the single device configuration, RSIX is set HIGH. In depth expansion or daisy chain expansion, RSIX is connected to RSOX (expansion out) of the previous device.                                                                                                                                                                                                                                                                                                                 |

| SO       | Serial Output                                                        | 0   | Serial data is output on the Serial Output (SO) pin. Data is clocked out LSB or MSB depending on the Direction pin programming. During Expansion the SO pins are tied together.                                                                                                                                                                                                                                                                                                      |

| FF       | Full Flag                                                            | 0   | When $\overline{\text{FF}}$ goes LOW, the device is full and further WRITE operations are inhibited. When $\overline{\text{FF}}$ is HIGH, the device is not full.                                                                                                                                                                                                                                                                                                                    |

| ĒF       | Empty Flag                                                           | 0   | When $\overline{\text{EF}}$ goes LOW, the device is empty and further READ operations are inhibited. When $\overline{\text{EF}}$ is HIGH, the device is not empty.                                                                                                                                                                                                                                                                                                                   |

| HF       | Half-Full Flag                                                       | 0   | When $\overline{\text{HF}}$ is LOW, the device is more than half-full. When $\overline{\text{HF}}$ is HIGH, the device is empty to half-full.                                                                                                                                                                                                                                                                                                                                        |

| RSOX/ĀĒF | Read Serial<br>Out Expansion<br>Almost-Empty,<br>Almost-Full<br>Flag | 0   | This is a dual purpose output. In the single device configuration (RSIX HIGH), this is an $\overline{\text{AEF}}$ output pin. When $\overline{\text{AEF}}$ is LOW, the device is empty-to-(1/8 full -1) or (7/8 full +1)-to-full. When $\overline{\text{AEF}}$ is HIGH, the device is 1/8-full up to 7/8-full. In the Expansion configuration (RSOX connected to RSIX of the next device) a pulse is sent from RSOX to RSIX to coordinate the width, depth or daisy chain expansion. |

| Vcc      | Power Supply                                                         |     | Single power supply of 5V.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| GND      | Ground                                                               |     | Single ground of 0V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

2665 tbl 01

5.35 2

#### STATUS FLAGS

| Nu       | ımber of Words in Fl | FO       |    |     |    |    |

|----------|----------------------|----------|----|-----|----|----|

| IDT72105 | IDT72115             | IDT72125 | FF | ĀĒF | ĦF | ĒĒ |

| 0        | 0                    | 0        | Н  | L   | Н  | L  |

| 1–31     | 1–63                 | 1–127    | Н  | L   | Н  | Н  |

| 32–128   | 64–256               | 128–512  | Н  | Н   | Н  | Н  |

| 129–224  | 257–448              | 513–896  | Н  | Н   | L  | Н  |

| 225–255  | 449–511              | 897–1023 | Н  | L   | L  | Н  |

| 256      | 512                  | 1024     | L  | L   | L  | Н  |

NOTE:

2665 tbl 02

### ABSOLUTE MAXIMUM RATINGS(1)

| Symbol | Rating                               | Commercial    | Unit |

|--------|--------------------------------------|---------------|------|

| VTERM  | Terminal Voltage with Respect to GND | -0.5 to + 7.0 | V    |

| ТА     | Operating<br>Temperature             | 0 to +70      | °C   |

| TBIAS  | Temperature<br>Under Bias            | -55 to +125   | ° C  |

| Tstg   | Storage<br>Temperature               | -55 to + 125  | °C   |

| Іоит   | DC Output<br>Current                 | 50            | mA   |

**NOTE:** 2665 tbl 03

## RECOMMENDED DC OPERATING CONDITIONS

| Symbol              | Parameter          | Min. | Тур. | Max. | Unit |

|---------------------|--------------------|------|------|------|------|

| Vcc                 | Supply Voltage     | 4.5  | 5.0  | 5.5  | ٧    |

| GND                 | Supply Voltage     | 0    | 0    | 0    | V    |

| VIH                 | Input High Voltage | 2.0  | _    | _    | V    |

| V <sub>IL</sub> (1) | Input Low Voltage  | _    |      | 0.8  | V    |

2665 tbl 04

#### DC ELECTRICAL CHARACTERISTICS

(Commercial Vcc =  $5.0V \pm 10\%$ . TA =  $0^{\circ}$ C to  $+70^{\circ}$ C)

|                     |                                                                        | IDT72      |      |      |      |

|---------------------|------------------------------------------------------------------------|------------|------|------|------|

| Symbol              | Parameter                                                              | Min.       | Тур. | Max. | Unit |

| I IL <sup>(1)</sup> | Input Leakage Current (Any Input)                                      | <b>–</b> 1 | _    | 1    | μΑ   |

| IOL <sup>(2)</sup>  | Output Leakage Current                                                 | -10        | _    | 10   | μΑ   |

| Voн                 | Output Logic "1" Voltage IOUT = -2mA <sup>(5)</sup>                    | 2.4        | _    | _    | V    |

| Vol                 | Output Logic "0" Voltage IouT = 8mA <sup>(6)</sup>                     | _          | _    | 0.4  | V    |

| ICC1 <sup>(3)</sup> | Power Supply Current                                                   | _          | 50   | 100  | mA   |

| ICC2 <sup>(3)</sup> | Average Standby Current                                                | _          | 4    | 8    | mA   |

|                     | $(\overline{W} = \overline{RS} = \overline{FL}/DIR = VIH)(SOCP = VIL)$ |            |      |      |      |

| ICC3 (3,4,7)        | Power Down Current                                                     | _          | 1    | 6    | mA   |

5.35

## **NOTES:** 1. Measurements with $0.4V \le VIN \le Vcc$ .

- 2. SOCP = VIL,  $0.4 \le VOUT \le VCC$ .

- 3. Icc measurements are made with outputs open.

- 4.  $\overline{RS} = \overline{FL}/DIR = \overline{W} = Vcc 0.2V$ ; SOCP = 0.2V; all other inputs  $\geq Vcc 0.2$  or  $\leq 0.2V$ .

- For SO. Iout = -4mA.

- 6. For SO, IOUT = 16mA.

- 7. Measurements are made after reset.

2665 tbl 05

3

Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

<sup>1. 1.5</sup>V undershoots are allowed for 10ns once per cycle.

### **AC ELECTRICAL CHARACTERISTICS**

(Commercial:  $VCC = 5V\pm10\%$ ,  $TA = 0^{\circ}C$  to  $+70^{\circ}C$ )

|          |                                                 |        | COM'L                                         |          |                                               |    |          |  |

|----------|-------------------------------------------------|--------|-----------------------------------------------|----------|-----------------------------------------------|----|----------|--|

| Symbol   | Parameter                                       | Figure | 72105L25<br>72115L25<br>72125L25<br>Min. Max. |          | 72105L50<br>72115L50<br>72125L50<br>Min. Max. |    | Unit     |  |

| ts       | Parallel Shift Frequency                        | _      | _                                             | 28.5     | _                                             | 15 | MHz      |  |

| tsocp    | Serial Shift Frequency                          | _      | _                                             | 50       | _                                             | 40 | MHz      |  |

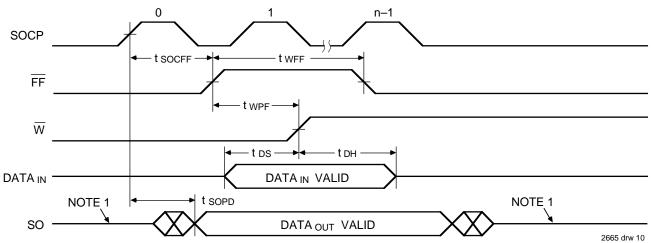

| PARALLE  | L INPUT TIMINGS                                 |        | •                                             | -        |                                               | •  | •        |  |

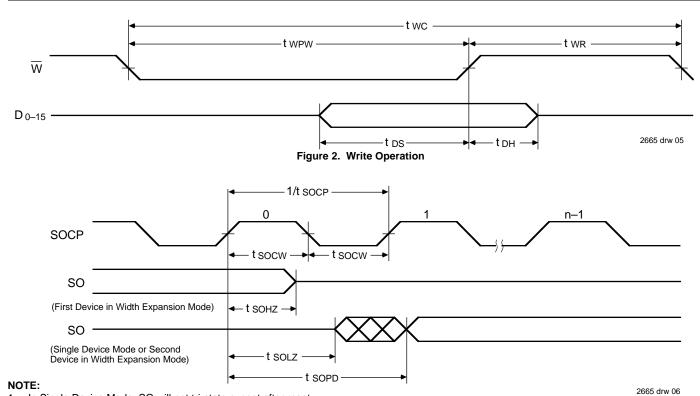

| twc      | Write Cycle Time                                | 2      | 35                                            | _        | 65                                            | _  | ns       |  |

| twpw     | Write Pulse Width                               | 2      | 25                                            | _        | 50                                            | _  | ns       |  |

| twr      | Write Recovery Time                             | 2      | 10                                            | _        | 15                                            | _  | ns       |  |

| tDS      | Data Set-up Time                                | 2      | 12                                            | _        | 15                                            | _  | ns       |  |

| tDH      | Data Hold Time                                  | 2      | 0                                             | _        | 2                                             | _  | ns       |  |

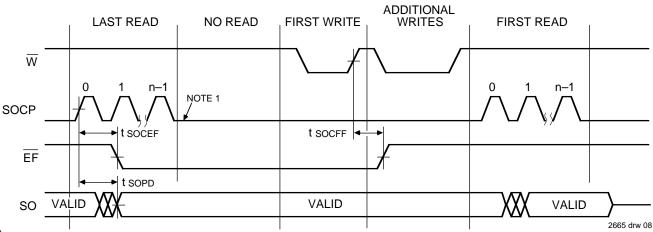

| twer     | Write High to EF HIGH                           | 5, 6   | _                                             | 35       | _                                             | 45 | ns       |  |

| twff     | Write Low to FF LOW                             | 4, 7   | <u> </u>                                      | 35       | _                                             | 45 | ns       |  |

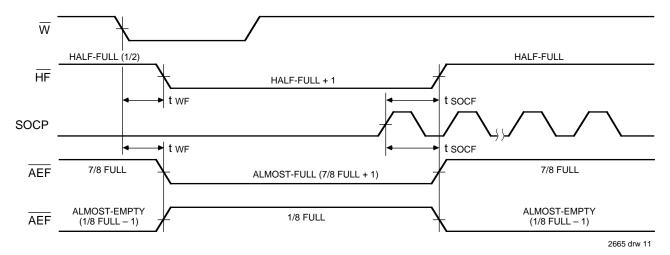

| twF      | Write Low to Transitioning HF, AEF              | 8      | _                                             | 35       | _                                             | 45 | ns       |  |

| twpf     | Write Pulse Width After FF HIGH                 | 7      | 25                                            | _        | 50                                            | _  | ns       |  |

| SERIAL C | OUTPUT TIMINGS                                  |        | •                                             | -        | •                                             | •  |          |  |

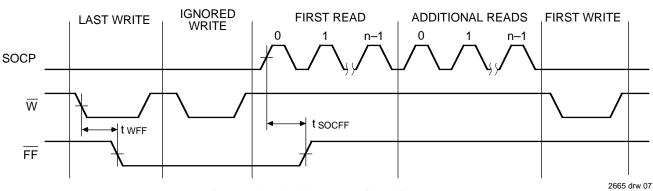

| tSOCP    | Serial Clock Cycle Time                         | 3      | 20                                            | <u> </u> | 25                                            | _  | ns       |  |

| tsocw    | Serial Clock Width HIGH/LOW                     | 3      | 8                                             | _        | 10                                            | _  | ns       |  |

| tsopd    | SOCP Rising Edge to SO Valid Data               | 3      | _                                             | 14       | _                                             | 15 | ns       |  |

| tsohz    | SOCP Rising Edge to SO at High-Z <sup>(1)</sup> | 3      | 3                                             | 14       | 3                                             | 15 | ns       |  |

| tsolz    | SOCP Rising Edge to SO at Low-Z <sup>(1)</sup>  | 3      | 3                                             | 14       | 3                                             | 15 | ns       |  |

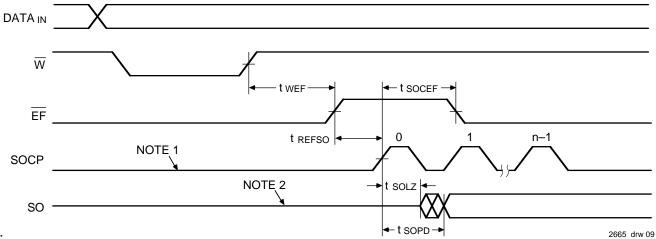

| tsocef   | SOCP Rising Edge to EF LOW                      | 5, 6   | _                                             | 35       | _                                             | 45 | ns       |  |

| tsocff   | SOCP Rising Edge to FF HIGH                     | 4, 7   | _                                             | 35       | _                                             | 45 | ns       |  |

| tsocf    | SOCP Rising Edge to Transitioning HF, AEF       | 8      | _                                             | 35       | _                                             | 45 | ns       |  |

| trefso   | SOCP Delay After EF HIGH                        | 6      | 35                                            | _        | 65                                            | _  | ns       |  |

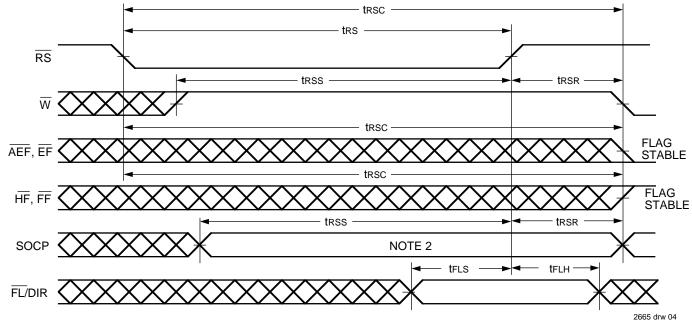

| RESET TI | MINGS                                           |        |                                               | -        |                                               |    | <u>-</u> |  |

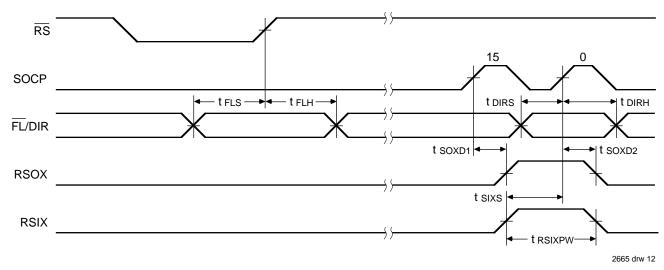

| trsc     | Reset Cycle Time                                | 1      | 35                                            | _        | 65                                            | _  | ns       |  |

| trs      | Reset Pulse Width                               | 1      | 25                                            | _        | 50                                            | _  | ns       |  |

| trss     | Reset Set-up Time                               | 1      | 25                                            | _        | 50                                            | _  | ns       |  |

| trsr     | Reset Recovery Time                             | 1      | 10                                            | _        | 15                                            | _  | ns       |  |

| EXPANSI  | ON MODE TIMINGS                                 |        | ,                                             | -        |                                               |    | -        |  |

| tFLS     | FL Set-up Time to RS Rising Edge                | 9      | 7                                             | _        | 8                                             | _  | ns       |  |

| tFLH     | FL Hold Time to RS Rising Edge                  | 9      | 0                                             | _        | 2                                             | _  | ns       |  |

| tdirs    | DIR Set-up Time to SOCP Rising Edge             | 9      | 10                                            | _        | 12                                            | _  | ns       |  |

| tdirh    | DIR Hold Time from SOCP Rising Edge             | 9      | 5                                             | _        | 5                                             | _  | ns       |  |

| tsoxd1   | SOCP Rising Edge to RSOX Rising Edge            | 9      | _                                             | 15       | _                                             | 17 | ns       |  |

| tSOXD2   | SOCP Rising Edge to RSOX Falling Edge           | 9      | _                                             | 15       |                                               | 17 | ns       |  |

| tsixs    | RSIX Set-up Time to SOCP Rising Edge            | 9      | 5                                             | _        | 8                                             | _  | ns       |  |

| tsixpw   | RSIX Pulse Width                                | 9      | 10                                            | _        | 15                                            | _  | ns       |  |

NOTE:

1. Values guaranteed by design.

2665 tbl 06

#### **AC TEST CONDITIONS**

| Input Pulse Levels            | GND to 3.0V  |

|-------------------------------|--------------|

| Input Rise/Fall Times         | 5ns          |

| Input Timing Reference Levels | 1.5V         |

| Output Reference Levels       | 1.5V         |

| Output Load                   | See Figure A |

2665 tbl 07

#### **CAPACITANCE** (TA = $+25^{\circ}$ C, f = 1.0MHz)

| Symbol | Parameter <sup>(1)</sup> | Conditions | Max. | Unit |

|--------|--------------------------|------------|------|------|

| CIN    | Input Capacitance        | VIN = 0V   | 10   | pF   |

| Соит   | Output<br>Capacitance    | Vout = 0V  | 12   | pF   |

NOTE:

2665 tbl 08

# 5V 1.1KΩ OUTPUT PIN 680Ω 30pF\*

or equivalent circuit

Figure A. Output Load

#### **FUNCTIONAL DESCRIPTION**

#### **Parallel Data Input**

The device must be reset before beginning operation so that all flags are set to their initial state. In width or depth expansion the First Load pin  $(\overline{FL})$  must be programmed to indicate the first device.

The data is written into the FIFO in parallel through the Do- 15 input data lines. A write cycle is initiated on the falling edge of the Write  $(\overline{W})$  signal provided the Full Flag  $(\overline{FF})$  is not asserted. If the  $\overline{W}$  signal changes from HIGH-to-LOW and the Full Flag  $(\overline{FF})$  is already set, the write line is internally inhibited internally from incrementing the write pointer and no write operation occurs.

Data set-up and hold times must be met with respect to the

rising edge of Write. On the rising edge of  $\overline{W}$ , the write pointer is incremented. Write operations can occur simultaneously or asynchronously with read operations.

#### **Serial Data Output**

The serial data is output on the SO pin. The data is clocked out on the rising edge of SOCP providing the Empty Flag ( $\overline{\text{EF}}$ ) is not asserted. If the Empty Flag is asserted then the next data word is inhibited from moving to the output register and being clocked out by SOCP.

The serial word is shifted out Least Significant Bit or Most Significant Bit first, depending on the FL/DIR level during operation. A LOW on DIR will cause the Least Significant Bit to be read out first. A HIGH on DIR will cause the Most Significant Bit to be read out first.

#### NOTES:

- 1. EF, FF, HF and AEF may change status during Reset, but flags will be valid at trsc.

- 2. SOCP should be in the steady LOW or HIGH during tRSS. The first LOW-HIGH (or HIGH-LOW) transition can begin after tRSR.

Figure 1. Reset

<sup>1.</sup> This parameter is sampled and not 100% tested.

<sup>\*</sup>Includes jig and scope capacitances.

1. In Single Device Mode, SO will not tri-state except after reset.

Figure 3. Read Operation

Figure 4. Full Flag from Last Write to First Read

NOTE:

1. SOCP should not be clocked until  $\overline{\text{EF}}$  goes HIGH.

Figure 5. Empty Flag from Last Read to First Write

5.35 6

#### NOTE:

- 1. Once  $\overline{\mathsf{EF}}$  has gone LOW and the last bit of the final word has been shifted out, SOCP should not be clocked until  $\overline{\mathsf{EF}}$  goes HIGH.

- 2. In Single Device Mode, SO will not tri-state except after Reset. It will retain the last valid data.

Figure 6. Empty Boundary Condition Timing

#### NOTE:

1. Single Device Mode will not tri-state but will retain the last valid data.

Figure 7. Full Boundary Condition Timing

Figure 8. Half-Full, Almost-Full and Almost-Empty Timings

5.35

7

Figure 9. Serial Read Expansion

#### **OPERATING CONFIGURATIONS**

#### **Single Device Mode**

The device must be reset before beginning operation so that all flags are set to location zero. In the standalone case, the RSIX line is tied HIGH and indicates single device operation to the device. The RSOX/AEF pin defaults to AEF and outputs the Almost-Empty and Almost-Full Flag.

#### Width Expansion Mode

In the cascaded case, word widths of more than 16 bits can be achieved by using more than one device. By tying the RSOX and RSIX pins together, as shown in Figure 11, and programming which is the Least Significant Device, a cascaded serial word is achieved. The Least Significant Device is programmed by a LOW on the  $\overline{\text{FL}}/\text{DIR}$  pin during reset. All other devices should be programmed HIGH on the  $\overline{\text{FL}}/\text{DIR}$  pin at reset.

Figure 10. Single Device Configuration

|            | Inputs |    |     | Interna                  | l Status                 | Outputs |    |    |

|------------|--------|----|-----|--------------------------|--------------------------|---------|----|----|

| Mode       | RS     | FL | DIR | Read Pointer             | Write Pointer            | ĀĒF, ĒF | FF | ĦF |

| Reset      | 0      | Х  | Х   | Location Zero            | Location Zero            | 0       | 1  | 1  |

| Read/Write | 1      | Х  | 0,1 | Increment <sup>(1)</sup> | Increment <sup>(1)</sup> | Х       | Х  | Х  |

NOTE:

1. Pointer will increment if appropriate flag is HIGH.

2665 tbl 09

Table 1. Reset and First Load Truth Table-Single Device Configuration

The Serial Data Output (SO) of each device in the serial word must be tied together. Since the SO pin is three stated, only the device which is currently shifting out is enabled and driving the 1-bit bus. NOTE: After reset, the level on the FL/DIR pin decides if the Least Significant or Most Significant

Bit is read first out of each device.

The three flag outputs, Empty ( $\overline{\text{EF}}$ ), Half-Full ( $\overline{\text{HF}}$ ) and Full ( $\overline{\text{FF}}$ ), should be taken from the Most Significant Device (in the example, FIFO #2). The Almost-Empty/Almost-Full flag is not available. The RSOX pin is used for expansion.

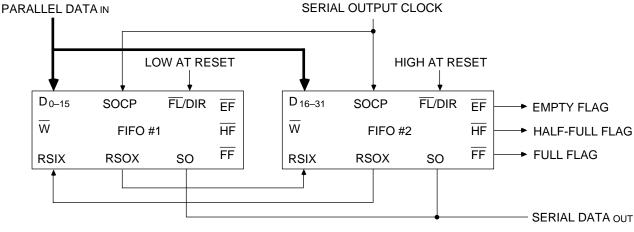

Figure 11. Width Expansion for 32-bit Parallel Data In

2665 drw 14

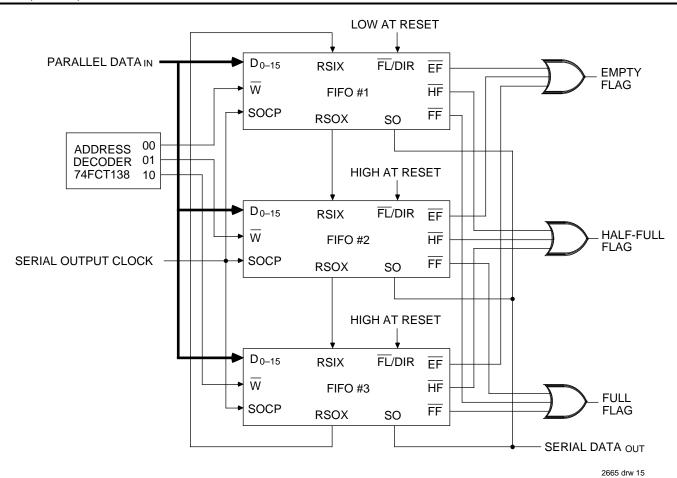

#### **Depth Expansion (Daisy Chain) Mode**

The IDT72105/15/25 can easily be adapted to applications requiring greater than 1024 words. Figure 12 demonstrates Depth Expansion using three IDT72105/15/25s and an IDT74FCT138 Address Decoder. Any depth can be attained by adding additional devices. The Address Decoder is necessary to determine which FIFO is being written. A word of data must be written sequentially into each FIFO so that the data will be read in the correct sequence. The IDT72105/15/25 operates in the Depth Expansion Mode when the following conditions are met:

- The first device must be programmed by holding FL LOW at Reset. All other devices must be programmed by holding FL HIGH at reset.

- 2. The Read Serial Out Expansion pin (RSOX) of each device must be tied to the Read Serial In Expansion pin (RSIX) of the next device (see Figure 12).

- External logic is needed to generate composite Empty, Half-Full and Full Flags. This requires the OR-ing of all EF, HF and FF Flags.

- 4. The Almost-Empty and Almost-Full Flag is not available due to using the RSOX pin for expansion.

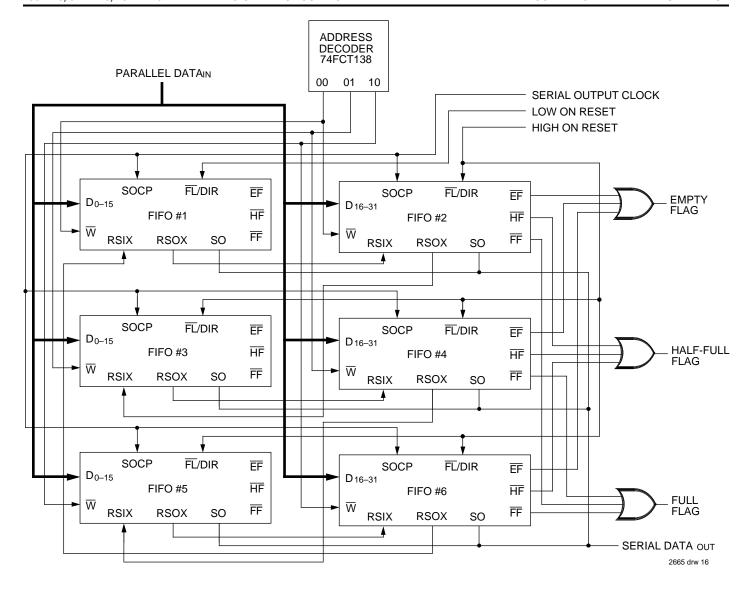

#### Compound Expansion (Daisy Chain) Mode

The IDT72105/15/25 can be expanded in both depth and width as Figure 13 indicates:

- 1. The RSOX-to-RSIX expansion signals are wrapped around sequentially.

- 2. The write  $(\overline{W})$  signal is expanded in width.

- 3. Flag signals are only taken from the Most Significant Devices.

- 4. The Least Significant Device in the array must be programmed with a LOW on FL/DIR during reset.

Figure 12. A 3K x 16 Parallel-to-Serial FIFO using the IDT72125

|                         | Inputs |    |     | Interna       | l Status      | Outputs |        |

|-------------------------|--------|----|-----|---------------|---------------|---------|--------|

| Mode                    | RS     | FL | DIR | Read Pointer  | Write Pointer | ĒĒ      | HF, FF |

| Reset-First Device      | 0      | 0  | Х   | Location Zero | Location Zero | 0       | 1      |

| Reset All Other Devices | 0      | 1  | Х   | Location Zero | Location Zero | 0       | 1      |

| Read/Write              | 1      | Х  | 0,1 | Х             | Х             | Х       | Х      |

#### NOTE:

1. RS = Reset Input, FL/FIR = First Load/Direction, EF = Empty Flag Output, HF = Half- Full Flag Output, FF = Full Flag Output.

Table 2. Reset and First Load Truth Table-Width/Depth Compound Expansion Mode

5.35

10

2665 tbl 10

Figure 13. A 3K x 32 Parallel-to-Serial FIFO using the IDT72125

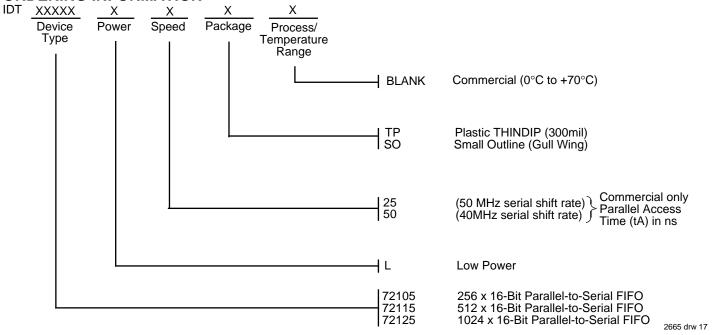

#### **ORDERING INFORMATION**