TOSHIBA TB2104F

TOSHIBA BI-CMOS INTEGRATED CIRCUIT SILICON MONOLITHIC

# TB2104F

# **VFD DRIVER**

The TB2104F is a VFD (fluorescent display tube) driver IC implemented by the Bi-CMOS process.

The logic section is configured with CMOS transistors, and the high voltage tolerant output driver section is configured with bipolar transistors.

### **FEATURES**

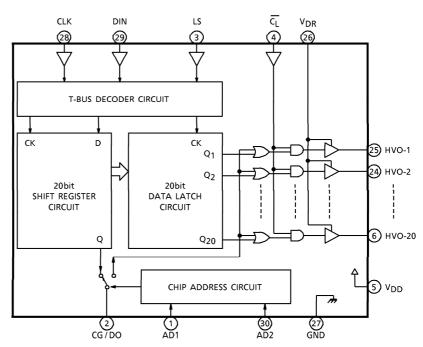

- Incorporates a shift register, latch, and driver capable of handling 20 bits of data.

- The output driver comes with an active pull-down, so it can function as a VFD grid, anode driver.

- Three serial data lines are used to input display data.

- The data receiver section can also accept general-purpose serial data and T-BUS (Toshiba Semiconductor Bus).

Weight: 0.7g (Typ.)

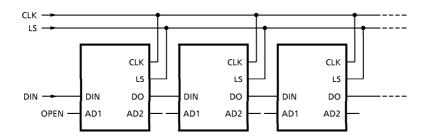

• In serial data mode, multiple drivers can be cascaded to expand the handling capacity in 20bit increments.

# **PIN CONNECTION**

### AD1 AD2 CG/DO 29 DIN LS CLK 28 $\overline{c_L}$ 27 GND 26 V<sub>DR</sub> $V_{DD}$ HVO-20 25 HVO-1 24 HVO-2 HVO-19 23 HVO-3 HVO-18 **■** 8 22 HVO-4 HVO-17 **■** 9 HVO-16 21 HVO-5 HVO-15 20 HVO-6 19 HVO-7 HVO-14 ■ 12 HVO-13 13 18 HVO-8 HVO-12 17 HVO-9

# **BLOCK DIAGRAM**

980508EBA2

TOSHIBA is continually working to improve the quality and the reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to observe standards of safety, and to avoid situations in which a malfunction or failure of a TOSHIBA product could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent products specifications. Also, please keep in mind the precautions and conditions set forth in the TOSHIBA Semiconductor Reliability Handbook.

**TOSHIBA**

# **PIN FUNCTION**

| PIN<br>No. | SYMBOL                                                            | PIN NAME                              | FUNCTION AND OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | REMARKS                                                   |  |  |  |

|------------|-------------------------------------------------------------------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|--|--|--|

| 1          | AD1                                                               | Address                               | <ul> <li>Chip select/address setting inputs</li> <li>When using in Serial Mode, keep AD1 and AD2 "Open".</li> </ul>                                                                                                                                                                                                                                                                                                                                                                          | 3-value<br>input<br>† ⊖<br>%                              |  |  |  |

| 30         | AD2                                                               | Setting Input                         | <ul> <li>In other settings than "Open", it becomes T-BUS Mode<br/>and addresses up to 8 kinds can be set.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                         | 10kΩ                                                      |  |  |  |

| 3          | LS                                                                | Strobe Input                          | <ul><li>Serial data input terminals</li><li>Inputs display data through the DIN terminal</li></ul>                                                                                                                                                                                                                                                                                                                                                                                           |                                                           |  |  |  |

| 28         | CLK                                                               | Clock Input                           | synchronizing with rise of CLK input.  • Display data are updated when inputting "H" level into                                                                                                                                                                                                                                                                                                                                                                                              | CMOS<br>Input                                             |  |  |  |

| 29         | DIN                                                               | Data Input                            | LS terminal after completing data input.  • In T-BUS Mode, LS terminal becomes "PERIOD" input.                                                                                                                                                                                                                                                                                                                                                                                               |                                                           |  |  |  |

| 2          | CG/DO                                                             | Lamp Test<br>Input and<br>Data Output | <ul> <li>Lamp test input terminal and data output terminal</li> <li>In Serial Mode (AD1 = AD2 = Open), this terminal serves as the serial data output terminal and enables cascade connection of driver IC.</li> <li>In T-BUS Mode, this terminal serves as the lamp test input and is able to use all the driver outputs (HVO-1~ - 20) at "H" level by inputting "H" level signal.</li> <li>During the normal operation in T-BUS Mode, use this terminal by fixing at "L" level.</li> </ul> | CMOS Input / CMOS Output built in pull-down resistor 20kΩ |  |  |  |

| 4          | <u>C</u> L                                                        | Clear Input                           | <ul> <li>Driver OFF (blanking) input terminal</li> <li>All the driver outputs are fixed at "L" level when "L" level signal is input.</li> <li>When "H" level signal is input, it becomes the normal mode.</li> </ul>                                                                                                                                                                                                                                                                         | CMOS Input built in pull-up resistor 20kΩ                 |  |  |  |

| 5          | V <sub>DD</sub>                                                   | Logic Unit<br>Power Supply            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                           |  |  |  |

| 26         | V <sub>DR</sub>                                                   | Drive Unit<br>Power Supply            | Power supply and GND terminals                                                                                                                                                                                                                                                                                                                                                                                                                                                               | _                                                         |  |  |  |

| 27         | GND                                                               | Ground                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                           |  |  |  |

|            | HVO-1<br>HVO-2<br>HVO-3<br>::<br>::<br>HVO-18<br>HVO-19<br>HVO-20 | Driver Output                         | ● High-tension driver output terminal  ● Equivalent circuit  VDR  HVO                                                                                                                                                                                                                                                                                                                                                                                                                        | _                                                         |  |  |  |

980508EBA2'

The products described in this document are subject to foreign exchange and foreign trade laws.

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

The information contained herein is subject to change without notice.

### **EXPLANATION OF OPERATION**

- 1. Serial data receiver circuit

- The serial data receiver circuit can be changed over to operate in the serial mode or the T-BUS Mode by switching, the AD1/AD2 terminals.

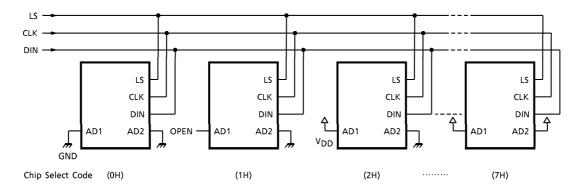

- In T-BUS Mode, the AD1/AD2 terminals become the chip select code inputs and it becomes possible to connect up to 8 drivers on the same bus line.

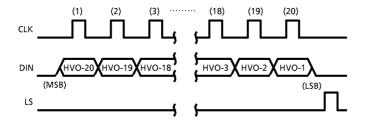

- 1) Input data format in serial data mode (AD1 = AD2 = "Open")

- Display data are updated when data for 20 bits are input from MSB side (HVO-20), synchronizing with rise of CLK signal and LS input is set to "H" level after inputting data.

- When increasing driver ICs, connect them through cascade connection as shown below :

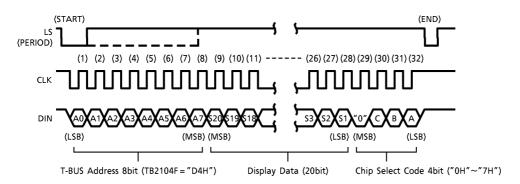

2. Input data format in T-BUS Mode

- In T-BUS Mode, start data transmission with the LS terminal (PERIOD) set at "L" level. Thereafter, send address data 8 bits, display data 20 bits, and chip select code 4 bits, synchronizing with rise of CLK signal.

- After sending data, set the LS terminal to "L" level again and terminate the data sending.

- On a driver IC when chip select code agrees with chip select code by AD1/AD2, display data are updated at fall of LS signal.

- When increasing driver ICs, it is possible to connect up to 8 ICs on the same bus line in combination with AD1/AD2.

- T-BUS address of the TB2104F is "D4H".

- When data are transferred using T-BUS address "00H", the data can be input to all the driver ICs on the bus line independently of chip select codes ("0H"~"7H"). (This function can be used for Power On reset.)

- 3. AD1/AD2 input and chip select codes

AD1/AD2 input are 3-value level inputs and 9 kinds  $(3 \times 3)$  of codes can be set.

| AD1             | AD2             | Α | В | С | CHIP SELECT CODE | MODE   |  |

|-----------------|-----------------|---|---|---|------------------|--------|--|

| V <sub>IH</sub> |                 | 1 | 1 | 1 | "7H"             |        |  |

| VIM             | V <sub>IH</sub> | 0 | 1 | 1 | "6H"             | T-BUS  |  |

| V <sub>IL</sub> |                 | 1 | 0 | 1 | "5H"             |        |  |

| V <sub>IH</sub> | VIM             | 0 | 0 | 1 | "4H"             |        |  |

| V <sub>IM</sub> |                 | _ | _ | _ | _                | Serial |  |

| V <sub>IL</sub> |                 | 1 | 1 | 0 | "3H"             |        |  |

| VIH             | V <sub>IL</sub> | 0 | 1 | 0 | "2H"             | T DIIC |  |

| VIM             |                 | 1 | 0 | 0 | "1H"             | T-BUS  |  |

| V <sub>IL</sub> |                 | 0 | 0 | 0 | "0H"             |        |  |

4. Example of extension of driver ICs in T-BUS Mode chip select code

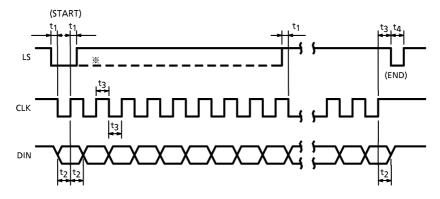

# 5. T-BUS Mode timing chart

- $\bullet \quad \mathsf{f}_{\mathsf{CLK}} \! \leq \! \mathsf{500kHz}$

- $t_1 \ge 0.2 \mu s$ ,  $t_2 \ge 0.2 \mu s$

- $t_3 \ge 1.0 \mu s$ ,  $t_4 \ge 1.0 \mu s$

# Cautions for use

- Therefore, multiple driver outputs may possibly become "H" level simultaneously after the power is turned ON.

- (In this case, the allowable power dissipation of a device using this IC may possible be exceeded, destroying the device.)

- In order to avoid this, while keeping the clear terminal ( $\overline{C_L}$ ) at "L" level, rise the power supply for the logic unit ( $V_{DD}$ ) and then, that for the drivers ( $V_{DR}$ ), reset all the contents of the data latch ("L" level) by serial data, and initialize the driver outputs.

# **MAXIMUM RATINGS** (Ta = 25°C)

| CHARACTERISTIC        | SYMBOL                | RATING                   | UNIT |

|-----------------------|-----------------------|--------------------------|------|

| Supply Voltage        | $V_{DD}$              | -0.3~7.0                 | V    |

| Input Voltage         | VIN                   | $-0.3 \sim V_{DD} + 0.3$ | V    |

| Driver Voltage        | $V_{DR}$              | V <sub>DD</sub> ~60      | ٧    |

| Driver Current        | I <sub>DR</sub>       | 50                       | mA   |

| Power Dissipation     | P <sub>D</sub> (Note) | 800                      | mW   |

| Operating Temperature | T <sub>opr</sub>      | <b>- 40∼85</b>           | °C   |

| Storage Temperature   | T <sub>stg</sub>      | <b>-</b> 55∼150          | °C   |

(Note) In case it is used at more than Ta = 25°C, it is considered by reducing 6.4mW each 1°C.

# **ELECTRICAL CHARACTERISTICS** (Unless otherwise specified, V<sub>DD</sub> = 5V, V<sub>DR</sub> = 50V, Ta = 25°C)

| ELECTRICAL CHARACTERISTICS (Offices officerwise specified, VDD = 3V, VDR = 30V, Ta = 23 C) |                  |                      |                                       |                                                        |                      |                          |                          |                         |         |

|--------------------------------------------------------------------------------------------|------------------|----------------------|---------------------------------------|--------------------------------------------------------|----------------------|--------------------------|--------------------------|-------------------------|---------|

| CHARA                                                                                      | SYMBOL           | TEST<br>CIR-<br>CUIT | TEST CONDITION                        |                                                        | MIN.                 | TYP.                     | MAX.                     | UNIT                    |         |

| Operating Sup                                                                              | $V_{DD}$         | _                    | Logic unit                            |                                                        | 4.5                  | 5.0                      | 5.5                      | ٧                       |         |

| Operating Sup                                                                              | oply Voltage (2) | $V_{DR}$             | _                                     | Driver unit                                            |                      | 10                       | ~                        | 50                      | V       |

| Operating Sup                                                                              | oply Current (1) | I <sub>DD</sub>      | _                                     | No load, No input                                      |                      | _                        | 0.3                      | 1.5                     | mA      |

| Operating Sup                                                                              | <sup>I</sup> DR  | _                    | No load, Output V <sub>OL</sub> level |                                                        | _                    | 2.3                      | 3.5                      | mA                      |         |

| Input                                                                                      | "H" Level        | V <sub>IH</sub> (1)  |                                       | CMOS input terminal DIN, CLK, LS, CG, $\overline{C_L}$ |                      | V <sub>DD</sub><br>×0.7  | ~                        | V <sub>DD</sub>         | V       |

| Voltage                                                                                    | "L" Level        | V <sub>IL (1)</sub>  |                                       |                                                        |                      | GND                      | ?                        | V <sub>DD</sub><br>×0.3 |         |

|                                                                                            | "H" Level        | V <sub>IH</sub> (2)  |                                       | 3-value input terminal<br>AD1, AD2                     |                      | V <sub>DD</sub><br>- 0.5 | ?                        | $V_{DD}$                | V       |

| Input<br>Voltage                                                                           | Open             | V <sub>IM</sub>      | _                                     |                                                        |                      | _                        | V <sub>DD</sub><br>× 0.5 | ı                       |         |

|                                                                                            | "L" Level        | V <sub>IL (2)</sub>  |                                       |                                                        |                      | GND                      | }                        | GND<br>+ 0.5            |         |

| Input                                                                                      | "H" Level        | ΊΗ                   |                                       | CMOS                                                   | V <sub>IH</sub> = 5V | - 1.0                    | ~                        | 1.0                     |         |

| Current                                                                                    | "L" Level        | ΊL                   |                                       | input terminal                                         | V <sub>IL</sub> = 0V | - 1.0                    | ~                        | 1.0                     | $\mu$ A |

| Input Resistan                                                                             | R <sub>IN</sub>  | _                    | 3-value input terminal                |                                                        | 80                   | 100                      | 120                      | kΩ                      |         |

| Output                                                                                     | "H" Level        | <sup>I</sup> OH (1)  |                                       | HVO-1~ − 20                                            | $V_{OH} = 45V$       | _                        | - 8.4                    | <b>-</b> 5              | mΑ      |

| Current                                                                                    | "L" Level        | <sup>I</sup> OL (1)  |                                       | Output terminal                                        | $V_{OL} = 3V$        | 2.0                      | 2.7                      | l                       | IIIA    |

| Output                                                                                     | "H" Level        | <sup>1</sup> OH (2)  |                                       | DO output                                              | $V_{OH} = 4V$        | _                        | - 0.3                    | - 0.1                   | mΑ      |

| Current                                                                                    | "L" Level        | IOL (2)              |                                       | terminal                                               | V <sub>OL</sub> = 1V | 0.1                      | 0.3                      |                         | IIIA    |

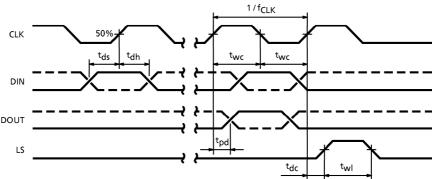

| Clock Frequency                                                                            |                  | fCLK                 |                                       | CLK max. operating                                     |                      | _                        | 5.0                      | 4.0                     | MHz     |

| Clock Pulse Width                                                                          |                  | t <sub>wc</sub>      |                                       | CLK min. operating                                     |                      | 75                       | 60                       |                         | ns      |

| Data Setup Ti                                                                              | tds              |                      | DIN min. operating pulse width        |                                                        | 50                   | 40                       | _                        | ns                      |         |

| Data Hold Time                                                                             |                  | <sup>t</sup> dh      |                                       |                                                        | Fig.1                | 50                       | 40                       |                         | ns      |

| LS Pulse Width                                                                             |                  | t <sub>wl</sub>      | ] 19.1                                | LS min. operating                                      |                      | 80                       | 60                       |                         | ns      |

| CLK-LS Delay Time                                                                          |                  | <sup>t</sup> dc      |                                       | CLK→LS delay time                                      |                      | 50                       | 40                       |                         | ns      |

| CLK-DOUT Delay Time                                                                        |                  | <sup>t</sup> pd      |                                       | CLK→DOUT delay time<br>CL = 30pF                       |                      | _                        | 120                      | 160                     | ns      |

Fig.1 : Serial data timing chart

# OUTLINE DRAWING SSOP30-P-375-1.00 Unit: mm 30 16 20452 0.7TYP 15.9MAX 15.4±0.2 15.9MAX 15.4±0.2 0.92±0.2

Weight: 0.7g (Typ.)