## **DATA SHEET**

# MOS INTEGRATED CIRCUIT $\mu$ PD75517(A)

# **4 BIT SINGLE-CHIP MICROCOMPUTER**

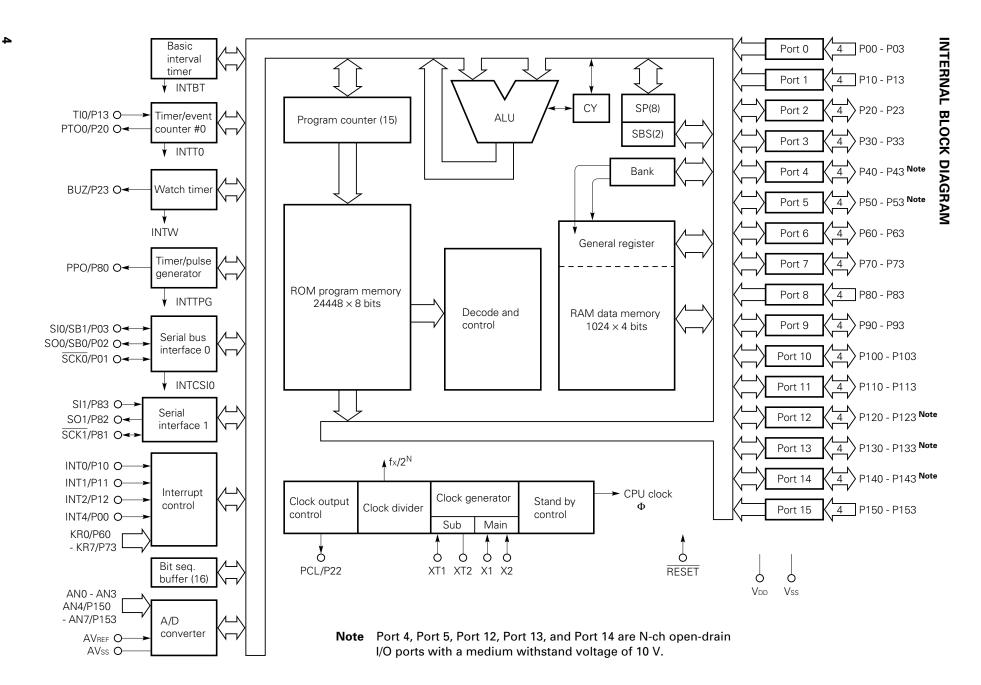

The  $\mu$ PD75517(A) is a 75X series four-bit single-chip microcomputer which enables data processing equivalent to that performed by an eight-bit microcomputer. It is a high-performance product, whose minimum instruction execution time is 0.67  $\mu$ s, shorter than 0.95  $\mu$ s for the conventional  $\mu$ PD75516. The ROM and RAM capacities are also larger, and the throughput of the 75X series is further increased. The  $\mu$ PD75517(A) is suited to controllers of electric parts of automobiles.

#### **FEATURES**

- Higher reliable than the  $\mu$ PD75517

- Capacities of program memory, ROM:  $24448 \times 8$  bits

- Capacity of data memory, RAM:  $1024 \times 4$  bits

- Function for specifying the instruction execution time (useful for high-speed operation and saving power)

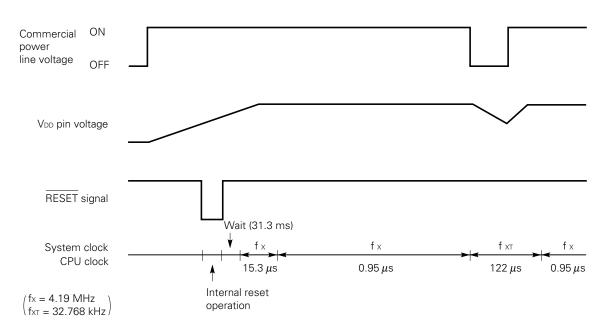

- + 0.67  $\mu$ s/1.33  $\mu$ s/2.67  $\mu$ s/10.7  $\mu$ s (when the main system clock operates at 6.0 MHz)

- + 0.95  $\mu$ s/1.91  $\mu$ s/3.82  $\mu$ s/15.3  $\mu$ s (when the main system clock operates at 4.19 MHz)

- 122  $\mu$ s (when the subsystem clock operates at 32.768 kHz)

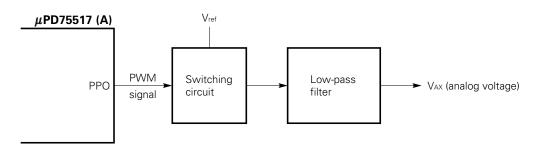

- Built-in A/D converter operable on low voltage

- 8-bit resolution × 8 channels (Successive approximation system)

- VDD = 2.7 to 6.0 V

- Many I/O lines: 64

- Enhanced timer function: 4 channels

- Built-in 8-bit serial interface: Two channels

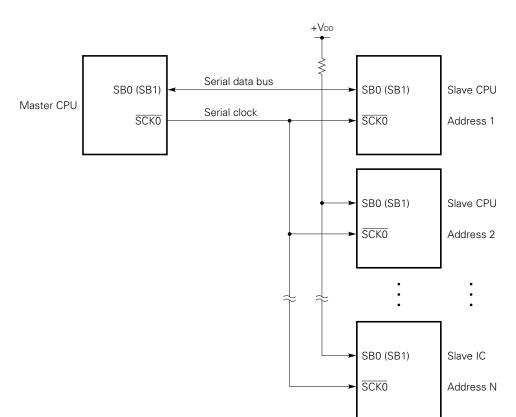

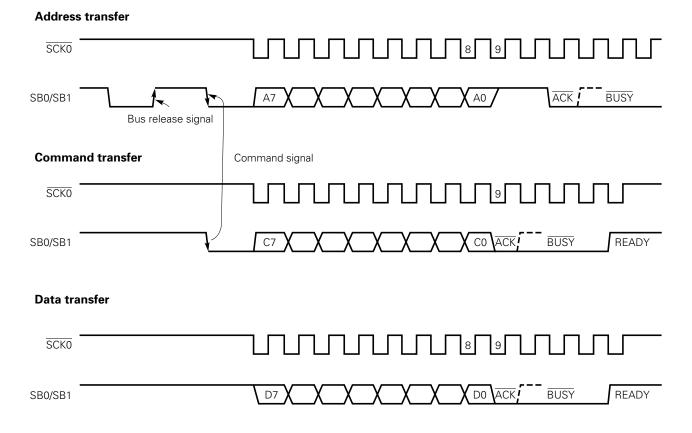

- Built-in NEC serial bus interface (SBI)

- Clock operable with ultra-low power consumption (when 5- $\mu$ A TYP. operates on 3 V.)

- Product with a built-in PROM available: μPD75P518

#### **APPLICATIONS**

Controller of electric parts of automobiles

#### **ORDERING INFORMATION**

| Part number           | Package                                  | Quality grade |  |

|-----------------------|------------------------------------------|---------------|--|

| uPD75517GF(A)-xxx-3B9 | 80-pin plastic QFP (14 mm $	imes$ 20 mm) | Special       |  |

####

Please refer to "Quality Grades on NEC Semiconductor Devices" (Document number IEI-1209) published by NEC Corporation to know the specification of quality grade on the devices and its recommended applications.

The information in this document is subject to change without notice.

# FUNCTIONS

| ltem                |                  |                                 | Functions                                                                                                                                                                                                                                                               |  |  |

|---------------------|------------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Built-in memory ROM |                  | ROM                             | 24448 × 8 bits                                                                                                                                                                                                                                                          |  |  |

|                     |                  | RAM                             | 1024 × 4 bits                                                                                                                                                                                                                                                           |  |  |

| General re          | gisters          |                                 | (4-bit $\times$ 8 or 8-bit $\times$ 4) $\times$ 4 banks                                                                                                                                                                                                                 |  |  |

| Instruction         | cycle            |                                 | <ul> <li>0.67 μs/1.33 μs/2.67 μs/10.7 μs (At 6.0 MHz)</li> <li>0.95 μs/1.91 μs/3.82 μs/15.3 μs (At 4.19 MHz)</li> <li>122 μs (At 32.768 kHz)</li> </ul>                                                                                                                 |  |  |

| I/O ports           | Total            |                                 | 64                                                                                                                                                                                                                                                                      |  |  |

|                     |                  | ber of CMOS<br>lines            | 16 (Shared with INT, SIO, PPO, and analog input. Seven lines can be pulled up by software.)                                                                                                                                                                             |  |  |

|                     | Num<br>I/O li    | ber of CMOS<br>nes              | <ul><li>28 (Four lines for LED driving)</li><li>16 lines can be pulled up by software.</li><li>Four lines can be pulled down by the mask option.</li></ul>                                                                                                              |  |  |

|                     |                  | ber of N-ch<br>-drain I/O lines | 20 (Eight lines for LED driving. Withstand voltage is 10 V. 20 lines can be pulled up by the mask option.)                                                                                                                                                              |  |  |

| A/D conve           | rter             |                                 | <ul> <li>8-bit resolution × 8 channels (Successive approximation system)</li> <li>Capable of low-voltage operation: VDD = 2.7 to 6.0 V</li> </ul>                                                                                                                       |  |  |

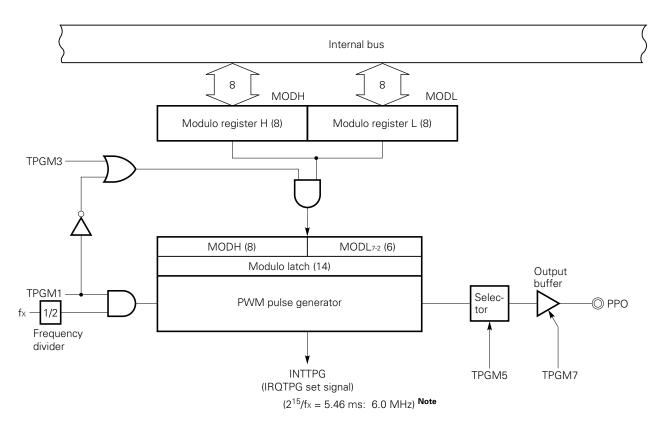

| Timer/cour          | Timer/counter    |                                 | Four channels<br>• Timer/event counter<br>• Basic interval timer<br>• Timer/pulse generator (14-bit PWM output enabled)<br>• Clock timer                                                                                                                                |  |  |

| Serial inter        | Serial interface |                                 | Two channels<br>• NEC standard serial bus interface (SBI)/<br>three-wire SIO: One channel<br>• General clock synchronous serial interface<br>(three-wire SIO): One channel                                                                                              |  |  |

| Interrupt           |                  |                                 | <ul> <li>Vectored interrupt : Seven sources (External: 3, internal: 4)</li> <li>Test input : Two sources (External: 1, internal: 1)</li> <li>Clock test flag is provided.</li> <li>Parallel edge detection flag for key scan input is provided.</li> </ul>              |  |  |

| Instruction set     |                  |                                 | <ul> <li>Set/reset/test/Boolean operation for bit data</li> <li>4-bit data transfer, arithmetic/logical, increment/decrement, and comparison instructions</li> <li>8-bit data transfer, arithmetic/logical, increment/decrement, and comparison instructions</li> </ul> |  |  |

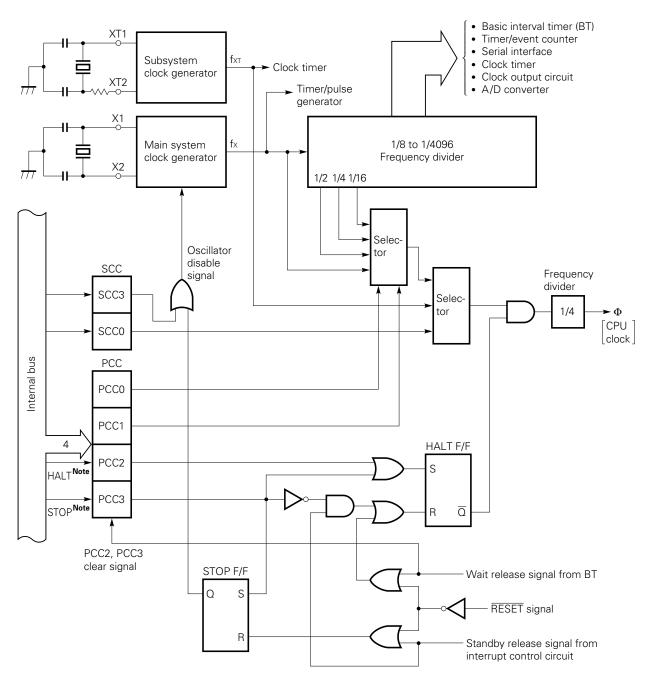

| System clo          | ock gene         | rator                           | <ul> <li>Ceramic/crystal oscillator for main system clock: 6.0 MHz, 4.19 MHz</li> <li>Crystal oscillator for subsystem clock : 32.768 kHz</li> </ul>                                                                                                                    |  |  |

| Operating           | supply v         | oltage                          | V <sub>DD</sub> = 2.7 to 6.0 V                                                                                                                                                                                                                                          |  |  |

| Package             |                  |                                 | 80-pin plastic QFP (14 $	imes$ 20 mm)                                                                                                                                                                                                                                   |  |  |

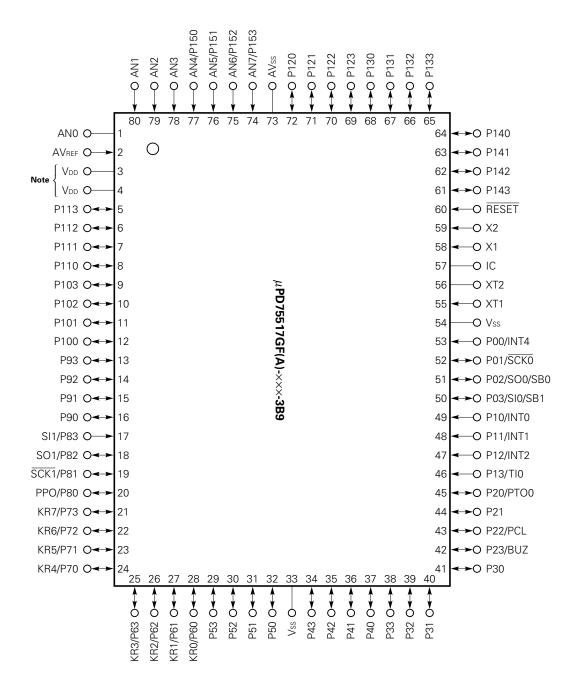

NEC

IC: Internally connected. Connect the IC pin to Vss.

Note Be sure to supply power to both the VDD pins.

### CONTENTS

NEC

| 1.         | PIN I | UNCTIONS                                                | 7   |

|------------|-------|---------------------------------------------------------|-----|

|            | 1.1   | PORT PINS                                               | 7   |

|            | 1.2   | NON-PORT PINS                                           | 9   |

|            | 1.3   | PIN INPUT/OUTPUT CIRCUITS                               | 10  |

|            | 1.4   | CONNECTION OF UNUSED PINS                               | 13  |

|            | 1.5   | SELECTION OF A MASK OPTION                              | 14  |

| <b>2</b> . | ARC   | HTECTURE AND MEMORY MAP OF THE $\mu$ PD75517(A)         | 15  |

|            | 2.1   | DATA MEMORY BANK CONFIGURATION AND ADDRESSING MODES     | 15  |

|            | 2.2   | GENERAL REGISTER BANK CONFIGURATION                     | 19  |

|            | 2.3   | MEMORY-MAPPED I/O                                       | 22  |

| 3.         | INTE  | RNAL CPU FUNCTIONS                                      | 27  |

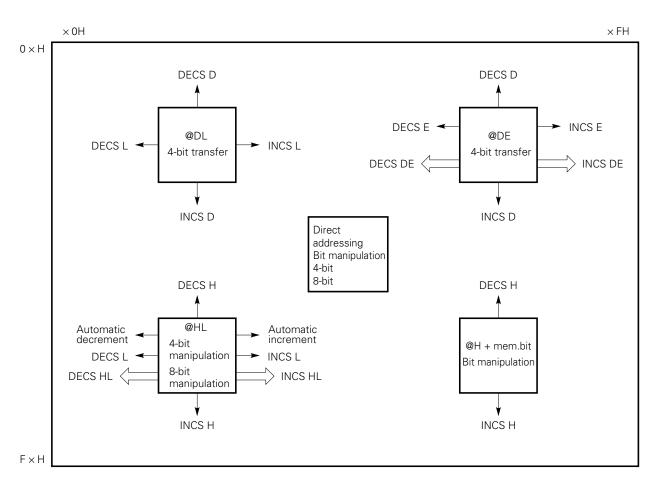

|            | 3.1   | PROGRAM COUNTER (PC)                                    | 27  |

|            | 3.2   | PROGRAM MEMORY (ROM)                                    | 27  |

|            | 3.3   | DATA MEMORY (RAM)                                       | 29  |

|            | 3.4   | GENERAL REGISTERS                                       | 31  |

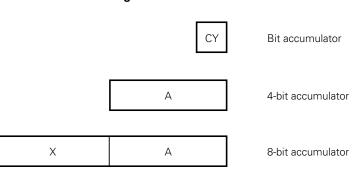

|            | 3.5   | ACCUMULATORS                                            | 32  |

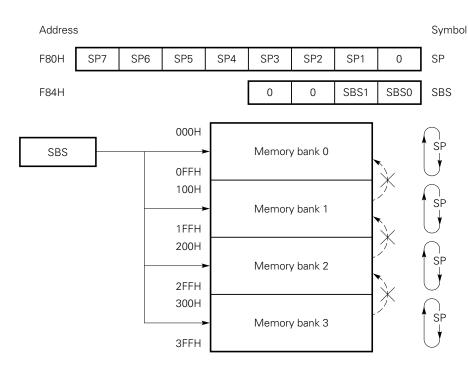

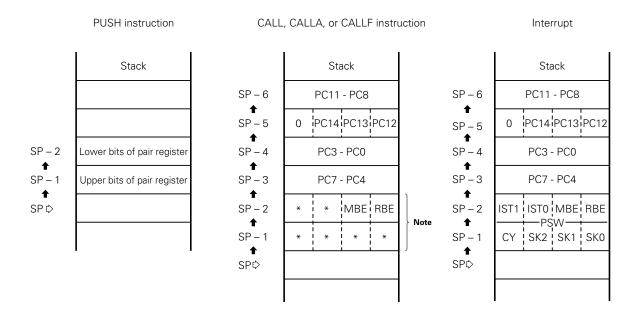

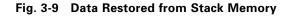

|            | 3.6   | STACK POINTER (SP) AND STACK BANK SELECT REGISTER (SBS) | 32  |

|            | 3.7   | PROGRAM STATUS WORD (PSW)                               | 35  |

|            | 3.8   | BANK SELECT REGISTER (BS)                               | 38  |

| 4.         | PERI  | PHERAL HARDWARE FUNCTIONS                               | 39  |

|            | 4.1   | DIGITAL I/O PORTS                                       | 39  |

|            | 4.2   | CLOCK GENERATOR                                         | 51  |

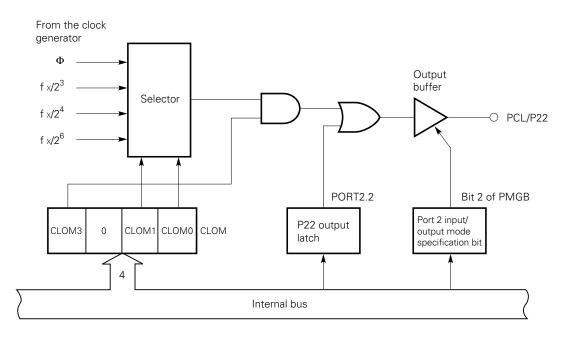

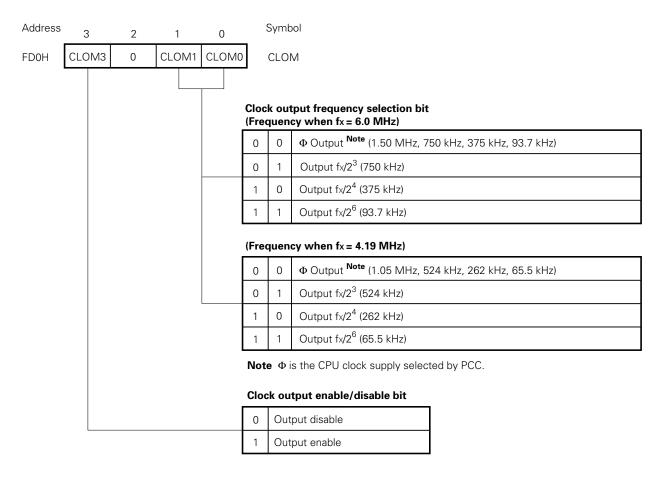

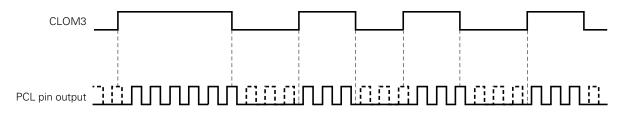

|            | 4.3   | CLOCK OUTPUT CIRCUIT                                    | 60  |

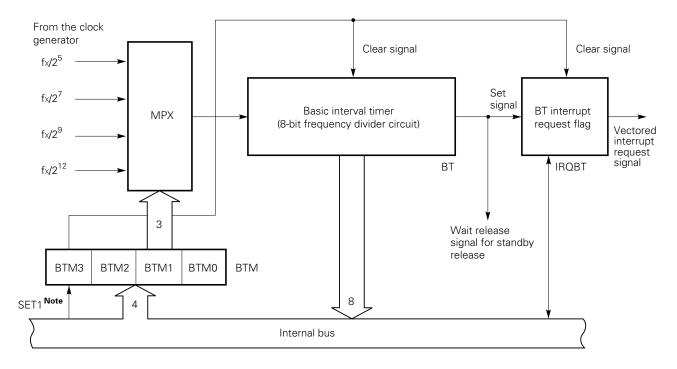

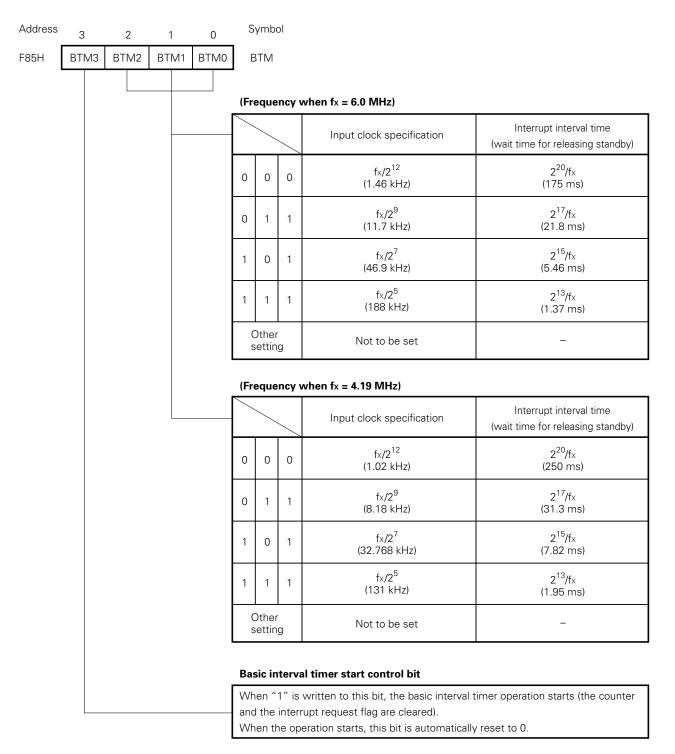

|            | 4.4   | BASIC INTERVAL TIMER                                    | 63  |

|            | 4.5   | CLOCK TIMER                                             | 67  |

|            | 4.6   | TIMER/EVENT COUNTER                                     | 69  |

|            | 4.7   | TIMER/PULSE GENERATOR                                   | 75  |

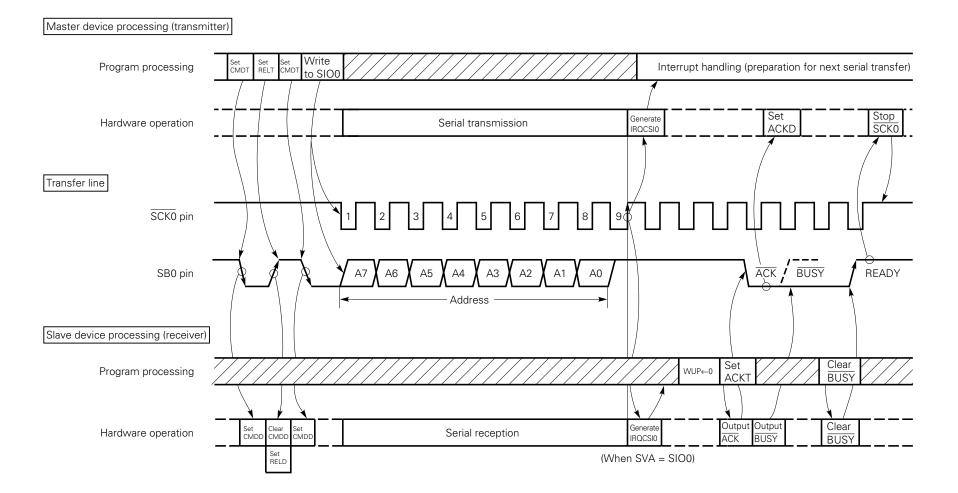

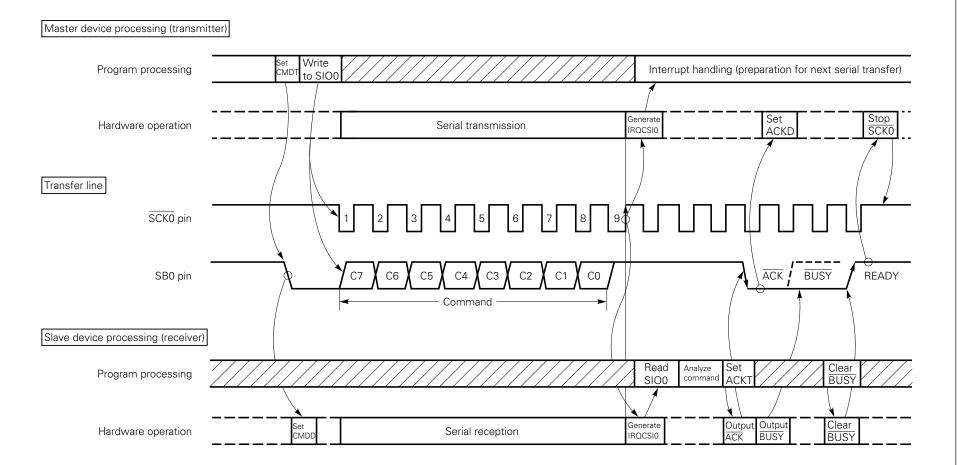

|            | 4.8   | SERIAL INTERFACE (CHANNEL 0)                            | 83  |

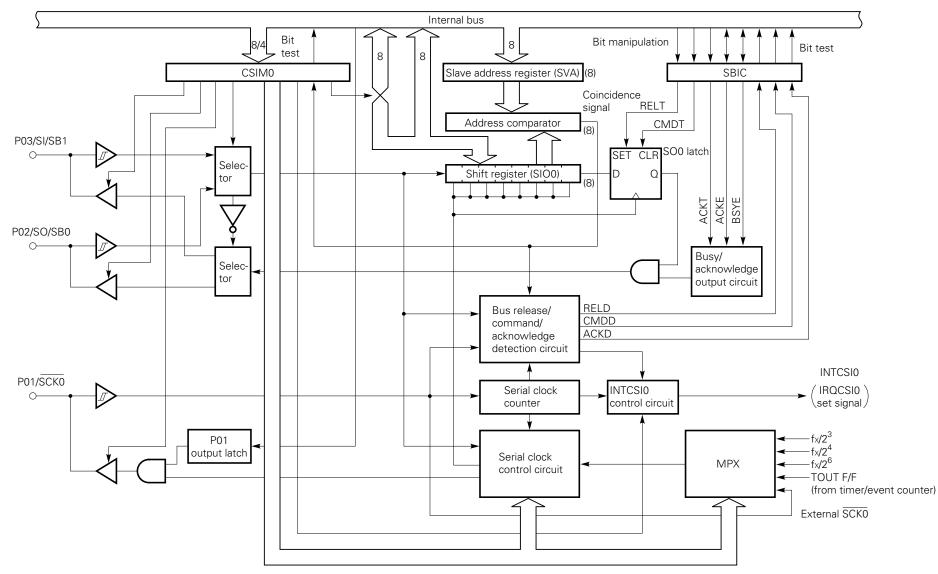

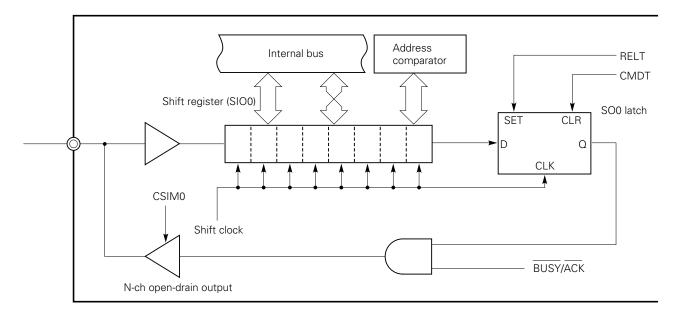

|            |       | 4.8.1 Serial Interface (Channel 0) Functions            | 84  |

|            |       | 4.8.2 Configuration of Serial Interface (Channel 0)     | 84  |

|            |       | 4.8.3 Register Functions                                | 86  |

|            |       | 4.8.4 Signals                                           | 94  |

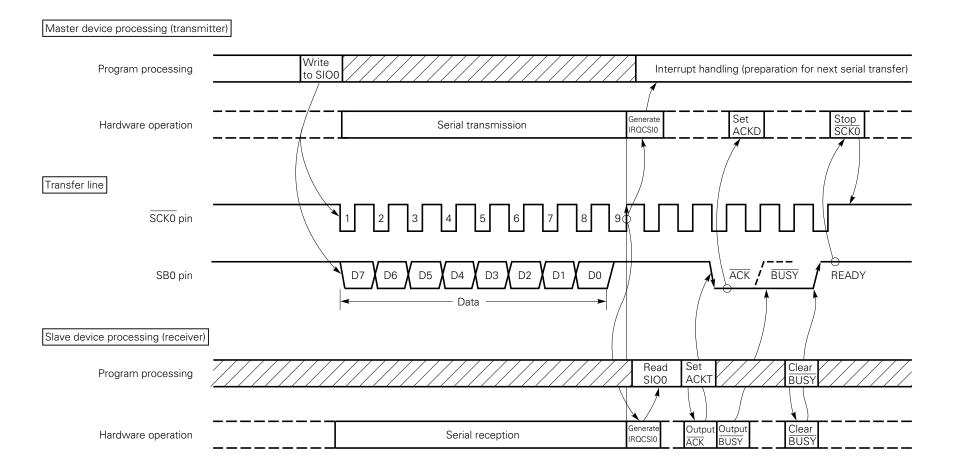

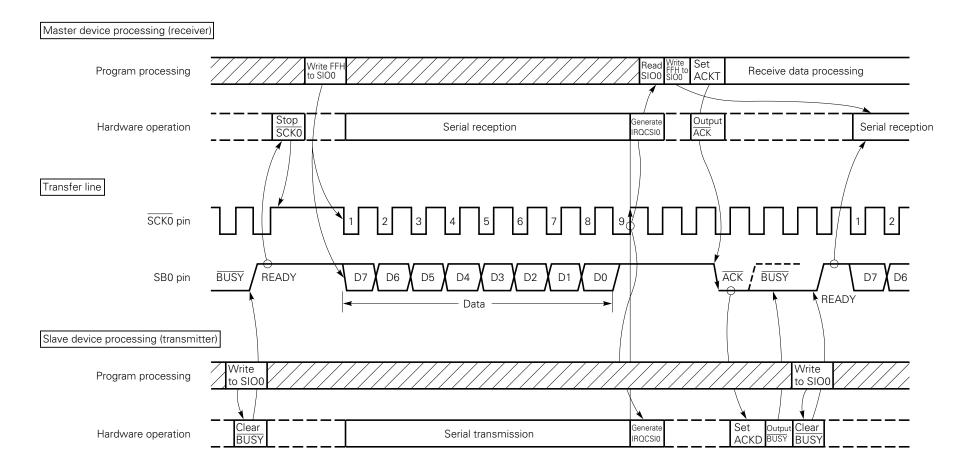

|            |       | 4.8.5 Serial Interface (Channel 0) Operation 1          | 100 |

|            |       | 4.8.6 Transfer Start in Each Mode 1                     | 110 |

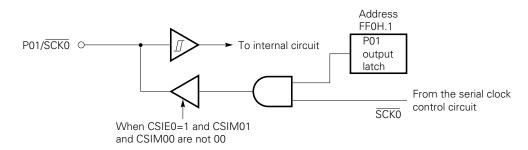

|            |       | 4.8.7 Manipulation of SCK0 Pin Output 1                 | 111 |

|     | 4.9    | 9 SERIAL INTERFACE (CHANNEL 1) 112 |                                            |     |  |  |  |

|-----|--------|------------------------------------|--------------------------------------------|-----|--|--|--|

|     |        | 4.9.1                              | Serial Interface (Channel 1) Functions     | 112 |  |  |  |

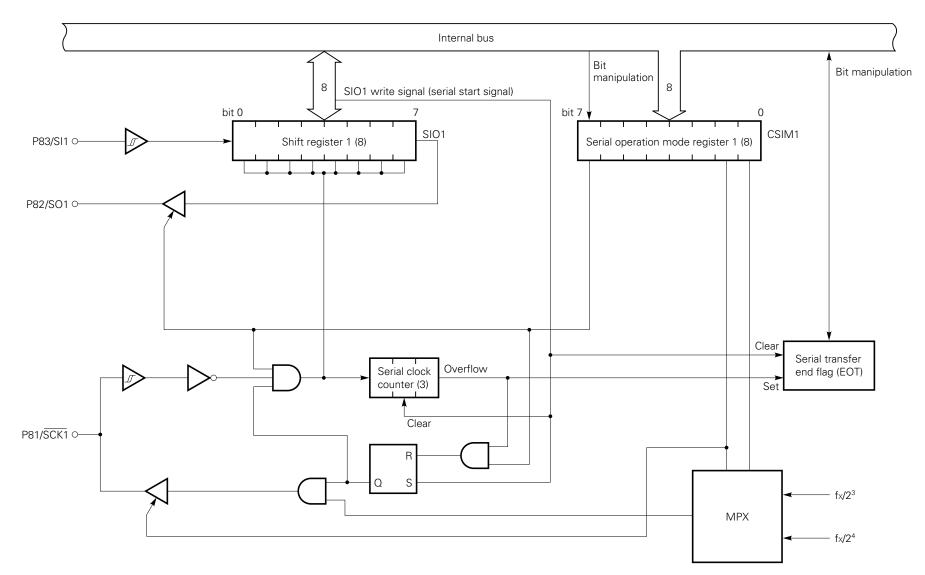

|     |        | 4.9.2                              | Serial Interface (Channel 1) Configuration | 112 |  |  |  |

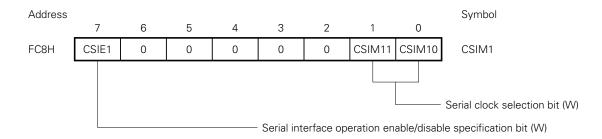

|     |        | 4.9.3                              | Register Functions                         | 114 |  |  |  |

|     |        | 4.9.4                              | Serial Interface (Channel 1) Operation     | 115 |  |  |  |

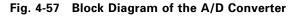

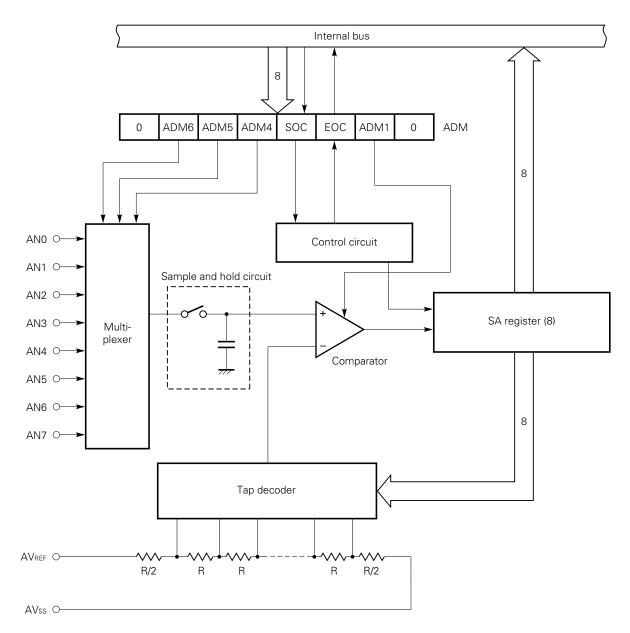

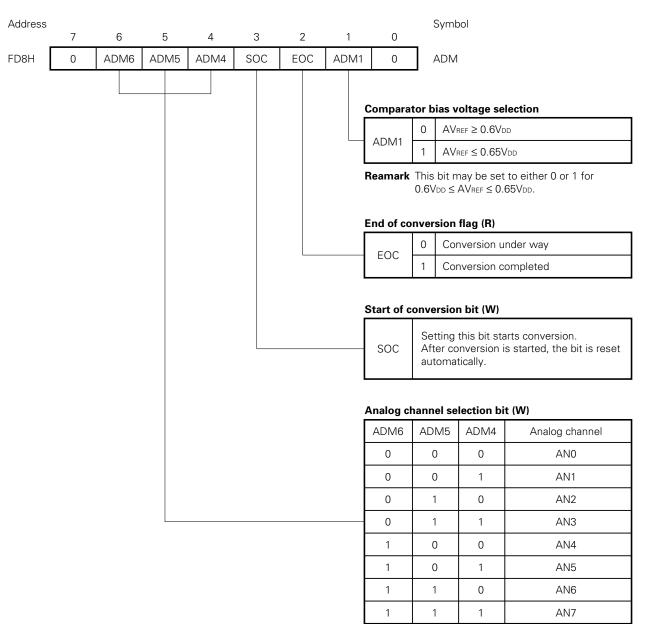

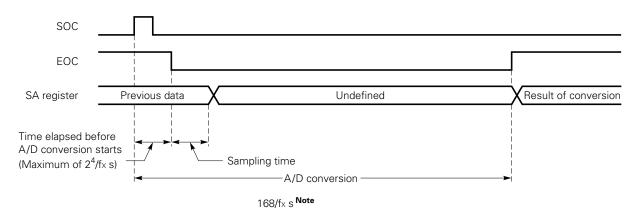

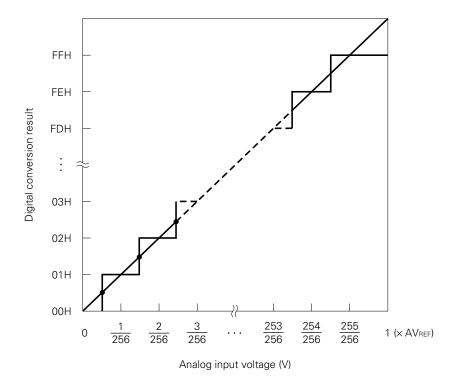

|     | 4.10   | A/D CO                             | NVERTER                                    | 117 |  |  |  |

|     | 4.11   | BIT SEC                            | UENTIAL BUFFER                             | 124 |  |  |  |

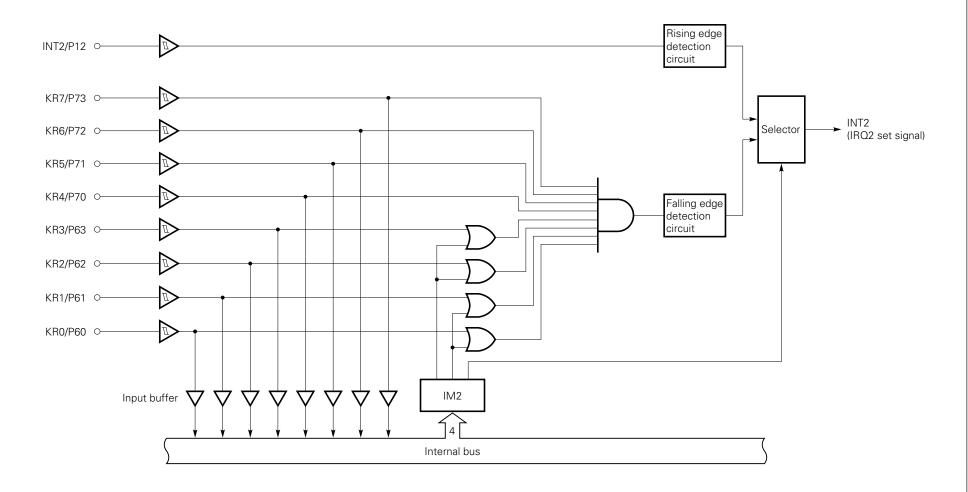

| 5.  | INTEF  | RUPT F                             |                                            | 125 |  |  |  |

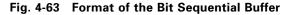

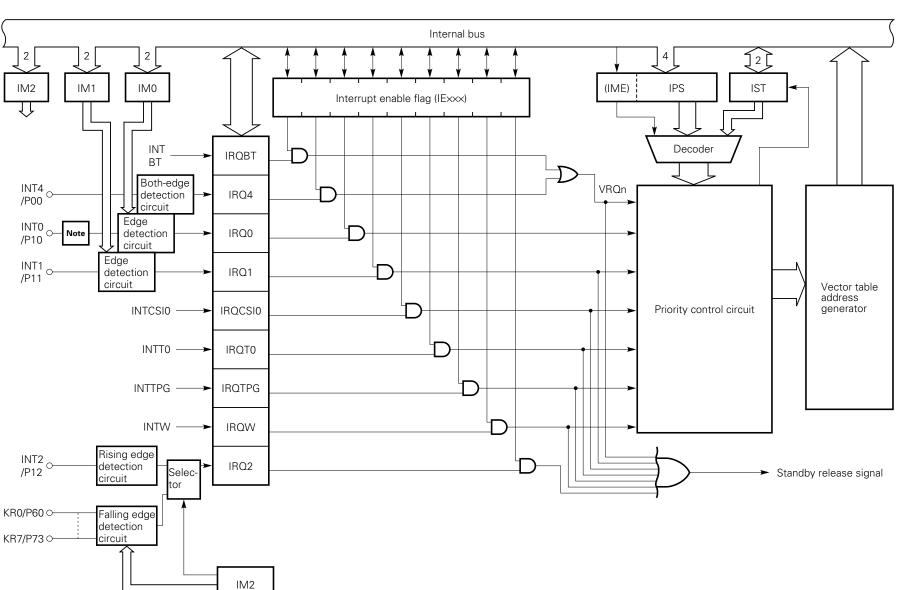

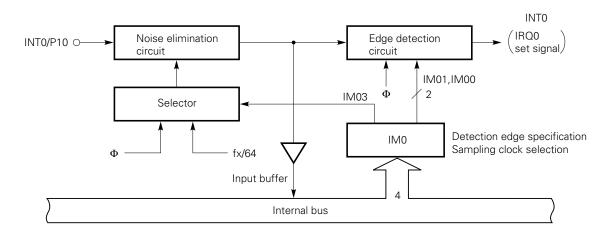

|     | 5.1    | CONFIG                             | URATION OF THE INTERRUPT CONTROL CIRCUIT   | 125 |  |  |  |

|     | 5.2    | HARDW                              | ARE OF THE INTERRUPT CONTROL CIRCUIT       | 127 |  |  |  |

|     | 5.3    | INTERR                             | UPT SEQUENCE                               | 134 |  |  |  |

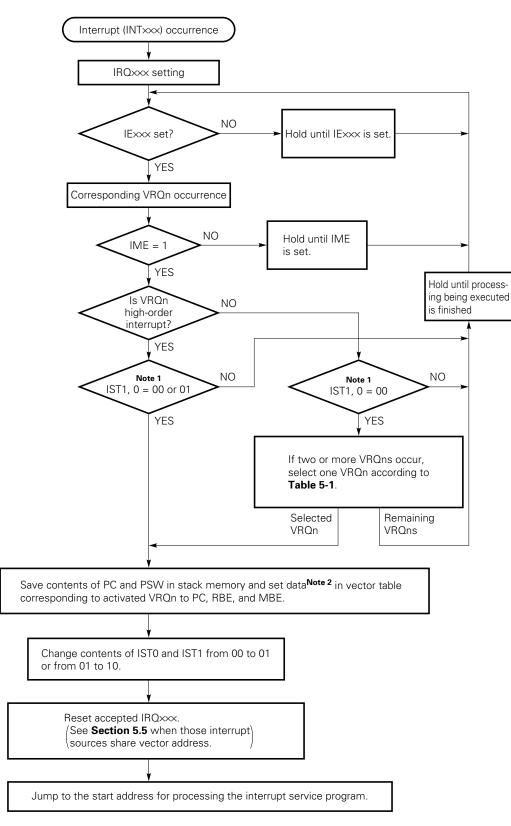

|     | 5.4    | MULTIP                             | LE INTERRUPT PROCESSING CONTROL            | 135 |  |  |  |

|     | 5.5    | VECTOR                             | R ADDRESS SHARE INTERRUPT PROCESSING       | 137 |  |  |  |

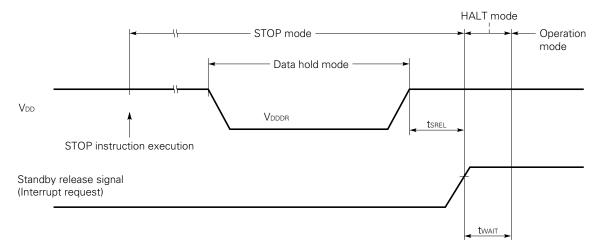

| 6.  | STAN   | DBY FU                             |                                            | 138 |  |  |  |

|     | 6.1    | SETTIN                             | G OF STANDBY MODES AND OPERATION STATUSES  | 138 |  |  |  |

|     | 6.2    | RELEAS                             | E OF THE STANDBY MODES                     | 139 |  |  |  |

|     | 6.3    | OPERAT                             | TION AFTER A STANDBY MODE IS RELEASED      | 141 |  |  |  |

| 7.  | RESE   | T FUNC                             | TION                                       | 142 |  |  |  |

| 8.  | INSTR  | RUCTIO                             | N SET                                      | 144 |  |  |  |

|     | 8.1    | μ <b>PD755</b>                     | 17(A) INSTRUCTIONS                         | 144 |  |  |  |

|     | 8.2    | INSTRU                             | CTION SET AND ITS OPERATION                | 147 |  |  |  |

|     | 8.3    | INSTRU                             | CTION CODES OF EACH INSTRUCTION            | 156 |  |  |  |

| 9.  | ELEC   |                                    | CHARACTERISTICS                            | 162 |  |  |  |

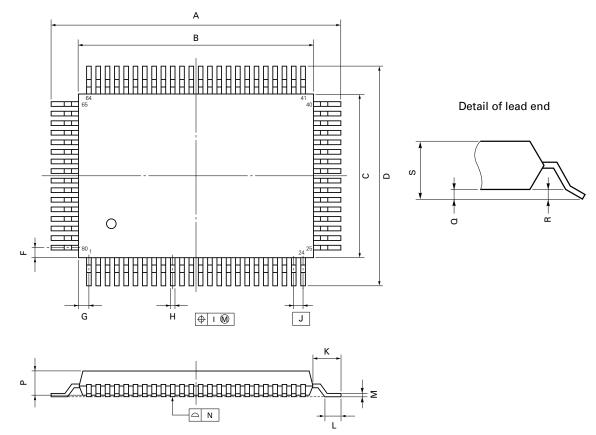

| 10. | РАСК   | AGE DI                             | MENSIONS                                   | 174 |  |  |  |

| 11. | RECO   | MMEND                              | DED SOLDERING CONDITIONS                   | 175 |  |  |  |

| API | PENDI  | KA SE                              | RIES PRODUCT FUNCTIONS                     | 176 |  |  |  |

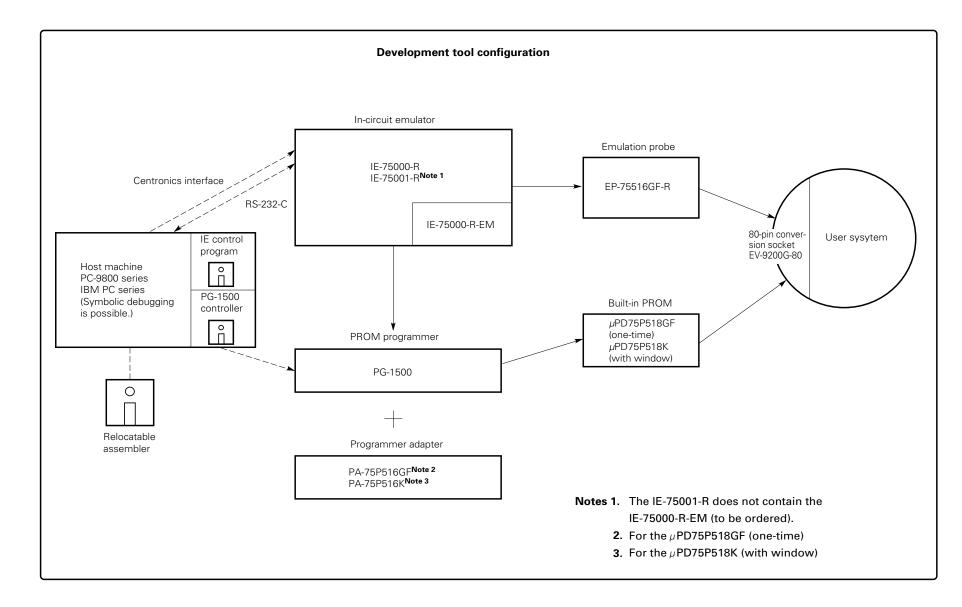

| API | PENDIX | K B DE                             | EVELOPMENT TOOLS                           | 177 |  |  |  |

#### **1. PIN FUNCTIONS**

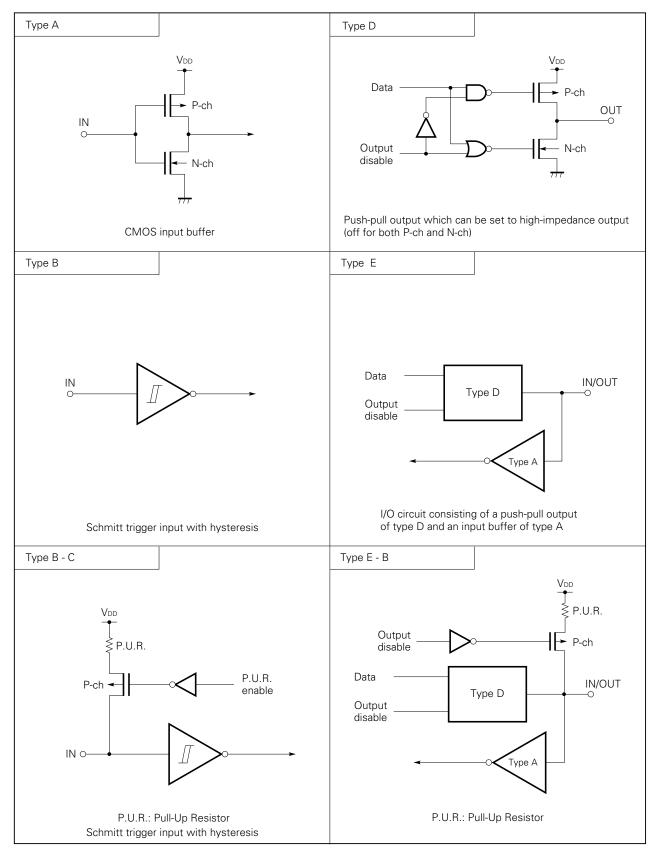

#### 1.1 PORT PINS (1/2)

| Pin name              | I/O | Also<br>used as | Function                                                                                                                                                     | 8-bit I/O | When reset                                                                     | I/O <sup>Note 1</sup><br>circuit<br>type |

|-----------------------|-----|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------------------------------------------------------------------------------|------------------------------------------|

| P00                   | I   | INT4            | 4-bit input port (Port 0).                                                                                                                                   | ×         | Input                                                                          | B                                        |

| P01                   |     | SCK0            | For P01 to P03, pull-up resistors can be                                                                                                                     |           |                                                                                | (F) - A                                  |

| P02                   |     | SO0/SB0         | provided by software in units of 3 bits.                                                                                                                     |           |                                                                                | (F) - В                                  |

| P03                   | -   | SI0/SB1         |                                                                                                                                                              |           |                                                                                | ∭- C                                     |

| P10                   | I   | INT0            | With noise elimination function                                                                                                                              | ×         | Input                                                                          | B - C                                    |

| P11                   |     | INT1            | 4-bit input port (Port 1).                                                                                                                                   |           |                                                                                |                                          |

| P12                   |     | INT2            | Pull-up resistors can be provided by software                                                                                                                |           |                                                                                |                                          |

| P13                   | ]   | TI0             | in units of 4 bits.                                                                                                                                          |           |                                                                                |                                          |

| P20                   | I/O | PTO0            | 4-bit I/O port (Port 2).                                                                                                                                     | ×         | Input                                                                          | E - B                                    |

| P21                   |     | -               | Pull-up resistors can be provided by software                                                                                                                |           |                                                                                |                                          |

| P22                   | -   | PCL             | in units of 4 bits.                                                                                                                                          |           |                                                                                |                                          |

| P23                   |     | BUZ             |                                                                                                                                                              |           |                                                                                |                                          |

| P30 <sup>Note 2</sup> | I/O | -               | Programmable 4-bit I/O port (Port 3).                                                                                                                        | ×         | Input                                                                          | E - C                                    |

| P31 <sup>Note 2</sup> | -   | -               | Input/output can be specified bit by bit.                                                                                                                    |           |                                                                                |                                          |

| P32 <sup>Note 2</sup> |     | -               | Pull-up resistors can be provided by software<br>in units of 4 bits.                                                                                         |           |                                                                                |                                          |

| P33Note 2             | -   | -               |                                                                                                                                                              |           |                                                                                |                                          |

| P40-P43Note 2         | I/O | _               | N-ch open-drain 4-bit I/O port (Port 4).<br>A pull-up resistor can be provided bit by bit<br>(mask option).<br>Withstand voltage is 10 V in open-drain mode. |           | High level<br>(when a pull-up<br>resistor is<br>provided) or<br>high impedance | М                                        |

| P50-P53Note 2         | I/O | _               | N-ch open-drain 4-bit I/O port (Port 5).<br>A pull-up resistor can be provided bit by bit<br>(mask option).<br>Withstand voltage is 10 V in open-drain mode. |           | High level<br>(when a pull-up<br>resistor is<br>provided) or<br>high impedance | М                                        |

| P60                   | I/O | KR0             | Programmable 4-bit I/O port (Port 6).                                                                                                                        | О         | Input                                                                          | (F) - C                                  |

| P61                   |     | KR1             | Input/output can be specified bit by bit.                                                                                                                    |           |                                                                                |                                          |

| P62                   |     | KR2             | Pull-up resistors can be provided by software<br>in units of 4 bits.                                                                                         |           |                                                                                |                                          |

| P63                   |     | KR3             |                                                                                                                                                              |           |                                                                                |                                          |

| P70                   | I/O | KR4             | 4-bit I/O port (Port 7).                                                                                                                                     |           | Input                                                                          | (F) - A                                  |

| P71                   |     | KR5             | Pull-up resistors can be provided by software                                                                                                                |           |                                                                                |                                          |

| P72                   |     | KR6             | in units of 4 bits.                                                                                                                                          |           |                                                                                |                                          |

| P73                   |     | KR7             |                                                                                                                                                              |           |                                                                                |                                          |

Notes 1. The circuits enclosed in circles have a Schmitt-triggered input.

2. An LED can be driven directly.

#### 1.1 PORT PINS (2/2)

| Pin name  | I/O | Also<br>used as | Function                                                                                                                                                      | 8-bit I/O | When reset                                                                      | I/O <sup>Note</sup><br>circuit<br>type |

|-----------|-----|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------------------------------------------------------------------------------|----------------------------------------|

| P80       | I   | PPO             | 4-bit input port (Port 8).                                                                                                                                    | ×         | Input                                                                           | Е                                      |

| P81       | 1   | SCK1            |                                                                                                                                                               |           |                                                                                 | F                                      |

| P82       |     | SO1             | -                                                                                                                                                             |           |                                                                                 | E                                      |

| P83       |     | SI1             |                                                                                                                                                               |           |                                                                                 | B                                      |

| P90-P93   | I/O | -               | 4-bit I/O port (Port 9).<br>A pull-down resistor can be provided bit by bit<br>(mask option).                                                                 | ×         | Low level (when<br>a pull-down<br>resistor is<br>provided) or<br>high impedance |                                        |

| P100-P103 | I/O | -               | 4-bit I/O port (Port 10)                                                                                                                                      | ×         | Input                                                                           | Е                                      |

| P110-P113 | I/O | -               | 4-bit I/O port (Port 11)                                                                                                                                      |           | Input                                                                           | Е                                      |

| P120-P123 | I/O | -               | N-ch open-drain, 4-bit I/O port (Port 12).<br>Pull-up resistors can be provided bit by bit<br>(mask option).<br>Withstand voltage is 10 V in open-drain mode. | ×         | High level<br>(when a pull-up<br>resistor is<br>provided) or<br>high impedance  | М                                      |

| P130-P133 | I/O | _               | N-ch open-drain, 4-bit I/O port (Port 13).<br>Pull-up resistors can be provided bit by bit<br>(mask option).<br>Withstand voltage is 10 V in open-drain mode. | ×         | High level<br>(when a pull-up<br>resistor is<br>provided) or<br>high impedance  | М                                      |

| P140-P143 | I/O | -               | N-ch open-drain, 4-bit I/O port (Port 14).<br>Pull-up resistors can be provided bit by bit<br>(mask option).<br>Withstand voltage is 10 V in open-drain mode. | ×         | High level<br>(when a pull-up<br>resistor is<br>provided) or<br>high impedance  | М                                      |

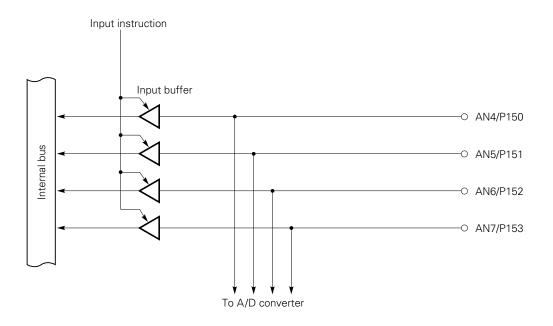

| P150-P153 | I   | AN4-AN7         | 4-bit input port (Port 15)                                                                                                                                    | ×         | Input                                                                           | Y - A                                  |

Note The circuits enclosed in circles have a Schmitt-triggered input.

#### 1.2 NON-PORT PINS

| Pin name | I/O | Also<br>used as | Function                                                                                                                                                                          |                  | When reset | I/O <sup>Note 1</sup><br>circuit<br>type |

|----------|-----|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------|------------------------------------------|

| T10      | I   | P13             | External event pulse input pin for the timer/                                                                                                                                     | event counter    | -          | B- C                                     |

| PTO0     | 0   | P20             | Timer/event counter output pin                                                                                                                                                    |                  | Input      | E - B                                    |

| PCL      | 0   | P22             | Clock output pin                                                                                                                                                                  |                  | Input      | E - B                                    |

| BUZ      | 0   | P23             | Fixed frequency output pin (for buzzer or sy trimming)                                                                                                                            | stem clock       | Input      | E - B                                    |

| SCK0     | I/O | P01             | Serial clock I/O pin                                                                                                                                                              |                  | Input      | (F)- A                                   |

| SO0/SB0  | I/O | P02             | Serial data output pin or serial bus I/O pin                                                                                                                                      |                  | Input      | (F)- В                                   |

| SI0/SB1  | I/O | P03             | Serial data input pin or serial bus I/O pin                                                                                                                                       |                  | Input      | ∭- C                                     |

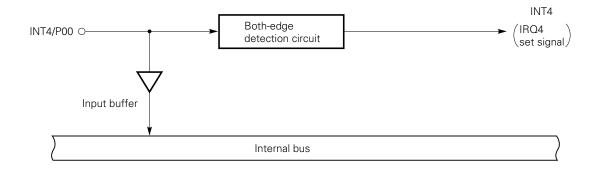

| INT4     | I   | P00             | Edge detection vectored interrupt input pin or falling edge is detected.)                                                                                                         | (Either a rising | -          | B                                        |

| INTO     | I   | P10             | Edge detection vectored interrupt input pin                                                                                                                                       | Synchronous      | -          | ®- C                                     |

| INT1     |     | P11             | (The edge to be detected is selectable.)                                                                                                                                          | Asynchronous     |            |                                          |

| INT2     | I   | P12             | Edge detection testable input pin<br>(An rising edge is detected.)                                                                                                                | Asynchronous     | -          | ₿- C                                     |

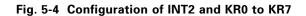

| KR0-KR3  | I   | P60-P63         | Parallel-falling-edge-sensitive testable input                                                                                                                                    | pins             | Input      | (F)- C                                   |

| KR4-KR7  | I   | P70-P73         | Parallel-falling-edge-sensitive testable input                                                                                                                                    | pins             | Input      | (F) - A                                  |

| SCK1     | I/O | P81             | Serial clock I/O pin                                                                                                                                                              |                  | Input      | F                                        |

| S01      | 0   | P82             | Serial data output pin                                                                                                                                                            |                  | Input      | E                                        |

| SI1      | I   | P83             | Serial data input pin                                                                                                                                                             |                  | Input      | B                                        |

| AN0-AN3  | I   | _               | Analog input pins to A/D converter                                                                                                                                                |                  | -          | Y                                        |

| AN4-AN7  |     | P150-P153       |                                                                                                                                                                                   |                  |            | Y - A                                    |

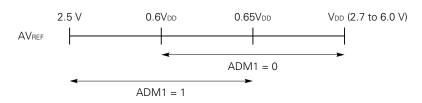

| AVREF    | I   | _               | A/D converter reference voltage input pin                                                                                                                                         |                  | -          | Z                                        |

| AVss     | -   | -               | A/D converter reference GND pin                                                                                                                                                   |                  | -          | _                                        |

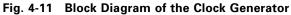

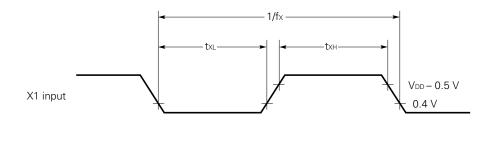

| X1, X2   | I   | _               | Pin for connection to a crystal/ceramic resonator for main<br>system clock generation. When external clock is used, it is<br>input to X1, and its inverted signal is input to X2. |                  | _          | _                                        |

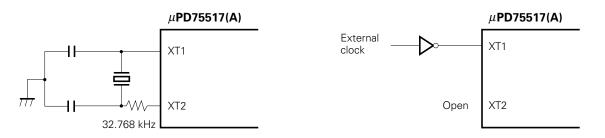

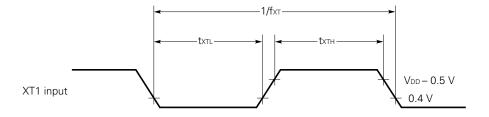

| XT1      | I   | -               | Pin for connection to a crystal resonator for subsystem                                                                                                                           |                  | _          | _                                        |

| XT2      | -   |                 | clock generation. When external clock is used, it is input to XT1, and XT2 is left open.                                                                                          |                  |            |                                          |

| RESET    | I   | _               | System reset input pin                                                                                                                                                            |                  | -          | B                                        |

| PPO      | 0   | P80             | Timer/pulse generator pulse output pin                                                                                                                                            |                  | Input      | E                                        |

| Vdd      | _   | -               | Positive power supply pin                                                                                                                                                         |                  | -          | -                                        |

| Vss      | _   | _               | Ground pin                                                                                                                                                                        |                  | -          | -                                        |

| IC       | -   | -               | Internally connected <sup>Note 2</sup>                                                                                                                                            |                  |            | _                                        |

Notes 1. The circuits enclosed in circles have a Schmitt-triggered input.

2. Be sure to input Vss level to this pin.

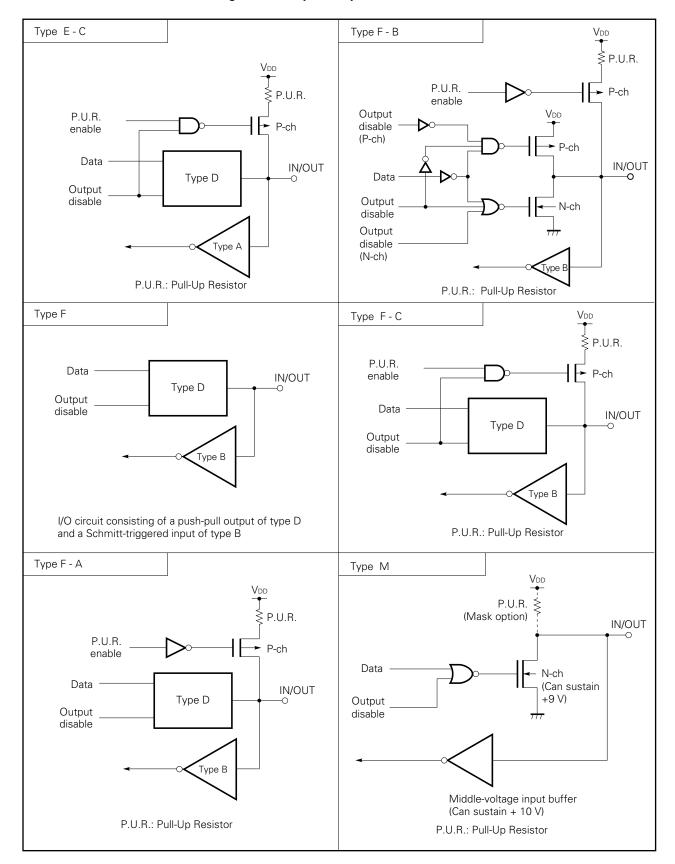

#### **1.3 PIN INPUT/OUTPUT CIRCUITS**

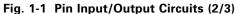

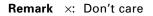

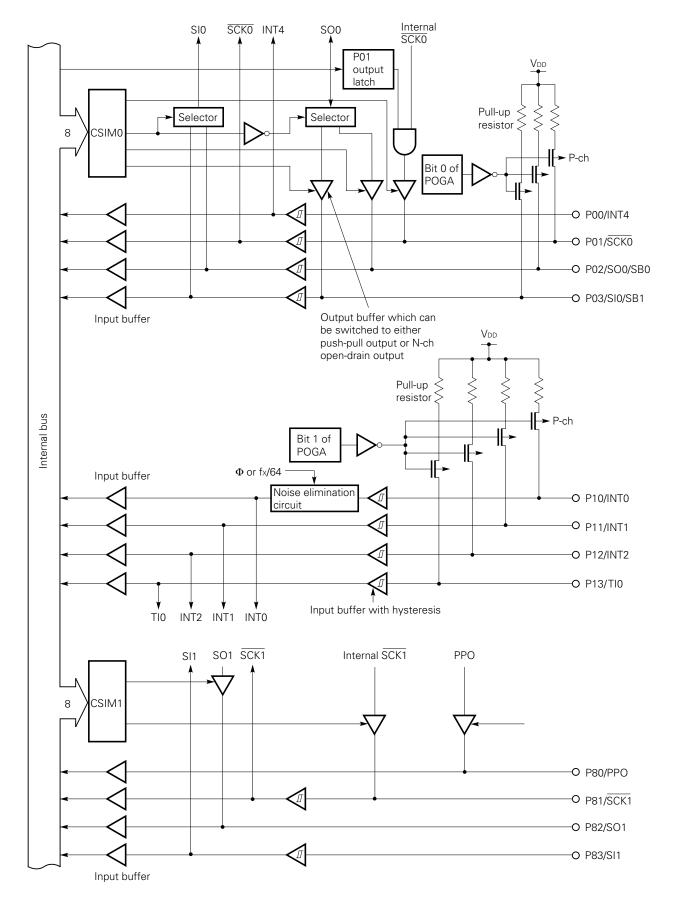

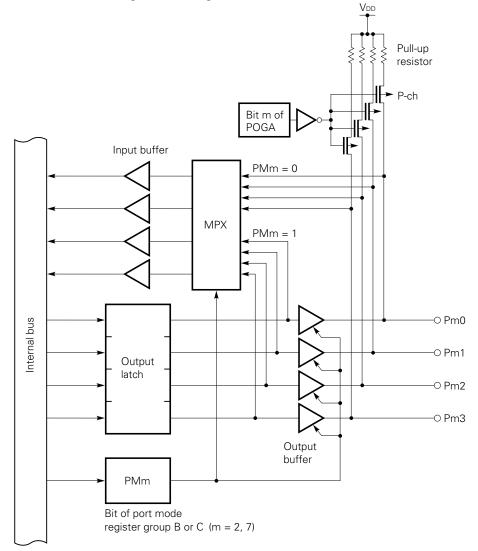

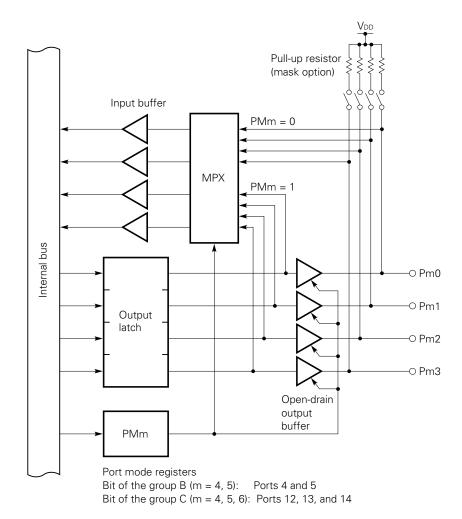

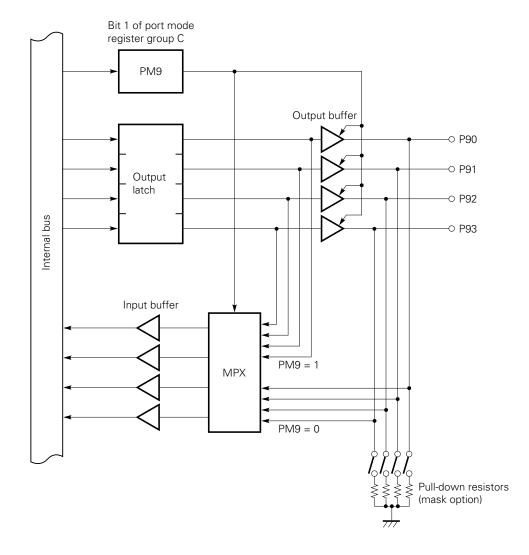

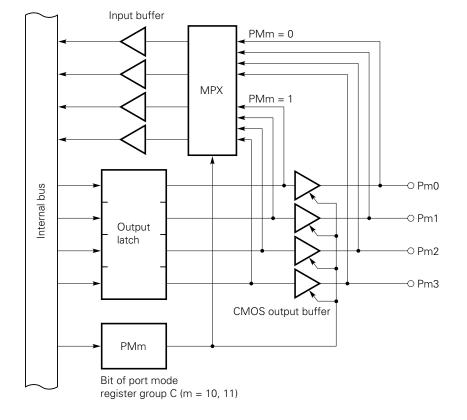

Fig. 1-1 shows the input/output circuit of each  $\mu$ PD75517(A) pin in a simplified manner.

#### Fig. 1-1 Pin Input/Output Circuits (1/3)

Fig. 1-1 Pin Input/Output Circuits (3/3)

#### 1.4 CONNECTION OF UNUSED PINS

| Pin name          | Recommended connection                         |

|-------------------|------------------------------------------------|

| P00/INT4          | To be connected to Vss                         |

| P01/SCK0          | To be connected to Vss or VDD                  |

| P02/SO0/SB0       |                                                |

| P03/SI1/SB1       |                                                |

| P10/INT0-P12/INT2 | To be connected to Vss                         |

| P13/TI0           |                                                |

| P20/PTO0          | Input state : To be connected to Vss or VDD    |

| P21               | Output state: To be left open                  |

| P22/PCL           |                                                |

| P23/BUZ           |                                                |

| P30-P33           |                                                |

| P40-P43           |                                                |

| P50-P53           |                                                |

| P60/KR0-P63/KR3   |                                                |

| P70/KR4-P73/KR7   |                                                |

| P80/PPO           | To be connected to Vss or VDD                  |

| P81/SCK1          |                                                |

| P82/SO1           |                                                |

| P83/SI1           |                                                |

| P90-P93           | Input state $$ : To be connected to Vss or VDD |

| P100-P103         | Output state: To be left open                  |

| P110-P113         |                                                |

| P120-P123         |                                                |

| P130-P133         |                                                |

| P140-P143         |                                                |

| P150/AN4-P153/AN7 | To be connected to Vss                         |

| AN0-AN3           |                                                |

| XT1               | To be connected to Vss or VDD                  |

| XT2               | To be left open                                |

| AVREF             | To be connected to Vss                         |

| AVss              |                                                |

| IC                |                                                |

#### Table 1-1 Recommended Connection of Unused Pins

#### 1.5 SELECTION OF A MASK OPTION

The following mask options are provided for pins.

#### (1) Specification of built-in pull-up and pull-down resistors

| Table 1-2 | Selection | of Pull-Up | and Pull-Down | Resistors  |

|-----------|-----------|------------|---------------|------------|

|           | OCICCUION | or r un op |               | 1103131013 |

| Pin name                                                      | Mask option                                                                                                                                                          |

|---------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P40-P43,<br>P50-P53,<br>P120-P123,<br>P130-P133,<br>P140-P143 | <ol> <li>Pull-up resistors provided</li> <li>(Can be specified bit by bit.)</li> <li>No pull-up resistor provided</li> <li>(Can be specified bit by bit.)</li> </ol> |

| P90-P93                                                       | <ul> <li>Pull-down resistors provided</li> <li>(Can be specified bit by bit.)</li> <li>(Can be specified bit by bit.)</li> </ul>                                     |

#### (2) Specification of built-in feed-back resistors for subsystem clock oscillation

#### Table 1-3 Selection of Feed-Back Resistors

| Pin name | Mask option                                                                                                                                                  |  |  |  |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| XT1, XT2 | <ol> <li>Feed-back resistors provided (when a subsystem clock is used)</li> <li>No feed-back resistors provided (when no subsystem clock is used)</li> </ol> |  |  |  |

# Caution Even if built-in feed-back resistors are provided when no subsystem clock is used, operation is not affected except increased power supply current lbb.

#### 2. ARCHITECTURE AND MEMORY MAP OF THE $\mu$ PD75517(A)

The  $\mu$ PD75517(A) has three architectural features:

- (a) Data memory bank configuration

- (b) General register bank configuration

- (c) Memory-mapped I/O

Each of these features is explained below.

#### 2.1 DATA MEMORY BANK CONFIGURATION AND ADDRESSING MODES

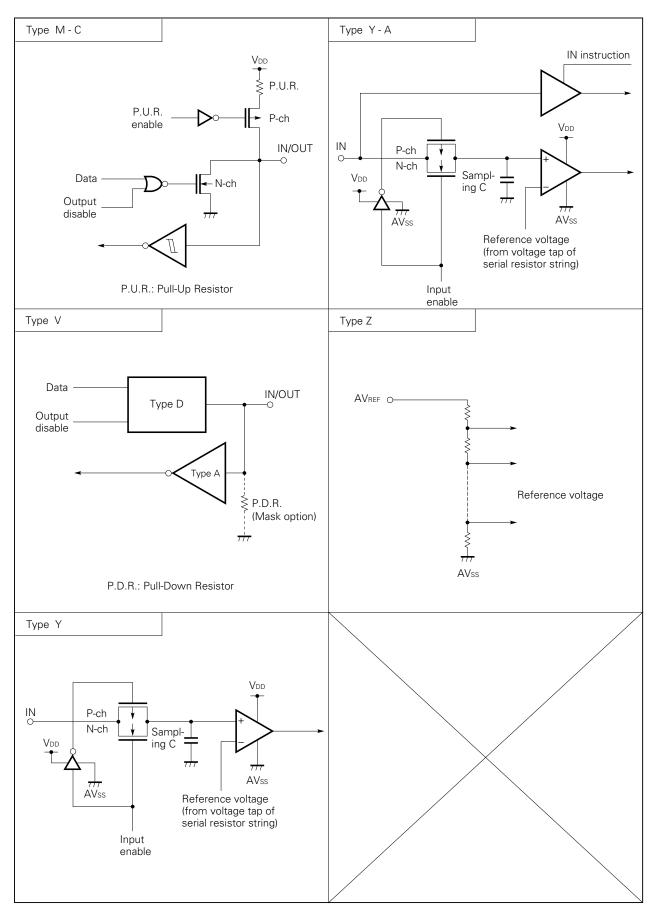

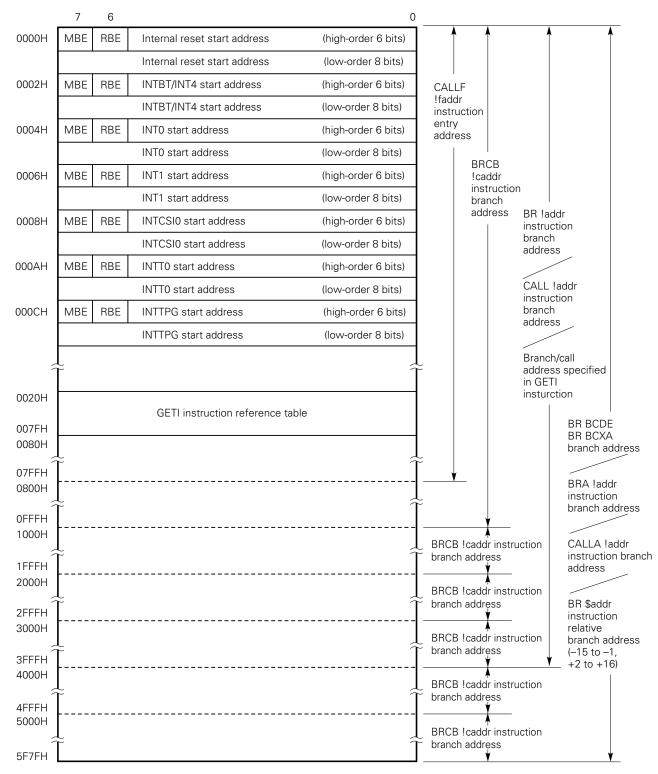

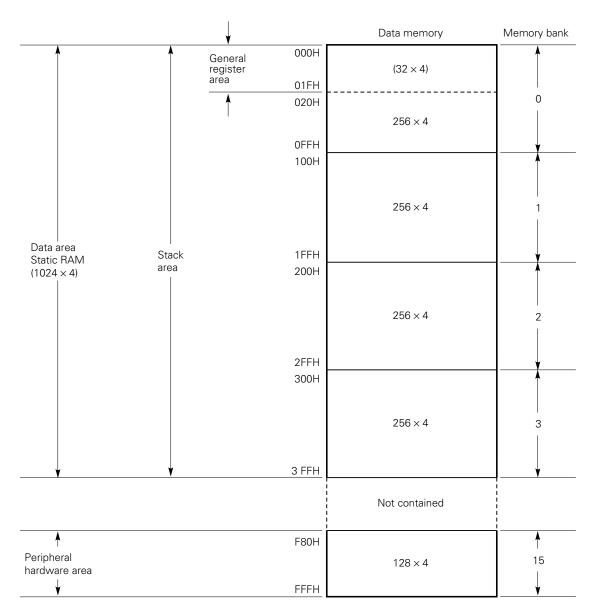

As shown in Fig. 2-1, the data memory space of the  $\mu$ PD75517(A) contains a static RAM (1024 words × 4 bits) at addresses 000H to 3FFH and peripheral hardware (such as I/O ports and timers) at addresses F80H to FFFH. To address a 12-bit address in this data memory space, the  $\mu$ PD75517(A) uses such a memory bank configuration that the low-order eight bits are specified with an instruction directly or indirectly, and the high-order four bits are used to specify a memory bank (MB).

To specify a memory bank (MB), a memory bank enable flag (MBE) and memory bank select register (MBS) are contained, allowing the addressing indicated in Fig. 2-1 and 2-2 and Table 2-1. (The MBS is a register used to select a memory bank, and can be set to 0, 1, 2, 3, or 15. The MBE is a flag used to determine whether a memory bank selected using the MBS register is to be enabled. The MBE is automatically saved or restored at the time of interrupt processing or subroutine processing, so that it can be freely set in interrupt processing and subroutine processing.)

In addressing data memory space, the MBE is usually set to 1 (MBE = 1), and the static RAM in the memory bank specified by the MBS is operated. However, the MBE = 0 mode or the MBE = 1 mode can be selected for each step of program processing for more efficient programming.

|              | Applicable program processing                                                                                                                        |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| MBE = 0 mode | <ul> <li>Interrupt processing</li> <li>Processing that repeats internal hardware and static RAM operations</li> <li>Subroutine processing</li> </ul> |

| MBE = 1 mode | Usual program processing                                                                                                                             |

The MBE and MBS are set as indicated below.

| Example | SET1 MBE | ; MBE $\leftarrow$ 1  |

|---------|----------|-----------------------|

|         | CLR1 MBE | ; MBE $\leftarrow$ 0  |

|         | SEL MB0  | ; MBS $\leftarrow$ 0  |

|         | SEL MB1  | ; MBS $\leftarrow$ 1  |

|         | SEL MB15 | ; MBS $\leftarrow$ 15 |

|         |          |                       |

|                              | Addressing mode                              | mem<br>mem.bit | t           | @H<br>@H + m |             | @DE<br>@DL | Stack<br>address-<br>ing | fmem.bit | pmem.<br>@L |

|------------------------------|----------------------------------------------|----------------|-------------|--------------|-------------|------------|--------------------------|----------|-------------|

|                              | Memory bank enable flag                      |                | ИВЕ<br>= 1  | MBE<br>= 0   | MBE<br>= 1  | Ι          | -                        | -        | _           |

| 000H<br>01FH<br>020H<br>07FH | Data area<br>Static RAM<br>(memory bank 0)   |                | ЛВS<br>= 0  |              | MBS<br>= 0  |            | SBS<br>= 0               |          |             |

| 0FFH<br>100H                 |                                              |                |             |              |             |            |                          |          |             |

|                              | Data area<br>Static RAM<br>(memory bank 1)   |                | ABS<br>= 1  |              | MBS<br>= 1  |            | SBS<br>= 1               |          |             |

| 1FFH<br>200H                 | Stack area                                   |                |             |              |             |            |                          |          |             |

|                              | Static RAM<br>(memory bank 2)                |                | /BS<br>= 2  |              | MBS<br>= 2  |            | SBS<br>= 2               |          |             |

| 2FFH<br>300H                 | Data area                                    |                |             |              |             |            |                          |          |             |

|                              | Static RAM<br>(memory bank 3)                |                | ABS<br>= 3  |              | MBS<br>= 3  |            | SBS<br>= 3               |          |             |

| 3FFH                         | ¥ ¥<br>Not contained                         |                |             |              |             |            |                          |          |             |

| F80H                         | <b>A</b>                                     |                |             |              |             |            |                          |          |             |

| FB0H<br>FBFH<br>FC0H         | Peripheral hardware area<br>(memory bank 15) |                | 1BS<br>= 15 |              | MBS<br>= 15 |            |                          | ~~~~~    |             |

| FF0H<br>FFFH                 | , v                                          |                |             |              |             |            |                          |          |             |

Fig. 2-1 Data Memory Organization and Addressing Range of Each Addressing Mode

Remark —: Don't care

| Addressing mode                       | Representation<br>format | Specified address                                                                                                                                                                              |

|---------------------------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1-bit direct addressing               | mem.bit                  | Bit specified by bit at the address specified by MB and mem. In this case:<br>When MBE = 0 and mem = 00H-7FH, MB = 0<br>When MBE = 0 and mem = 80H-FFH, MB = 15<br>When MBE = 1, MB = MBS      |

| 4-bit direct addressing               | mem                      | Address specified by MB and mem. In this case:<br>When MBE = 0 and mem = 00H-7FH, MB = 0<br>When MBE = 0 and mem = 80H-FFH, MB = 15<br>When MBE = 1, MB = MBS                                  |

| 8-bit direct addressing               |                          | Address specified by MB and mem (mem: even address). In this case:<br>When MBE = 0 and mem = 00H-7FH, MB = 0<br>When MBE = 0 and mem = 80H-FFH, MB = 15<br>When MBE = 1, MB = MBS              |

| 4-bit register indirect<br>addressing | @HL<br>@HL+<br>@HL–      | Address specified by MB and HL.<br>In this case, MB = MBE•MBS                                                                                                                                  |

|                                       | @DE                      | Address specified by DE in memory bank 0                                                                                                                                                       |

|                                       | @DL                      | Address specified by DL in memory bank 0                                                                                                                                                       |

| 8-bit register indirect<br>addressing | @HL                      | Address specified by MB and HL (with the L register holding an even number).<br>In this case, MB = MBE•MBS                                                                                     |

| Bit manipulation<br>addressing        | fmem.bit                 | Bit specified by bit at the address specified by fmem. In this case:<br>fmem = FB0H-FBFH (interrupt-related hardware)<br>fmem = FF0H-FFFH (I/O port)                                           |

|                                       | pmem.@L                  | Bit specified by the low-order 2 bits of the L register at the address specified by the high-order 10 bits of pmem and the high-order 2 bits of the L register. In this case, pmem = FC0H-FFFH |

|                                       | @H+mem.bit               | Bit specified by bit at the address specified by MB, H, and the low-order 4 bits of mem.<br>In this case, MB = MBE•MBS                                                                         |

| Stack addressing                      | _                        | Address specified by SP in memory bank 0, 1, 2, and 3 selected by SBS                                                                                                                          |

Table 2-1 Addressing Modes

As summarized in Table 2-1, the  $\mu$ PD75517(A) allows both direct and indirect addressing in data memory manipulation for 1-bit data, 4-bit data, and 8-bit data, so that very efficient and simple programming can be performed.

Examples 1. The 8-bit data of port 4 and port 5 are transferred to addresses 20H and 21H.

| CLR1 | MBE       | ; MBE $\leftarrow$ 0         |

|------|-----------|------------------------------|

| IN   | XA, PORT4 | ; XA $\leftarrow$ Ports 5, 4 |

| MOV  | 20H, XA   | ; (21H, 20H) $\leftarrow$ XA |

2. When P02 is 0, P33 is set.

| SKT  | PORT0.2 | ; Skip if bit 2 of port 0 is 1 |

|------|---------|--------------------------------|

| SET1 | PORT3.3 | ; Set bit 3 of port 3          |

3. A different value is output to port 6, depending on the status of P10.

| SKF | PORT1.0   | ; Skip if bit 0 of port 1 is 0         |

|-----|-----------|----------------------------------------|

| MOV | A, #1010B | ; A $\leftarrow$ 1010B (string effect) |

| MOV | A, #0101B | ; A $\leftarrow$ 0101B (string effect) |

| SEL | MB15      | ; or CLR1 MBE                          |

| OUT | PORT6, A  | ; Port 6 ← A                           |

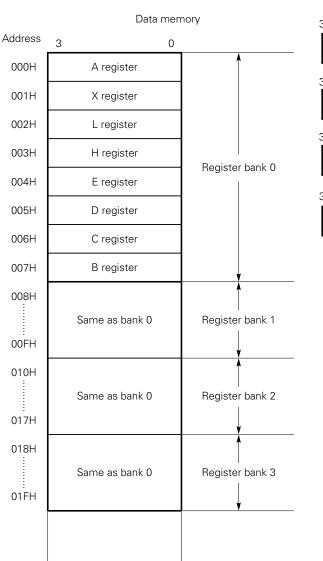

#### 2.2 GENERAL REGISTER BANK CONFIGURATION

The  $\mu$ PD75517(A) contains four register banks, each consisting of eight general registers: X, A, B, C, D, E, H, and L. These registers are mapped to addresses 00H to 1FH in memory bank 0 of the data memory. (See **Fig. 2-3**.) To specify a general register bank, a register bank enable flag (RBE) and a register bank select register (RBS) are contained. The RBS is a register used to select a register bank, and the RBE is a flag used to determine whether a register bank selected using the RBS is to be enabled. The register bank (RB) enabled at instruction execution is determined as RB = RBE•RBS

As indicated in Table 2-2, the  $\mu$ PD75517(A) enables the user to create programs in a very efficient manner by selecting a register bank from the four register banks, depending on whether the processing is normal processing or interrupt processing. (The RBE is automatically saved and set at the time of interrupt processing, and is automatically restored upon completion of interrupt processing.)

Table 2-2 Example of the Use of Register Banks with Normal Routines and Interrupt Routines

| Normal processing                              | Use register banks 2 and 3 with RBE = 1.                                                     |

|------------------------------------------------|----------------------------------------------------------------------------------------------|

| Single interrupt processing                    | Use register bank 0 with RBE = 0.                                                            |

| Dual interrupt processing                      | Use register bank 1 with RBE = 1.<br>(In this case, the RBS needs to be saved and restored.) |

| Multiple (triple or more) interrupt processing | Save the registers with PUSH or POP.                                                         |

The RBE and RBS are set as indicated below.

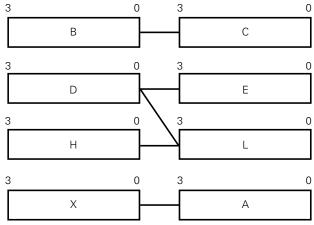

The general registers allow transfers, comparisons, arithmetic/logical operations, and increments and decrements not only on a 4-bit basis, but also on an 8-bit basis with the XA, HL, DE, and BC register pairs. In this case, the register pairs of the register bank that has the inverted value of bit 0 of a register bank specified by RBE•RBS can be specified as XA', HL', DE', and BC', thus providing eight 8-bit registers. (See **Fig. 2-4**.)

| Example | SET1 | RBE      | ; RBE ← 1                                                |

|---------|------|----------|----------------------------------------------------------|

|         | SEL  | RB2      | ; $RBS \leftarrow 2$                                     |

|         | MOV  | XA, #18H | ; XA ← 18H                                               |

|         | ADDS | HL, XA   | ; $HL \leftarrow HL+XA$                                  |

|         | SUBS | HL', XA  | ; HL' $\leftarrow$ HL'–XA (HL' is HL of register bank 3) |

|         | INCS | HL       | ; $HL \leftarrow HL+1$                                   |

|         | MOV  | XA, #00H | ; XA $\leftarrow$ 00H (string effect)                    |

|         | MOV  | XA, #10H | ; XA $\leftarrow$ 10H (string effect)                    |

| x | 01H | А | 00H | <b>A</b>        |

|---|-----|---|-----|-----------------|

| н | 03H | L | 02H | Register bank 0 |

| D | 05H | E | 04H | (RBE·RBS = 0)   |

| В | 07H | С | 06H | <b></b>         |

| × | 09H | А | 08H | Î               |

| н | 0BH | L | 0AH | Register bank 1 |

| D | 0DH | E | 0CH | (RBE·RBS = 1)   |

| В | 0FH | С | 0EH |                 |

| Х | 11H | А | 10H | Â               |

| н | 13H | L | 12H | Register bank 2 |

| D | 15H | E | 14H | (RBE·RBS = 2)   |

| В | 17H | С | 16H | <b>↓</b>        |

| х | 19H | А | 18H | Â               |

| н | 1BH | L | 1AH | Register bank 3 |

| D | 1DH | E | 1CH | (RBE·RBS = 3)   |

| В | 1FH | С | 1EH |                 |

#### Fig. 2-3 General Register Configuration (4-Bit Processing)

| ХА  | 00H |                   | ХА' | 00H |                   |     |

|-----|-----|-------------------|-----|-----|-------------------|-----|

| HL  | 02H | -                 | HL' | 02H |                   |     |

| DE  | 04H |                   |     |     | DE'               | 04H |

| BC  | 06H | When RBE·RBS      | BC' | 06H | │<br>When RBE·RBS |     |

| XA' | 08H | = 0               | ХА  | 08H | = 1               |     |

| HL' | 0AH |                   | HL  | 0AH |                   |     |

| DE' | 0CH |                   | DE  | 0CH |                   |     |

| BC' | 0EH |                   | BC  | 0EH |                   |     |

|     |     |                   |     |     |                   |     |

| XA  | 10H |                   | ХА' | 10H |                   |     |

| HL  | 12H |                   | HL' | 12H |                   |     |

| DE  | 14H |                   | DE' | 14H |                   |     |

| ВС  | 16H | │<br>When RBE·RBS | BC' | 16H | │<br>When RBE·RBS |     |

| ХА' | 18H | = 2               | ХА  | 18H | = 3               |     |

| HĽ' | 1AH |                   | HL  | 1AH |                   |     |

| DE' | 1CH |                   | DE  | 1CH |                   |     |

| BC' | 1EH |                   | BC  | 1EH |                   |     |

#### Fig. 2-4 General Register Configuration (8-Bit Processing)

#### 2.3 MEMORY-MAPPED I/O

The  $\mu$ PD75517(A) employs memory-mapped I/O, which maps peripheral hardware such as timers and I/O ports to addresses F80H to FFFH in the data memory space as shown in Fig. 2-1. This means that there is no particular instruction to control peripheral hardware, but all peripheral hardware is controlled using memory manipulation instructions. (Some mnemonics for hardware control are available to make programs readable.)

To manipulate peripheral hardware, the addressing modes listed in Table 2-3 can be used.

| Table 2-3 | Addressing Modes Applicable to Peripheral Hardware |

|-----------|----------------------------------------------------|

|-----------|----------------------------------------------------|

|                    | Applicable addressing mode                                                                                                | Applicable hardware                                  |  |

|--------------------|---------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|--|

| Bit manipulation   | Direct addressing mode specifying mem.bit with MBE = 0 or (MBE = 1, MBS = 15)                                             | All hardware allowing bit manipulation               |  |

|                    | Direct addressing mode specifying fmem.bit regardless of MBE and MBS setting                                              | IST0, IST1, MBE, RBE, EOT,<br>IExxx, IRQxxx, PORTn.x |  |

|                    | Indirect addressing mode specifying pmem.@L regardless of MBE and MBS setting                                             | BSBn.×<br>PORTn.×                                    |  |

| 4-bit manipulation | Direct addressing mode specifying mem with MBE = 0 or (MBE = 1, MBS = 15)                                                 | All hardware allowing 4-bit manipulation             |  |

|                    | Register indirect addressing mode specifying @HL with (MBE = 1, MBS = 15)                                                 |                                                      |  |

| 8-bit manipulation | Direct addressing mode specifying mem (even address) with MBE = 0 or (MBE = 1, MBS = 15)                                  | All hardware allowing 8-bit manipulation addressing  |  |

|                    | Register indirect addressing mode specifying @HL (with the L register containing an even number) with (MBE = 1, MBS = 15) |                                                      |  |

Fig. 2-5 summarizes the I/O map of the  $\mu$ PD75517(A). The items in Fig. 2-5 have the following meanings:

- Symbol: Name representing the address of incorporated hardware, which can be coded in the operand field of an instruction

- R/W : Indicates whether the hardware allows read/write operation.

R/W: Both read and write operations possible

- R : Read only

- W : Write only

- Number of manipulatable bits:

- Indicates the number of bits that can be processed in hardware manipulation

- ○: Bits can be manipulated on an indicated bit (1-, 4-, or 8-bit) basis.

- $\triangle$ : Particular bits can be manipulated. For these bits, see Remarks.

- : Bits cannot be manipulated on an indicated bit (1-, 4-, or 8-bit) basis.

- Bit manipulation addressing:

- Bit manipulation addressing applicable in hardware bit manipulation

| Address   |                                          | Hardware na                                                         | ame (sy | /mbol) |    | R/W     |       | ber of bits         |        | Bit<br>manipulation | Remarks                                 |  |

|-----------|------------------------------------------|---------------------------------------------------------------------|---------|--------|----|---------|-------|---------------------|--------|---------------------|-----------------------------------------|--|

| , laarooo | b3                                       | b2                                                                  | b       | 1      | b0 | 11/ V V | 1 bit | 4 bits              | 8 bits | addressing          |                                         |  |

| F80H      | Stack point                              |                                                                     | R/W     | -      | _  | 0       |       | Bit 0 is fixed to 0 |        |                     |                                         |  |

|           |                                          |                                                                     |         |        |    |         |       |                     |        |                     |                                         |  |

| F82H      | Register ba<br>(RBS)                     | Register bank select register<br>(RBS) Bank select<br>register (BS) |         |        |    |         |       | 0                   |        |                     | Note 1                                  |  |

| F83H      | Memory bank select register<br>(MBS)     |                                                                     |         |        |    | R       | -     | 0                   |        |                     | Note I                                  |  |

| F84H      | Stack bank select register (SBS)         |                                                                     |         |        |    | R/W     | -     | 0                   | -      |                     | Bits 3 and 2<br>are always<br>set to 0. |  |

| F85H      | Basic interval timer mode register (BTM) |                                                                     |         |        |    | W       |       | 0                   | -      | mem.bit             | Only bit 3 can<br>be manipulat-<br>ed   |  |

| F86H      | Basic interval timer (BT)                |                                                                     |         |        |    | R       | _     | _                   | 0      |                     |                                         |  |

#### Fig. 2-5 µPD75517(A) I/O Map (1/4)

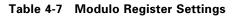

| F90H | Timer pulse generator (TPGM)                 | W   | $\bigtriangleup$ | - | 0 | mem.bit | Only bit 3<br>allows bit<br>manipulation. |

|------|----------------------------------------------|-----|------------------|---|---|---------|-------------------------------------------|

|      |                                              |     | -                | - |   |         |                                           |

| F94H | Timer/pulse generator modulo register (MODL) | R/W | -                | - | 0 |         |                                           |

| F96H | Timer/pulse generator modulo register (MODH) | R/W | _                | _ | 0 |         |                                           |

| F98H | Clock mode register (M/M)                    | _   | _                | - |   |         |                                           |

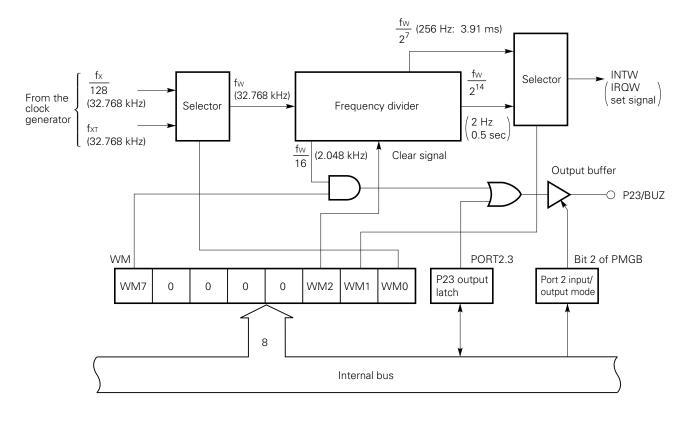

|      | Clock mode register (WM)                     | W   | _                | - | 0 |         |                                           |

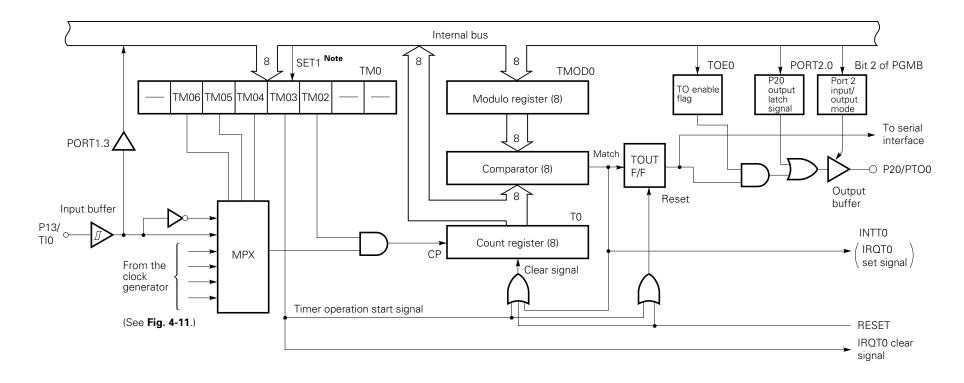

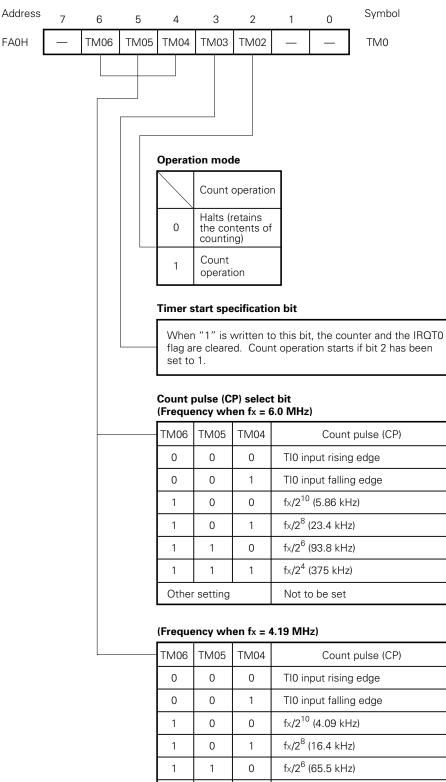

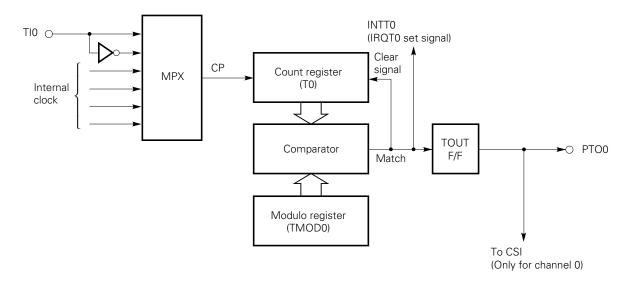

| FA0H | Timer/event counter 0 mode register (TM0)     | W | $\bigtriangleup$ | - | 0 | mem.bit | Only bit 3 can<br>be manipulat-<br>ed |

|------|-----------------------------------------------|---|------------------|---|---|---------|---------------------------------------|

|      |                                               |   | Ι                | - |   |         |                                       |

| FA2H | TOE0Note 2                                    | W | 0                | - | - | mem.bit |                                       |

| FA4H | Timer/event counter 0 count register (T0)     | R | _                | _ | 0 |         |                                       |

| FA6H | Timer/event counter 0 modulo register (TMOD0) | W | _                | _ | 0 |         |                                       |

#### Notes 1. Can be operated separately as the RBS and MBS during 4-bit manipulation.

Can also be operated as the BS during 8-bit manipulation.

2. TOE0: Timer/event counter 0 output enable flag (W)

| Address   |             | Hardware na      | ime (symbol)  |         | R/W   |       | nber of bit<br>be manipu |        | Bit<br>manipulation               | Remarks                                  |

|-----------|-------------|------------------|---------------|---------|-------|-------|--------------------------|--------|-----------------------------------|------------------------------------------|

| / 1001000 | b3          | b2               | b1            | b0      | 11/00 | 1 bit | 4 bits                   | 8 bits | addressing                        | Hernarks                                 |

| FB0H      | IST1        | IST0             | MBE           | RBE     | R/W   | 0     | 0                        | 0      |                                   |                                          |

|           | Program st  | atus word (P     | SW)           |         | R     | _     | _                        |        | for one hit                       |                                          |

| FB2H      | Interrupt p | riority select r | egister (IPS) |         | W     | Ι     | 0                        | _      | fmem.bit                          | Manipulated<br>with EI/DI<br>instruction |

| FB3H      | Processor   | clock control    | register (PCC | )       | W     | -     | 0                        |        |                                   |                                          |

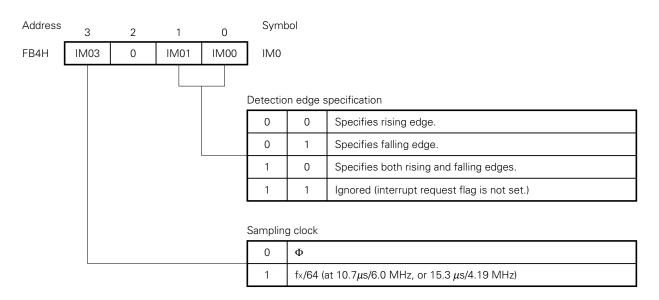

| FB4H      | INT0 mode   | e register (IMC  | ))            |         | W     | I     | 0                        |        |                                   | Bit 2 is fixed to 0                      |

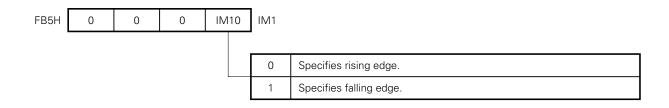

| FB5H      | INT1 mode   | e resistor (IM1  | )             |         | W     | -     | 0                        | _      |                                   | Bits 3, 2, and<br>1 are fixed to<br>0    |

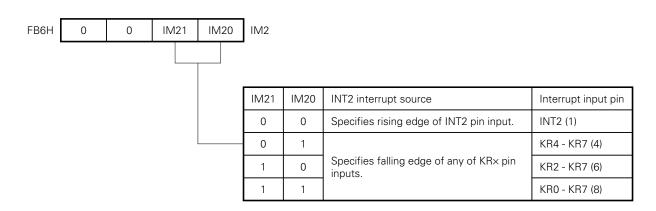

| FB6H      | INT2 mode   | e register (IM2  |               | W       | -     | 0     |                          |        | Bits 3 and 2<br>are fixed to<br>0 |                                          |

| FB7H      | System clo  | ock control reg  | gister (SCC)  |         | W     | 0     | -                        |        |                                   | Bits 2 and 1<br>are fixed to 0           |

| FB8H      | IE4         | IRQ4             | IEBT          | IRQBT   | R/W   | 0     | 0                        |        |                                   |                                          |

| FB9H      |             |                  |               | EOT     | R/W   | 0     | 0                        | _      |                                   |                                          |

| FBAH      |             |                  | IEW           | IRQW    | R/W   | 0     | 0                        | _      |                                   |                                          |

| FBBH      |             |                  | IETPG         | IRQTPG  | R/W   | 0     | _                        |        | fmem.bit                          |                                          |

| FBCH      |             |                  | IET0          | IRQT0   | R/W   | 0     | 0                        | _      | intern.bit                        |                                          |

| FBDH      |             |                  | IECSI0        | IRQCSI0 | R/W   | 0     | 0                        |        |                                   |                                          |

| FBEH      | IE1         | IRQ1             | IEO           | IRQ0    | R/W   | 0     | 0                        | _      |                                   |                                          |

| FBFH      |             |                  | IE2           | IRQ2    | R/W   | 0     | 0                        |        |                                   |                                          |

Fig. 2-5 μPD75517(A) I/O Map (2/4)

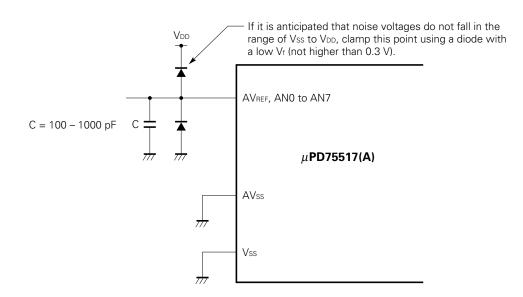

| FC0H | Bit sequential buffer 0 (BSB0)           | R/W | 0                | 0 |   |                    |                                           |

|------|------------------------------------------|-----|------------------|---|---|--------------------|-------------------------------------------|

| FC1H | Bit sequential buffer 1 (BSB1)           | R/W | 0                | 0 | 0 | mem.bit<br>pmem.@L |                                           |

| FC2H | Bit sequential buffer 2 (BSB2)           | R/W | 0                | 0 |   |                    |                                           |

| FC3H | Bit sequential buffer 3 (BSB3)           |     | 0                | 0 |   |                    |                                           |

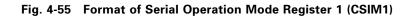

| FC8H | Serial operation mode register 1 (CSIM1) |     | -                | - |   |                    |                                           |

|      | CSIE1                                    | W   | $\bigtriangleup$ | - | 0 | mem.bit            | Only bit 7<br>allows bit<br>manipulation. |

| FCCH | Serial I/O shift register 1 (SIO1)       | R/W | _                | _ | 0 |                    |                                           |

|      |                                          |     |                  |   |   |                    |                                           |

Remarks 1. IExxx : Interrupt enable flag

2. IRQ XXX: Interrupt request flag

| Address    |                        | Hardware na     | ame (symbol)          | R/W |       | ber of bits<br>be manipul |        | Bit<br>manipulation | Remarks                           |

|------------|------------------------|-----------------|-----------------------|-----|-------|---------------------------|--------|---------------------|-----------------------------------|

| , luar obo | b3                     | b2              | b1 b0                 | .,  | 1 bit | 4 bits                    | 8 bits | addressing          | Homando                           |

| FD0H       | Clock outp             | ut mode regis   | ster (CLOM)           | W   | -     | 0                         | -      |                     |                                   |

| FD8H       | SOC                    | EOC             | 1<br> <br> <br>       | w   |       | -                         | 0      |                     | b3: 1-bit write<br>b2: 1-bit read |

|            | A/D conve              | rsion mode re   | egister (ADM)         |     | -     | -                         | Ŭ      |                     |                                   |

| FDAH       | SA register            | ( ( )           |                       | R   | -     | -                         |        |                     |                                   |

|            | SA register            | (3A)            |                       | n   | -     | -                         | 0      |                     |                                   |

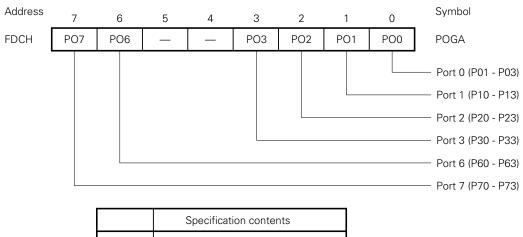

| FDCH       | Pull-up resi<br>(POGA) | istor specifica | tion register group A | W   | _     | _                         | 0      |                     |                                   |

#### Fig. 2-5 µPD75517(A) I/O Map (3/4)

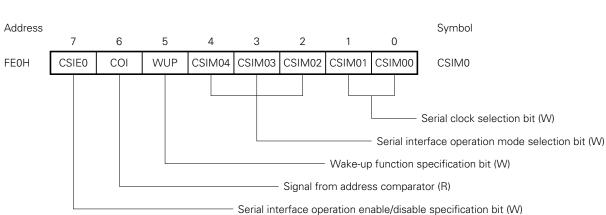

| FE0H | Serial opera                                                                    | ation mode re                                      | gister 0 (CSII | VI0)          | W   | - | - | 0       |                |                                 |

|------|---------------------------------------------------------------------------------|----------------------------------------------------|----------------|---------------|-----|---|---|---------|----------------|---------------------------------|

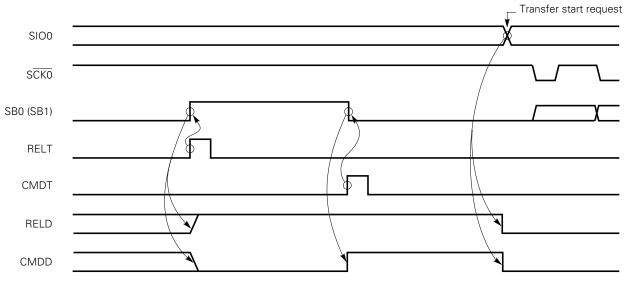

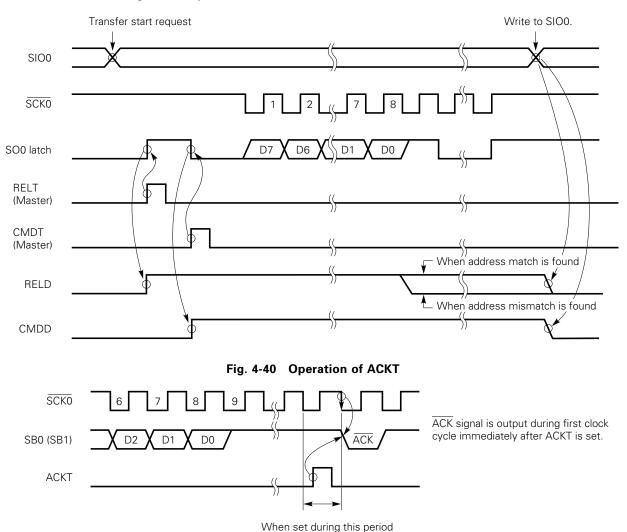

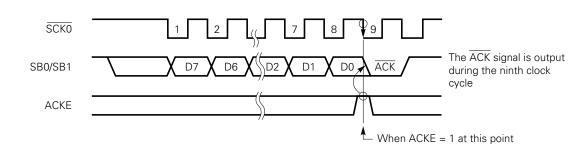

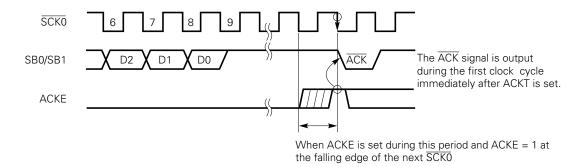

|      | CSIE0                                                                           | COI                                                | ]              | R/W           | 0   | 0 |   | mem.bit | b6: 1-bit read |                                 |

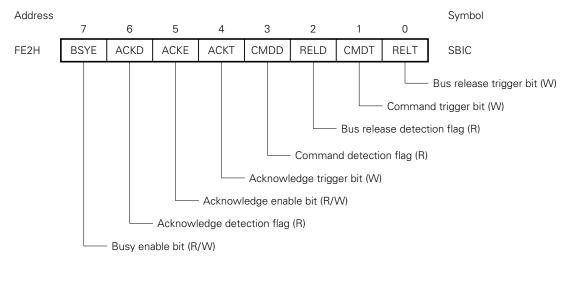

| FE2H | CMDD<br>SBI control                                                             | CMDD RELD CMDT RELT<br>SBI control register (SBIC) |                |               |     | 0 | _ | _       | mem.bit        | All bits allow<br>bit manipula- |

|      | BSYE                                                                            |                                                    |                |               |     |   |   |         |                | tion only                       |

| FE4H |                                                                                 |                                                    |                |               |     |   |   |         |                |                                 |

|      | Serial I/O s                                                                    | hift register 0                                    | (SIO0)         |               | R/W | - | - | 0       |                |                                 |

| FE6H | Slave addre                                                                     | Slave address register (SVA)                       |                |               |     |   | _ | 0       |                |                                 |

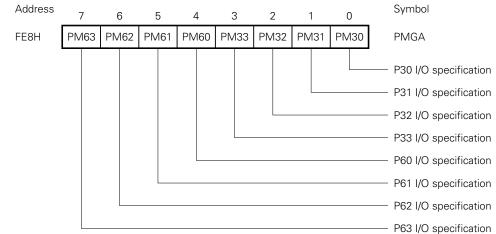

| FE8H | PM33 PM32 PM31 PM30<br>Port mode register group A (PMGA)<br>PM63 PM62 PM61 PM60 |                                                    |                |               | W   | _ | _ | 0       |                |                                 |

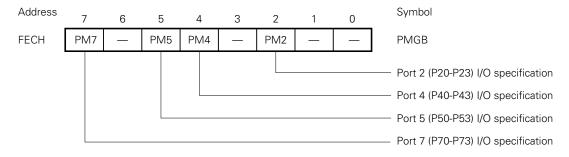

| FECH | Port mode register group B (PMGB)                                               |                                                    |                |               | W   | _ | _ | 0       |                |                                 |

|      | PM7                                                                             | -                                                  | PM5<br>PM9     | PM4<br>_ Note |     |   |   |         |                |                                 |

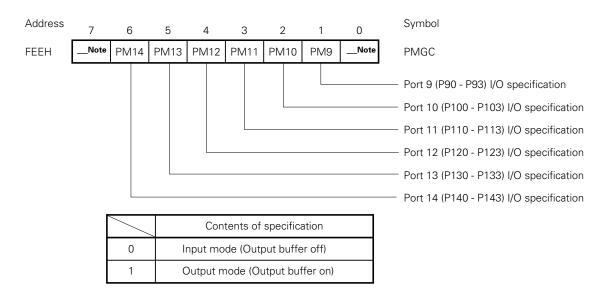

| FEEH | PM11<br>Port mode                                                               | PM10<br>register grou                              |                | W             | _   | _ |   |         |                |                                 |

|      | _ Note                                                                          | PM14                                               | PM13           | PM12          | vv  |   |   |         |                |                                 |

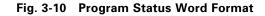

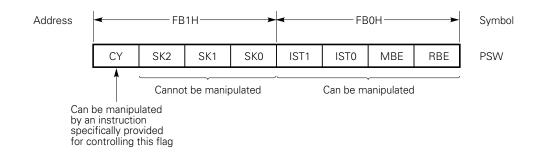

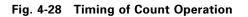

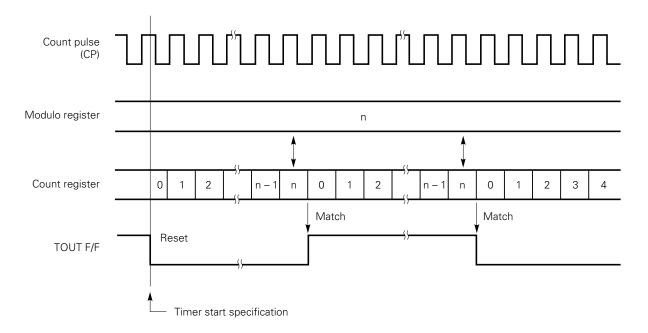

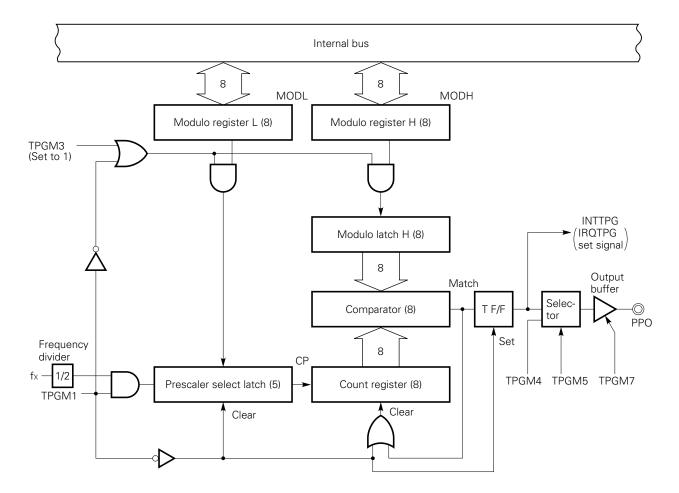

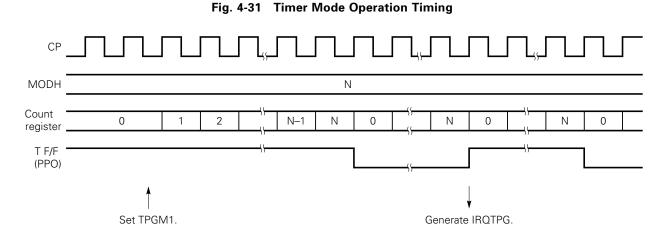

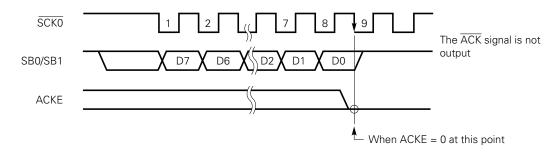

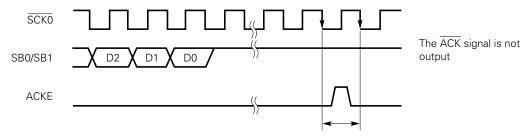

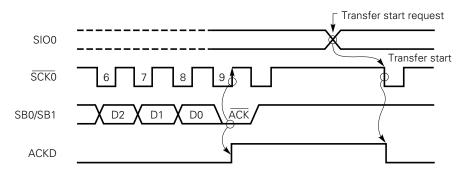

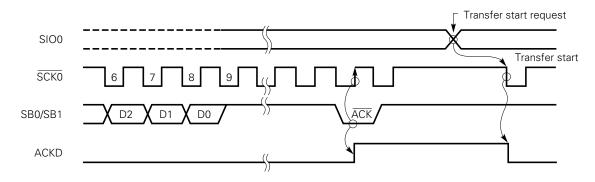

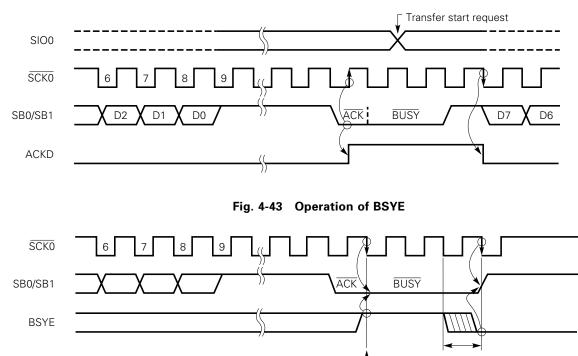

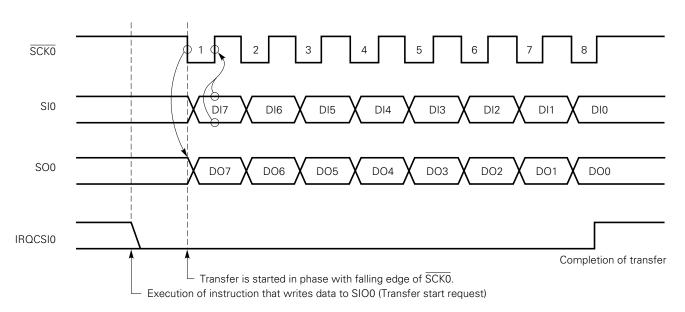

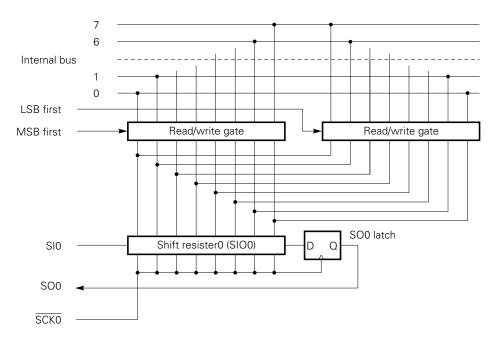

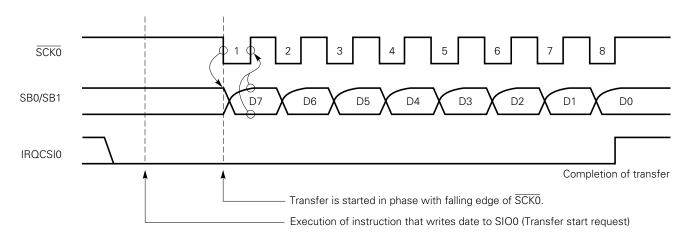

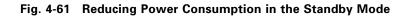

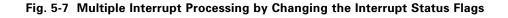

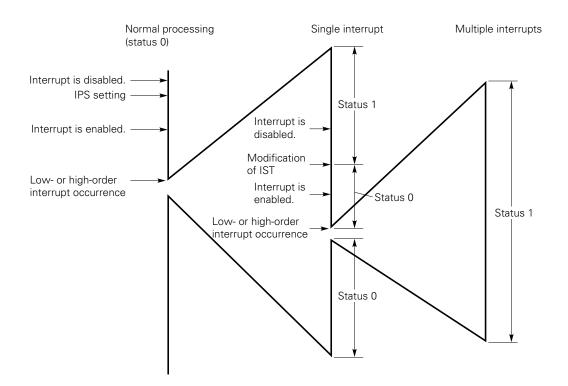

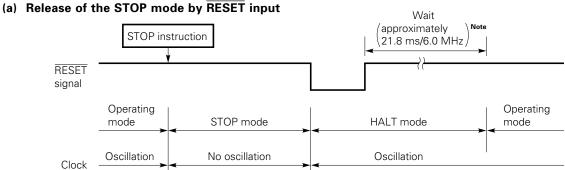

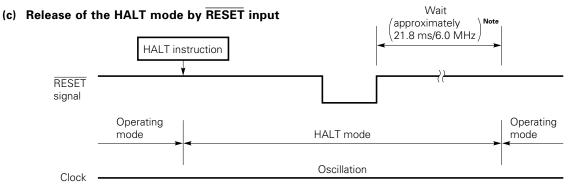

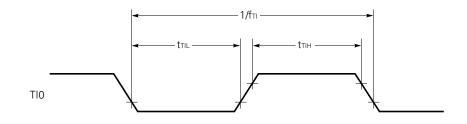

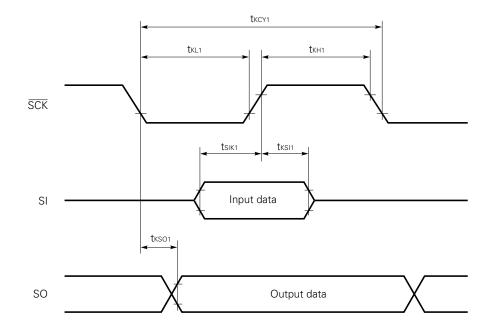

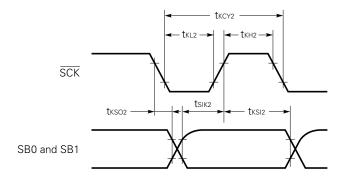

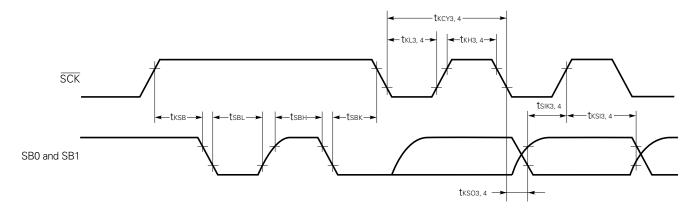

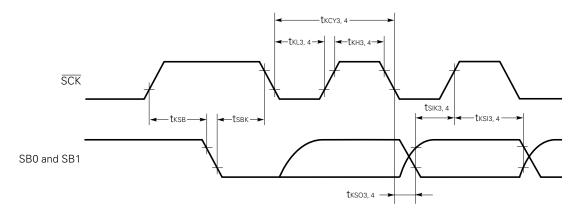

**Note** When developing a program, set 0 to the following two bits of the port mode register group C (PMGC): FEEH, b0 (Equivalent to PM8)