# 82285 CLOCK GENERATOR AND READY INTERFACE FOR I/O COPROCESSORS

82285 is an 18 pin bipolar clock generator/driver designed to provide clock signals for the 82730, 82586, or other master peripherals. It also contains READY multiplexing logic to provide the required RDYO and READY timing and synchronization for the peripheral chips. RESET logic with hysteresis and synchronization is also provided.

- Uses crystal or TTL signal for Frequency Source.

- Provides a 50% duty cycle peripheral clock output with MOS drive characteristics.

- Provides synchronous READY for peripherals from synchronous and/or asynchronous sources.

- Generates system reset output from Schmitt Trigger input.

- Capable of clock synchronization with other 82285's.

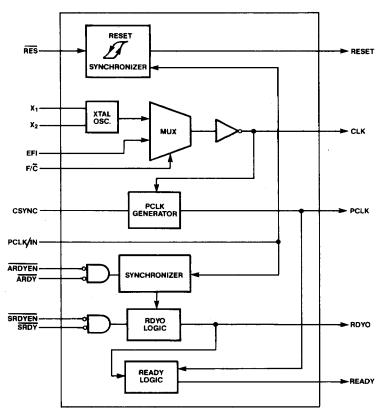

Figure 1. 82285 Block Diagram

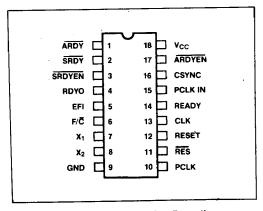

Figure 2. 82285 Pin Configuration

#### NOTE

- CLK is a TTL level output and has the same frequency as either the crystal or EFI, depending on the state of F/C.

- PCLK is a MOS level output and has half the frequency of CLK.

- ARDY and ARDYEN are interchangeable.

- 4. SRDY and SRDYEN are interchangeable.

# **FUNCTIONAL DESCRIPTION**

#### **Clock Generator**

The CLK and PCLK clock outputs may be generated either by an external crystal or by an external TTL frequency input. If the frequency/crystal select input (F/C) is high, the EFI input is used. If F/C is low, a crystal attached to X₁ and X₂ pins is used. CLK is a TTL output at the crystal or EFI frequency. PCLK is a MOS-level output which has a 50% duty cycle, operates,at 1/2 the CLK frequency, and can be used to drive the clock inputs of the 82586, 82730, or other devices.

## **Reset Logic**

The reset logic provides a Schmitt Trigger input (RES) and two synchronization flip-flops to synchronize the reset timing. The reset signal is synchronized at the falling edge of PCLK IN. A simple RC network can be used to provide power-on reset of proper duration.

Table 1. Pin Description

| Symbol                          | Pin<br>Number | Туре | Name and Function                                                                                                                                                                                                                                                                                 |  |  |  |

|---------------------------------|---------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| RES                             |               |      | RESET IN: RES is an active low signal which is used to generate RESET. A Schmitt trigger input is provided so that a RC connection can be used to establish the power up reset of proper duration.                                                                                                |  |  |  |

| RESET                           | 12            | 0    | RESET: RESET is an active high signal which is the synchron ized version of the RES input.                                                                                                                                                                                                        |  |  |  |

| X <sub>1</sub> , X <sub>2</sub> | 7,8           | l    | CRYSTAL INPUT: X <sub>1</sub> and X <sub>2</sub> are attached to a parallel resonant, fundamental mode crystal. If F/\overline{\overline{C}} is strapped low to select the internal oscillator as the clock source, CLK will be the same frequency as the crystal, PCLK will be ½ that frequency. |  |  |  |

| CLK                             | 13            | 0    | CLOCK: CLK is a TTL output and has the same frequency as either the crystal or the external frequency input (EFI), dependent upon the state of F/C.                                                                                                                                               |  |  |  |

| PCLK                            | 10            | 0    | PERIPHERAL CLOCK: PCLK is a clock output at half the frequency of the crystal input or EFI, depending on F/C input. It provides MOS levels to drive the system CLK inputs of 82586 or 82730 or other device. PCLK has a 50% duty cycle.                                                           |  |  |  |

| PCLK IN                         | 15            |      | PERIPHERAL CLOCK IN: PCLK IN is a clock input which is used for clocking the RESET flip-flops and the ARDY synchronizing flip-flop. It can be driven by the PCLK output or some other system clock.                                                                                               |  |  |  |

| F/Ĉ                             | 6             | ı    | FREQUENCY/CRYSTAL SELECT: F/C is a strapping option. When low, CLK and PCLK are generated from an external crystal. When high, CLK and PCLK are generated from the EFI input.                                                                                                                     |  |  |  |

Table 1. Pin Description (Cont.)

|                 | Pin    |      |                                                                                                                                                                                                                                                                                                             |  |  |  |

|-----------------|--------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Symbol          | Number | Туре | Name and Function                                                                                                                                                                                                                                                                                           |  |  |  |

| EFI             | 5      | 1    | EXTERNAL FREQUENCY IN: When F/C is strapped high, CLK and PCLK are generated from the EFI input. CLK will be the same frequency as EFI; PCLK will be half that frequency.                                                                                                                                   |  |  |  |

| ARDYEN          | 17     | l    | ASYNCHRONOUS READY ENABLE: ARDYEN is an asynchronous active low input which qualifies ARDY. Set up and hold times are given only to guarantee recognition on that clock edge.                                                                                                                               |  |  |  |

| ARDY            | 1      | 1    | ASYNCHRONOUS READY: ARDY is an asynchronous active low input which will be synchronized to provide the RDYO output at the falling edge of PCLK IN. Setup and hold times are given only to guarantee recognition on that falling edge of PCLK IN. The RDYO output will also be a function of the SRDY input. |  |  |  |

| SRDYEN          | 3      | _    | SYNCHRONOUS READY ENABLE: <u>SRDYEN</u> is a synchronous active low input which qualifies <u>SRDY</u> .                                                                                                                                                                                                     |  |  |  |

| SRDY            | 2      | 1    | SYNCHRONOUS READY: SRDY is a synchronous active low input. The RDYO outputs will also be a function of the ARDY input.                                                                                                                                                                                      |  |  |  |

| RDYO            | 4      | 0    | SYNCHRONOUS READY OUT: RDYO is an active high output which is either the SRDY input delayed, or the ARDY input synchronized. RDYO will be inactive (low) if the ready inputs are inactive (high).                                                                                                           |  |  |  |

| READY           | 14     | 0    | READY: READY is an active high output which is the RDYO signal synchronized with the falling edge of PCLK output.                                                                                                                                                                                           |  |  |  |

| CSYNC           | 16     | -    | CLOCK SYNCHRONIZATION: CSYNC is used to provide synchronization of PCLK's among multiple 82285's. The source of CSYNC come from the PCLK output of the reference 82285. When synchronization is not used, CSYNC should be connected to V <sub>CC</sub> .                                                    |  |  |  |

| GND             | 9      | -    | Ground.                                                                                                                                                                                                                                                                                                     |  |  |  |

| V <sub>CC</sub> | 18     | _    | +5V supply.                                                                                                                                                                                                                                                                                                 |  |  |  |

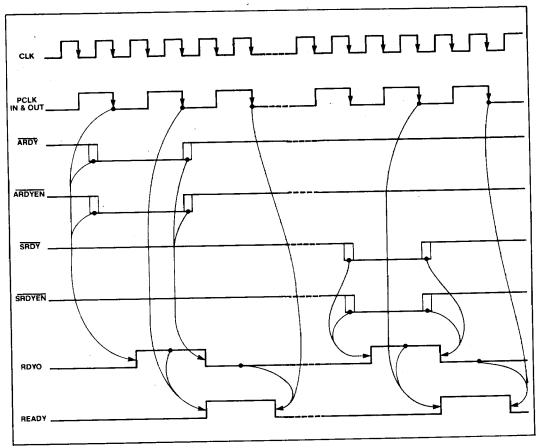

# **RDYO and READY Logic**

RDYO is determined by synchronous ready input SRDY qualified by SRDYEN or asynchronous ready input ARDY qualified by ARDYEN. For the asynchronous input ARDY, it will be clocked in at the falling edge of PCLK IN; and the RDYO output will become valid at the same falling edge of PCLK IN, provided ARDY is stable. The ARDY flip-flop is used as the first step in a two flip-flop synchronization method for RDYO. For the synchronous input SRDY, the RDYO output will become valid when SRDY is stable.

The READY output is the RDYO output latched at the falling edge of PCLK out. It provides an addi-

tional ready signal in order to optimize the operation of systems using the 82730, 82586, and 8086.

#### WARNING:

The RDYO output is not fully synchronized when the asynchronous mode (ARDY) is used.

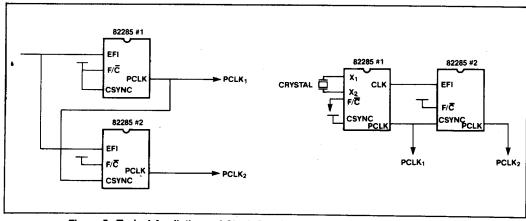

# **Clock Synchronization Logic**

The clock synchronization logic allows the PCLK signal of the device to be synchronized with the PCLK from other 82285's. A typical application of this synchronization logic is shown in Diagram 5. Diagram 3 and 4 illustrates typical functional sequences of 82285.

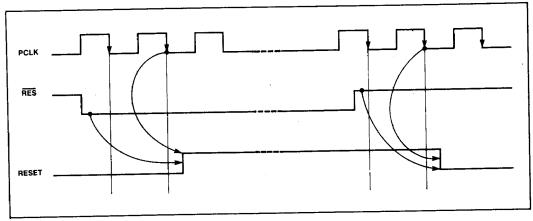

Figure 3. Reset Sequence

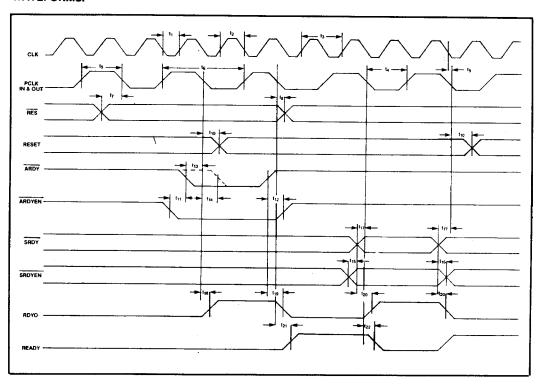

Figure 4. Ready Operation

Figure 5. Typical Applictions of Clock Synchronization Among Multiple 82285's

## **ABSOLUTE MAXIMUM RATINGS\***

| Ambient Temperature Under Bias  | 0°C to 70°C   |

|---------------------------------|---------------|

| Storage Temperature             | 65°C to 150°C |

| Voltage on any Pin with Respect |               |

| to Ground                       | -0.5V to +7V  |

| Power Dissination               | 1.5 Watt      |

\*NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# **Electrical Characteristics and Waveforms**

### D.C. Characteristics for 82285

Conditions:  $T_A = 0^{\circ} C$  to  $70^{\circ} C$ ;  $V_{CC} = 5V \pm 10\%$

| Symbol           | Parameter                   | Min. | Max.  | Units | Test Conditions                  |

|------------------|-----------------------------|------|-------|-------|----------------------------------|

| l <sub>F</sub>   | Forward Input Current       |      | -0.5  | mA    | V <sub>F</sub> = 0.45V           |

|                  | For PCLK IN                 |      | -0.6  | mA    | V <sub>F</sub> = 0.45V           |

|                  | For SRDYEN, SRDY            |      | -0.85 | mA    | V <sub>F</sub> = 0.45V           |

| İB               | Reverse Input Current       |      | 50    | μΑ    | V <sub>R</sub> = V <sub>CC</sub> |

| Vc               | Input Forward Clamp voltage |      | -1.0  | V     | i <sub>c</sub> = -5 mA           |

| lcc              | Power Supply Current        |      | 145   | mA    |                                  |

| V <sub>IL</sub>  | Input "low" voltage         |      | 0.8   | V     |                                  |

| V <sub>iH</sub>  | Input "high" voltage        | 2.0  |       |       |                                  |

| V <sub>IHR</sub> | Reset input "high" voltage  | 2.6  |       | V     |                                  |

| VoL              | Output "low" voltage        |      | 0.45  | V     | I <sub>OL</sub> = 5.25 mA        |

| V <sub>он</sub>  | Output "high" voltage PCLK  | 4.0  |       | ٧     | -1.05 mA                         |

|                  | Other outputs               | 2.4  |       | V     | –1,05 mA                         |

| VIHR-VILR        | RES Input Hysteresis        | 0.25 |       | -     | <del></del>                      |

| Ci               | Input Capacitance           |      | 10    | pF    |                                  |

82285 A.C. Characteristics (Cont.) Condition:  $T_A$  = 0° C to 70° C;  $V_{CC}$  = %V  $\pm$  10% (Note 1)

| Symbol          | Parameter                    | Min.                   | Max. | Units |           |

|-----------------|------------------------------|------------------------|------|-------|-----------|

| t <sub>R</sub>  | CLK and PCLK rise time       |                        | 10   | ns    | Note 2    |

| t <sub>F</sub>  | CLK and PCLK fall time       |                        | 10   | ns    | Note 2    |

| tL              | PCLK IN and EFI low time     | 30                     |      | ns    |           |

| t <sub>H</sub>  | PCLK IN and EFI high time    | 30                     |      | ns    |           |

| t <sub>1</sub>  | CLK low time                 | 1/2 t <sub>3</sub> -15 |      | ns    |           |

| t <sub>2</sub>  | CLK high time                | 1/2 t <sub>3</sub> -15 |      | ns    |           |

| ts              | CLK cycle time               | 56                     |      | ns    |           |

| t <sub>4</sub>  | PCLK low time @ 0.6V         | t₃-12.5                |      | ns    |           |

|                 | PCLK low time @ 1.5V         | t <sub>3</sub> -10     | `    | ns    |           |

| t <sub>5</sub>  | PCLK high time @ 3.8V        | t <sub>3</sub> -17.5   |      | ns .  |           |

|                 | PCLK high time @ 1.5V        | t <sub>3</sub> -10     |      | ns    |           |

| t <sub>6</sub>  | PCLK cycle time              | 2t <sub>3</sub>        |      | ns    |           |

| t <sub>7</sub>  | RES setup time to PCLK INI   | 15                     |      | ns    | Note 3, 4 |

| t <sub>B</sub>  | RES hold time from PCLK INI  | 10                     |      | ns    | Note 3, 4 |

| to              | PCLK delay from CLK low      | 0                      | 40   | ns    |           |

| t <sub>10</sub> | RESET delay from PCLK low    | 0                      | 50   | ns    |           |

| t <sub>11</sub> | ARDYEN setup time to ARDY    | 0                      |      | ns    | Note 4    |

| t <sub>12</sub> | ARDYEN hold time from ARDY   | 0                      |      | ns    | Note 4    |

| t <sub>13</sub> | ARDY setup time to PCLK IN   | 0                      |      | ns    | Note 3, 4 |

| t <sub>14</sub> | ARDY hold time from PCLK INI |                        | 30   | ns    | Note 3, 4 |

| t <sub>15</sub> | SRDYEN setup time to SRDY    | 0                      |      | ns    | Note 4    |

| t <sub>16</sub> | SRDYEN hold time from SRDY   | 0                      |      | ns    | Note 4    |

| t <sub>17</sub> | SRDY setup time to PCLKI     |                        | 50   | ns    |           |

| t <sub>18</sub> | RDYO1 delay from PCLK INI    |                        | 55   | ns    |           |

| t <sub>19</sub> | RDYOi delay from ARDY1       |                        | 30   | ns    |           |

| t <sub>20</sub> | RDYO delay from SRDY         |                        | 30   | ns    |           |

| t <sub>21</sub> | READYI delay from PCLKI      | -20                    | 0    | ns    |           |

| t <sub>22</sub> | READYI delay from PCLKI      | -20                    | 8    | ns    |           |

|                 | Crystal frequency            | 17.6                   | 4    | MHz   | Note 6    |

|                 | EFI frequency                | D.C.                   | 17.6 | MHz   | Note 5    |

(see notes next page)

#### NOTE

1. All times are measured at the 1.5V level unless specified otherwise.

The rise and fall times for CLK are measured between 0.8V and 2.0V (TTL level drive characteristics). The rise and fall times for PCLK are measured between 1.0V and 3.5V (MOS level drive characteristics).

3. These are asynchronous inputs.

The setup and hold times are measured at the 0.8V and 2.0V levels for the inputs and at 1.5V from the PCLK signal.

5. To assure proper operation, the rise time or fall time of EFI cannot exceed 100 ns.

The specified timings are given in accordance with the maximum operating fre quency of 17.6 MHz. However, the device will be designed to operate to 24 MHz with all timing specs to be determined.

## Loading:

For READY OUTPUT:

$C_L = 30 \text{ pf}, I_{OL} = 5.25 \text{ mA}, I_{OH} = -1.05 \text{ mA}$

For the CLK output:

$C_L = 75 \text{ pf}, I_{OL} = 5.25 \text{ mA}, I_{OH} = -1.05 \text{ mA}$

For the RDYO output:

$C_L = 75 \text{ pf}, I_{OL} = 5.25 \text{ mA}, I_{OH} = -1.05 \text{ mA}$

For the PCLK output:

$C_L = 175 \text{ pf}, I_{OL} = 5.25 \text{ mA}, I_{OH} = -1.05 \text{ mA}$

All input capacitance will be:

C<sub>i</sub> = 10 of

#### WAVEFORMS.