### 82374EB/82374SB EISA SYSTEM COMPONENT (ESC)

- Integrates EISA Compatible Bus Controller

- Translates Cycles Between EISA and **ISA Bus**

- Supports EISA Burst and Standard Cycles

- Supports ISA Zero Wait-State Cycles - Supports Byte Assembly/

- Disassembly for 8-, 16- and 32-Bit Transfers

- Supports EISA Bus Frequency of up to 8.33 MHz

- Supports Eight EISA Slots

- Directly Drives Address, Data and Control Signals for Eight Slots

- Decodes Address for Eight Slot **Specific AENs**

- Provides Enhanced DMA Controller - Provides Scatter-Gather Function

- Supports Type A, Type B, Type C (Burst), and Compatible DMA Transfer

- Provides Seven Independently **Programmable Channels**

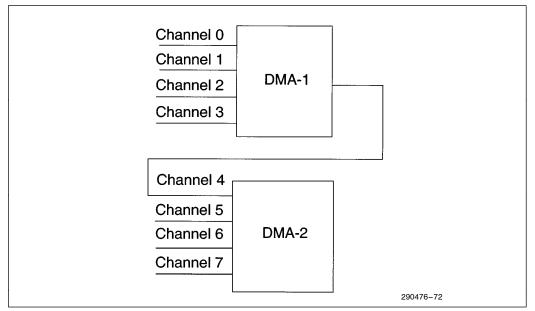

- Integrates Two 82C37A Compatible **DMA Controllers**

- Integrates the Functionality of two 82C59 Interrupt Controllers and two 82C54 Timers

- Provides 14 Programmable Channels for Edge or Level Interrupts

- Provides 4 PCI Interrupts Routible to any of 11 Interrupt Channels

- Supports Timer Function for Refresh **Request, System Timer, Speaker** Tone, Fail Safe Timer, and CPU **Speed Control**

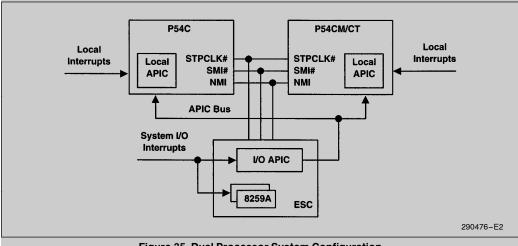

- Advanced Programmable Interrupt Controller (APIC)

- Multiprocessor Interrupt

- Management

- Separate Bus For Interrupt Messages

- 5V CMOS Technology

- Provides High Performance Arbitration Supports Eight EISA Masters and PCEB

- Supports ISA Masters, DMA Channels, and Refresh

- **Provides Programmable Arbitration** Scheme for Fixed, Rotating, or **Combination Priority**

- Integrates Support Logic for X-Bus Peripherals

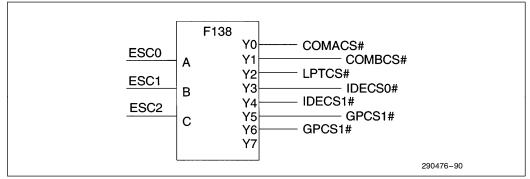

- Generates Chip Selects/Encoded Chip Selects for Floppy and Keyboard Controller, IDE, Parallel/ Serial Ports, and General Purpose Peripherals

- Provides Interface for Real Time Clock

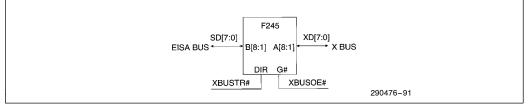

- **Generates Control Signals for X-Bus Data Transceiver**

- Integrates Port 92, Mouse Interrupt, and Coprocessor Error Reporting

- Generates Non-Maskable Interrupts (NMI)

- PCI System Errors

- PCI Parity Errors

- EISA Bus Parity Errors

- Fail Safe Timer

- Bus Timeout

- Via Software Control

- Provides BIOS Interface

- Supports 512K Bytes of Flash or **EPROM BIOS on the X-Bus** - Allows BIOS on PCI

- Supports Integrated VGA BIOS

- 82374SB System Power Management (Intel SMM Support)

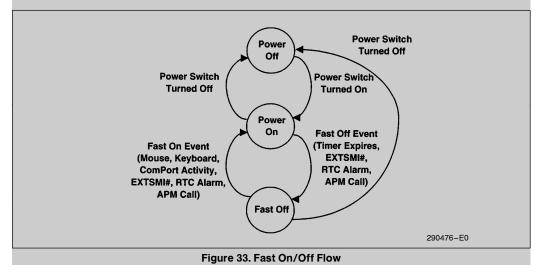

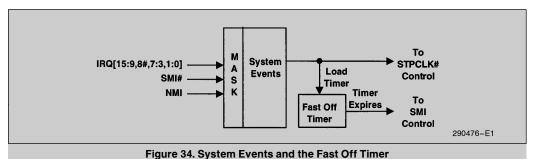

- Fast On/Off Support via SMI GenerationHardware Events, Software Events, EXTSMI#, Fast Off **Timer, System Events**

- Programmable CPU Clock Control

- Enables Energy Efficient Desktop Systems

- Only Available as Part of a Supported Kit

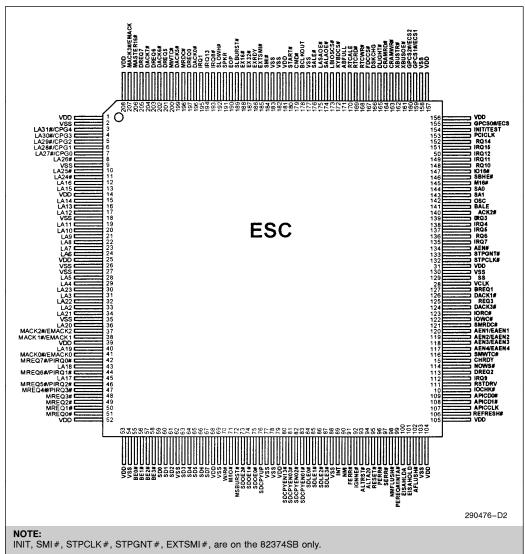

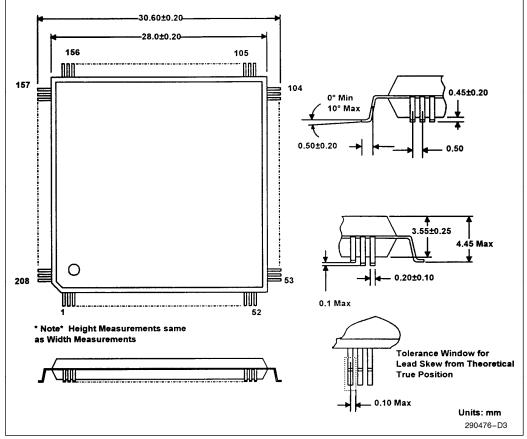

- 208-Pin QFP Package

\*Other brands and names are the property of their respective owners. Information in this document is provided in connection with Intel products. Intel assumes no liability whatsoever, including infringement of any patent or copyright, for sale and use of Intel products except as provided in Intel's Terms and Conditions of Sale for such products. Intel retains the right to make changes to these specifications at any time, without notice. Microcomputer Products may have minor variations to this specification known as errata. COPYRIGHT © INTEL CORPORATION, 1996 March 1996 Order Number: 290476-004

This document describes both the 82374EB and 82374SB components. Unshaded areas describe the 82374EB. Shaded areas, like this one, describe the 82374SB operations that differ from the 82374EB.

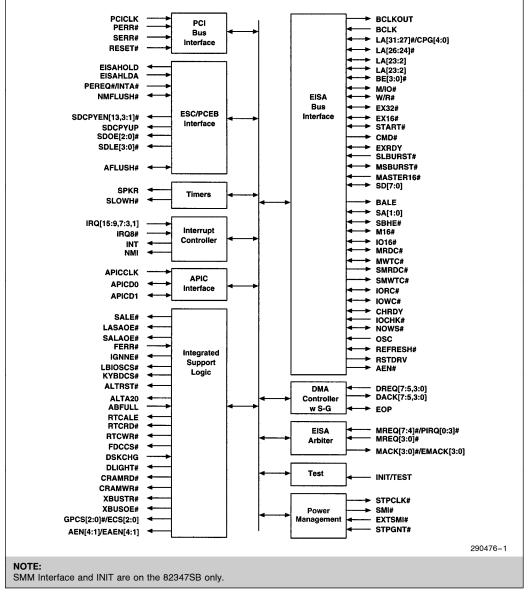

The 82374EB/SB EISA System Component (ESC) provides all the EISA system compatible functions. The ESC with the PCEB provide all the functions to implement an EISA-to-PCI bridge and EISA I/O subsystem. The ESC integrates the common I/O functions found in today's EISA-based PC systems. The ESC incorporates the logic for an EISA (master and slave) interface, EISA bus controller, enhanced seven channel DMA controller with scatter-gather support, EISA arbitration, 14 channel interrupt controller, Advanced Programmable Interrupt Controller (APIC), five programmable timer/counters, and non-maskable-interrupt (NMI) control logic. The ESC also integrates support logic to decode peripheral devices such as the Flash BIOS, real time clock, keyboard/mouse controller, floppy controller, two serial ports, one parallel port, and IDE hard disk drive.

The 82374SB also contains support for SMM power management

## intel

Simplified ESC Block Diagram

### 82374EB/82374SB EISA SYSTEM COMPONENT (ESC)

### CONTENTS

| 1.0 ARCHITECTURAL OVERVIEW                           | 11 |

|------------------------------------------------------|----|

| 1.1 PCEB Overview                                    | 14 |

| 1.2 ESC Overview                                     | 16 |

| 2.0 SIGNAL DESCRIPTION                               | 17 |

| 2.1 PCI Local Bus Interface Signals                  | 18 |

| 2.2 EISA Bus Interface Signals                       |    |

| 2.3 ISA Bus Signals                                  |    |

| 2.4 DMA Signal Description                           | 24 |

| 2.5 EISA Arbitration Signals                         | 25 |

| 2.6 Timer Unit Signal                                |    |

| 2.7 Interrupt Controller Signals                     | 27 |

| 2.8 APIC Bus Signals                                 | 27 |

| 2.9 System Power Management Signals (82374SB Only)   | 27 |

| 2.10 ESC/PCEB Interface Signals                      | 28 |

| 2.10.1 ARBITRATION AND INTERRUPT ACKNOWLEDGE CONTROL | 28 |

| 2.10.2 PCEB BUFFER COHERENCY CONTROL                 | 29 |

| 2.11 Integrated Logic Signals                        |    |

| 2.11.1 EISA ADDRESS BUFFER CONTROL                   | 30 |

| 2.11.2 COPROCESSOR INTERFACE                         |    |

| 2.11.3 BIOS INTERFACE                                |    |

| 2.11.4 KEYBOARD CONTROLLER INTERFACE                 |    |

| 2.11.5 REAL TIME CLOCK INTERFACE                     |    |

| 2 11.6 FLOPPY DISK CONTROLLER INTERFACE              |    |

| 2.11.7 CONFIGURATION RAM INTERFACE                   |    |

| 2.11.8 X-BUS CONTROL AND GENERAL PURPOSE DECODE      |    |

| 2.12 Test Signal                                     | 35 |

| 3.0 REGISTER DESCRIPTION                             | 35 |

| 3.1 Configuration Registers                          | 35 |

| 3.1.1 ESCID—ESC ID REGISTER                          | 36 |

| 3.1.2 RID—REVISION ID REGISTER                       | 36 |

| 3.1.3 MS—MODE SELECT REGISTER                        | 36 |

| 3.1.4 BIOSCSA—BIOS CHIP SELECT A REGISTER            | 38 |

| 3.1.5 BIOSCSB—BIOS CHIP SELECT B REGISTER            | 39 |

| CONTENTS                                                                                             | PAGE |

|------------------------------------------------------------------------------------------------------|------|

| 3.1.6 CLKDIV—EISA CLOCK DIVISOR REGISTER                                                             | 40   |

| 3.1.7 PCSA—PERIPHERAL CHIP SELECT A REGISTER                                                         | 41   |

| 3.1.8 PCSB—PERIPHERAL CHIP SELECT B REGISTER                                                         | 42   |

| 3.1.9 EISAID[4:1]—EISA ID REGISTERS                                                                  | 43   |

| 3.1.10 SGRBA—SCATTER/GATHER RELOCATE BASE ADDRESS REGISTER                                           | 43   |

| 3.1.11 APICBASE—APIC BASE ADDRESS RELOCATION                                                         | 44   |

| 3.1.12 PIRQ[0:3] #—PIRQ ROUTE CONTROL REGISTERS                                                      | 44   |

| 3.1.13 GPCSLA[2:0]—GENERAL PURPOSE CHIP SELECT LOW ADDRESS<br>REGISTER                               | 45   |

| 3.1.14 GPCSHA[2:0]—GENERAL PURPOSE CHIP SELECT HIGH ADDRESS<br>REGISTER                              |      |

| 3.1.15 GPCSM[2:0]—GENERAL PURPOSE CHIP SELECT MASK REGISTER                                          |      |

| 3.1.16 GPXBC—GENERAL PURPOSE PERIPHERAL X-BUS CONTROL REGISTER                                       |      |

| 3.1.17 PAC—PCI/APIC CONTROL REGISTER                                                                 |      |

| 3.1.18 TESTC—TEST CONTROL REGISTER                                                                   |      |

| 3.1.19 SMICNTL—SMI CONTROL REGISTER                                                                  |      |

| 3.1.20 SMIEN—SMI ENABLE REGISTER                                                                     |      |

| 3.1.21 SEE—SYSTEM EVENT ENABLE REGISTER                                                              |      |

| 3.1.22 FTMR—FAST OFF TIMER REGISTER                                                                  |      |

| 3.1.23 SMIREQ—SMI REQUEST REGISTER                                                                   |      |

| 3.1.24 CTLTMR—CLOCK SCALE STPCLK # LOW TIMER                                                         |      |

| 3.1.25 CTLTMRH—CLOCK SCALE STPCLK # HIGH TIMER                                                       |      |

| 3.2 DMA Register Description                                                                         |      |

| 3.2.1 DCOM—COMMAND REGISTER                                                                          |      |

| 3.2.2 DCM—DMA CHANNEL MODE REGISTER                                                                  |      |

| 3.2.3 DCEM—DMA CHANNEL EXTENDED MODE REGISTER                                                        |      |

| 3.2.4 DR—DMA REQUEST REGISTER                                                                        |      |

| 3.2.5 MASK REGISTER—WRITE SINGLE MASK BIT                                                            |      |

| 3.2.6 WAMB—WRITE ALL MASK BITS REGISTER                                                              |      |

| 3.2.7 DS—DMA STATUS REGISTER                                                                         |      |

| 3.2.8 DB&CA—DMA BASE AND CURRENT ADDRESS REGISTER (8237<br>COMPATIBLE SEGMENT)                       | 61   |

| 3.2.9 DB&CBW—DMA BASE AND CURRENT BYTE/WORD COUNT REGISTER<br>(8237 COMPATIBLE SEGMENT)              |      |

| 3.2.10 DMA BASE AND CURRENT HIGH BYTE/WORD COUNT REGISTER; DMA<br>BASE HIGH BYTE/WORD COUNT REGISTER | 63   |

| 3.2.11 DMA MEMORY LOW PAGE REGISTER; DMA MEMORY BASE LOW PAGE<br>REGISTER                            | 64   |

| 3.2.12 DMAP—DMA PAGE REGISTER                                                                        | 64   |

| CONTENTS                                                                            | PAGE |

|-------------------------------------------------------------------------------------|------|

| 3.2.13 DMALPR—DMA LOW PAGE REFRESH REGISTER                                         | 65   |

| 3.2.14 DMAMHPG—DMA MEMORY HIGH PAGE REGISTER; DMA MEMORY BASE<br>HIGH PAGE REGISTER |      |

| 3.2.15 DMAHPGR—DMA HIGH PAGE REGISTER REFRESH                                       | 66   |

| 3.2.16 STOP REGISTERS                                                               | 66   |

| 3.2.17 CHAIN—CHAINING MODE REGISTER                                                 | 67   |

| 3.2.18 CHAINSTA—CHAINING MODE STATUS REGISTER                                       | 68   |

| 3.2.19 CHINTST—CHANNEL INTERRUPT STATUS REGISTER                                    | 68   |

| 3.2.20 CHAINBEC—CHAIN BUFFER EXPIRATION CONTROL REGISTER                            | 68   |

| 3.2.21 SCATGA—SCATTER-GATHER COMMAND REGISTER                                       | 69   |

| 3.2.22 SCAGAST—SCATTER-GATHER STATUS REGISTER                                       | 71   |

| 3.2.23 SCAGAD—SCATTER-GATHER DESCRIPTOR TABLE POINTER REGISTER                      | 72   |

| 3.2.24 CBPFF—CLEAR BYTE POINTER FLIP FLOP REGISTER                                  | 73   |

| 3.2.25 DMC—DMA MASTER CLEAR REGISTER                                                | 73   |

| 3.2.26 DCM—DMA CLEAR MASK REGISTER                                                  | 74   |

| 3.3 Timer Unit Registers                                                            | 74   |

| 3.3.1 TCW—TIMER CONTROL WORD REGISTER                                               | 74   |

| 3.3.2 TIMER READ BACK COMMAND REGISTER                                              | 76   |

| 3.3.3 COUNTER LATCH COMMAND REGISTER                                                | 77   |

| 3.3.4 TMSTAT—TIMER STATUS BYTE FORMAT REGISTER                                      | 78   |

| 3.3.5 CAPS—COUNTER ACCESS PORTS                                                     | 79   |

| 3.4 Interrupt Controller Registers                                                  | 79   |

| 3.4.1 ICW1—INITIALIZATION COMMAND WORD 1                                            |      |

| 3.4 2 ICW2—INITIALIZATION COMMAND WORD 2                                            | 81   |

| 3.4.3 ICW3—INITIALIZATION COMMAND WORD 3 (MASTER)                                   | 82   |

| 3.4.4 ICW3—INITIALIZATION COMMAND WORD 3 (SLAVE)                                    | 82   |

| 3.4.5 ICW4—INITIALIZATION COMMAND WORD 4                                            | 83   |

| 3.4.6 OCW1—OPERATION CONTROL WORD 1                                                 | 84   |

| 3.4.7 OCW2—OPERATION CONTROL WORD 2                                                 | 84   |

| 3.4.8 OCW3—OPERATION CONTROL WORD 3                                                 | 85   |

| 3.4.9 ELCR—EDGE/LEVEL CONTROL REGISTER                                              | 87   |

| 3.4.10 NMISC—NMI STATUS AND CONTROL REGISTER                                        | 87   |

| 3.4.11 NMIERTC—NMI CONTROL AND REAL-TIME CLOCK ADDRESS                              | 88   |

| 3.4.12 NMIESC—NMI EXTENDED STATUS AND CONTROL REGISTER                              | 89   |

| 3.4.13 SOFTNMI—SOFTWARE NMI GENERATION REGISTER                                     | 90   |

| 3.5 EISA Configuration, Floppy Support, and Port 92h                                | 90   |

| 3.5.1 CONFRAMP—CONFIGURATION RAM PAGE REGISTER                                      |      |

| 3.5.2 DIGOUT—DIGITAL OUTPUT REGISTER                                                |      |

| CONTENTS                                             | PAGE |

|------------------------------------------------------|------|

| 3.5.3 PORT 92 REGISTER                               |      |

| 3.5.4 LEISAMG—LAST EISA BUS MASTER GRANTED REGISTER  |      |

| 3.6 Power Management Registers                       |      |

| 3.6.1 APMC—ADVANCED POWER MANAGEMENT CONTROL PORT    |      |

| 3.6.2 APMS—ADVANCED POWER MANAGEMENT STATUS PORT     |      |

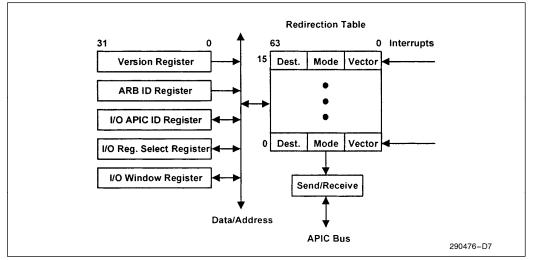

| 3.7 APIC Registers                                   | 93   |

| 3.7.1 IOREGSEL—I/O REGISTER SELECT REGISTER          |      |

| 3.7.2 IOWIN—I/O WINDOW REGISTER                      | 93   |

| 3.7.3 APICID—I/O APIC IDENTIFICATION REGISTER        | 94   |

| 3.7.4 APICID—I/O APIC IDENTIFICATION REGISTER        | 94   |

| 3.7.5 APICARB—I/O APIC ARBITRATION REGISTER          | 95   |

| 3.7.6 IOREDTBL[15:0]—I/O REDIRECTION TABLE REGISTERS | 95   |

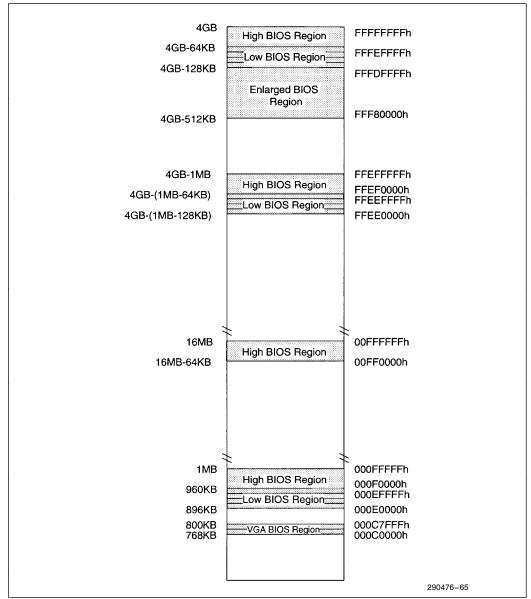

| 4.0 ADDRESS DECODING                                 | 98   |

| 4.1 BIOS Memory Space                                |      |

| 4.2 I/O Addresses Contained Within The ESC           |      |

| 4.3 Configuration Addresses                          |      |

| 4.4 X-Bus Peripherals                                |      |

| 4.5 I/O APIC Registers                               |      |

| 5.0 EISA CONTROLLER FUNCTIONAL DESCRIPTION           |      |

| 5.1 Overview                                         |      |

| 5.2 Clock Generation                                 |      |

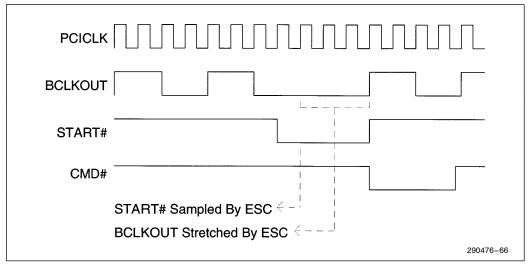

| 5.2.1 CLOCK STRETCHING                               | 116  |

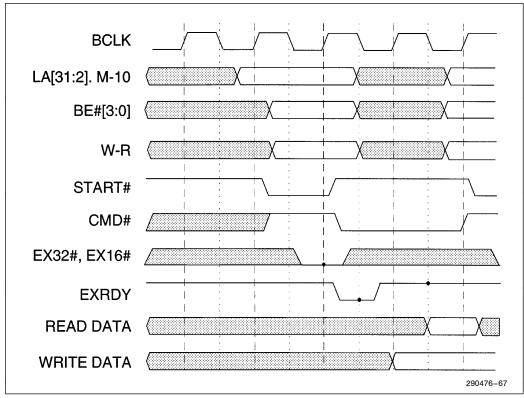

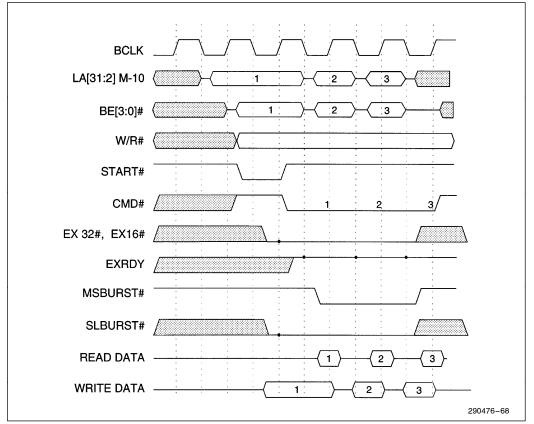

| 5.3 EISA Master Cycles                               | 117  |

| 5.3.1 EISA MASTER TO 32-BIT EISA SLAVE               |      |

| 5.3.2 EISA MASTER TO 16-BIT ISA SLAVE                | 119  |

| 5.3.3 EISA MASTER TO 8-BIT EISA/ISA SLAVES           | 119  |

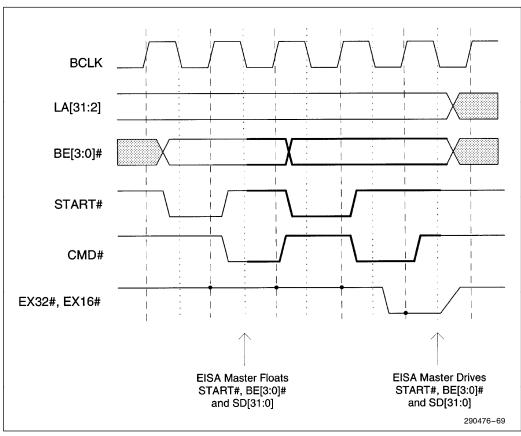

| 5.3.4 EISA MASTER BACK-OFF                           | 120  |

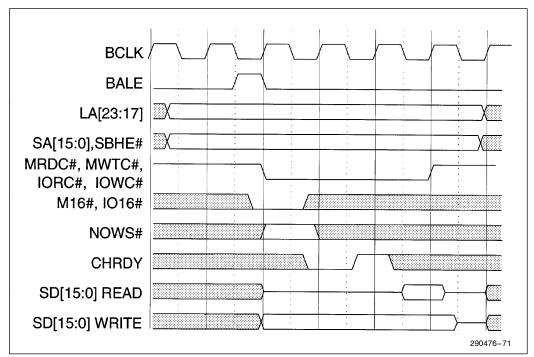

| 5.4 ISA Master Cycles                                | 121  |

| 5.4.1 ISA MASTER TO 32-/16-BIT EISA SLAVE            | 121  |

| 5.4.2 ISA MASTER TO 16-BIT ISA SLAVE                 | 121  |

| 5.4.3 ISA MASTER TO 8-BIT EISA/ISA SLAVE             | 123  |

| 5.4.4 ISA WAIT STATE GENERATION                      | 123  |

| 5.5 Mis-Match Cycles                                 | 124  |

| 5.6 Data Swap Buffer Control Logic                   | 125  |

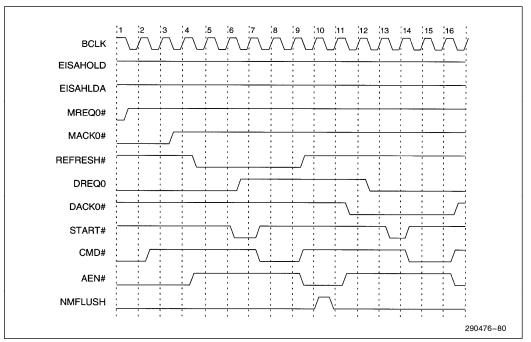

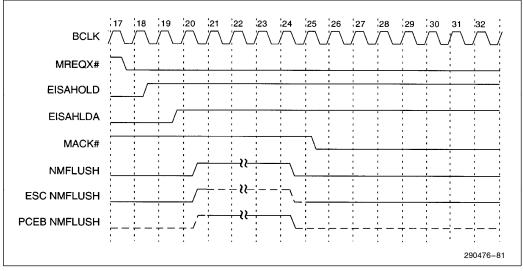

| 5.7 Servicing DMA Cycles                             | 126  |

| 5.8 Refresh Cycles                                   | 126  |

| CONTENTS                                                       | PAGE |

|----------------------------------------------------------------|------|

| 5.9 EISA Slot Support                                          | 126  |

| 5.9.1 AEN GENERATION                                           | 126  |

| 5.9.2 MACKX# GENERATION                                        | 128  |

| 6.0 DMA CONTROLLER                                             |      |

| 6.1 DMA Controller Overview                                    |      |

| 6.2 DMA Transfer Modes                                         |      |

| 6.2.1 SINGLE TRANSFER MODE                                     |      |

| 6.2.2 BLOCK TRANSFER MODE                                      |      |

| 6.2.3 DEMAND TRANSFER MODE                                     |      |

| 6.2.4 CASCADE MODE                                             |      |

| 6.3 DMA Transfer Types                                         |      |

| 6.4 DMA Timing                                                 |      |

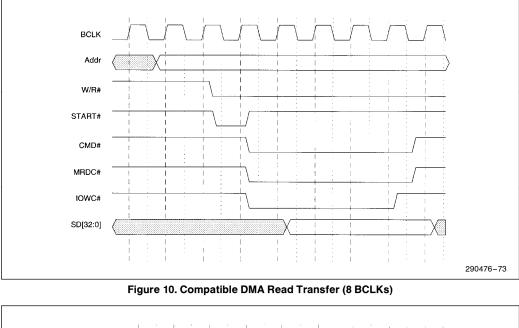

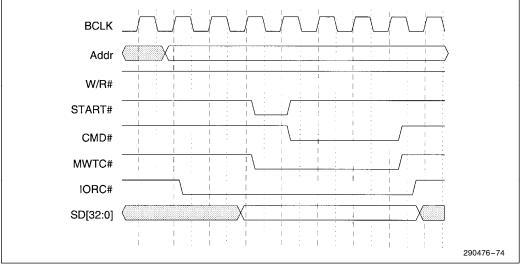

| 6.4.1 COMPATIBLE TIMINGS                                       |      |

| 6.4.2 TYPE "A" TIMING                                          |      |

| 6.4.3 TYPE "B" TIMING                                          |      |

| 6.4.4 TYPE "C" (BURST) TIMING                                  |      |

| 6.5 Channel Priority                                           |      |

| 6.6 Scatter-Gather Functional Description                      |      |

| 6.7 Register Functionality                                     |      |

| 6.7.1 ADDRESS COMPATIBILITY MODE                               |      |

| 6.7.3 ADDRESS SHIFTING WHEN PROGRAMMED FOR 16-BIT I/O COUNT BY | 139  |

| WORDS                                                          | 139  |

| 6.7.4 STOP REGISTERS (RING BUFFER DATA STRUCTURE)              | 139  |

| 6.7.5 BUFFER CHAINING MODE AND STATUS REGISTERS                |      |

| 6.7.6 AUTOINITIALIZE                                           | 141  |

| 6.8 Software Commands                                          |      |

| 6.8.1 CLEAR BYTE POINTER FLIP-FLOP                             |      |

| 6.8.2 DMA MASTER CLEAR                                         |      |

| 6.8.3 CLEAR MASK REGISTER                                      |      |

| 6.9 Terminal Count/EOP Summary                                 |      |

| 6.10 Buffer Chaining                                           |      |

| 6.11 Refresh Unit                                              | 143  |

| 7.0 EISA BUS ARBITRATION                                       |      |

| 7.1 Arbitration Priority                                       |      |

| 7.2 Preemption                                                 |      |

| 7.2.1 PCEB EISA BUS ACQUISITION AND PCEB PREEMPTION            | 144  |

| CONTENTS PAG<br>7.2.2 EISA MASTER PREEMPTION           |    |

|--------------------------------------------------------|----|

| 7.2.3 DMA PREEMPTION                                   | 46 |

| 7.3 Slave Timeouts                                     | 46 |

| 7.4 Arbitration During Non-Maskable Interrupts 14      | 46 |

| 8.0 INTERVAL TIMERS                                    |    |

| 8.1 Interval Timer Address Map 14                      | 47 |

| 8.2 Programming The Interval Timer 14                  | 48 |

| 9.0 INTERRUPT CONTROLLER 15                            |    |

| 9.1 Interrupt Controller Internal Registers 15         |    |

| 9.2 Interrupt Sequence                                 | 53 |

| 9.3 80x86 Mode 15                                      |    |

| 9.3.1 ESC INTERRUPT ACKNOWLEDGE CYCLE 15               |    |

| 9.4 Programming The Interrupt Controller 15            |    |

| 9.5 End-Of-Interrupt Operation                         |    |

| 9.5.1 END OF INTERRUPT (EOI) 15                        |    |

| 9.5.2 AUTOMATIC END OF INTERRUPT (AEOI) MODE           |    |

| 9.6 Modes Of Operation 15                              |    |

| 9.6.1 FULLY NESTED MODE 15                             |    |

| 9.6.2 THE SPECIAL FULLY NESTED MODE 16                 |    |

| 9.6.3 AUTOMATIC ROTATION (EQUAL PRIORITY DEVICES)      |    |

| 9.6.4 SPECIFIC ROTATION (SPECIFIC PRIORITY) 16         |    |

| 9.6.5 POLL COMMAND                                     |    |

| 9.6.6 CASCADE MODE 16                                  |    |

| 9.6.7 EDGE AND LEVEL TRIGGERED MODES 16                |    |

| 9.7 Register Functionality                             |    |

| 9.7.1 INITIALIZATION COMMAND WORDS                     |    |

| 9.7.2 OPERATION CONTROL WORDS (OCWS)                   |    |

| 9.8 Interrupt Masks                                    |    |

| 9.8.1 MASKING ON AN INDIVIDUAL INTERRUPT REQUEST BASIS |    |

| 9.8.2 SPECIAL MASK MODE                                |    |

| 9.9 Reading The Interrupt Controller Status            |    |

| 9.10 Non-Maskable Interrupt (NMI) 16                   |    |

| 10.0 ADVANCED PROGRAMMABLE INTERRUPT CONTROLLER (APIC) |    |

| 10.1 Physical Characteristics Of APIC Bus 16           |    |

| 10.2 Arbitration For APIC Bus                          |    |

| 10.3 Bus Message Formats 16                            | 69 |

### CONTENTS

### PAGE

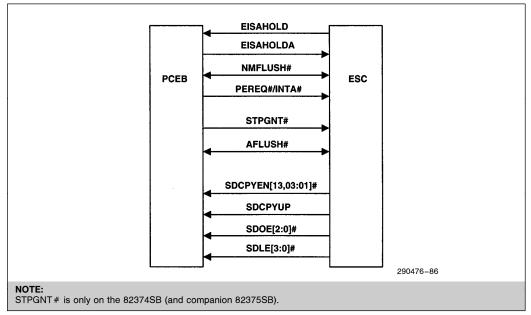

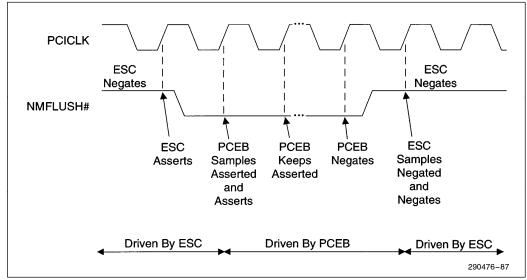

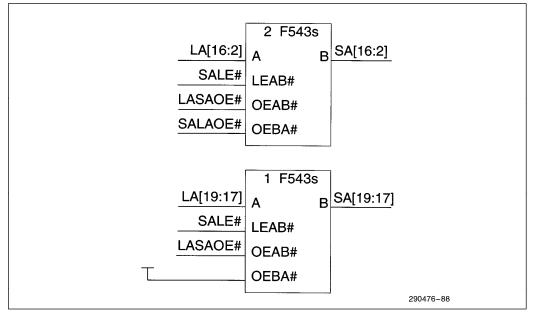

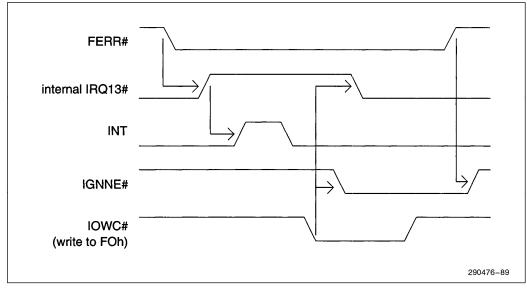

| 11.0 PCEB/ESC INTERFACE         11.1 Arbitration Control Signals         11.2 System Buffer Coherency Control—APIC         11.3 Power Management         11.4 EISA Data Swap Buffer Control Signals         11.5 Interrupt Acknowledge Control                                                                                                                                                                                                  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 12.0 INTEGRATED SUPPORT LOGIC         12.1 EISA Address Buffer Control         12.2 Coprocessor Interface         12.3 BIOS Interface         12.4 Keyboard Controller Interface         12.5 Real Time Clock         12.6 Floppy Disk Control Interface         12.7 Configuration RAM Interface         12.8 General Purpose Peripherals, IDE, Parallel Port, And Serial Port Interface         12.9 X-Bus Control And General Purpose Decode |  |

| ·                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| <ul> <li>13.0 POWER MANAGEMENT (82374SB)</li> <li>13.1 SMM Mode</li> <li>13.2 SMI Sources</li> <li>13.3 SMI # And INIT Interaction</li> <li>13.3.1 CLOCK CONTROL</li> <li>13.4 Stop Grant Special Cycle</li> <li>13.5 Dual-Processor Power Management Support</li> <li>13.5.1 SMI # DELIVERY MECHANISM</li> <li>13.5.2 STPCLK # TIED TO BOTH SOCKETS</li> <li>13.5.3 SMI # /INTR (APIC MODE)</li> </ul>                                         |  |

| <ul> <li>13.0 POWER MANAGEMENT (82374SB)</li> <li>13.1 SMM Mode</li> <li>13.2 SMI Sources</li> <li>13.3 SMI # And INIT Interaction</li> <li>13.3.1 CLOCK CONTROL</li> <li>13.4 Stop Grant Special Cycle</li> <li>13.5 Dual-Processor Power Management Support</li> <li>13.5.1 SMI # DELIVERY MECHANISM</li> <li>13.5.2 STPCLK # TIED TO BOTH SOCKETS</li> </ul>                                                                                 |  |

## intel

#### **1.0 ARCHITECTURAL OVERVIEW**

The PCI-EISA bridge chip set provides an I/O subsystem core for the next generation of high-performance personal computers (e.g., those based on the Intel486<sup>TM</sup> or Pentium<sup>®</sup> processors). System designers can take advantage of the power of the PCI (Peripheral Component Interconnect) for the local I/O bus while maintaining access to the large base of EISA and ISA expansion cards, and corresponding software applications. Extensive buffering and buffer management within the PCI-EISA bridge ensures maximum efficiency in both bus environments.

The chip set consists of two components—the 82375EB/SB PCI-EISA Bridge (PCEB) and the 82374EB/SB EISA System Component (ESC). These components work in tandem to provide an EISA I/O subsystem interface for personal computer platforms based on the PCI standard. This section provides an overview of the PCI and EISA Bus hierarchy followed by an overview of the PCEB and ESC components.

#### **Bus Hierarchy—Concurrent Operations:**

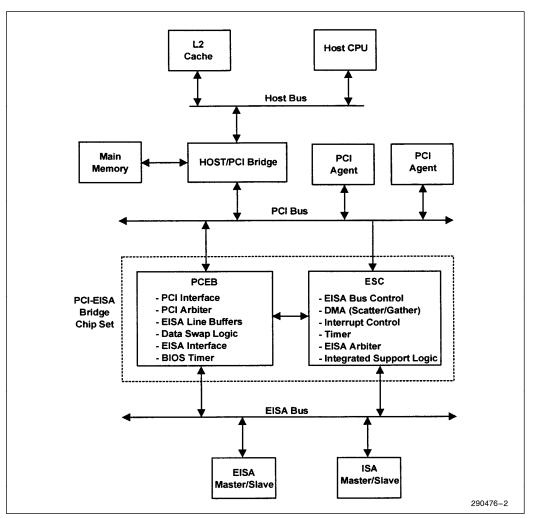

Figure 1 shows a block diagram of a typical system using the PCI-EISA Bridge chip set. The system contains three levels of buses structured in the following hierarchy:

- Host Bus as the execution bus

- PCI Bus as a primary I/O bus

- EISA Bus as a secondary I/O bus

This bus hierarchy allows concurrency for simultaneous operations on all three bus environments. Data buffering permits concurrency for operations that cross over into another bus environment. For example, a PCI device could post data into the PCEB, permitting the PCI Local Bus transaction to complete in a minimum time and freeing up the PCI Local Bus for further transactions. The PCI device does not have to wait for the transfer to complete to its final destination. Meanwhile, any ongoing EISA Bus transactions are permitted to complete. The posted data is then transferred to its EISA Bus destination when the EISA Bus is available. The PCI-EISA Bridge chip set implements extensive buffering for PCI-to-EISA and EISA-to-PCI bus transactions. In addition to concurrency for the operations that cross bus environments, data buffering allows the fastest operations within a particular bus environment (via PCI burst transfers and EISA burst transfers).

The PCI Local Bus with 132 MByte/sec and EISA with 33 MByte/sec peak data transfer rate represent bus environments with significantly different bandwidths. Without buffering, transfers that cross the single bus environment are performed at the speed of the slower bus. Data buffers provide a mechanism for data rate adoption so that the operation of the fast bus environment (PCI), i.e. usable bandwidth, is not significantly impacted by the slower bus environment (EISA).

## intel

Figure 1. PCI-EISA Chip Set System Block Diagram

## intel

#### PCI Bus

The PCI Bus has been defined to address the growing industry needs for a standardized *local bus* that is not directly dependent on the speed and the size of the processor bus. New generations of personal computer system software such as Windows™ and Win-NT™ with sophisticated graphical interfaces, multi-tasking and multi-threading bring new requirements that traditional PC I/O architectures can not satisfy. In addition to the higher bandwidth, reliability and robustness of the I/O subsystem is becoming increasingly important. The PCI environment addresses these needs and provides an upgrade path for the future. PCI features include:

- Processor independent

- · Multiplexed, burst mode operation

- Synchronous at frequencies from 20-33 MHz

- 120 MByte/sec usable throughput (132 MByte/sec peak) for 32 bit data path

- 240 MByte/sec usable throughput (264 MByte/sec peak) for 64 bit data path

- Optional 64 bit data path with operations that are transparent with the 32 bit data path

- · Low latency random access (60 ns write access latency to slave registers from a master parked on the bus)

- · Capable of full concurrency with processor/memory subsystem

- Full multi-master capability allowing any PCI master peer-to-peer access to any PCI slave

- Hidden (overlapped) central arbitration

- · Low pin count for cost effective component packaging (address/data multiplexed)

- Address and data parity

- Three physical address spaces: memory, I/O, and configuration

- · Comprehensive support for autoconfiguration through a defined set of standard configuration functions

System partitioning shown in Figure 1 illustrates how the PCI can be used as a common interface between different portions of a system platform that are typically supplied by the chip set vendor. These portions are the Host/PCI Bridge (including a main memory DRAM controller and an optional second level cache controller) and the PCI-EISA Bridge. Thus, the PCI allows a system I/O core design to be decoupled from the processor/ memory treadmill, enabling the I/O core to provide maximum benefit over multiple generations of processor/ memory technology. For this reason, the PCI-EISA Bridge can be used with different processors. Regardless of the new requirements imposed on the processor side of the Host/PCI Bridge (e.g. 64-bit data path, 3.3V interface, etc.) the PCI-EISA Bridge but also of all other I/O functions interfaced at the PCI level. These functions typically include graphics, SCSI, and LAN.

#### **EISA Bus**

The EISA bus in the system shown in the Figure 1.0 represents a second level I/O bus. It allows personal computer platforms built around the PCI as a primary I/O bus to leverage the large EISA/ISA product base. Combinations of PCI and EISA buses, both of which can be used to provide expansion functions, will satisfy even the most demanding applications.

Along with compatibility with 16-bit and 8-bit ISA hardware and software, the EISA bus provides the following key features:

- 32-bit addressing and 32-bit data path

- 33 MByte/sec bus bandwidth

- · Multiple bus master support through efficient arbitration

- Support for autoconfiguration

#### Integrated Bus Central Control Functions

The PCI-EISA Bridge chip set integrates central bus functions on both the PCI and EISA Buses. For the PCI Bus, the functions include PCI bus arbitration and default bus driver. For the EISA Bus, central functions include the EISA Bus controller and EISA arbiter are integrated in the ESC component and EISA Data Swap Logic is integrated in the PCEB.

#### Integrated System Functions

The PCI-EISA Bridge chip set integrates system functions including PCI parity and system errors reporting, buffer coherency management protocol, PCI and EISA memory and I/O address space mapping and decoding. For maximum flexibility all of these functions are programmable allowing for variety of optional features.

#### 1.1 PCEB Overview

The PCEB provides the interface (bridge) between PCI and EISA buses by translating bus protocols in both directions. It uses extensive buffering on both the PCI and EISA interfaces to allow concurrent bus operations. The PCEB also implements the PCI central support functions (e.g., PCI arbitration, error signal support, and subtractive decoding). The major functions provided by the PCEB are described in this section.

#### **PCI Bus Interface**

The PCEB can be either a master or slave on the PCI Bus and supports bus frequencies from 25 MHz to 33 MHz. For PCI-initiated transfers, the PCEB can only be a slave. The PCEB becomes a slave when it positively decodes the cycle. The PCEB also becomes a slave for unclaimed cycles on the PCI Bus. These unclaimed cycles are either negatively or subtractively decoded by the PCEB and forwarded to the EISA Bus.

As a slave, the PCEB supports single cycle transfers for memory, I/O, and configuration operations and burst cycles for memory operations. Note that, burst transfers cannot be performed to the PCEB's internal registers. Burst memory write cycles to the EISA Bus can transfer up to four Dwords, depending on available space in the PCEB's Posted Write Buffers. When space is no longer available in the buffers, the PCEB terminates the transaction. This supports the Incremental Latency Mechanism as defined in the Peripheral Component Interconnect (PCI) Specification. Note that, if the Posted Write Buffers are disabled, PCI burst operations are not performed and all transfers are single cycle.

For EISA-initiated transfers to the PCI Bus, the PCEB is a PCI master. The PCEB permits EISA devices to access either PCI memory or I/O. While all PCI I/O transfers are single cycle, PCI memory cycles can be either single cycle or burst, depending on the status of the PCEB's Line Buffers. During EISA reads of PCI memory, The PCEB uses a burst read cycle of four Dwords to prefetch data into a Line Buffer. During EISA-to-PCI memory writes, the PCEB uses PCI burst cycles to flush the Line Buffers. The PCEB contains a programmable Master Latency Timer that provides the PCEB with a guaranteed time slice on the PCI Bus, after which it surrenders the bus.

As a master on the PCI Bus, the PCEB generates address and command signal (C/BE#) parity for read and write cycles, and data parity for write cycles. As a slave, the PCEB generates data parity for read cycles. Parity checking is not supported.

The PCEB, as a resource, can be locked by any PCI master. In the context of locked cycles, the entire PCEB subsystem (including the EISA Bus) is considered a single resource.

## intel

#### **PCI Bus Arbitration**

The PCI arbiter supports six PCI masters—The Host/PCI bridge, PCEB, and four other PCI masters. The arbiter can be programmed for twelve fixed priority schemes, a rotating scheme, or a combination of the fixed and rotating schemes. The arbiter can be programmed for bus parking that permits the Host/PCI Bridge default access to the PCI Bus when no other device is requesting service. The arbiter also contains an efficient PCI retry mechanism to minimize PCI Bus thrashing when the PCEB generates a retry. The arbiter can be disabled, if an external arbiter is used.

#### **EISA Bus Interface**

The PCEB contains a fully EISA-compatible master and slave interface. The PCEB directly drives eight EISA slots without external data or address buffering. The PCEB is only a master or slave on the EISA Bus for transfers between the EISA Bus and PCI Bus. For transfers contained to the EISA Bus, the PCEB is never a master or slave. However, the data swap logic contained in the PCEB is involved in these transfers, if data size translation is needed. The PCEB also provide support for I/O recovery.

EISA/ISA masters and DMA can access PCI memory or I/O. The PCEB only forwards EISA cycles to the PCI Bus if the address of the transfer matches one of the address ranges programmed into the PCEB for EISA-to-PCI positive decode. This includes the main memory segments used for generating MEMCS# from the EISA Bus, one of the four programmable memory regions, or one of the four programmable I/O regions. For EISA-initiated accesses to the PCI Bus, the PCEB is a slave on the EISA Bus. I/O accesses are always non-buffered and memory accesses can be either non-buffered or buffered via the Line Buffers. For buffered accesses, burst cycles are supported.

During PCI-initiated cycles to the EISA Bus, the PCEB is an EISA master. For memory write operations through the Posted Write Buffers, the PCEB uses EISA burst transfers, if supported by the slave, to flush the buffers. Otherwise, single cycle transfers are used. Single cycle transfers are used for all I/O cycles and memory reads.

#### PCI/EISA Address Decoding

The PCEB contains two address decoders—one to decode PCI-initiated cycles and the other to decode EISA-initiated cycles. The two decoders permit the PCI and EISA Buses to operate concurrently.

The PCEB can also be programmed to provide main memory address decoding on behalf of the Host/PCI bridge. When programmed, the PCEB monitors the PCI and EISA bus cycle addresses, and generates a memory chip select signal (MEMCS#) indicating that the current cycle is targeted to main memory residing behind the Host/PCI bridge. Programmable features include, read/write attributes for specific memory segments and the enabling/disabling of a memory hole. If MEMCS# is not used, this feature can be disabled.

In addition to the main memory address decoding, there are four programmable memory regions and four programmable I/O regions for EISA-initiated cycles. EISA/ISA master or DMA accesses to one of these regions are forwarded to the PCI Bus.

#### **Data Buffering**

To isolate the slower EISA Bus from the PCI Bus, the PCEB provides two types of data buffers. Buffer management control guarantees data coherency.

For EISA-initiated cycles to the PCI Bus, there are four 16-byte wide Line Buffers. These buffers permit prefetching of PCI memory read data and posting of PCI memory write data.

By using burst transactions to fill or flush these buffers, if appropriate, the PCEB maximizes bus efficiency. For example, an EISA device could fill a Line Buffer with byte, word, or Dword transfers and The PCEB would use a PCI burst cycle to flush the filled line to PCI memory.

#### **BIOS Timer**

The PCEB has a 16 bit BIOS Timer. The timer can be used by BIOS software to implement timing loops. The timer count rate is derived from the EISA clock (BCLK) and has an accuracy of  $\pm 1 \ \mu$ s.

#### 1.2 ESC Overview

The ESC implements system functions (e.g., timer/counter, DMA, and interrupt controller) and EISA subsystem control functions (e.g., EISA bus controller and EISA bus arbiter). The major functions provided by the ESC are described in this section.

#### **EISA Controller**

The ESC incorporates a 32-bit master and an 8-bit slave. The ESC directly drives eight EISA slots without external data or address buffering. EISA system clock (BCLK) generation is integrated by dividing the PCI clock (divide by 3 or divide by 4) and wait-state generation is provided. The AENx and MACKx signals provide a direct interface to four EISA slots and supports eight EISA slots with encoded AENx and MACKx signals.

The ESC contains an 8-bit data bus (lower 8 bits of the EISA data bus) that is used to program the ESC's internal registers. Note that for transfers between the PCI and EISA Buses, the PCEB provides the data path. Thus, the ESC does not require a full 32 bit data bus. A full 32-bit address bus is provided and is used during refresh cycles and for DMA operations.

The ESC performs cycle translation between the EISA Bus and ISA Bus. For mis-matched master/slave combinations, the ESC controls the data swap logic that is located in the PCEB. This control is provided through the PCEB/ESC interface.

#### **DMA Controller**

The ESC incorporates the functionality of two 82C37 DMA controllers with seven independently programmable channels. Each channel can be programmed for 8 or 16 bit DMA device size, and ISA-compatible, type "A", type "B", or type "C" timings. Full 32 bit addressing is provided. The DMA controller is also responsible for generating refresh cycles.

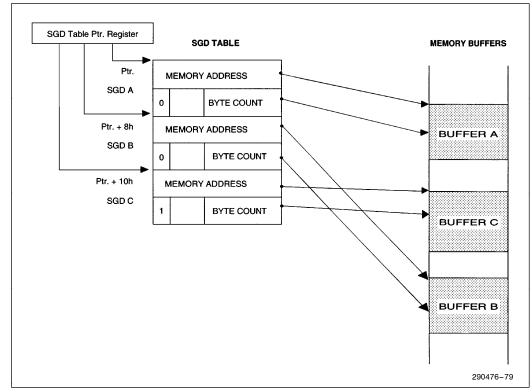

The DMA controller supports an enhanced feature called scatter/gather. This feature provides the capability of transferring multiple buffers between memory and I/O without CPU intervention. In scatter/gather mode, the DMA can read the memory address and word count from an array of buffer descriptors, located in main memory, called the scatter/gather descriptor (SGD) table. This allows the DMA controller to sustain DMA transfers until all of the buffers in the SGD table are handled.

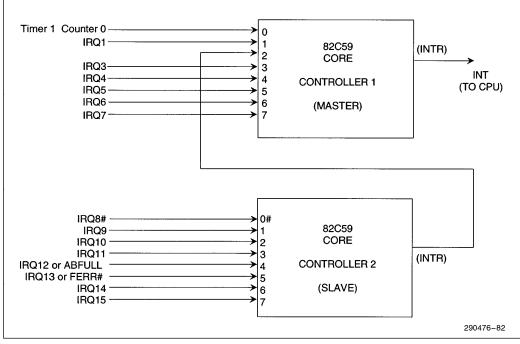

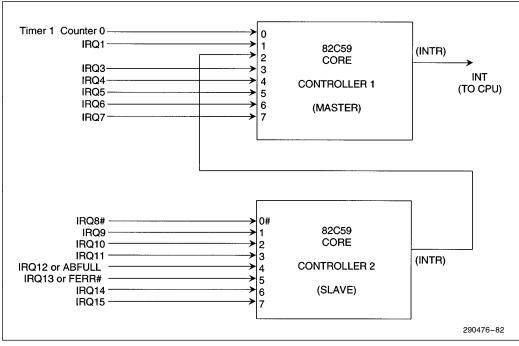

#### Interrupt Controller

The ESC contains an EISA compatible interrupt controller that incorporates the functionality of two 82C59 Interrupt Controllers. The two interrupt controllers are cascaded providing 14 external and two internal interrupts.

## intel

#### Advanced Programmable Interrupt Controller (APIC)

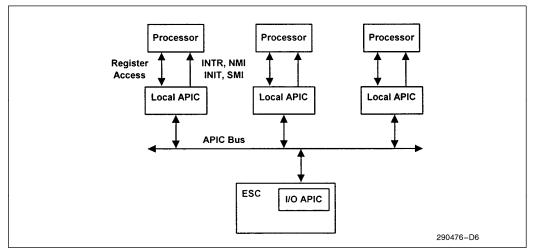

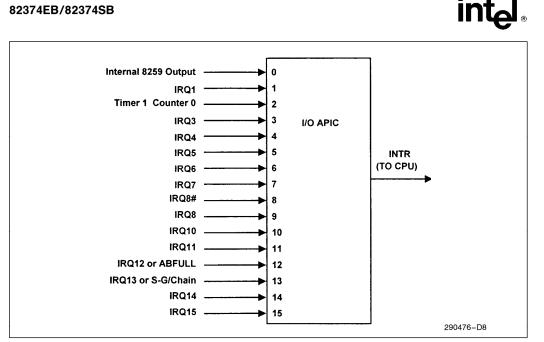

In addition to the standard EISA compatible interrupt controller described above, the ESC incorporates the Advanced Programmable Interrupt Controller (APIC). While the standard interrupt controller is intended for use in a uni-processor system, APIC can be used in either a uni-processor or multi-processor system. APIC provides multi-processor interrupt management and incorporates both static and dynamic symmetric interrupt distribution across all processors. In systems with multiple I/O subsystems, each subsystem can have its own set of interrupts.

#### Timer/Counter

The ESC provides two 82C54 compatible timers (Timer 1 and Timer 2). The counters in Timer 1 support the system timer interrupt (IRQ0#), refresh request, and a speaker tone output (SPKR). The counters in Timer 2 support fail-safe timeout functions and the CPU speed control.

#### **Integrated Support Logic**

To minimize the chip count for board designs, the ESC incorporates a number of extended features. The ESC provides support for ALTA20 (Fast A20GATE) and ALTRST with I/O Port 92h. The ESC generates the control signals for SA address buffers and X-Bus buffer. The ESC also provides chip selects for BIOS, the keyboard controller, the floppy disk controller, and three general purpose devices. Support for generating chip selects with an external decoder is provided for IDE, a parallel port, and a serial port. The ESC provides support for a PC/AT compatible coprocessor interface and IRQ13 generation.

#### Power Management (82374SB)

Extensive power management capability permits a system to operate in a low power state without being powered down. Once in the low power state (called "Fast Off" state), the computer appears to be off. For example, the SMM code could turn off the CRT, line printer, hard disk drive's spindle motor, and fans. In addition, the CPU's clock can be governed. To the user, the machine appears to be in the off state. However, the system is actually in an extremely low power state that still permits the CPU to function and maintain communication connections normally associated with today's desktops (e.g., LAN, Modem, or FAX). Programmable options provide power management flexibility. For example, various system events can be programmed to place the system in the low power state or break events can be programmed to wake the system up.

#### 2.0 SIGNAL DESCRIPTION

This section provides a detailed description of each signal. The signals are arranged in a functional group according to their associated interface.

The "#" symbol at the end of a signal indicates that the active, or asserted state occurs when the signal is at a low voltage level. When "#" is not presented after the signal name, the signal is asserted when at the high voltage level.

The terms assertion and negation are used extensively. This is done to avoid confusion when working with a mixture of "active-low" and "active-high" signals. The term **assert**, or **assertion** indicates that a signal is active, independent of whether that level is represented by a high or low voltage. The term **negate**, or **negation** indicates that a signal is inactive.

The following notations are used to describe the signal type.

- in Input is a standard input-only signal.

- out Totem Pole Output is a standard active driver.

- o/d Open Drain Input/Output.

- t/s Tri-State is a bi-directional, tri-state input/output pin.

- s/t/s Sustained Tri-State is an active low tri-state signal owned and driven by one and only one agent at a time. The agent that drives a s/t/s pin low must drive it high for at least one clock before letting it float. A new agent can not start driving a s/t/s signal any sooner than one clock after the previous owner tri-states it. A pull-up sustains the inactive state until another agent drives it and is provided by the central resource.

#### NOTE:

During a hard reset, INTR, NMI, IGNNE#, SMI# (on 82374SB), ALTRST#, STPCLK# (on 82374SB) and ALTA20 are driven low to prevent problems associated with 5V/3.3V power sequencing. Any outputs of the ESC that are directed to a 3.3V CPU must be driven through a 5V to 3.3V translator.

| Pin Name | Туре | Description                                                                                                                                                                                                                                                                                                                                                 |

|----------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCICLK   | in   | <b>PCI CLOCK:</b> PCICLK provides timing for all transactions on the PCI bus. The ESC uses the PCI Clock (PCICLK) to generate EISA Bus Clock (BCLK). The PCICLK is divided by 3 or 4 to generate the BCLK. The EISA Bridge supports PCI Clock frequencies of 25 MHz through 33 MHz.                                                                         |

| PERR#    | in   | <b>PARITY ERROR:</b> PERR # indicates a data parity error. PERR # may be pulsed active by any agent that detects an error condition. Upon sampling PERR # active, the ESC generates an NMI interrupt to the CPU.                                                                                                                                            |

| SERR#    | in   | <b>SYSTEM ERROR:</b> SERR # may be pulsed active by any agent that detects an error condition. Upon sampling SERR # active, the ESC generates an NMI interrupt to the CPU.                                                                                                                                                                                  |

| RESET#   | in   | <b>SYSTEM RESET:</b> RESET # forces the entire ESC chip into a known state. All internal ESC state machines are reset and all registers are set to their default values. RESET # may be asynchronous to PCICLK when asserted or negated. Although asynchronous, negation must be a clean, bounce-free edge. The ESC uses RESET # to generate RSTDRV signal. |

#### 2.1 PCI Local Bus Interface Signals

#### 2.2 EISA Bus Interface Signals

| Pin Name | Туре | Description                                                                                                                                                                                                                                                                                    |

|----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BCLKOUT  | out  | <b>EISA BUS CLOCK OUTPUT</b> : BCLKOUT is typically buffered to create EISA Bus Clock (BCLK). The BCLK is the system clock used to synchronize events on the EISA/ISA bus. The BCLKOUT is generated by dividing the PCICLK. The ESC uses a divide by 3 or divide by 4 to generate the BCLKOUT. |

| BCLK     | in   | <b>EISA BUS CLOCK</b> : The ESC uses BCLK to synchronize events on the EISA bus. The ESC generates or samples all the EISA/ISA bus signals on either the rising or the falling edge of BCLK.                                                                                                   |

## intel®

| Pin Name                       | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LA[31:27] # /<br>CPG[4:0]      | t/s  | <b>EISA ADDRESS BUS/CONFIGURATION RAM PAGE ADDRESS</b> : These are multiplexed signals. These signals behave as the EISA address bus under all conditions except during access cycle to the Configuration RAM.                                                                                                                                                                                                         |

|                                |      | EISA Address Bus: LA[31:27] # are directly connected to the EISA address bus.<br>The ESC uses the address bus in conjunction with the BE[3:0] # signals as inputs to<br>decode accesses to its internal resources except in DMA and Refresh modes.<br>During DMA and Refresh modes, these are outputs, and the ESC uses these signals<br>in conjunction with BE[3:0] # to drive Memory address.                        |

|                                |      | Configuration Ram Page Address: CPG[4:0] are connected to Configuration SRAM address lines. During I/O access to 0800h-08FFh, the ESC drives these signals with the configuration page address (the value contained in register 0C00h). The Configuration RAM Page Address function can be disabled by setting Mode Select register bit $5 = 0$ .                                                                      |

| LA[26:24] #<br>and<br>LA[23:2] | t/s  | <b>EISA ADDRESS BUS</b> : These signals are directly connected to the EISA address bus. The ESC uses the address bus in conjunction with the BE[3:0] # signals as inputs to decode accesses to its internal resources except in DMA and Refresh modes. During DMA and Refresh modes, these are outputs, and the ESC uses these signals in conjunction with BE[3:0] # to drive Memory address.                          |

| BE[3:0] #                      | t/s  | <b>BYTE ENABLES:</b> BE[3:0] # signals are directly connected to the EISA address bus.<br>These signals indicate which byte on the 32-bit EISA data bus are involved in the<br>current cycle. BE[3:0] # are inputs during EISA master cycles which do not require<br>assembly/disassembly operation. For EISA master assembly/disassembly cycles,<br>ISA master cycles, DMA, and Refresh cycles BE[3:0] # are outputs. |

|                                |      | BE0 #: Corresponds to byte lane 0-SD[7:0]<br>BE1 #: Corresponds to byte lane 0-SD[15:8]<br>BE2 #: Corresponds to byte lane 0-SD[23:16]<br>BE3 #: Corresponds to byte lane 0-SD[31:24]                                                                                                                                                                                                                                  |

| M/IO#                          | t/s  | <b>MEMORY OR I/O CYCLE:</b> M/IO # signal is used to differentiate between memory cycles and I/O cycles on the EISA bus. A High value on this signal indicates a memory cycle, and a Low value indicates an I/O cycle. M/IO# is an input to the ESC during EISA master cycles, and M/IO# is an output during ISA, DMA, and ESC initiated Refresh cycles. M/IO# is floated during ISA master initiated Refresh cycles.  |

| W/R#                           | t/s  | <b>WRITE OR READ CYCLE:</b> W/R# signal is used to differentiate between write and read cycles on the EISA bus. A High value on this signal indicates a Write cycle , and a Low value indicates a Read cycle. W/R# is an input to the ESC during EISA master cycles, and W/R# is an output during ISA, DMA, and Refresh cycles.                                                                                        |

| Pin Name | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EX32#    | o/d  | <b>EISA 32 BIT DEVICE DECODE</b> : EX32 # signal is asserted by a 32-bit EISA slave device. EX32 # assertion indicates that an EISA device has been selected as a slave, and the device has a 32-bit data bus size. The ESC uses this signal as an input as part of its slave decode to determine if data size translation and/or cycle translation is required. EX32 # is an output of the ESC during the last portion of the mis-matched cycle. This is an indication to the backed-off EISA master that the data translation has been completed. The backed-off EISA master uses this signal to start driving the EISA bus again.                                                                                                                                                                                                                                                   |

| EX16#    | o/d  | <b>EISA 16-BIT DEVICE DECODE:</b> EX16# signal is asserted by a 16-bit EISA slave device. EX16# assertion indicates that an EISA device has been selected as a slave, and the device has a 16 bit data bus size. The ESC uses this signal as an input as part of its slave decode to determine if data size translation and/or cycle translation is required. EX16# is an output of the ESC during the last portion of the mis-matched cycle. This is an indication to the backed-off EISA master that the data translation has been completed. The backed-off EISA master uses this signal to start driving the EISA bus again.                                                                                                                                                                                                                                                       |

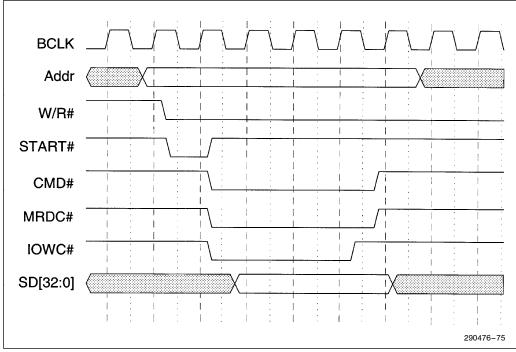

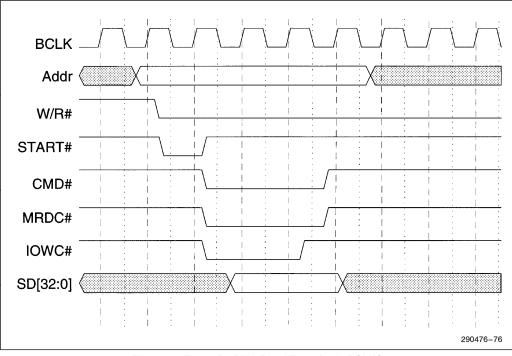

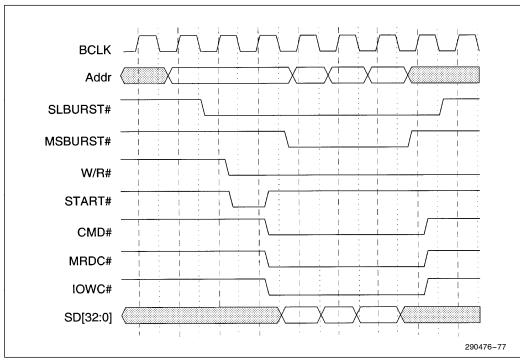

| START#   | t/s  | <b>START CYCLE:</b> START # signal provides timing control at the start of an EISA cycle.<br>START # is asserted for one BCLK. START # is an input to the ESC during EISA<br>master cycles except portions of the EISA master to mis-matched slave cycles where<br>it becomes an output. During ISA, DMA, and Refresh cycles START # is an output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| CMD#     | out  | <b>COMMAND:</b> CMD# signal provides timing control within an EISA cycle. The ESC is a central resource of the CMD# signal, and the ESC generates CMD# during all EISA cycles. CMD# is asserted from the rising edge of BCLK simultaneously with the negation of START#, and remains asserted until the end of the cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| EXRDY    | o/d  | <b>EISA READY:</b> EXRDY signal is deasserted by EISA slave devices to add wait states to a cycle. EXRDY is an input to the ESC for EISA master cycles, ISA master cycles, and DMA cycles where an EISA slave has responded with EX32# or EX16# asserted. The ESC samples EXRDY on the falling edge of BCLK after CMD# is asserted (except during DMA compatible cycles). During DMA compatible cycles, EXRDY is sampled on the second falling edge of BCLK after CMD# is driven active. For all types of cycles if EXRDY is sampled inactive, the ESC keeps sampling it on every falling edge of BCLK#. EXRDY is an output for EISA master cycles decoded as accesses to the ESC internal registers. ESC forces EXRDY low for one BCLK at the start of a potential DMA burst write cycle to insure that the initial write data is held long enough to be sampled by the memory slave. |

| SLBURST# | in   | <b>SLAVE BURST:</b> SLBURST # signal is asserted by an EISA slave to indicate that the device is capable of accepting EISA burst cycles. The ESC samples SLBURST # on the rising edge of BCLK at the end of START # for all EISA cycles. During DMA cycles, the ESC samples SLBURST # twice; once on the rising edge of BCLK at the beginning of START # and again on the rising edge of BCLK at the end of START #.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

# intel

| Pin Name  | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MSBURST#  | t/s  | <b>MASTER BURST:</b> MSBURST # signal is asserted by an EISA master to indicate<br>EISA burst cycles. MSBURST # is asserted by an EISA master in response to an<br>asserted SLBURST # signal. The ESC samples SLBURST # on the rising edge of<br>BCLK that CMD # is asserted. If asserted, the ESC samples SLBURST # on all<br>subsequent rising edges of BCLK until sampled negated. The ESC keeps CMD #<br>asserted during Burst cycles. MSBURST # is an output during DMA burst cycles.<br>The ESC drives MSBURST # active on the falling edge of BCLK, one half BCLK<br>after SLBURST # is sampled active at the end of START #.                                                                                                                     |

| MASTER16# | in   | <b>MASTER 16-BIT:</b> MASTER16# is asserted by a 16-bit EISA Bus master or an ISA<br>Bus master device to indicate that it has control of the EISA Bus or ISA Bus. The<br>ESC samples MASTER16# on the rising edge of BCLK that START# is asserted. If<br>MASTER16# is sampled asserted, the ESC determines that a 16-bit EISA Bus<br>master or an ISA Bus master owns the Bus. If MASTER16# is sampled negated at<br>the first sampling point, the ESC will sample MASTER16# a second time on the<br>rising edge of BCLK at the end of START#. If MASTER16# is sampled asserted<br>here, the ESC determines that a 32-bit EISA Bus master has downshifted to a 16-bit<br>Bus master, and thus, the ESC will disable the data size translation function. |

| SD[7:0]   | t/s  | <b>SYSTEM DATA:</b> SD[7:0] signals are directly connected to the System Data bus.<br>The SD[7:0] pins are outputs during I/O reads when the ESC internal registers are<br>being accessed and during interrupt acknowledge cycles. The SD[7:0] pins are<br>input during I/O writes cycles when the ESC internal registers are being accessed.                                                                                                                                                                                                                                                                                                                                                                                                            |

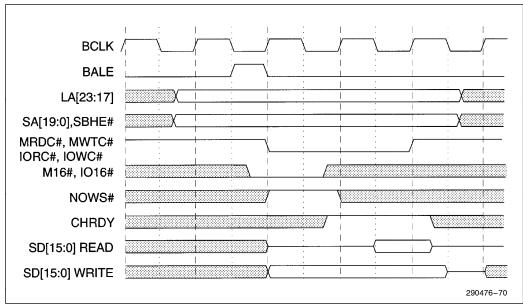

### 2.3 ISA Bus Signals

| Pin Name | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BALE     | out  | <b>BUS ADDRESS LATCH ENABLE:</b> BALE signal is asserted by the ESC to indicate that a address (SA[19:0], LA[23:17]), AEN and SBHE# signal lines are valid. The LA[23:17] address lines are latched on the trailing edge of BALE. BALE remains active throughout DMA and ISA Master cycles and Refresh cycles.                                                                                                                        |

| SA[1:0]  | t/s  | <b>ISA ADDRESS BITS 0&amp; 1:</b> SA[1:0] are the least significant bits of the ISA address bus.<br>SA[1:0] are inputs to the ESC during ISA master cycles except during ISA master<br>initiated Refresh cycles. The ESC uses the SA[1:0] in conjunction with SBHE# to<br>generate BE[3:0] # on the EISA bus. The SA[1:0] are outputs of the ESC during EISA<br>master cycles and DMA cycles. The ESC generates these from BE[3:0] #. |

| SBHE #   | t/s  | <b>ISA BYTE HIGH ENABLE:</b> SBHE# signal indicates that the high byte on the ISA data bus (SD[15:8]) is valid. SBHE# is an input to the ESC during ISA master cycles, except during ISA master initiated Refresh cycles. The ESC uses the SBHE# in conjunction with SA[1:0] to generate BE[3:0] # on the EISA bus. SBHE# is an output during EISA master and DMA cycles.                                                             |

| Pin Name | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| M16#     | o/d  | <b>MEMORY CHIP SELECT 16:</b> M16# is an input when the ESC component owns the ISA bus. M16# is an output when an external ISA bus Master owns the ISA bus. The ISA slave memory drives this signal Low if it is a 16-bit memory device. For ISA to EISA translation cycles, the ESC combinatorially asserts M16# if either EX32# or EX16# are asserted. This signal has an external pull-up resistor.                |

| IO16#    | o/d  | <b>16 BIT I/O CHIP SELECT:</b> IO16 # signal is used to indicate a 16-bit I/O bus cycle. This signal is asserted by the I/O devices to indicate that they support 16-bit I/O bus cycles. All I/O accesses to the ESC registers are run as 8-bit I/O bus cycles. This signal has an external pull-up resistor.                                                                                                         |

| MRDC#    | t/s  | <b>MEMORY READ:</b> MRDC# signal indicates a read cycle to the ISA memory devices.<br>MRDC# is the command to a memory slave that it may drive data onto the ISA data<br>bus. MRDC# is an output when the ESC owns the ISA bus. MRDC# is an input when<br>an external ISA Bus master owns the ISA Bus. This signal is driven by the ESC during<br>refresh cycles.                                                     |

| MWTC#    | t/s  | <b>MEMORY WRITE:</b> MWTC# signal indicates a write cycle to the ISA memory devices.<br>MWTC# is the command to a memory slave that it may latch data from the ISA data<br>bus. MWTC# is an output when the ESC owns the ISA bus. MWTC# is an input when<br>an ISA Bus master owns the ISA Bus.                                                                                                                       |

| SMRDC#   | out  | <b>SYSTEM MEMORY READ:</b> SMRDC# signal is asserted by the ESC to request a memory slave to drive data onto the data lines. SMRDC# indicates that the memory read cycle is for an address below the 1 MByte range on the ISA bus. This signal is also asserted during refresh cycles.                                                                                                                                |

| SMWTC#   | out  | <b>SYSTEM MEMORY WRITE:</b> SMWTC# signal is asserted by the ESC to request a memory slave to accept data from the data lines. SMWTC# indicates that the memory write cycle is for an address below the 1 MByte range.                                                                                                                                                                                                |

| IORC#    | t/s  | <b>I/O READ:</b> IORC# is the command to an ISA I/O slave device that it may drive data on to the data bus (SD[15:0]). The device must hold the data valid until after IORC# is negated. IORC# is an output when the ESC component owns the ISA bus. IORC# is an input when an ISA Bus master owns the ISA Bus.                                                                                                       |

| IOWC#    | t/s  | <b>I/O WRITE:</b> IOWC# is the command to an ISA I/O slave device that it may latch data from the ISA data bus (SD[15:0]). IOWC# is an output when the ESC component owns the ISA Bus. IOWC# is an input when an ISA Bus master owns the ISA Bus.                                                                                                                                                                     |

| CHRDY    | o/d  | I/O CHANNEL READY: CHRDY when asserted allows ISA Bus resources request<br>additional time (wait-states) to complete the cycle. CHRDY is an input when the ESC<br>owns the ISA Bus. CHRDY is an input to the ESC during compatible DMA cycles.<br>CHRDY is an output during ISA Bus master cycles to PCI slave or ESC internal register.<br>The ESC will ignores CHRDY for ISA-Bus master accessing an ISA-Bus slave. |

| IOCHK#   | in   | <b>I/O CHANNEL CHECK:</b> IOCHK # can be asserted by any resource on the ISA Bus.<br>When asserted, it indicates that a parity or an uncorrectable error has occurred for a device or memory on the ISA Bus. A NMI will be generated to the CPU if enabled.                                                                                                                                                           |

\_

## intel

| Pin Name               | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NOWS#                  | o/d  | <b>ZERO WAIT STATES:</b> NOWS # indicates that an peripheral device wishes to execute a zero wait-state bus cycle (the normal default 16-bit ISA bus memory or I/O cycle is 3 BCLKS). When NOWS # is asserted, a 16-bit memory cycle will occur in two BCLKs and a 16-bit I/O cycle will occur in three BCLKs. When NOWS # is asserted by an 8-bit device the default 6 BCLKs cycle is shortened to 4 or 5 BCLKs.                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                        |      | NOWS # is an input when the ESC performing bus translation cycles. NOWS # is an output when the ESC internal registers are accessed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                        |      | If CHRDY and NOWS# are both asserted during the same clock then NOWS# will be ignored and wait-states will be added as a function of CHRDY (CHRDY has precedence over NOWS#).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| OSC                    | in   | <b>OSCILLATOR:</b> OSC is the 14.31818 MHz signal with 50% duty cycle. OSC is used by the ESC timers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| RSTDRV                 | out  | <b>RESET DRIVE:</b> RSTDRV is asserted by the ESC. An asserted RSTDRV causes a hardware reset of the devices on the ISA Bus. RSTDRV is asserted whenever the RESET# input to the ESC is asserted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

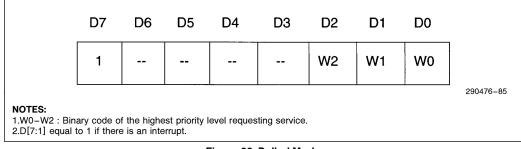

| REFRESH#               | t/s  | <b>REFRESH:</b> REFRESH# is used by the ESC as an output to indicate when a refresh cycle is in progress. It should be used to enable the SA[15:0] address to the row address inputs of all banks of dynamic memory on the ISA bus so that when MRDC# goes active, the entire expansion bus dynamic memory is refreshed. Memory slaves must not drive any data onto the bus during refresh and should not add wait states since this will affect the entire system throughput. As an output, this signal is driven directly onto the ISA bus. This signal is an output only when the ESC DMA Refresh is a master on the bus responding to an internally generated request for Refresh. Upon RESET this pin will tristate. Note that address lines [15:8] are driven during refresh, but the value is meaningless and is not used to refresh ISA bus memory. |