# SIEMENS

# Preliminary SAB 8284B, SAB 8284B-1 Clock Generator and Driver for SAB 8086 Family Processors

- Fully compatible with SAB 8284A, SAB 8284A-1

- 30% Less Power Supply Current than Standard SAB 8284A, SAB 8284A-1

- Generates the System clock for SAB 8086 and SAB 8088 Processors: upto 8 MHz with SAB 8284B upto 10 MHz with SAB 8284B-1

- Uses a Crystal or a TTL Signal for Frequency Source upto 30 MHz

- Provides Synchronization for Synchronous and Asynchronous READY Signals

- 18-Pin Package

- Single +5V Power Supply

- Generates System Reset Output from Schmitt Trigger Input

- Capable of Clock Synchronization with Other SAB 8284Bs

| Figure 1             |              |                      | Pin Names                            |                                                   |

|----------------------|--------------|----------------------|--------------------------------------|---------------------------------------------------|

| Pin Configuration    |              |                      | X <sub>1</sub> X <sub>2</sub>        | Connections for crystal                           |

|                      |              |                      | F/C                                  | Clock source select                               |

| <u>-</u>             | ~            |                      | EFI                                  | External clock input                              |

| CYSNC 🗌 1            |              | 18 🗀 V <sub>CC</sub> | CSYNC                                | Clock synchronization input                       |

| PCLK ☐ 2             |              | 17 🗀 X <sub>1</sub>  | ASYNC                                | Ready synchronization select                      |

| ĀĒN₁ ☐ 3             |              | 16 🗆 X <sub>2</sub>  | RDY <sub>1</sub><br>RDY <sub>2</sub> | Ready signal                                      |

| RDY <sub>1</sub> ☐ 4 | 040          | 15 ASYNC             | AEN,<br>AEN <sub>2</sub>             | Address enabled qualifiers for RDY <sub>1,2</sub> |

| READY 5              | SAB<br>8284B | 14 EFI               | RES                                  | Reset input                                       |

| $RDY_2 \square 6$    |              | 13 🗆 F/C             | RESET                                | Synchronized reset output                         |

| AEN <sub>2</sub> ☐ 7 |              | 12 🗀 OSC             | osc                                  | Oscillator output                                 |

| CLK ☐ 8              |              | 11 RES               | CLK                                  | MOS Clock for the processor                       |

| GND ☐ 9              |              | 10 RESET             | PCLK                                 | TTL Clock for peripherals                         |

|                      |              |                      | READY                                | Synchronized ready output                         |

|                      |              |                      | V <sub>CC</sub>                      | Power Supply (+5V)                                |

|                      |              |                      | GND                                  | Ground (OV)                                       |

SAB 8284B is a bipolar clock generator/driver designed to provide clock signals for SAB 8086 and SAB 8088 processors and peripherals. It also contains READY logic for operation with two bus systems and provides the processors required

READY synchronization and timing. Reset logic with hysteresis and synchronization is also provided. This device is fabricated in a fast bipolar ASBC (Advanced Standard Buried Collector) process of Siemens.

# **Pin Definitions and Functions**

| Number | Input (I)<br>Output (O)              | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3,7    | I                                    | ADDRESS ENABLE. AEN is an active LOW signal. AEN serves to qualify its respective Bus Ready Signal (RDY <sub>1</sub> or RDY <sub>2</sub> ). AEN <sub>1</sub> validates RDY <sub>1</sub> while AEN <sub>2</sub> validates RDY <sub>2</sub> . Two AEN signal inputs are useful in system configurations which permit the processor to access two Multi-Master System Busses. In non Multi-Master configurations the AEN signal inputs are tied true (LOW). |

| 4, 6   | 1                                    | BUS READY (Transfer Complete). RDY is an active HIGH signal which is an indication from a device located on the system data bus that data has been received, or is available. RDY1 is qualified by AEN <sub>1</sub> while RDY2 is qualified by AEN <sub>2</sub> .                                                                                                                                                                                        |

| 15     | I                                    | READY SYNCHRONIZATION SELECT. ASYNC is an input which defines the synchronization mode of the READY logic. When ASYNC is low, two stages of READY synchronization are provided. When ASYNC is left open or HIGH a single stage of READY synchronization is in provided.                                                                                                                                                                                  |

| 5      | 0                                    | READY. READY is an active HIGH signal which is the synchronized RDY signal input. READY is cleared after the guaranteed hold time to the processor has been met.                                                                                                                                                                                                                                                                                         |

| 16, 17 |                                      | CRYSTAL IN. $X_1$ and $X_2$ are the pins to which a crystal is attached. The crystal frequency is 3 times the desired processor clock frequency.                                                                                                                                                                                                                                                                                                         |

| 13     | 1                                    | FREQUENCY/CRYSTAL SELECT. $F/\overline{C}$ is a strapping option. When strapped LOW, $F/\overline{C}$ permits the processors clock to be generated by the crystal. When $F/\overline{C}$ is strapped HIGH, CLK is generated from the EFI input.                                                                                                                                                                                                          |

| 14     | 1                                    | EXTERNAL FREQUENCY IN. When $F/\overline{C}$ is strapped HIGH, CLK is generated from the input frequency appearing on this pin. The input signal is a square wave 3 times the frequency of the desired CLK output.                                                                                                                                                                                                                                       |

| 8      | 0                                    | PROCESSOR CLOCK. CLK is the clock output used by the processor and all devices which directly connect to the processor's local bus (i.e., the bipolar support chips and other MOS devices). CLK has an output frequency which is 1/3 of the crystal or EFI input frequency and a 1/3 duty cycle. An output HIGH of 4.5 volts ( $V_{\rm CC}=5V$ ) is provided on this pin to drive MOS devices.                                                           |

| 2      | 0                                    | PERIPHERAL CLOCK. PCLK is a TTL level peripheral clock signal whose output frequency is 1/2 that of CLK and has 50% duty cycle.                                                                                                                                                                                                                                                                                                                          |

| 12     | 0                                    | OSCILLATOR OUTPUT. OSC is the TTL level output of the internal oscillator circuitry. Its frequency is equal to that of the crystal.                                                                                                                                                                                                                                                                                                                      |

| 11     | I                                    | RESET IN. RES is an active LOW signal which is used to generate RESET. The SAB 8284B provides a Schmitt trigger input so that an RC connection can be used to establish the power-up reset of proper duration.                                                                                                                                                                                                                                           |

|        | 3, 7  4, 6  15  5  16, 17  13  14  8 | Number Output (O)  3, 7      4, 6      5   O    16, 17      13      14      8   O    2   O    12   O                                                                                                                                                                                                                                                                                                                                                     |

| Symbol          | Number | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------|--------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET           | 10     | 0                       | RESET. RESET is an active HIGH signal which is used to reset the SAB 8086 family processors. Its timing characteristics are determined by RES.                                                                                                                                                                                                                                                         |

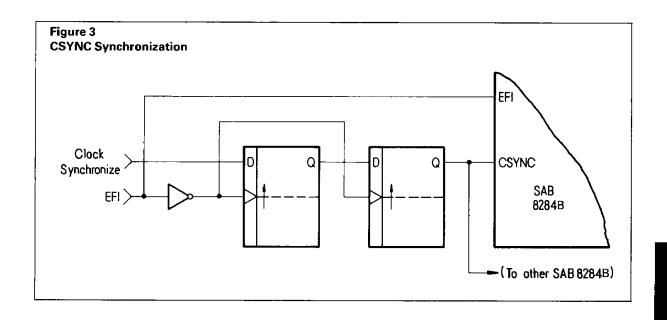

| CSYNC           | 1      | I                       | CLOCK SYNCHRONIZATION. CSYNC is an active HIGH signal which allows multiple SAB 8284B to be synchronized to provide clocks that are in phase. When CSYNC is HIGH the internal counters are reset. When CSYNC goes LOW the internal counters are allowed to resume counting. CSYNC needs to be externally synchronized to EFI. When using the internal oscillator CSYNC should be hard-wired to ground. |

| V <sub>cc</sub> | 18     | _                       | Power Supply (+5V)                                                                                                                                                                                                                                                                                                                                                                                     |

| GND             | 9      | _                       | Ground (OV)                                                                                                                                                                                                                                                                                                                                                                                            |

#### **Functional Description**

#### General

The SAB 8284B is a single chip clock generator/driver for SAB 8086 and SAB 8088 processors.

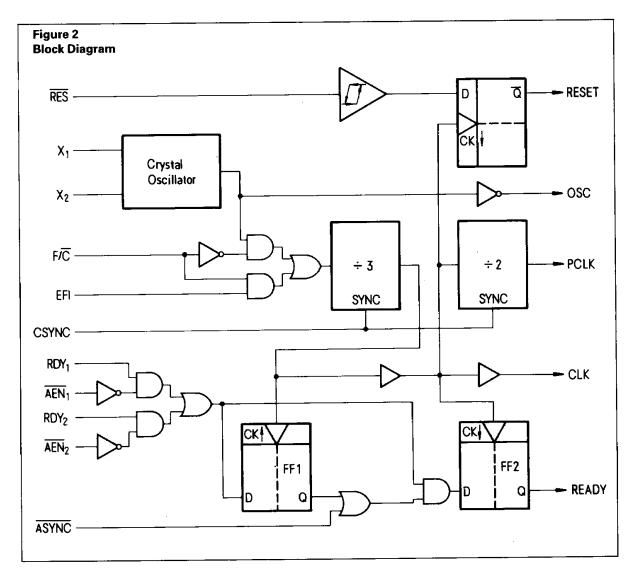

The chip contains a crystal-controlled oscillator, a divide-by-three counter, "Ready" synchronization and reset logic. Refer to Figure 2 for "Block Diagram" and Figure 1 for "Pin Configuration".

#### Oscillator

The oscillator circuit of the SAB 8284B is designed primarily for use with an external series resonant fundamental mode crystal from which the basic operating frequency is derived.

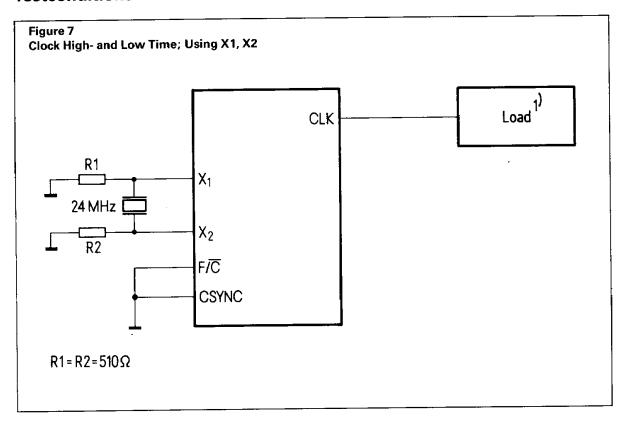

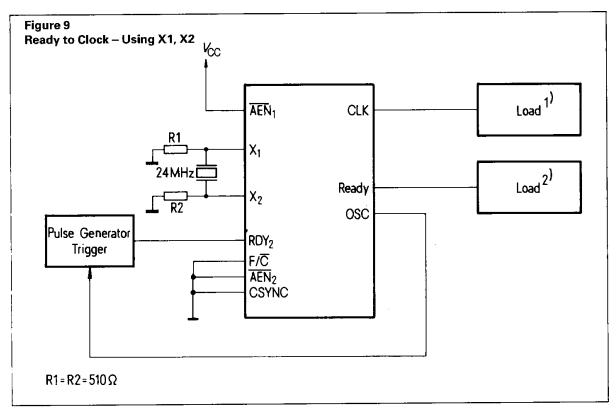

The crystal frequency should be selected at three times the required CPU clock. X1 and X2 are the two crystal input crystal connections. For the most stable operation of the oscillator (OSC) output circuit, two series resistors ( $R_1=R_2=510~\Omega$ ) as shown in figure 7 are recommended. The output of the oscillator is buffered and brought out on OSC so that other system timing signals can be derived from this stable, crystal-controlled source.

It is advisable to limit stray capacitances to less than 10pF on X1 and X2 to minimize deviation from operating at the fundamental frequency.

#### Clock Generator

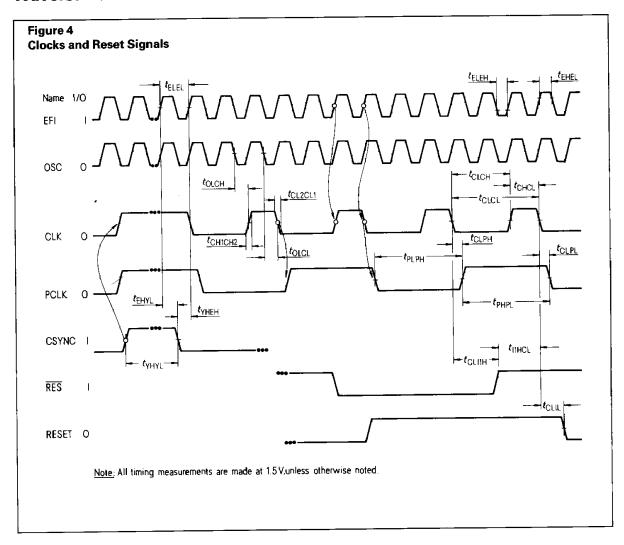

The clock generator consists of a synchronous divide-by-three counter with a special clear input that inhibits the counting. This clear input (CSYNC) allows the output clock to be synchronized with an external event (such as another SAB 8284B clock). It is necessary to synchronize the CSYNC input to the EFI clock external to the SAB 8284B. This is accomplished with two Schottky flip-flops (see figure 3). The counter output is a 33% duty cycle clock at one-third the input frequency.

The  $F/\overline{C}$  input is a strapping pin that selects either the crystal oscillator or the EFI input as the clock for the  $\div 3$  counter. If the EFI input is selected as the clock source, the oscillator section can be used independently for another clock source. Output is taken from OSC.

#### **Clock Outputs**

The CLK output is a 33% duty cycle MOS clock driver designed to drive the SAB 8086 and SAB 8088 processors directly. PCLK is a TTL level peripheral clock signal whose output frequency is 1/2 that of CLK. PCLK has 50% duty cycle.

#### **Reset Logic**

The reset logic provides a Schmitt trigger input (RES) and a synchronizing flip-flop to generate the reset timing. The reset signal is synchronized to the falling edge of CLK. A simple RC network can be used to provide power-on reset by utilizing this function of the SAB 8284B. Waveforms for clocks and reset signals are illustrated in Figure 4.

#### **READY Synchronization**

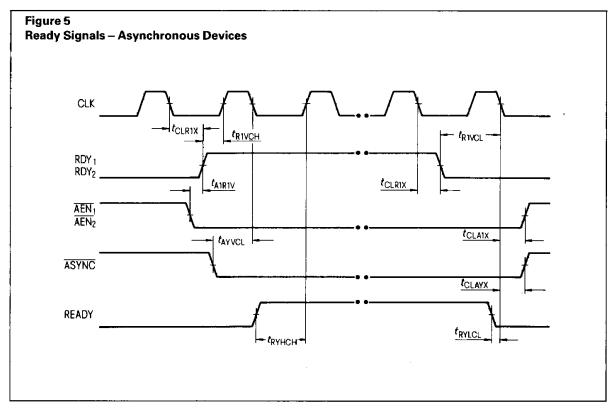

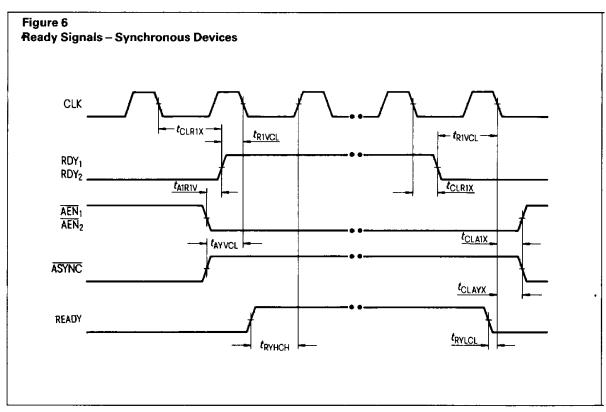

Two READY inputs (RDY<sub>1</sub>, RDY<sub>2</sub>) are provided to accomodate two Multi-Master system busses. Each input has a qualifier ( $\overline{AEN_1}$  and  $\overline{AEN_2}$ , respectively).

The AEN signals validate their respective RDY signals. If a Multi-Master system is not being used the AEN pin should be tied LOW.

Synchronization is required for all asynchronous active going edges of either RDY input to guarantee that the RDY setup and hold times are met. Inactive-going edges of RDY in normally ready systems do not require synchronization but must satisfy RDY setup and hold as a matter of proper system design.

The ASYNC input defines two modes of READY synchronization operation.

When  $\overline{\text{ASYNC}}$  is LOW, two stages of synchronization are provided for active READY input signals. Positive-going asynchronous READY inputs will first be synchronized to flip-flop one at the rising edge of CLK (requiring a setup time  $t_{\text{RIVCH}}$ ) and then synchronized to flip-flop two at the next falling edge of CLK, after which time the READY

output will go active (HIGH). Negative-going asynchronous READY inputs will be synchronized directly to flip-flop two at the falling edge of CLK, after which time the READY output will go inactive. This mode of operation is intended for use by asynchronous (normally not ready) devices in the system which cannot be guaranteed by design to meet the required RDY setup timing,  $t_{RIVCL}$ , on each bus cycle (Refer to Figure 5).

When ASYNC is high or left open, the first READY flip-flop is bypassed in the READY synchronization logic. READY inputs are synchronized by flip-flop two on the falling edge of CLK before they are presented to the processor. This mode is available for synchronous devices that can be guaranteed to meet the required RDY time (Refer to Figure 6).

ASYNC can be changed on every bus cycle to select the appropriate mode of synchronization for each device in the system.

# Absolute maximum ratings 1)

Temperature Under Bias

Storage Temperature

All Output and Supply Voltages

All Input Voltages

Power Dissipation

0 to 70°C - 65 to 150°C -0.5 to 7 V -1.0 to 5.5 V 1W

#### **D.C. Characteristics**

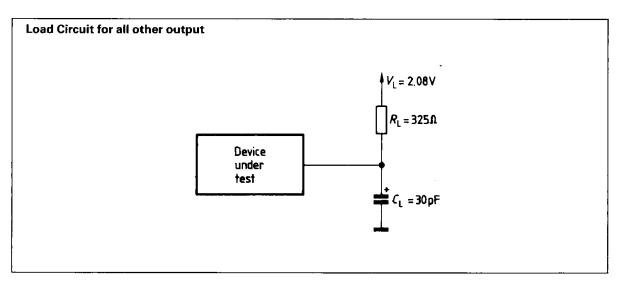

$T_{\rm A}=0$  to 70°C;  $V_{\rm CC}=+5\,{

m V}\pm10\%$

|                                   |                                            | Limi     | Limit Values |      | Test Condition                                   |

|-----------------------------------|--------------------------------------------|----------|--------------|------|--------------------------------------------------|

| Symbol                            | ibol Parameter                             |          | Max.         | Unit |                                                  |

| $I_{F}$                           | Forward Input Current (ASYNC) Other Inputs |          | -1.3<br>-0.5 | mA   | $V_F = 0.45 \text{ V}$<br>$V_F = 0.45 \text{ V}$ |

| I <sub>R</sub>                    | Reverse Input Current (ASYNC) Other Inputs |          | 50<br>50     | μΑ   | $V_{R} = V_{CC}$ $V_{R} = 5.25 \text{ V}$        |

| <b>V</b> <sub>C</sub>             | Input Forward Clamp Voltage                |          | -1.0         | ٧    | $I_{\rm C} = -5  \mathrm{mA}$                    |

| I <sub>CC</sub>                   | Power Supply Current                       |          | 110          | mA   | All outputs open                                 |

| V <sub>IL</sub>                   | Input LOW Voltage                          |          | 8.0          |      |                                                  |

| V <sub>IH</sub>                   | Input HIGH Voltage                         | 2.0      |              |      | -                                                |

| V <sub>IHR</sub>                  | Reset Input HIGH Voltage                   | 2.6      |              |      |                                                  |

| V <sub>OL</sub>                   | Output LOW Voltage                         | -        | 0.45         | v    | 5 mA                                             |

| V <sub>OH</sub>                   | Output HIGH Voltage CLK<br>Other Outputs   | 4<br>2.4 | _            |      | -1 mA<br>-1 mA                                   |

| $V_{\text{IHR}} - V_{\text{ILR}}$ | RES Input Hysteresis                       | 0.25     |              |      | -                                                |

<sup>1)</sup> Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## A.C. Characteristics

$T_A = 0 \text{ to } +70^{\circ}\text{C}; V_{CC} = +5 \text{ V } \pm 10\%$

## **Timing Requirements**

| Constant            | D                                                                                | Limit Values                   |                   | 11   | T4 C 4'4'                |  |

|---------------------|----------------------------------------------------------------------------------|--------------------------------|-------------------|------|--------------------------|--|

| Symbol              | Parameter                                                                        | Min.                           | Max.              | Unit | Test Condition           |  |

| t <sub>EHEL</sub>   | External Frequency HIGH Time                                                     | 13                             |                   |      | 90%-90% V <sub>IN</sub>  |  |

| t <sub>ELEH</sub>   | External Frequency LOW Time                                                      |                                | -                 | ns   | 10%-10% V <sub>IN</sub>  |  |

| t <sub>ELEL</sub>   | EFI Period                                                                       | $t_{EHEL} + t_{ELEH} + \delta$ |                   |      | 3)                       |  |

|                     | XTAL Frequency                                                                   | 12                             | 25 <sup>7</sup> ) | MHz  | <b> -</b>                |  |

| t <sub>R1VCL</sub>  | RDY <sub>1</sub> , RDY <sub>2</sub> Active Setup to CLK                          |                                |                   |      | ASYNC = HIGH             |  |

| t <sub>R1VCH</sub>  | RDY <sub>1</sub> , RDY <sub>2</sub> Active Setup to CLK                          | 35                             |                   |      | $\overline{ASYNC} = LOW$ |  |

| t <sub>R1VCL</sub>  | RDY <sub>1</sub> , RDY <sub>2</sub> Inactive Setup to CLK                        |                                |                   |      |                          |  |

| t <sub>CLR1X</sub>  | RDY <sub>1</sub> , RDY <sub>2</sub> Hold to CLK                                  | 0                              |                   | i    |                          |  |

| t <sub>AYVCL</sub>  | ASYNC Setup to CLK                                                               | 50                             |                   |      |                          |  |

| t <sub>CLAYX</sub>  | ASYNC Hold to CLK                                                                | 0                              |                   |      |                          |  |

| t <sub>A1VR1V</sub> | AEN <sub>1</sub> , AEN <sub>2</sub> Setup to RDY <sub>1</sub> , RDY <sub>2</sub> | 15                             | _                 | ns   | _                        |  |

| t <sub>CLA1X</sub>  | AEN₁, AEN₂ Hold to CLK                                                           | 0                              |                   |      |                          |  |

| t <sub>YHEH</sub>   | CSYNC Setup to EFI                                                               | 20                             |                   |      |                          |  |

| t <sub>EHYL</sub>   | CSYNC Hold to EFI                                                                | 10                             |                   |      |                          |  |

| t <sub>YHYL</sub>   | CSYNC Width                                                                      | 2 · t <sub>ELEL</sub>          |                   |      |                          |  |

| t <sub>I1HCL</sub>  | RES Setup to CLK                                                                 | 65                             |                   |      | 4)                       |  |

| t <sub>CLI1H</sub>  | RES Hold to CLK                                                                  | 20                             |                   |      | ,                        |  |

| t <sub>iLiH</sub>   | Input Rise Time                                                                  |                                | 20                |      | From 0.8 V to 2.0 V      |  |

| t <sub>iHIL</sub>   | Input Fall Time                                                                  |                                | 12                |      | From 2.0 V to 0.8 V      |  |

Notes see next page.

### **SAB 8284B**

#### **Timing Responses**

|                                            |                               | Limit Values          |      | Unit  | Test Condition      |

|--------------------------------------------|-------------------------------|-----------------------|------|-------|---------------------|

| Symbol                                     | Parameter                     | Min.                  | Max. | Oliit | Test Condition      |

| t <sub>CLCL</sub>                          | CLK Cycle Period              | 100                   |      |       |                     |

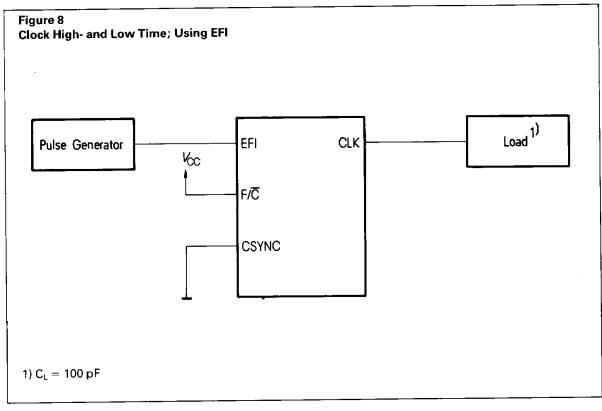

| t <sub>CHCL</sub>                          | CLK HIGH Time                 | <sup>1</sup> )        | _    |       | Fig. 7 & Fig. 8     |

| t <sub>CLCH</sub>                          | CLK LOW Time                  | 2)                    |      |       | Fig. 7 & Fig. 8     |

| t <sub>CH1CH2</sub><br>t <sub>CL2CL1</sub> | CLK Rise or Fall Time         |                       | 10   |       | 1.0 V to 3.5 V      |

| t <sub>PHPL</sub>                          | PCLK HIGH Time                | t <sub>CLCL</sub> -20 |      |       | _                   |

| t <sub>PLPH</sub>                          | PCLK LOW Time                 | $t_{\text{CLCL}}$ –20 | _    |       |                     |

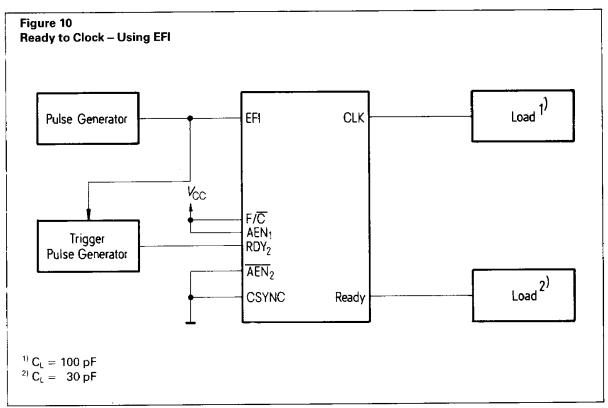

| t <sub>RYLCL</sub>                         | Ready Inactive to CLK 6)      | -8                    | ns   | ns    | Fig. 9 & Fig. 10    |

| t <sub>RYHCH</sub>                         | Ready Active to CLK 5)        | 2)                    |      |       | Fig. 9 & Fig. 10    |

| $t_{\text{CLIL}}$                          | CLK to Reset Delay            |                       | 40   | _     |                     |

| $t_{CLPH}$                                 | CLK to PCLK HIGH Delay        |                       |      |       |                     |

| $t_{CLPL}$                                 | CLK to PCLK LOW Delay         |                       | 22   |       | -                   |

| t <sub>OLCH</sub>                          | OSC to CLK HIGH Delay         | -5                    |      |       |                     |

| t <sub>OLCL</sub>                          | OSC to CLK LOW Delay          | 2                     | 35   |       |                     |

| t <sub>OLOH</sub>                          | Output Rise Time (except CLK) |                       | 20   |       | From 0.8 V to 2.0 V |

| t <sub>OHOL</sub>                          | Output Fall Time (except CLK) |                       | 12   |       | From 2.0 V to 0.8 V |

$<sup>^{1})~(^{1}\!/</sup>_{3}\,t_{CLCL})~+2$  for CLK Freq.  $\leqslant 8$  MHz  $(1/3 t_{CLCL})$  +6 for CLK Freq. = 10 MHz

<sup>2) (2/3</sup> t<sub>CLCL</sub>) - 15 for CLK Freq. ≤ 8 MHz (2/3 t<sub>CLCL</sub>) - 14 for CLK Freq. = 10 MHZ

3) δ = EFI rise (5 ns max) + EFI fall (5 ns max).

<sup>4)</sup> Setup and hold necessary only to guarantee recognition at next clock.

<sup>&</sup>lt;sup>5</sup>) Applies only to T<sub>3</sub> and T<sub>W</sub> states.

<sup>&</sup>lt;sup>6</sup>) Applies only to T<sub>2</sub> states.

<sup>7) 30</sup> MHz for SAB 8284B-1

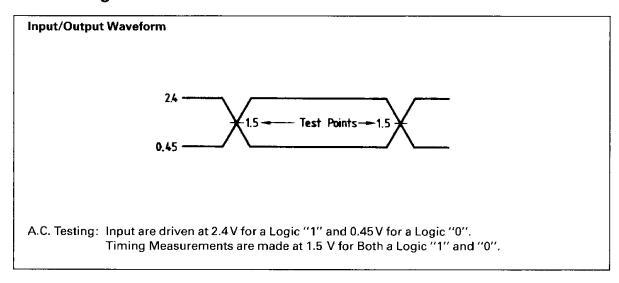

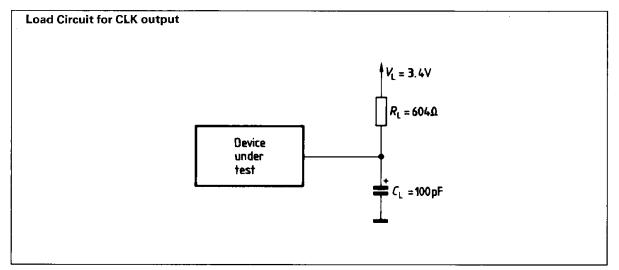

# A.C. Testing

# **Waveforms**

# **Testconditions**

# **SAB 8284B**

# Ordering Information

| Corhponent                  | Description                        | Ordering Code |  |

|-----------------------------|------------------------------------|---------------|--|

|                             | Clock Generator- (Plastic Package) |               |  |

| SAB 8284B – P               | upto 8 MHz                         | Q67020-Y151   |  |

| SAB 8284B-1 – P upto 10 MHz |                                    | Q67020-Y152   |  |