# DS78C120/DS88C120 Dual CMOS Compatible Differential Line Receiver

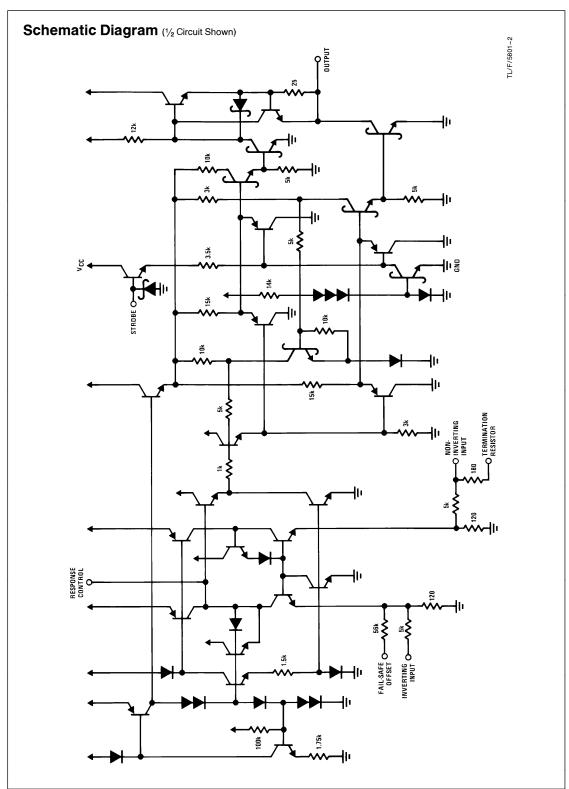

## **General Description**

The DS78C120 and DS88C120 are high performance, dual differential, CMOS compatible line receivers for both balanced and unbalanced digital data transmission. The inputs are compatible with EIA, Federal and MIL standards.

Input specifications meet or exceed those of the popular DS7820/DS8820 line receiver.

The line receiver will discriminate a  $\pm 200$  mV input signal over a common-mode range of  $\pm 10$ V and a  $\pm 300$  mV signal over a range of  $\pm 15$ V.

Circuit features include hysteresis and response control for applications where controlled rise and fall times and/or high frequency noise rejection are desirable. Threshold offset control is provided for fail-safe detection, should the input be open or short. Each receiver includes a 180 $\Omega$  terminating resistor and the output gate contains a logic strobe for time discrimination. The DS78C120 is specified over a  $-55^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$  temperature range and the DS88C120 from 0°C to  $+70^{\circ}\text{C}$ .

## **Features**

- Full compatibility with EIA Standards RS232-C, RS422 and RS423, Federal Standards 1020, 1030 and MIL-188-114

- $\blacksquare$  Input voltage range of  $\pm 15 \text{V}$  (differential or common-mode)

- Separate strobe input for each receiver

- 1/2 V<sub>CC</sub> strobe threshold for CMOS compatibility

- 5k typical input impedance

- 50 mV input hysteresis

- 200 mV input threshold

- Operation voltage range = 4.5V to 15V

- Separate fail-safe mode

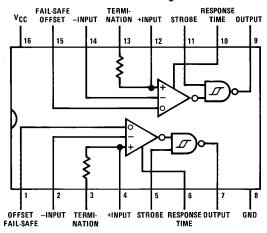

## **Connection Diagram**

#### **Dual-In-Line Package**

Top View

TL/F/5801-1

Order Number DS88C120N See NS Package Number N16A

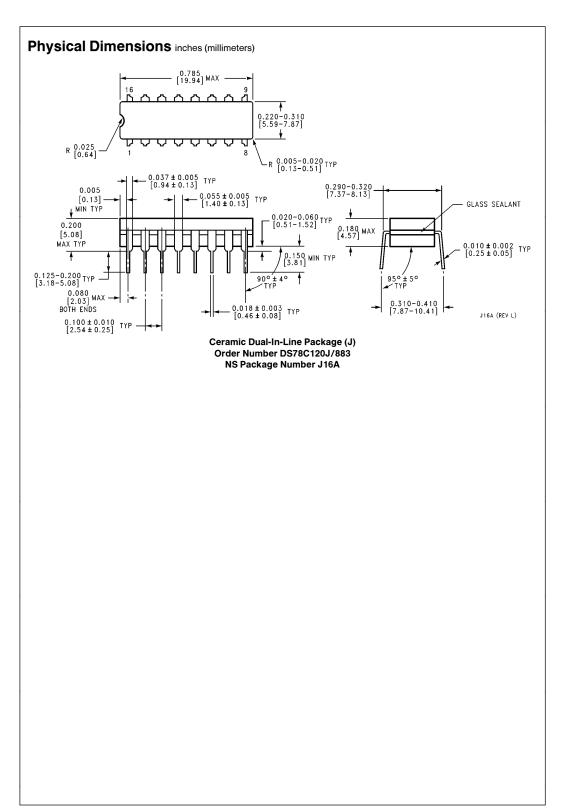

For Complete Military 883 Specifications, see RETS Data Sheet. Order Number DS78C120J/883 See NS Package Number J16A

TRI-STATE® is a registered trademark of National Semiconductor Corporation

## **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Supply Voltage

18V

Input Voltage

± 25V

Strobe Voltage

18V

Output Sink Current

50 mA

Maximum Power Dissipation\* at 25°C

Cavity Package 1433 mW Molded Package 1362 mW  $\begin{tabular}{lll} Storage Temperature Range & -65^{\circ}C to +150^{\circ}C \\ Lead Temperature (Soldering, 4 seconds) & 260^{\circ}C \\ \end{tabular}$

# **Operating Conditions**

| _                                 | Min | Max  | Units |

|-----------------------------------|-----|------|-------|

| Supply Voltage (V <sub>CC</sub> ) | 4.5 | 15   | V     |

| Temperature (T <sub>A</sub> )     |     |      |       |

| DS78C120                          | -55 | +125 | °C    |

| DS88C120                          | 0   | +70  | °C    |

| Common-Mode Voltage ( $V_{CM}$ )  | -15 | +15  | V     |

# Electrical Characteristics (Notes 2 and 3)

| Symbol             | ol Parameter Conditions                     |                                                                                                                               | Min                       | Тур                   | Max                    | Units |    |

|--------------------|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|---------------------------|-----------------------|------------------------|-------|----|

| V <sub>TH</sub>    | Differential Threshold                      | $I_{OUT} = -200 \mu A,$                                                                                                       | $-7V \le V_{CM} \le 7V$   |                       | 0.06                   | 0.2   | V  |

|                    | Voltage                                     | $V_{OUT} \ge V_{CC} - 1.2V$                                                                                                   | $-15V \le V_{CM} \le 15V$ |                       | 0.06                   | 0.3   | V  |

| V <sub>TL</sub>    | Differential Threshold                      | $I_{OUT} = 1.6 \text{ mA}, V_{OUT} \le 0.5 \text{V}$                                                                          | $-7V \le V_{CM} \le 7V$   |                       | -0.08                  | -0.2  | V  |

|                    | Voltage                                     |                                                                                                                               | $-15V \le V_{CM} \le 15V$ |                       | -0.08                  | -0.3  | V  |

| V <sub>TH</sub>    | Differential Threshold<br>Voltage Fail-Safe | $I_{OUT} = -200 \mu A,$ $V_{OUT} \ge V_{CC} - 1.2 V$                                                                          | $-7V \le V_{CM} \le 7V$   |                       | 0.47                   | 0.7   | ٧  |

| V <sub>TL</sub>    | Offset = 5V                                 | $I_{OUT} = 1.6 \text{ mA}, V_{OUT} \le 0.5 \text{V}$                                                                          | $-7V \le V_{CM} \le 7V$   | 0.2                   | 0.42                   |       | V  |

| R <sub>IN</sub>    | Input Resistance                            | $-15V \le V_{CM} \le 15V, 0V \le V_{CC} \le$                                                                                  | 15V                       | 4                     | 5                      |       | kΩ |

| R <sub>T</sub>     | Line Termination Resistance                 | $T_A = 25^{\circ}C$                                                                                                           |                           | 100                   | 180                    | 300   | Ω  |

| Ro                 | Offset Control Resistance                   | $T_A = 25^{\circ}C$                                                                                                           |                           |                       | 56                     |       | kΩ |

| I <sub>IND</sub>   | Data Input Current                          | $0V \le V_{CC} \le 15V$                                                                                                       | V <sub>CM</sub> = 10V     |                       | 2                      | 3.1   | mA |

|                    | (Unterminated)                              |                                                                                                                               | V <sub>CM</sub> = 0V      |                       | 0                      | -0.5  | mA |

|                    |                                             |                                                                                                                               | $V_{CM} = -10V$           |                       | -2                     | -3.1  | mA |

| V <sub>THB</sub>   | Input Balance<br>(Note 5)                   | $\label{eq:lout_power} \begin{split} I_{OUT} &= 200~\mu\text{A}, V_{OUT} \geq \\ V_{CC} &= 1.2V, R_S = 500\Omega \end{split}$ | $-7V \le V_{CM} \le 7V$   |                       | 0.1                    | 0.4   | V  |

|                    |                                             | $I_{OUT} = 1.6$ mA, $V_{OUT} \le 0.5$ V $R_S = 500\Omega$                                                                     | $-7V \le V_{CM} \le 7V$   |                       | -0.1                   | -0.4  | ٧  |

| V <sub>OH</sub>    | Logical "1" Output Voltage                  | $I_{OUT} = -200 \mu\text{A}, V_{DIFF} = 1V$                                                                                   |                           | V <sub>CC</sub> - 1.2 | V <sub>CC</sub> - 0.75 |       | V  |

| V <sub>OL</sub>    | Logical "0" Output Voltage                  | $I_{OUT} = 1.6 \text{ mA}, V_{DIFF} = -1V$                                                                                    |                           |                       | 0.25                   | 0.5   | V  |

| Icc                | Power Supply Current                        | $15V \le V_{CM} \le -15V$ ,                                                                                                   | $V_{CC} = 5.5V$           |                       | 8                      | 15    | mA |

|                    | $V_{DIFF} = -0.5V$ (Both Receivers)         | $V_{CC} = 15V$                                                                                                                |                           | 15                    | 30                     | mA    |    |

| I <sub>IN(1)</sub> | Logical "1" Strobe Input<br>Current         | V <sub>STROBE</sub> = 15V, V <sub>DIFF</sub> = 3V                                                                             |                           |                       | 15                     | 100   | μΑ |

| I <sub>IN(0)</sub> | Logical "0" Strobe Input<br>Current         | $V_{STROBE} = 0V, V_{DIFF} = -3V$                                                                                             |                           |                       | -0.5                   | -100  | μΑ |

| V <sub>IH</sub>    | Logical "1" Strobe Input                    | $V_{OL} \le 0.5V$ , $I_{OUT} = 1.6$ mA                                                                                        | $V_{CC} = 5V$             | 3.5                   | 2.5                    |       | V  |

|                    | Voltage                                     |                                                                                                                               | $V_{CC} = 10V$            | 8.0                   | 5.0                    |       | V  |

|                    |                                             |                                                                                                                               | $V_{CC} = 15V$            | 12.5                  | 7.5                    |       | V  |

<sup>\*</sup>Derate cavity package 9.6 mW/°C above 25°C; derate molded package 10.9 mW/°C above 25°C.

## Electrical Characteristics (Notes 2 and 3) (Continued)

| Symbol          | Parameter                    | Conditions                                                                       |                       |    | Тур | Max | Units |

|-----------------|------------------------------|----------------------------------------------------------------------------------|-----------------------|----|-----|-----|-------|

| V <sub>IL</sub> | Logical "0" Strobe Input     | V <sub>OH</sub> V <sub>CC</sub> - 1.2V,                                          | $V_{CC} = 5V$         |    | 2.5 | 1.5 | ٧     |

|                 | Voltage                      | $I_{OUT} = -200 \mu\text{A}$                                                     | V <sub>CC</sub> = 10V |    | 5.0 | 2.0 | V     |

|                 |                              |                                                                                  | V <sub>CC</sub> = 15V |    | 7.5 | 2.5 | V     |

| los             | Output Short-Circuit Current | V <sub>OUT</sub> = 0V, V <sub>CC</sub> = 15V, V <sub>STROBE</sub> = 0V, (Note 4) |                       | -5 | -20 | -40 | mA    |

Note 1: "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. Except for "Operating Temperature Range" they are not meant to imply that the devices should be operated at these limits. The table of "Electrical Characteristics" provides conditions for actual device operation.

Note 2: Unless otherwise specified min/max limits apply across the  $-55^{\circ}$ C to  $+125^{\circ}$ C temperature range for the DS78C120 and across the  $0^{\circ}$ C to  $+70^{\circ}$ C range for the DS88C120. All typical values for  $T_A = 25^{\circ}$ C,  $V_{CC} = 5V$  and  $V_{CM} = 0V$ .

Note 3: All currents into device pins shown as positive, out of device pins as negative, all voltages referenced to ground unless otherwise noted. All values shown as max or min on absolute value basis.

Note 4: Only one output at a time should be shorted.

Note 5: Refer to EIA-RS422 for exact conditions.

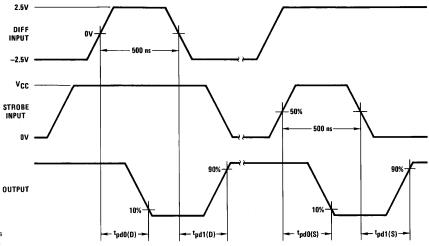

# Switching Characteristics $V_{CC} = 5V, T_A = 25^{\circ}C$

| Symbol              | Parameter                        | Conditions    | Min | Тур | Max | Units |

|---------------------|----------------------------------|---------------|-----|-----|-----|-------|

| t <sub>pd0(D)</sub> | Differential Input to "0" Output | $C_L = 50 pF$ |     | 60  | 100 | ns    |

| t <sub>pd1(D)</sub> | Differential Input to "1" Output | $C_L = 50 pF$ |     | 100 | 150 | ns    |

| t <sub>pd0(S)</sub> | Strobe Input to "0" Output       | $C_L = 50 pF$ |     | 30  | 70  | ns    |

| t <sub>pd1(S)</sub> | Strobe Input to "1" Output       | $C_L = 50 pF$ |     | 100 | 150 | ns    |

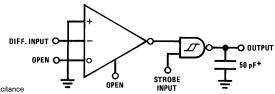

# **AC Test Circuit and Switching Time Waveforms**

## Differential and Strobe Input Signal

\*Includes probe and test fixture capacitance

TL/F/5801-3

$t_r = t_f \le 10 \text{ ns}$ PRR = 1 MHz

TL/F/5801-4

Note: Optimum switching response is obtained by minimizing stray capacitance on Response Control pin (no external connection).

# **Application Hints**

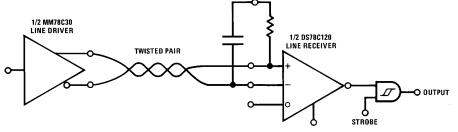

#### **Balanced Data Transmission**

TL/F/5801-5

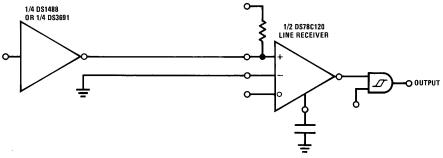

#### **Unbalanced Data Transmission**

TL/F/5801-6

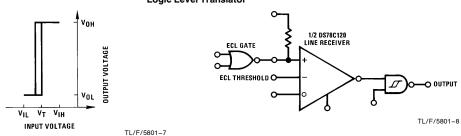

## Logic Level Translator

The DS78C120/DS88C120 may be used as a level transistor to interface between  $\pm$ 12V MOS, ECL, TTL and CMOS. To configure, bias either input to a voltage equal to ½ the voltage of the input signal, and the other input to the driving gate.

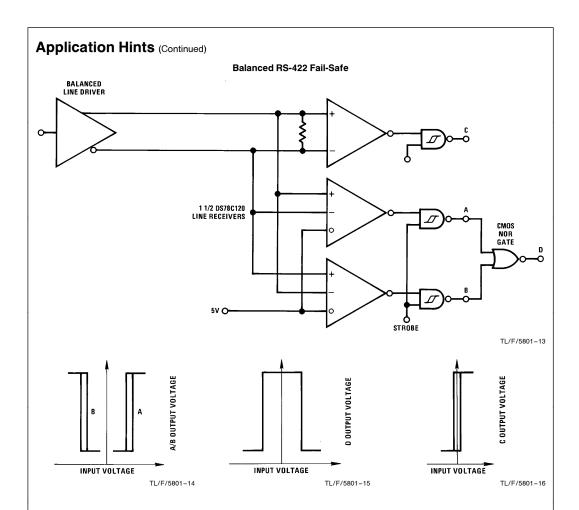

## **Application Hints** (Continued)

#### LINE DRIVERS

Line drivers which will interface with the DS78C120/DS88C120 are listed below.

#### **Balanced Drivers**

DS26LS31 Quad RS-422 Line Driver

DS7830, DS8830 Dual TTL

DS7831, DS8831 Dual TRI-STATE® TTL DS7832, DS8832 Dual TRI-STATE TTL

DS1691A, DS3691 Quad RS-423/Dual RS-422 TTL DS1692, DS3692 Quad RS-423/Dual TRI-STATE

RS-422 TTL

DS3587, DS3487 Quad TRI-STATE RS-422

#### **Unbalanced Drivers**

DS1488 Quad RS-232 DS14C88 Quad RS-232 DS75150 Dual RS-232

#### **RESPONSE CONTROL AND HYSTERESIS**

In unbalanced (RS-232/RS-423) applications it is recommended that the rise time and fall time of the line driver be controlled to reduce cross-talk. Elimination of switching noise is accomplished in the DS78C120/DS8C120 by the 50 mV of hysteresis incorporated in the output gate. This eliminates the oscillations which may appear in a line receiver due to the input signal slowly varying about the threshold level for extended periods of time.

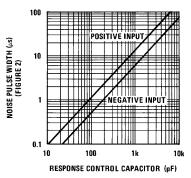

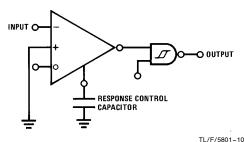

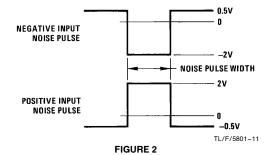

High frequency noise which is superimposed on the input signal which may exceed 50 mV can be reduced in amplitude by filtering the device input. On the DS78C120/DS88C120, a high impedance response control pin in the input amplifier is available to filter the input signal without affecting the termination impedance of the transmission line. Noise pulse width rejection vs the value of the response control capacitor is shown in *Figures 1* and *2*. This combination of filters followed by hysteresis will optimize performance in a worse case noise environment.

#### TRANSMISSION LINE TERMINATION

On a transmission line which is electrically long, it is advisable to terminate the line in its characteristic impedance to prevent signal reflection and its associated noise/crosstalk. A  $180\Omega$  termination resistor is provided in the DS78C120/DS88C120 line receiver. To use the termination resistor, connect pins 2 and 3 together and pins 13 and 14 together. The  $180\Omega$  resistor provides a good compromise between line reflections, power dissipation in the driver, and IR drop in the transmission line. If power dissipation and IR drop are still a concern, a capacitor may be connected in series with the resistor to minimize power loss.

The value of the capacitor is recommended to be the line length (time) divided by 3 times the resistor value. Example: if the transmission line is 1,000 feet long, (approximately 1000 ns) the capacitor value should be 1852 pF. For additional application details, refer to application notes AN-22 and AN-108.

TL/F/5801-9

FIGURE 1. Noise Pulse Width vs Response Control Capacitor

TL/F/5801=10

### **Application Hints** (Continued)

#### **FAIL-SAFE OPERATION**

Communication systems require elements of a system to detect the presence of signals in the transmission lines, and it is desirable to have the system shut-down in a fail-safe mode if the transmission line is open or shorted. To facilitate the detection of input opens or shorts, the DS78C120/DS88C120 incorporates an input threshold voltage offset. This feature will force the line receiver to a specific logic state if presence of either fault is a condition.

Given that the receiver input threshold is  $\pm 200$  mV, an input signal greater than  $\pm 200$  mV insures the receiver will be in a specific logic state. When the offset control input (pins 1 and 15) is connected to  $V_{CC}=5$  V, the input thresholds are offset from 200 mV to 700 mV, referred to the non-inverting input, or -200 mV to -700 mV, referred to the inverting input. Therefore, if the input is open or shorted, the input will be greater than the input threshold and the receiver will remain in a specified logic state.

The input circuit of the receiver consists of a 5k resistor terminated to ground through  $120\Omega$  on both inputs. This network acts as an attenuator, and permits operation with common-mode input voltages greater than  $\pm 15 V$ . The offset control input is actually another input to the attenuator, but its resistor value is 56k. The offset control input is connected to the inverting input side of the attenuator, and the input voltage to the amplifier is the sum of the inverting input plus 0.09 times the voltage on the offset control input. When the offset control input is connected to 5V the input amplifier will see  $V_{\rm IN(INVERTING)} + 0.9 V$  when the control input is connected to 10V. The offset control input will not significantly affect the differential

performance of the receiver over its common-mode operating range, and will not change the input impedance balance of the receiver.

It is recommended that the receiver be terminated (500 $\Omega$  or less) to insure it will detect an open circuit in the presence of noise.

The offset control can be used to insure fail-safe operation for unbalanced interface (RS-423) or for balanced interface (RS-422) operation.

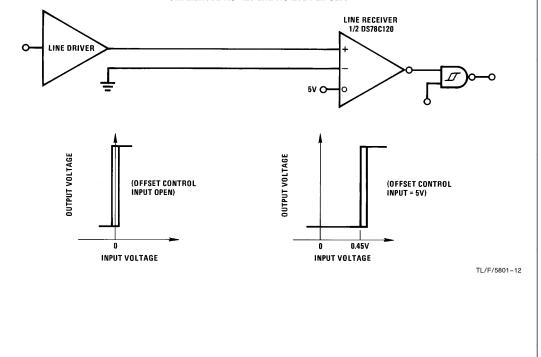

For unbalanced operation, the receiver would be in an indeterminate logic state if the offset control input was open. Connecting the offset to 5V offsets the receiver threshold 0.45V. The output is forced to a logic zero state if the input is open or shorted.

For balanced operation with inputs shorted or open, receiver C will be in an indeterminate logic state. Receivers A and B will be in a logic zero state allowing the NOR gate to detect the short or open condition. The strobe will disable receivers A and B and may therefore be used to sample the fail-safe detector. Another method of fail-safe detection consists of filtering the output of the NOR gate D so it would not indicate a fault condition when receiver inputs pass through the threshold region, generating an output transient. In a communications system, only the control signals are required to detect input fault condition. Advantages of a balanced data transmission system over an unbalanced transmission system are:

- 1. High noise immunity

- 2. High data ratio

- 3. Long line lengths

#### Unbalanced RS-423 and RS-232 Fail-Safe

# Truth Table (For Balanced Fail-Safe)

| Input | Strobe | A-OUT | B-OUT | C-OUT | D-OUT |

|-------|--------|-------|-------|-------|-------|

| 0     | 1      | 0     | 1     | 0     | 0     |

| 1     | 1      | 1     | 0     | 1     | 0     |

| X     | 1      | 0     | 0     | Х     | 1     |

| 0     | 0      | 1     | 1     | 0     | 0     |

| 1     | 0      | 1     | 1     | 0     | 0     |

| X     | 0      | 1     | 1     | 0     | 0     |

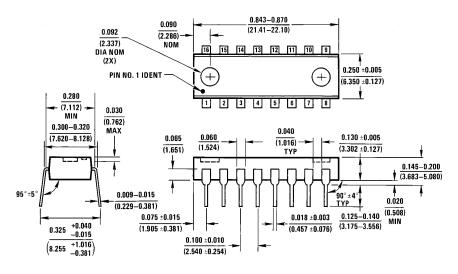

## Physical Dimensions inches (millimeters) (Continued)

Molded Dual-In-Line Package (N) Order Number DS88C120N NS Package Number N16A

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

N16A (REV.E)

**National Semiconductor** National Semiconducto Corporation 1111 West Bardin Road Arlington, TX 76017 Tel: 1(800) 272-9959 Fax: 1(800) 737-7018

http://www.national.com

**National Semiconductor** Europe

Fax: +49 (0) 180-530 85 86 Fax: +49 (0) 180-530 so so Email: europe.support@nsc.com Deutsch Tel: +49 (0) 180-530 85 85 English Tel: +49 (0) 180-532 78 32 Français Tel: +49 (0) 180-532 95 58 Italiano Tel: +49 (0) 180-534 16 80

National Semiconductor Hong Kong Ltd.

13th Floor, Straight Block,

Ocean Centre, 5 Canton Rd.

Tsimshatsui, Kowloon Hong Kong Tel: (852) 2737-1600 Fax: (852) 2736-9960

National Semiconductor Japan Ltd.

Tel: 81-043-299-2308

Fax: 81-043-299-2408