### LTCC multilayer substrates

## features

- The high-density wiring by the fine line and pattern is available

- Miniaturization is possible by burying L, C and Strip-line

- By the uses of low dielectric-loss ceramics and low loss conductors, the substrates excel in the high frequency characteristic

- As the thermal expansion coefficient is close to silicon's, the substrates are suitable for the bare chip mounting

- By preparing the thermal vias under bare chips, the substrates are excellent in the heat dissipation

- The substrates are outstanding in heat resistance and humidity resistance due to the ceramics used

#### Construction C IC Chip Cavity Cavity Cavity SMD SMD SMD SMD SMD SMD SMD Cavity Ca

## ordering information

# definition

With the high functioning and the advance in down-sizing of electronic equipment, wiring substrates are also required to be highly functioned.

One of the technologies to respond to the high functioning of the substrates is LTCC (Low Temperature Co-fired Ceramics), which is the ceramic multilayer technology that enables the alumina to be fired at a "low temperature" of 900°C or lower by adding glass materials to the alumina while it is fired by a "high temperature" of about 1500°C.

It is the LTCC's important characteristic that low melting point materials like Ag, etc. can be used for the buried conductors for the low temperature firing.

# environmental applications

#### **Characteristics of Substrate Material**

| Parameter                       | Characteristics       |  |

|---------------------------------|-----------------------|--|

| Bending Strength                | 250                   |  |

| Thermal Expansion Coefficient   | 5.5                   |  |

| Thermal Conductivity            | 3                     |  |

| Insulation Resistance           | >1013                 |  |

| Dielectric Constant             | 7                     |  |

| Dielectric Loss                 | <0.003                |  |

| Resistivity of Buried Conductor | Ag 2.5                |  |

| Density                         | 2.8                   |  |

| Surface Roughness Ra            | <0.4                  |  |

| Withstanding Voltage            | >15                   |  |

| Layer Thickness                 | 80, 100, 125 Standard |  |

| Substrate Flatness              | <0.03                 |  |

Specifications given herein may be changed at any time without prior notice. Please confirm technical specifications before you order and/or use.

247

# LTCC multilayer substrates

# environmental applications (continued)

#### **Characteristics of Substrate Material**

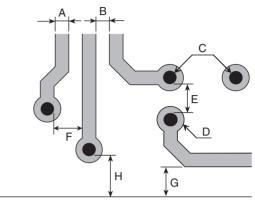

| Symbol | Parameter                      | Design Value              |

|--------|--------------------------------|---------------------------|

| А      | Line Width                     | 0.06mm Min.               |

| В      | Line to Line Spacing           | 0.06mm Min.               |

| С      | Via Diameter                   | 0.1mm, 0.15mm, 0.2mm      |

| D      | Via Pad Diameter               | Via diameter +0.05mm Min. |

| E      | Via to Via Spacing             | 0.2mm Min.                |

| F      | Via to Line Spacing            | 0.15mm Min.               |

| G      | Part Edge to Conductor Spacing | 0.2mm Min.                |

| Н      | Part Edge to Via Spacing       | 0.3mm Min.                |

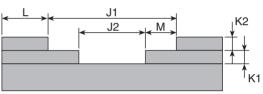

| J1, J2 | Cavity Width                   | 0.6mm Min.                |

| K1, K2 | Cavity Depth                   | 0.1mm Min.                |

| L      | Wall Thickness of Cavity       | 0.5mm Min.                |

| М      | Shelf Width in the Cavity      | 0.5mm Min.                |

Surface layer - Inner layer

Cavity

1/08/09

Specifications given herein may be changed at any time without prior notice. Please confirm technical specifications before you order and/or use.