- Modulation Scheme Optimized to Operate Without a Filter

- 2 W Into a 4-Ω Speaker (THD+N<1%)

- <0.2% THD+N at 1.5 W, 1 kHz, Into a 4-Ω Load

- Extremely Efficient Third Generation 5-V Class-D Technology:

- Low-Supply Current (No Filter) ... 4 mA

- Low-Supply Current (Filter) . . . 7.5 mA

- Low-Shutdown Current ... 0.05 μA

Low-Noise Floor ... 40 μV<sub>RMS</sub>

- (No-Weighting Filter) – Maximum Efficiency Into 8  $\Omega$ , 75 – 85 %

- 4 Internal Gain Settings . . . 6 23.5 dB

- PSSR . . . –77 dB

- Integrated Depop Circuitry

- Short-Circuit Protection (Short to Battery, Ground, and Load)

- -40°C to 85°C Operating Temperature Range

#### description

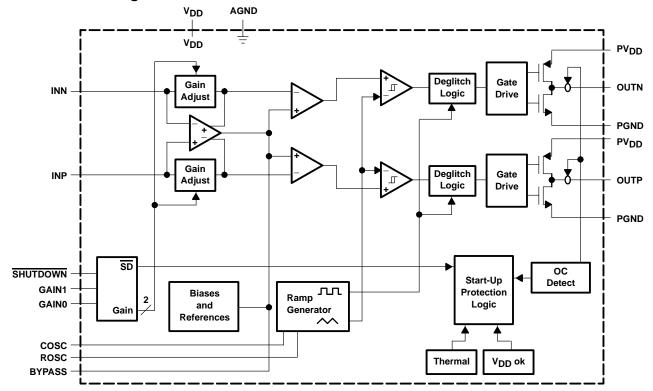

The TPA2000D1 is a 2-W mono bridge-tied-load (BTL) class-D amplifier designed to drive a speaker with at least  $4-\Omega$  impedance. The amplifier uses TI's third generation modulation technique, which results in improved efficiency

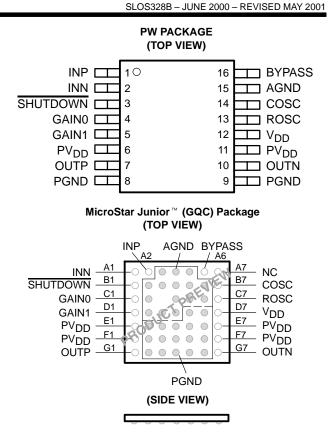

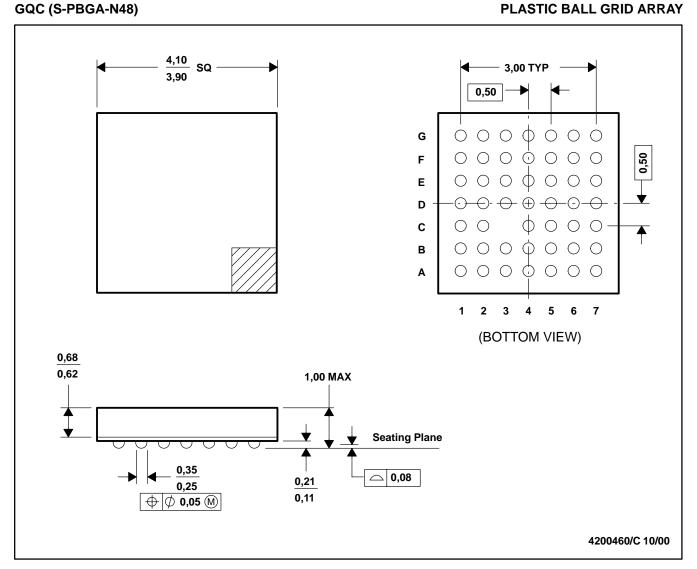

NC – No internal connection, still requires a pad for the ball. NOTE: The shaded terminals are used for thermal connections to the ground plane.

and SNR. It also allows the device to be connected directly to the speaker without the use of the LC output filter commonly associated with class-D amplifiers (this will result in EMI which must be shielded at the system level). These features make the device ideal for use in devices where high-efficiency is needed to extend battery run time.

The gain of the amplifier is controlled by two input terminals, GAIN1, and GAIN0. This allows the amplifier to be configured for a gain of 6, 12, 18, and 23.5 dB. The differential input terminals are high-impedance CMOS inputs, and can be used as summing nodes.

The class-D BTL amplifier includes depop circuitry to reduce the amount of turnon pop at power up, and when cycling SHUTDOWN.

The TPA2000D1 is available in the 16-pin TSSOP package (PW) which is capable of driving 2-W continuous output power level into a  $4-\Omega$  load. TPA2000D1 operates over an ambient temperature range of  $-40^{\circ}$ C to  $85^{\circ}$ C.

| T.            | PACKAGED DEVICES        |              |  |  |  |

|---------------|-------------------------|--------------|--|--|--|

| 'A            | TSSOP (PW) <sup>†</sup> | GQC          |  |  |  |

| -40°C to 85°C | TPA2000D1PW             | TPA2000D1GQC |  |  |  |

AVAILABLE OPTIONS

<sup>†</sup> The PW package is available taped and reeled. To order a taped and reeled part, add the suffix R to the part number (e.g., TPA2000D1PWR).

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

MicroStar Junior is a trademark of Texas Instruments.

This document contains information on products in more than one phase of development. The status of each device is indicated on the page(s) specifying its electrical characteristics.

Copyright © 2001, Texas Instruments Incorporated

1

SLOS328B - JUNE 2000 - REVISED MAY 2001

## functional block diagram

### **Terminal Functions**

| TER             | MINAL                                     |       |     |                                                                                                                                                           |  |

|-----------------|-------------------------------------------|-------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME            | NAME NO.                                  |       | I/O | DESCRIPTION                                                                                                                                               |  |

| NAME            | GQY                                       | PW    |     |                                                                                                                                                           |  |

| AGND            | A3 – A5,<br>B2 – B6<br>C2 – C6<br>D2 – D4 | 15    | Η   | Analog ground                                                                                                                                             |  |

| BYPASS          | A6                                        | 16    | Ι   | Connect capacitor to ground for BYPASS voltage filtering.                                                                                                 |  |

| COSC            | B7                                        | 14    | Ι   | Connect capacitor to ground to set oscillation frequency.                                                                                                 |  |

| GAIN0           | C1                                        | 4     | -   | Bit 0 of gain control (TTL logic level)                                                                                                                   |  |

| GAIN1           | D1                                        | 5     | I   | Bit 1 of gain control (TTL logic level)                                                                                                                   |  |

| INN             | A1                                        | 2     | I   | Negative differential input                                                                                                                               |  |

| INP             | A2                                        | 1     | Ι   | Positive differential input                                                                                                                               |  |

| OUTN            | G7                                        | 10    | 0   | Negative BTL output                                                                                                                                       |  |

| OUTP            | G1                                        | 7     | 0   | Positive BTL output                                                                                                                                       |  |

| PGND            | D5, D6<br>E2 – E7<br>F2 – F7<br>G2 – G7   | 8, 9  | I   | High-current grounds (2)                                                                                                                                  |  |

| PVDD            | E1, E7,<br>F1, F7                         | 6, 11 | Ι   | High-current power supplies (2)                                                                                                                           |  |

| ROSC            | C7                                        | 13    | I   | Connect resistor to ground to set oscillation frequency.                                                                                                  |  |

| SHUTDOWN        | B1                                        | 3     | Ι   | Places the amplifier in shutdown mode if a TTL logic low is placed on this terminal, and normal operation if a TTL logic high is placed on this terminal. |  |

| V <sub>DD</sub> | D7                                        | 12    | I   | Analog power supply                                                                                                                                       |  |

SLOS328B - JUNE 2000 - REVISED MAY 2001

#### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)<sup>†</sup>

| Supply voltage, V <sub>DD</sub> , PV <sub>DD</sub>           | –0.3 V to 5.5 V                |

|--------------------------------------------------------------|--------------------------------|

| Input voltage, V <sub>1</sub>                                |                                |

| Continuous total power dissipation                           | (see Dissipation Rating Table) |

| Operating free-air temperature range, T <sub>A</sub>         | –40°C to 85°C                  |

| Operating junction temperature range, T <sub>J</sub>         | –40°C to 150°C                 |

| Storage temperature range, T <sub>stg</sub>                  | –65°C to 150°C                 |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds |                                |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### **DISSIPATION RATING TABLE**

| PACKAGE | T <sub>A</sub> ≤ 25°C | DERATING FACTOR | T <sub>A</sub> = 70°C | T <sub>A</sub> = 85°C |

|---------|-----------------------|-----------------|-----------------------|-----------------------|

| PW      | 774 mW                | 6.19 mW/°C      | 495 mW                | 402 mW                |

| GQC‡    | TBD                   | TBD             | TBD                   | TBD                   |

<sup>‡</sup> Product preview stage of development

#### recommended operating conditions

|                                                   |                        | MIN | MAX | UNIT |

|---------------------------------------------------|------------------------|-----|-----|------|

| Supply voltage, V <sub>DD,</sub> PV <sub>DD</sub> |                        | 2.7 | 5.5 | V    |

| High-level input voltage, V <sub>IH</sub>         | GAIN0, GAIN1, SHUTDOWN | 2   |     | V    |

| Low-level input voltage, VIL                      | GAIN0, GAIN1, SHUTDOWN |     | 0.8 | V    |

| Operating free-air temperature, T <sub>A</sub>    |                        | -40 | 85  | °C   |

# electrical characteristics at specified free-air temperature, $PV_{DD} = 5 V$ , $T_A = 25^{\circ}C$ (unless otherwise noted)

| PARAMETER       |                                                          | TEST CONDITIONS                   | MIN | TYP | MAX  | UNIT |    |

|-----------------|----------------------------------------------------------|-----------------------------------|-----|-----|------|------|----|

| IVosl           | Output offset voltage (measured differentially)          | $V_I = 0 V$ , $A_V = any gain$    |     |     |      | 25   | mV |

| PSRR            | Power supply rejection ratio                             | PV <sub>DD</sub> = 4.9 V to 5.1 V |     |     | 77   |      | dB |

| Ілні            | High-level input current                                 | $PV_{DD} = 5.5, V_I = PV_{DD}$    |     |     |      | 1    | μA |

| I <sub>IL</sub> | Low-level input current                                  | $PV_{DD} = 5.5, \qquad V_I = 0 V$ |     |     |      | 1    | μA |

| IDD             | Supply current, no filter (with or without speaker load) |                                   |     |     | 4    | 6    | mA |

| IDD(SD)         | Supply current, shutdown mode                            |                                   |     |     | 0.05 | 20   | μΑ |

## operating characteristics, $PV_{DD} = 5 V$ , $T_A = 25^{\circ}C$ , $R_L = 4 \Omega$ , gain = 6 dB (unless otherwise noted)

| PARAMETER    |                                                  | TEST (                  | MIN                     | TYP | MAX   | UNIT |         |

|--------------|--------------------------------------------------|-------------------------|-------------------------|-----|-------|------|---------|

| PO           | Output power                                     | THD = 1%,               | f = 1 kHz,              |     | 2     |      | W       |

| THD + N      | Total harmonic distortion plus noise             | P <sub>O</sub> = 1.5 W, | f = 20 Hz to 20 kHz     |     | <0.2% |      |         |

| BOM          | Maximum output power bandwidth                   | THD = 1%,               |                         |     | 20    |      | kHz     |

| <b>k</b> SVR | Supply ripple rejection ratio                    | f = 1 kHz,              | C <sub>BYP</sub> = 1 μF |     | 71    |      | dB      |

| SNR          | Signal-to-noise ratio                            |                         |                         |     | 95    |      | dB      |

| Vn           | Output noise voltage (no-noise weighting filter) | $C_{BYP} = 1 \ \mu F$ , | f = <10 Hz to 22 kHz    |     | 40    |      | μV(rms) |

| Zi           | Input impedance                                  |                         |                         |     | >15   |      | kΩ      |

SLOS328B - JUNE 2000 - REVISED MAY 2001

# electrical characteristics at specified free-air temperature, $\text{PV}_{\text{DD}}$ = 3.3 V, $\text{T}_{\text{A}}$ = 25°C (unless otherwise noted)

| PARAMETER |                                                          | TEST                    | MIN                       | TYP | MAX  | UNIT |    |

|-----------|----------------------------------------------------------|-------------------------|---------------------------|-----|------|------|----|

| IVosl     | Output offset voltage (measured differentially)          | V <sub>I</sub> = 0 V,   | A <sub>V</sub> = any gain |     |      | 25   | mV |

| PSRR      | Power supply rejection ratio                             | $PV_{DD} = 3.2 V to$    | 3.4 V                     |     | 61   |      | dB |

| IIH       | High-level input current                                 | PV <sub>DD</sub> = 3.3, | $V_{I} = PV_{DD}$         |     |      | 1    | μΑ |

| _         | Low-level input current                                  | PV <sub>DD</sub> = 3.3, | V <sub>I</sub> = 0 V      |     |      | 1    | μA |

| IDD       | Supply current, no filter (with or without speaker load) |                         |                           |     | 4    | 6    | mA |

| IDD(SD)   | Supply current, shutdown mode                            |                         |                           |     | 0.05 | 20   | μA |

# operating characteristics, PV<sub>DD</sub> = 3.3 V, T<sub>A</sub> = 25°C, R<sub>L</sub> = 4 $\Omega$ , gain = 6 dB (unless otherwise noted)

| PARAMETER        |                                                  | TEST                     | MIN                     | TYP | MAX   | UNIT |         |

|------------------|--------------------------------------------------|--------------------------|-------------------------|-----|-------|------|---------|

| РО               | Output power                                     | THD = 1%,                | f = 1 kHz               |     | 850   |      | mW      |

| THD + N          | Total harmonic distortion plus noise             | P <sub>O</sub> = 55 mW,  | f = 20 Hz to 20 kHz     |     | <0.2% |      |         |

| ВОМ              | Maximum output power bandwidth                   | THD = 0.7%               |                         |     | 20    |      | kHz     |

| k <sub>SVR</sub> | Supply ripple rejection ratio                    | f = 1 kHz,               | C <sub>BYP</sub> = 1 μF |     | 61    |      | dB      |

| SNR              | Signal-to-noise ratio                            |                          |                         |     | 93    |      | dB      |

| Vn               | Output noise voltage (no-noise weighting filter) | C <sub>BYP</sub> = 1 μF, | f = <10 Hz to 22 kHz    |     | 40    |      | μV(rms) |

| Zi               | Input impedance                                  |                          |                         |     | >15   |      | kΩ      |

## **APPLICATION INFORMATION**

## eliminating the output filter with the TPA2000D1

This section will focus on why the user can eliminate the output filter with the TPA2000D1.

#### effect on audio

The class-D amplifier outputs a pulse-width modulated (PWM) square wave, which is the sum of the switching waveform and the amplified input audio signal. The human ear acts as a band-pass filter such that only the frequencies between approximately 20 Hz and 20 kHz are passed. The switching frequency components are much greater than 20 kHz, so the only signal heard is the amplified input audio signal.

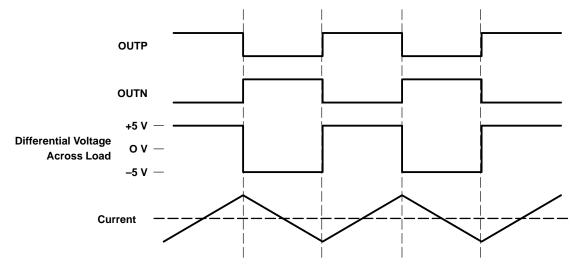

#### traditional class-D modulation scheme

The traditional class-D modulation scheme, which is used in the TPA005Dxx family, has a differential output where each output is 180 degrees out of phase and changes from ground to the supply voltage,  $V_{DD}$ . Therefore, the differential pre-filtered output varies between positive and negative  $V_{DD}$ , where filtered 50% duty cycle yields 0 V across the load. The traditional class-D modulation scheme with voltage and current waveforms is shown in Figure 1. Note that even at an average of 0 V across the load (50% duty cycle), the current to the load is high, causing high loss, thus causing a high supply current.

Figure 1. Traditional Class-D Modulation Scheme's Output Voltage and Current Waveforms Into an Inductive Load With No Input

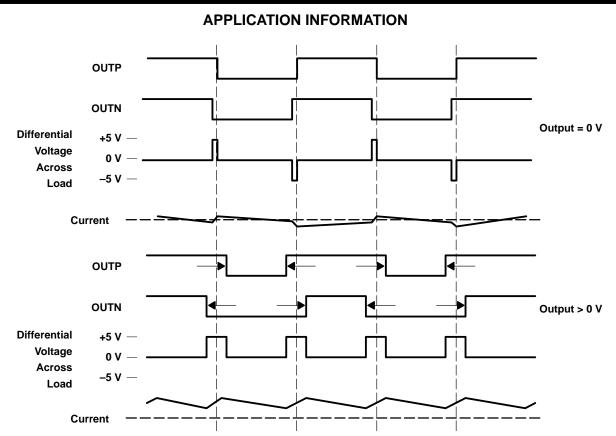

#### **TPA2000D1** modulation scheme

The TPA2000D1 uses a modulation scheme that still has each output switching from 0 to the supply voltage. However, OUTP and OUTN are now in phase with each other with no input. The duty cycle of OUTP is greater than 50% and OUTN is less than 50% for positive voltages. The duty cycle of OUTP is less than 50% and OUTN is greater than 50% for negative voltages. The voltage across the load sits at 0 V throughout most of the switching period greatly reducing the switching current, which reduces any I<sup>2</sup>R losses in the load.

SLOS328B - JUNE 2000 - REVISED MAY 2001

#### Figure 2. The TPA2000D1 Output Voltage and Current Waveforms Into an Inductive Load

#### efficiency: why you must use a filter with the traditional class-D modulation scheme

The main reason that the traditional class-D amplifier needs an output filter is that the switching waveform results in maximum current flow. This causes more loss in the load, which causes lower efficiency. The ripple current is large for the traditional modulation scheme because the ripple current is proportional to voltage multiplied by the time at that voltage. The differential voltage swing is  $2 \times V_{DD}$  and the time at each voltage is half the period for the traditional modulation scheme. An ideal LC filter is needed to store the ripple current from each half cycle for the next half cycle, while any resistance causes power dissipation. The speaker is both resistive and reactive, whereas an LC filter is almost purely reactive.

The TPA2000D1 modulation scheme has very little loss in the load without a filter because the pulses are very short and the change in voltage is  $V_{DD}$  instead of  $2 \times V_{DD}$ . As the output power increases, the pulses widen making the ripple current larger. Ripple current could be filtered with an LC filter for increased efficiency, but for most applications the filter is not needed.

An LC filter with a cut-off frequency less than the class-D switching frequency allows the switching current to flow through the filter instead of the load. The filter has less resistance than the speaker that results in less power dissipated, which increases efficiency.

## **APPLICATION INFORMATION**

#### effects of applying a square wave into a speaker

Audio specialists have advised for years not to apply a square wave to speakers. If the amplitude of the waveform is high enough and the frequency of the square wave is within the bandwidth of the speaker, the square wave could cause the voice coil to jump out of the air gap and/or scar the voice coil. A 250-kHz switching frequency, however, is not significant because the speaker cone movement is proportional to  $1/f^2$  for frequencies beyond the audio band. Therefore, the amount of cone movement at the switching frequency is very small. However, damage could occur to the speaker if the voice coil is not designed to handle the additional power. To size the speaker for added power, the ripple current dissipated in the load needs to be calculated by subtracting the theoretical supplied power (P<sub>SUP</sub> THEORETICAL) from the actual supply power (P<sub>SUP</sub>) at maximum output power (P<sub>OUT</sub>). The switching power dissipated in the speaker is the inverse of the measured efficiency ( $\eta_{MEASURED}$ ) minus the theoretical efficiency ( $\eta_{THEORETICAL}$ ) all multiplied by P<sub>OUT</sub>.

$$P_{SPKR} = P_{SUP} - P_{SUP THEORETICAL} (at max output power)$$

(1)

$P_{SPKR} = P_{OUT}(P_{SUP} / P_{OUT} - P_{SUP THEORETICAL} / P_{OUT}) \text{ (at max output power)}$ (2)

$$P_{SPKR} = P_{OUT}(1/\eta_{MEASURED} - 1/\eta_{THEORETICAL}) \text{ (at max output power)}$$

(3)

The maximum efficiency of the TPA2000D1 with an 8- $\Omega$  load is 85%. Using equation 3 with the efficiency at maximum power (78%), we see that there is an additional 106 mW dissipated in the speaker. The added power dissipated in the speaker is not an issue as long as it is taken into account when choosing the speaker.

#### when to use an output filter

Design the TPA2000D1 without the filter if the traces from amplifier to speaker are short. The TPA2000D1 passed FCC and CE radiated emissions with no shielding with speaker wires eight inches long or less. Notebook PCs and powered speakers where the speaker is in the same enclosure as the amplifier are good applications for class-D without a filter.

A ferrite bead filter can often be used if the design is failing radiated emissions without a filter, and the frequency sensitive circuit is greater than 1 MHz. This is good for circuits that just have to pass FCC and CE because FCC and CE only test radiated emissions greater than 30 MHz. If choosing a ferrite bead, choose one with high impedance at high frequencies, but very low impedance at low frequencies.

Use an output filter if there are low frequency (<1 MHz) EMI sensitive circuits and/or there are long leads from amplifier to speaker.

#### gain setting via GAIN0 and GAIN1 inputs

The gain of the TPA2000D1 is set by two input terminals, GAIN0 and GAIN1.

The gains listed in Table 1 are realized by changing the taps on the input resistors inside the amplifier. This causes the input impedance ( $Z_i$ ) to be dependent on the gain setting. The actual gain settings are controlled by ratios of resistors, so the actual gain distribution from part-to-part is quite good. However, the input impedance may shift by 30% due to shifts in the actual resistance of the input resistors.

For design purposes, the input network (discussed in the next section) should be designed assuming an input impedance of 20 k $\Omega$ , which is the absolute minimum input impedance of the TPA2000D1. At the higher gain settings, the input impedance could increase as high as 115 k $\Omega$ .

| GAIN0 | GAIN1 | AMPLIFIER GAIN<br>(dB) | INPUT IMPEDANCE<br>(kΩ) |

|-------|-------|------------------------|-------------------------|

|       |       | ТҮР                    | TYP                     |

| 0     | 0     | 6                      | 104                     |

| 0     | 1     | 12                     | 74                      |

| 1     | 0     | 18                     | 44                      |

| 1     | 1     | 23.5                   | 24                      |

# APPLICATION INFORMATION Table 1. Gain Settings

### input resistance

Each gain setting is achieved by varying the input resistance of the amplifier, which can range from its smallest value to over six times that value. As a result, if a single capacitor is used in the input high-pass filter, the -3 dB or cutoff frequency will also change by over six times.

The –3-dB frequency can be calculated using equation 4.

$$f_{-3 dB} = \frac{1}{2\pi C_i (R \parallel Z_i)}$$

(4)

#### input capacitor, Ci

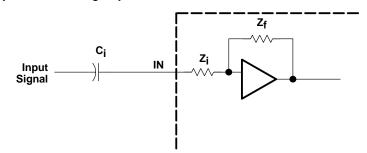

In the typical application an input capacitor ( $C_i$ ) is required to allow the amplifier to bias the input signal to the proper dc level for optimum operation. In this case,  $C_i$  and the input impedance of the amplifier ( $Z_i$ ) form a high-pass filter with the corner frequency determined in equation 5.

#### APPLICATION INFORMATION

#### input capacitor, C<sub>i</sub> (continued)

The value of  $C_i$  is important, as it directly affects the bass (low frequency) performance of the circuit. Consider the example where  $Z_i$  is 20 k $\Omega$  and the specification calls for a flat bass response down to 80 Hz. Equation 5 is reconfigured as equation 6.

$$C_{i} = \frac{1}{2\pi Z_{i} f_{c}}$$

(6)

In this example,  $C_i$  is 0.1  $\mu$ F, so one would likely choose a value in the range of 0.1  $\mu$ F to 1  $\mu$ F. If the gain is known and will be constant, use  $Z_i$  from Table 1 to calculate  $C_i$ . A further consideration for this capacitor is the leakage path from the input source through the input network ( $C_i$ ) and the feedback network to the load. This leakage current creates a dc offset voltage at the input to the amplifier that reduces useful headroom, especially in high gain applications. For this reason a low-leakage tantalum or ceramic capacitor is the best choice. When polarized capacitors are used, the positive side of the capacitor should face the amplifier input in most applications as the dc level there is held at  $V_{DD}/2$ , which is likely higher than the source dc level. Note that it is important to confirm the capacitor polarity in the application.

$C_i$  must be 10 times smaller than the bypass capacitor to reduce clicking and popping noise from power on/off and entering and leaving shutdown. After sizing  $C_i$  for a given cutoff frequency, size the bypass capacitor to 10 times that of the input capacitor.

$$C_i \leq C_{BYP} / 10$$

(7)

#### power supply decoupling, C<sub>S</sub>

The TPA2000D1 is a high-performance CMOS audio amplifier that requires adequate power supply decoupling to ensure the output total harmonic distortion (THD) is as low as possible. Power supply decoupling also prevents oscillations for long lead lengths between the amplifier and the speaker. The optimum decoupling is achieved by using two capacitors of different types that target different types of noise on the power supply leads. For higher frequency transients, spikes, or digital hash on the line, a good low equivalent-series-resistance (ESR) ceramic capacitor, typically 0.1  $\mu$ F placed as close as possible to the device V<sub>DD</sub> lead works best. For filtering lower-frequency noise signals, a larger aluminum electrolytic capacitor of 10  $\mu$ F or greater placed near the audio power amplifier is recommended.

#### midrail bypass capacitor, CBYP

The midrail bypass capacitor ( $C_{BYP}$ ) is the most critical capacitor and serves several important functions. During start-up or recovery from shutdown mode,  $C_{BYP}$  determines the rate at which the amplifier starts up. The second function is to reduce noise produced by the power supply caused by coupling into the output drive signal. This noise is from the midrail generation circuit internal to the amplifier, which appears as degraded PSRR and THD+N.

Bypass capacitor ( $C_{BYP}$ ) values of 0.47- $\mu$ F to 1- $\mu$ F ceramic or tantalum low-ESR capacitors are recommended for the best THD and noise performance.

Increasing the bypass capacitor reduces clicking and popping noise from power on/off and entering and leaving shutdown. To have minimal pop,  $C_{BYP}$  should be 10 times larger than  $C_i$ .

$$C_{BYP} \ge 10 \times C_i$$

(8)

SLOS328B - JUNE 2000 - REVISED MAY 2001

## APPLICATION INFORMATION

#### differential input

The differential input stage of the amplifier cancels any noise that appears on both input lines of the channel. To use the TPA2000D1 EVM with a differential source, connect the positive lead of the audio source to the INP input and the negative lead from the audio source to the INN input. To use the TPA2000D1 with a single-ended source, ac ground the INN input through a capacitor and apply the audio single to the input. In a single-ended input application, the INN input should be ac-grounded at the audio source instead of at the device input for best noise performance.

#### shutdown modes

The TPA2000D1 employs a shutdown mode of operation designed to reduce supply current  $(I_{DD})$  to the absolute minimum level during periods of nonuse for battery-power conservation. The <u>SHUTDOWN</u> input terminal should be held high during normal operation when the amplifier is in use. Pulling <u>SHUTDOWN</u> low causes the outputs to mute and the amplifier to enter a low-current state,  $I_{DD(SD)} = 1 \ \mu A$ . <u>SHUTDOWN</u> should never be left unconnected because amplifier operation would be unpredictable.

#### using low-ESR capacitors

Low-ESR capacitors are recommended throughout this application section. A real (as opposed to ideal) capacitor can be modeled simply as a resistor in series with an ideal capacitor. The voltage drop across this resistor minimizes the beneficial effects of the capacitor in the circuit. The lower the equivalent value of this resistance the more the real capacitor behaves like an ideal capacitor.

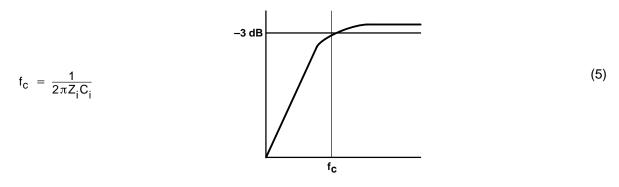

#### evaluation circuit

NOTE: R1, R2, and R3 are used in the EVM but are not required for normal applications.

## **APPLICATION INFORMATION**

| REFERENCE            | DESCRIPTION                                                        | SIZE            | QUANTITY | MANUFACTURER | PART NUMBER      |

|----------------------|--------------------------------------------------------------------|-----------------|----------|--------------|------------------|

| C1 – C6              | Capacitor, ceramic, 1 µF, +80%/-20%, Y5V, 16 V                     | 0805            | 6        | Murata       | GRM40-Y5V105Z16  |

| C7                   | Capacitor, ceramic, 10 $\mu\text{F}$ , +80%/–20%, Y5V, 16 V        | 1210            | 1        | Murata       | GRM235-Y5V106Z16 |

| C8                   | Capacitor, ceramic, 220 pF, ±10%, XICON, 50 V                      | 0805            | 1        | Mouser       | 140-CC501B221K   |

| R1†, R2†,<br>R3†, R4 | Resistor, chip, 120 k $\Omega$ , 1/10 W, 5%, XICON                 | 0805            | 4        | Mouser       | 260–120K         |

| U1                   | IC, TPA2000D1, audio power amplifier, 2-W, single channel, class-D | 24-pin<br>TSSOP | 1        | TI           | TPA2000D1PW      |

#### Table 2. TPA2000D1 Evaluation Bill of Materials

<sup>†</sup> These components are used in the EVM, but they are not required for normal applications.

SLOS328B - JUNE 2000 - REVISED MAY 2001

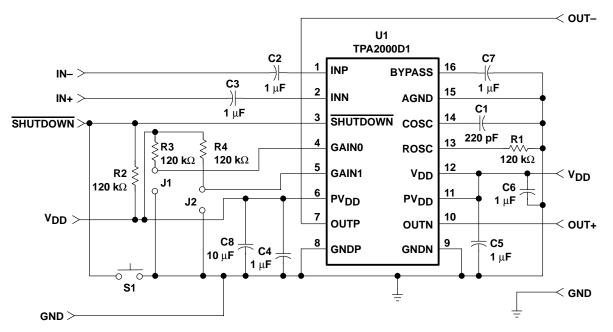

**MECHANICAL DATA**

PLASTIC SMALL-OUTLINE PACKAGE

### PW (R-PDSO-G\*\*) 14 PINS SHOWN

NOTES: A. All linear dimensions are in millimeters.

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold flash or protrusion not to exceed 0,15.

D. Falls within JEDEC MO-153

SLOS328B - JUNE 2000 - REVISED MAY 2001

**MECHANICAL DATA**

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. MicroStar Junior BGA ™ configuration

- D. Falls within JEDEC MO-225

MicroStar Junior BGA is a trademark of Texas Instruments.

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Customers are responsible for their applications using TI components.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, license, warranty or endorsement thereof.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations and notices. Representation or reproduction of this information with alteration voids all warranties provided for an associated TI product or service, is an unfair and deceptive business practice, and TI is not responsible nor liable for any such use.

Resale of TI's products or services with <u>statements different from or beyond the parameters</u> stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service, is an unfair and deceptive business practice, and TI is not responsible nor liable for any such use.

Also see: Standard Terms and Conditions of Sale for Semiconductor Products. www.ti.com/sc/docs/stdterms.htm

Mailing Address:

Texas Instruments Post Office Box 655303 Dallas, Texas 75265

Copyright © 2001, Texas Instruments Incorporated