| Parameter                                 | Conditions                                                             | AD892EJ/AD892TJ |              |              |                        |

|-------------------------------------------|------------------------------------------------------------------------|-----------------|--------------|--------------|------------------------|

|                                           |                                                                        | Min             | Тур          | Max          | Units                  |

| COMPARATORS                               |                                                                        |                 |              |              |                        |

| Input Offset Voltage                      |                                                                        |                 | 0.25         | 2.0          | mV                     |

| Input Offset Current                      |                                                                        |                 | 100          |              | nA                     |

| Input Bias Current                        |                                                                        |                 | 0.68         |              | μA                     |

| Open Loop Gain                            | f = 10  MHz                                                            |                 | 66           |              | dB                     |

| Input Resistance                          | Differential                                                           |                 | 500          |              | kΩ                     |

| Input Capacitance                         | Differential                                                           |                 | 1            | 5            | pF                     |

| Input Common Mode Range                   | Referred to Digital Ground                                             | 2.8             | -            | + 5          | V                      |

| OUTPUT/FILTER ONE-SHOT                    | AD892T                                                                 |                 |              | <b>-</b>     |                        |

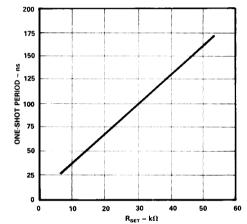

| Resistor Scaling <sup>5</sup>             | One-Shot Pulse $\approx 10+3.0 \times R_{SET}$                         |                 |              |              | ns                     |

| Pulse Duration                            | One-shot I use $\sim 10 \pm 3.0 \times K_{SET}$                        | 9               |              | 180          | ns                     |

| ruise Duration /                          | $R_{SET} = R_{min} \text{ to } R_{max}$ $R_{SET} = 10 \text{ k}\Omega$ | 31              | 38           | 45           | ns                     |

| Designar Denge                            |                                                                        | 0.75            | 36           | 56           | kΩ                     |

| Resistor Range                            | $R_{SET} = R_{min}$ to $R_{max}$                                       | 0.75            | <del> </del> | ) U          | 177                    |

| OUTPUT/FILTER ONE-SHOT                    | AD892E                                                                 |                 |              |              | Manager and the second |

| Resistor Scaling <sup>5</sup>             | One-Shot Pulse $\approx 3.5 + 3.5 \times R_{SET}$                      | -               |              | 5.2          | ns                     |

| Pulse Duration                            | $R_{SET} = R_{min}$ to $R_{max}$                                       | 7               |              | 52           | ns                     |

| T                                         | $R_{SET} = 3 k\Omega$                                                  | 9               | 14           | 19           | ns                     |

| Resistor Range                            | $R_{SET} = R_{min} \text{ to } R_{max}$                                | 1               |              | 14           | kΩ                     |

| EXTERNAL LOGIC                            |                                                                        |                 |              |              |                        |

| Data Output Level (AD892T)                | 400 $\Omega$ Pull-Up to +5 V                                           |                 |              |              |                        |

| Output Logic "1"                          | User Defined (Open Collector Output)                                   |                 |              |              |                        |

| Output Logic "0"                          |                                                                        |                 | 0.25         | 0.5          | V                      |

| Data Output Level (AD892E)                | 1 kΩ Pull-Down to Ground                                               |                 |              |              |                        |

| Output Logic "1"                          |                                                                        | 4.02            | 4.15         | 4.19         | V                      |

| Output Logic "0"                          |                                                                        | 3.05            | 3.15         | 3.37         | V                      |

| DATA THROUGHPUT                           |                                                                        |                 |              |              |                        |

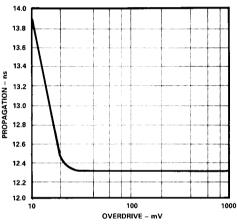

| Propagation Delay <sup>6</sup>            | Differentiator Input to Data Output                                    |                 | 12.3         |              | ns                     |

| Additional Pulse Pairing <sup>7</sup>     |                                                                        |                 |              | 1000         | ps                     |

| Max Transfer Rate (AD892T)                |                                                                        | 25              |              |              | Mb/s                   |

| Max Transfer Rate (AD892E)                |                                                                        | 30              |              |              | Mb/s                   |

| POWER SUPPLY REQUIREMENTS                 |                                                                        |                 |              |              |                        |

| Supply Voltage V <sub>12</sub>            |                                                                        | 10.8            | 12           | 13.2         | V                      |

| Supply Voltage V <sub>5</sub>             |                                                                        | 4.5             | 5            | 5.5          | v                      |

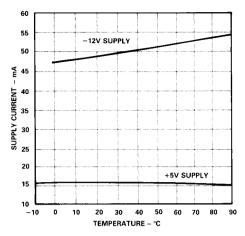

| Quiescent Current I <sub>12</sub>         | $T_{\min}$ to $T_{\max}$                                               | 40              | 49           | 61           | mA                     |

| Quiescent Current I <sub>5</sub>          | T <sub>min</sub> to T <sub>max</sub>                                   | 10              | 16           | 24           | mA                     |

| ABSOLUTE MAXIMUM RATINGS <sup>8</sup>     | - min max                                                              |                 |              | <del> </del> | 1                      |

|                                           |                                                                        |                 |              | 14.5         | V                      |

| Supply Voltage V <sub>12</sub>            |                                                                        |                 |              | 7.5          | V                      |

| Supply Voltage V <sub>5</sub>             |                                                                        | 0.0             |              | i            | 1                      |

| RF Input Stage Differential Input Voltage |                                                                        | -0.8            |              | 5.6          | V                      |

| Comparator Differential Input Voltage     |                                                                        | -0.8            |              | 5.6          | °C                     |

| Storage Temperature Range                 |                                                                        | -65<br>0        | -            | 130          | 0 ℃                    |

| Operating Temperature Range <sup>9</sup>  | Soldering 60 See                                                       | 0               |              | 70           | ℃                      |

| Lead Temperature Range                    | Soldering 60 Sec                                                       |                 | l            | 300          | \                      |

#### NOTES

<sup>&</sup>lt;sup>1</sup>Gain calibrated in gain set mode with 0 volts applied to the gain set pin.

$<sup>^2</sup> Clamp$  operation is specified with a source impedance of 200  $\Omega$  in series with 0.1  $\mu F.$

<sup>&</sup>lt;sup>3</sup>Over the full 50 MHz bandwidth of the AD892E/AD892T, the worst-case rms signal-to-noise ratio is 40 dB or better with a 40 dB AGC range.

<sup>&</sup>lt;sup>4</sup>Measured using a 4 kΩ resistor connected between qualifier threshold pin and ground; also between the differentiator pin and ground.

<sup>&</sup>lt;sup>5</sup>R<sub>SET</sub> specified in kΩ.

<sup>&</sup>lt;sup>6</sup>Propagation delay is measured from the zero crossing comparator input to the "Data Output" with 200 mV overdrive.

Measurements were performed using a ±100 mV square wave having a rise time under 5 ns; this was applied to the input of the zero crossing comparator. The resultant pulse pairing is the difference in delay times for two consecutive output pulses.

<sup>\*</sup>Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other condition above those indicated in the operational section of this specification is not implied. Exposure to absolute rating conditions for extended period may affect device reliability.

<sup>&</sup>lt;sup>9</sup>44-pin PLCC package:  $\theta_{JA} = +65^{\circ}\text{C/watt}$ .

Specifications in **boldface** are tested on all production units at final electrical test. Results from those tests are used to calculate outgoing quality levels. All min and max specifications are guaranteed, although only those shown in boldface are tested on all production units.

Specifications subject to change without notice.

# Typical Characteristics (@ +25°C with +5 V, +12 V Supplies)

Figure 1. Supply Current vs. Temperature

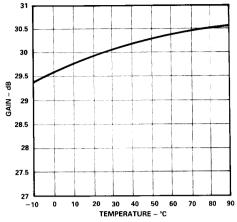

Figure 2. VGA Gain vs. Temperature

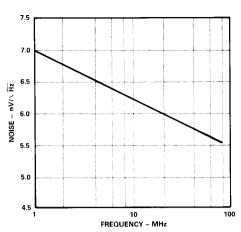

Figure 3. VGA Input Voltage Noise vs. Frequency

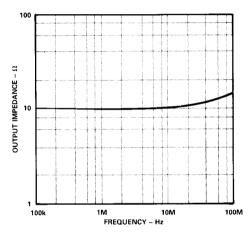

Figure 4. VGA Output Impedance vs. Frequency

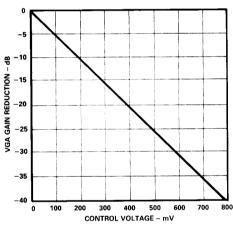

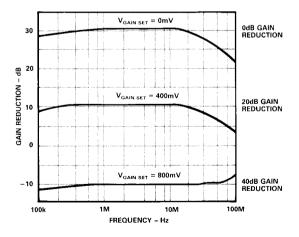

Figure 5. VGA Gain Reduction vs. Control Voltage

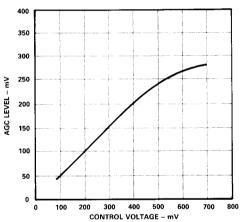

Figure 6. AGC Level vs. Control Voltage

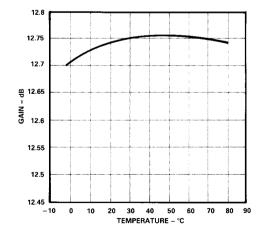

Figure 7. ×4 Buffer Gain vs. Temperature

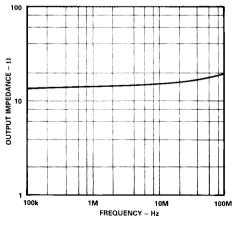

Figure 8. ×4 Buffer Output Impedance vs. Frequency

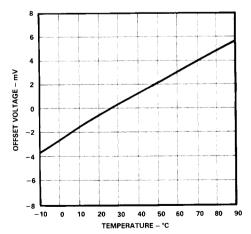

Figure 9. Rectifier Offset vs. Temperature

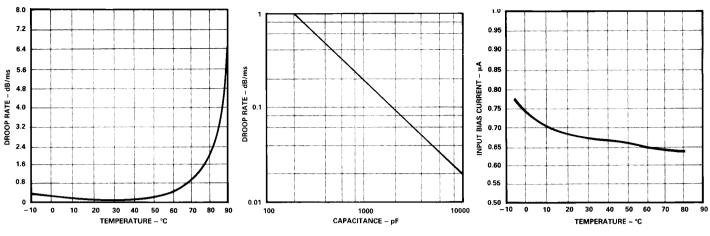

Figure 10. Hold Mode Droop Rate vs. Temperature ( $C_{HOLD} = 1000pF$ )

Figure 11. Hold Mode Droop Rate vs. Capacitance

Figure 12. Comparator Input Bias Current vs. Temperature

Figure 13. Propagation Delay (Comparator to Data Out) vs. Input Overdrive

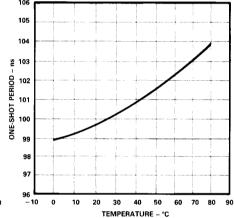

Figure 14. One-Shot Period vs. Temperature ( $R_{\rm SET}=30~{\rm k}\Omega$ )

Figure 15. One-Shot Period vs.  $R_{SET}$

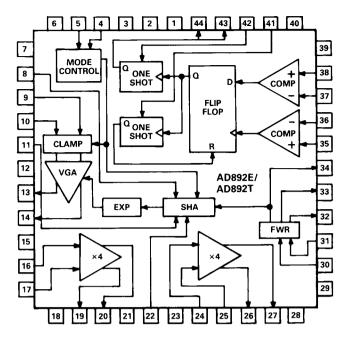

#### CHANNEL PROCESSING STAGES

#### The VGA Stage

The 30 dB variable gain stage input is biased at a potential of 5.0 V above analog ground. No additional dc bias is required, but ac coupling is necessary. The bias voltage is maintained during normal operation and during operation of the read-afterwrite recovery clamp.

The VGA differential output stage is an emitter follower with nominal dc biasing of 6.7 V. An internal 1.4 mA current source provides bias current to the output emitter followers. Output drive can be increased by an additional 1.4 mA by paralleling external resistors to the analog ground. However, caution should be exercised in order to avoid causing excess power dissipation for the package. The recommended output level for the VGA is 300 mV p-p differential into 200  $\Omega$  loads.

When the AD892E/AD892T is used in the "VGA Set Gain" mode, Control Bit A = 0 (Pin 5) and Bit B = 1 (Pin 4), the VGA gain is programmable through the "VGA Level Set" pin (Pin 11). The VGA gain and exponentiator scale factor are trimmed with respect to the dc control potential applied to the "VGA Level Set" pin. A 0 V potential applied to the "VGA Level Set" pin will produce a nominal VGA gain of 30 dB. Each 20 mV increment of voltage applied will produce a 1 dB reduction in VGA gain. Therefore, a simple equation can be used to calculate the nominal gain of the VGA in this mode:

$$VGA\ Gain\ (dB) = 30 - (50 \times V_{SET\ LEVEL})$$

The AD892E/AD892T offers a read-after-write overdrive protection clamp. The clamp mode, Control Bit A = 0 (Pin 5), Bit B = 0 (Pin 4), lowers the input impedance of the VGA from nominally 24 k $\Omega$  to 28  $\Omega$ . In order for the clamp to operate correctly with an emitter driven input, a 50  $\Omega$  minimum resistor should be placed in series with the input coupling capacitors. The input resistor can be used in conjunction with a shunt capacitor to limit the input bandwidth. For example, a 100  $\Omega$  series resistor with a 10 pF shunt capacitor will limit the input bandwidth to 75 MHz. When the VGA input is being driven by an open collector driver with resistive termination, no additional series resistors are required.

Figure 16. VGA Gain Reduction vs. Frequency

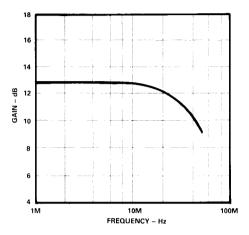

#### The ×4 Buffers

The inputs of these stages have on chip dc biasing of 4.2 V (the internal reference voltage,  $V_{\text{REF}}$ ); therefore, no input bias current path needs to be provided. The inputs to the buffers should then be ac coupled. When not used, the inputs should be shorted together in order to avoid noise pickup and instability.

The nominal dc output level is 5.75 V with an internal 2.9 mA pull down current source. Output drive can be increased in a similar manner to that described for the VGA stage. Therefore, output current can be increased by up to an additional 2.9 mA by paralleling external resistors to analog ground. As before, precautions to limit excessive overall power dissipation apply when steps are taken to increase the output drive capability.

Figure 17.  $\times$ 4 Buffer Gain vs. Frequency (200  $\Omega$  in Series with 1  $\mu$ F Load)

#### The Full Wave Rectifiers

The inputs to the three full wave rectifiers are biased at an internal voltage of 5 V; therefore, only ac coupling is recommended. The full wave rectifier outputs consist of three nearly identical stages. All three employ emitter follower outputs. The nominal output voltage with zero input voltage is close to the reference voltage of 4.2 V (Pin 39).

The rectified output to the sample-and-hold amplifier (Pin 34) has an internal 2.15 k $\Omega$  resistor in series with one diode tied to ground. This allows for accurate AGC operation in sinusoidal fields; however, if your application requires a peak-hold mode AGC operation, the AD892E/AD892T can be ordered with the resistor removed.

The other two full wave rectifier outputs – one rectified signal to drive the differentiator network and another to derive the threshold for the peak detector – are connected directly to their respective emitter follower output stages. Neither output has a built in pull-down resistor. Therefore, to obtain a zero nominal offset, their quiescent currents must be matched. A 1 mA quiescent current is recommended to ensure accurate operation.

#### The AGC Sample and Hold

When the AD892E/AD892T is used in the "AGC Acquire" mode, Control Bit A=1 (Pin 5) and Bit B=1 (Pin 4), the AGC level is programmable through the "AGC Level Set" pin (Pin 8). The AGC Level is defined as the AVERAGE of the full wave rectifier output voltage (Pin 34). A 400 mV dc potential applied to the "AGC Level Set" pin will produce a nominal average AGC level of 200 mV. Each 10 mV increment/decrement of the applied "AGC level set" voltage will produce a 5 mV increase/decrease in the average AGC level. Therefore, a simple equation can be used to calculate the nominal AGC level in this mode:

$$AGC\ Level = 0.5 \times V_{AGC\ LEVEL\ SET}$$

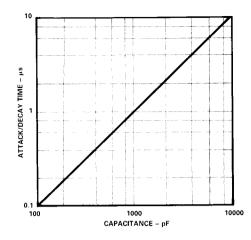

Without a peak hold capacitor at the full wave rectifier output for the sample-and-hold amplifier (Pin 34), accurate AGC operation only occurs with sinusoidal input signals. If your application requires the AGC operation to use a peak hold scheme, the AD892E/AD892T can be ordered with the pull down resistor removed on the rectified signal output to the sample-and-hold amplifier (Pin 34). The removal of this resistor now allows the user to program the degree of peak hold, by applying a RC combination to the rectified signal output for the sample-andhold amplifier. The addition of the capacitor alters the symmetry of the attack and decay rates of the rectifier, which is otherwise symmetric in operation. In order to ensure that the overall AGC response is the same for both high to low and low to high input level steps, it is necessary to make the rectifier attack and decay times at least a factor of two less than the AGC response time.

The AGC acquire time is approximately 1  $\mu s$  per 1000 pF of hold capacitor applied at Pin 22. A low leakage variety of hold capacitor, such as a silver mica, is necessary to ensure a low droop rate. The "VGA Level Set" pin should be tied to analog ground if not used.

The AGC control potential is present at the "sample-and-hold capacitor" pin. If control over open loop gain is desired, based on AGC control potentials measured during trial AGC operations, a FET input op amp should be used to buffer this node in order to avoid disturbing the hold operation.

Figure 18. AGC Attack/Decay vs. Capacitance

#### **DATA QUALIFIER STAGES**

The data qualifier section of the AD892E/AD892T consists of two comparators, one D-type flip-flop, an internal bandgap reference and a pair of externally adjustable one-shots. One comparator is used to provide data amplitude qualification, while the other acts as a zero-crossing detector when used with an external passive differentiator circuit.

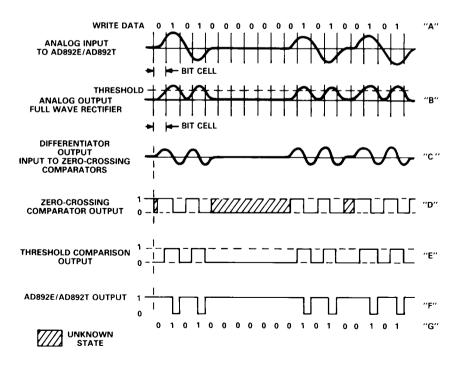

Figure 19 illustrates the operation of the data qualifier using the recommended passive delay line differentiator described in the Application section. Sequence "A" represents the pattern written on the disk where a Logic "1" is a change in magnetic state. Each change in magnetic state results in an output pulse. The analog input to the data qualifier consists of a sequence of rectified pulses "B." The data pattern shown is worst case for a RLL 1, 7 code input. "C" represents the output waveform from the external differentiator, such that the points at which zerocrossings occur correspond to the peaks of the analog input "B." Sequence "D" shows the output from the zero-crossing comparator. Changes in state of this output are used to clock the internal D-type flip-flop. The flip-flop is enabled using the output "E" from the amplitude-threshold comparator. The amplitude-comparator output changes state only when the analog input exceeds the programmed threshold level. When the threshold level is exceeded and a zero-crossing event occurs, the flip-flop changes state, producing an output pulse "F." The duration of this pulse, seen at the "Data Output" pin (Pin 43), is set using an external resistor (applied between Pin 42 and  $V_5$ ), as is the internal time-out (a resistor applied between Pin 41 and V<sub>5</sub>) which is used to prevent noise induced retriggering. The final output data sequence is shown in "G". As can be seen, despite inflections in the analog input, the data is correctly detected and the output is a time-shifted version of the write

Since the RLL 1, 7 code input is the most demanding of the popular encoding schemes to qualify, the AD892E/AD892T easily handles such other codes as MFM and RLL 2, 7.

#### **GENERAL LAYOUT REQUIREMENTS**

The channel processing section of the AD892E/AD892T has almost 60 dB of total gain available at 50 MHz. Good RF layout must be used in the circuit board to avoid oscillations in the 150 MHz to 350 MHz region. A single pole RC filter applied at the input of each stage, with a cut-off in the region of 75 MHz to 125 MHz, will help avoid oscillation problems. As a general rule, keep the connections to interstage components as short as possible; it is also recommended that any low pass filtering that may be required by the system be performed between the VGA stage and the first ×4 buffer amplifier. A ground plane should be used to surround any interstage components wherever possible. If these simple rules are followed, stable operation should be assured.

A parallel combination of 0.1  $\mu F$  and 0.01  $\mu F$  ceramic capacitors should be used as close to the supply pins as possible, for both the +12 V analog (Pin 18), +12 V digital (Pin 40) and +5 V (Pin 1) supplies. It is also recommended that the  $V_{REFER-ENCE}$  (Pin 39) is decoupled with a 0.1  $\mu F$  ceramic capacitor.

Extensive use of a ground plane is recommended. An analog ground (Pin 28) is supplied for the AGC section, while two digital grounds are supplied: one for the data qualifier section (Pin 6), and one for the emitter of the open collector output transistor (Pin 44 for the AD892T only). The digital ground should be connected to the analog ground as near to the power supply common as possible to minimize noise injection to the analog ground.

The filter and output pulse setting resistors should be tied, as directly possible, to the +5 V supply. To prevent the data output pulse from coupling into the output pulse setting circuit, a 1000 pF capacitor can be used in parallel with the output pulse setting resistor.

Figure 19. AD892E/AD892T Operation for Worst Case 1–7 RLL

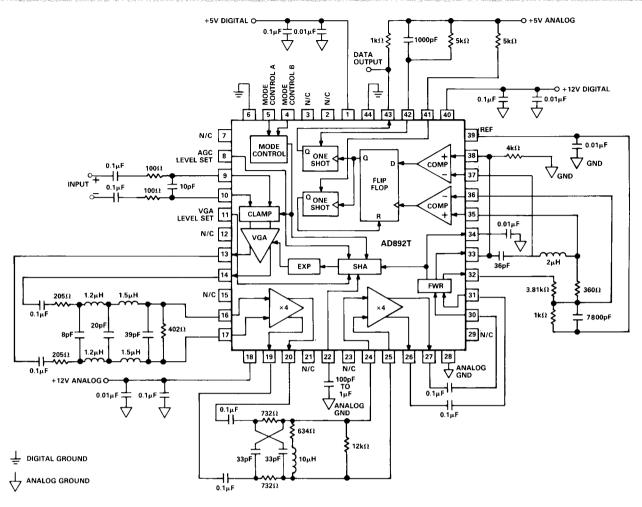

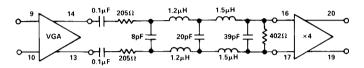

Figure 20. Typical AD892T Connection for a 15 MHz Channel

#### A 15 MHz APPLICATION

Figure 20 shows a typical application using the AD892T in a 15 MHz channel. This circuit includes a 5-pole 15 MHz Gaussian-to-6 dB transitional filter plus a second-order RLC time domain equalizer. A single ended passive delay-line differentiator is also included.

#### Using Equalizers with the AD892E/AD892T

The AD892E/AD892T is ideal for applications where equalization is employed. The  $\times 4$  buffer output drivers are designed to operate into 200  $\Omega$  loads, making tapped delay-line designs easy. Sum and differencing of different tap weights can be achieved by simple resistive dividers.

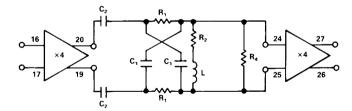

### The RLC Equalizer

As an alternative, a simple RLC network can be implemented to provide a low cost, fully differential alternative to the three tap, tapped delay-line equalizer which often is used for pulse slimming. The equalizer shown in Figure 21 approximates a function in the form of F  $(\omega\tau)=1-k$  cos  $(\omega\tau)$ . The approximation

Figure 21. RLC Equalizer

is achieved by first creating a magnitude function and then adding phase compensation to provide a flat group delay characteristic over the frequency range of interest. Our 15 MHz application example employs the cosine equalizer; where K=0.6 and  $\tau=24$  ns. The magnitude and group delay characteristics of the equalizer employed in the 15 MHz application are shown in Figures 22 and 23, respectively.

#### Magnitude Approximation

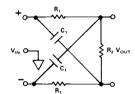

The magnitude approximation is achieved by an RC lattice (Figure 24).

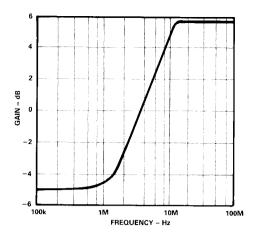

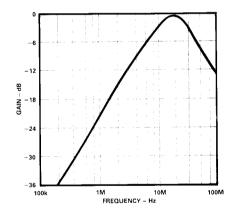

Figure 22. RLC Equalizer Magnitude Response

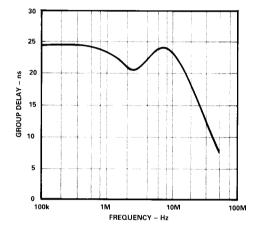

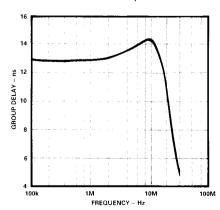

Figure 23. RLC Equalizer Group Delay Response

Figure 24. RC Lattice

The transfer function is as follows:

$$\frac{V_{OUT}}{V_{IN}} = \frac{R_2(1 - CR_1 S)}{CR_1 R_2 S + R_2 + 2R_1}$$

at dc

$$\frac{V_{OUT}}{V_{IN}} = \frac{R_2}{2R_1 + R_2}$$

and at high frequency

$$\frac{V_{OUT}}{V_{IN}} = -1$$

In the above case we can see that K in the  $1-K\cos(\omega\tau)$  expression is given by:

$$K = \frac{R_1}{R_1 + R_2}$$

and the average gain is then equal to:

$$\frac{R_1+R_2}{2R_1+R_2}$$

From these results we can see that K can be changed by altering either  $R_1$  or  $R_2$ . However, doing so will change the frequency response of the network. Normal rules of impedance scaling should be followed when changing the value of either  $R_1$  or  $R_2$ .

#### **Group Delay Approximation**

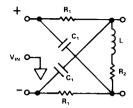

An inductor can now be added to give a suitable group delay response. We now have the RLC lattice depicted in Figure 25.

Figure 25. RLC Lattice

The complete derivation for the response of this equalizer is as follows:

$$\frac{V_{OUT}}{V_{IN}} = \frac{\begin{bmatrix} \frac{R_2}{2} + \frac{SL}{2} \end{bmatrix} \cdot \frac{1}{SC}}{\frac{R_2}{2} + \frac{SL}{2} + \frac{1}{SC}} - \frac{\begin{bmatrix} \frac{R_2}{2} + \frac{SL}{2} \end{bmatrix} \cdot R_1}{\frac{R_2}{2} + \frac{SL}{2} \end{bmatrix} \cdot \frac{1}{SC}}{\frac{R_2}{2} + \frac{SL}{2} + \frac{SL}{2} \end{bmatrix} \cdot R_1}{\frac{R_2}{2} + \frac{SL}{2} + \frac{1}{SC}}$$

$$= \frac{\left[\frac{R_2}{2} + \frac{SL}{2}\right] \cdot \left[\frac{1}{SC} - R_1\right]}{\frac{R_1 R_2}{2} + \frac{SLR_1}{2} + \frac{R_1}{SC} + \frac{R_2}{2SC} + \frac{SL}{2SC}}$$

$$= - \left[ \frac{S^2 R_1 LC - S [L - CR_1 R_2] - R_2}{S^2 R_1 LC + S [L + CR_1 R_2] + 2R_1 + R_2} \right]$$

ALL PASS NETWORK =

$$- \left[ \frac{S^2 R_1 LC - S [L + CR_1 R_2] + 2 R_1 + R_2}{S^2 R_1 LC + S [L + CR_1 R_2] + 2 R_1 + R_2} \right] +$$

MAGNITUDE

$$\begin{bmatrix} 2[R_1 + R_2 + SCR_1 R_2] \\ \overline{S^2 R_1 LC + S [L + CR_1 R_2] + 2R_1 + R_2} \end{bmatrix}$$

There is no "best" solution to the group delay question. The choice of inductor value in the 15 MHz application example was based on SPICE simulation of the transfer function. However, if K remains the same as in the example, then altering  $\tau$  becomes a simple frequency scaling of the network.

If R<sub>1</sub> and R<sub>2</sub> remain unchanged

and if

$$\tau \rightarrow \tau'$$

then

$$C \rightarrow \frac{\tau'C}{\tau}$$

and  $L \rightarrow \frac{\tau L}{\tau'}$

Any deviation from the K value given in the example will require the value of L to be recalculated.

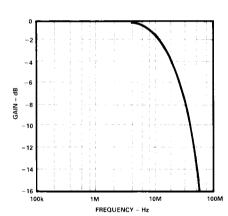

## CHOICE OF LOW PASS FILTER WITH THE RECOMMENDED EQUALIZER

A fifth order, Gaussian-to -6 dB transitional filter is recommended for use with the equalizer. This type of low pass filter, shown in Figure 26, is also used in the 15 MHz application example. Low group delay ripple and high out-of-band rejection make this design work well with the recommended equalizer and differentiator networks. The recommended location for the low pass filter is between the VGA and the first  $\times 4$  buffer. The equalizer is then placed between the first and second  $\times 4$  buffers. This minimizes the potential for oscillations induced by interstage feedback.

Figure 26. 5th Order Guassian to 6 dB Transitional Filter

The magnitude and group delay characteristics of this filter are shown in Figures 27 and 28, respectively.

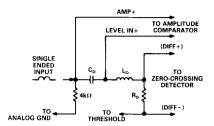

### THE SINGLE ENDED PASSIVE DELAY-LINE DIFFERENTIATOR

The recommended configuration of the passive delay-line differentiator is shown in Figure 29. Again, this configuration is employed in the 15 MHz application example.

Figure 29. Single Ended Configuration of Passive Delay Line Differentiator

#### RECOMMENDED COMPONENTS

$$f_D = \frac{1}{2 \pi \sqrt{L_D C_D}}$$

$f_D = 1.5$  Times the Maximum Desired Differentiated Frequency

$R_D$  Minimum Value: 120  $\Omega$ 150  $\Omega$  or Greater is Recommended

$$1.3 \le K \le 1.7$$

(Best Magnitude Response)

(Best Group Delay Response)

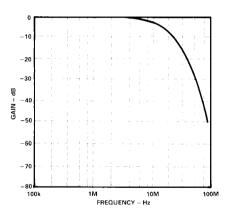

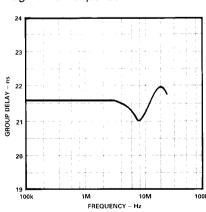

Figures 30 through 33 show the typical performance to be expected from the recommended passive delay-line differentiator. The choice of components used to obtain these characteristics are the ones used in the 15 MHz application example.

Figure 27. Gaussian Low Pass Filter Magnitude Response

Figure 28. Gaussian Low Pass Filter Group Delay Response

Figure 30. Magnitude Response of Undifferentiated Output

Figure 31. Group Delay Characteristics of Undifferentiated Output

Figure 32. Magnitude Response of Differentiated Output

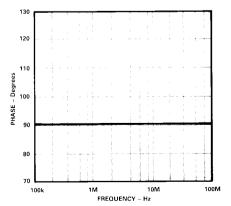

Figure 33. Relative Phase Between

Differentiated and Undifferentiated

Output

#### Description Pin

- +5 V Supply 1

- 2 No Connection (Can Be Left Floating)

- 3 No Connection (Can Be Left Floating)

- 4 Mode Control Bit B (TTL Compatible)

- Mode Control Bit A (TTL Compatible) 5

- Digital Ground 6

- No Connection (Can Be Left Floating) 7

- "AGC Level Set" Input Voltage 8

- Variable Gain Amplifier Input (+) 9

- 10 Variable Gain Amplifier Input (- )

- "VGA Level Set" Input Voltage 11

- No Connection (Can Be Left Floating) 12

- Variable Gain Amplifier Output (-) 13

- 14 Variable Gain Amplifier Output (+)

- No Connection (Can Be Left Floating) 15

- #1 12.75 dB Buffer Input (- ) 16

- #1 12.75 dB Buffer Input (+) 17

- +12 V Supply (Analog) 18

- #1 12.75 dB Buffer Output (+) 19

- 20 #1 12.75 dB Buffer Output (- )

- No Connection (Can Be Left Floating) 21

- 22 Sample-and-Hold Capacitor

- No Connection (Can Be Left Floating) 23

- #2 12.75 dB Buffer Input (- ) 24

- 25 #2 12.75 dB Buffer Input (+)

- 26 #2 12.75 dB Buffer Output (+)

- 27 #2 12.75 dB Buffer Output (- )

- 28 Analog Ground

- 29 No Connection (Can Be Left Floating)

- Full Wave Rectifier Input (+) 30

- Full Wave Rectifier Input (-) 31

- Rectified Signal to Derive Threshold 32

- Rectified Signal for Differentiator 33

- 34 Rectified Signal to S/H; AGC Attack and Decay Is Programmed at This Point

- 35 Zero Crossing Comparator Input (+)

- Zero Crossing Comparator Input (- ) 36

- 37 Minimum Threshold Level Input

- 38 Signal Amplitude Comparator Input

- 39 Internal Voltage Reference

- 40 +12 V Supply (Digital)

- Apply Resistor to Program Time Domain 41 Filter Pulse Width

- Apply Resistor to Program Output Pulse Width 42

- Data Output (Open Collector AD892T) 43 Data Output (+ ECL AD892E)

- Data Output Ground (Emitter of Output Device AD892T) 44

Data Output (- ECL AD892E)

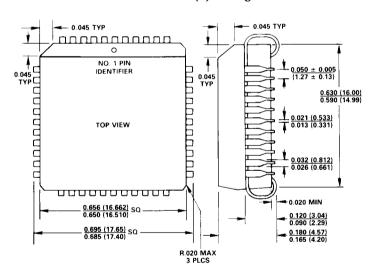

#### PACKAGE OUTLINE DIMENSIONS

Dimensions shown in inches and (mm).

#### 44-Pin PLCC (P) Package

### ORDERING GUIDE

Model No. Package

44-Pin PLCC AD892EIP AD892TIP 44-Pin PLCC

#### **CAUTION**

ESD (electrostatic discharge) sensitive device. The digital control inputs are diode protected; however, permanent damage may occur on unconnected devices subject to high energy electrostatic fields. Unused devices must be stored in conductive foam or shunts. The protective foam should be discharged to the destination socket before devices are inserted.

-12-