#### M/A-COM

# **Surface Mount Frequency Synthesizer CDMA 1720 - 1800 MHz**

#### **Features**

- Integrated VCO/PLL

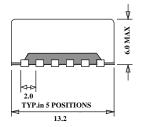

- Miniature SMT Package

- Low Phase Noise

- +5V Operation

## **Description**

The MLS9228-01760 synthesizer design integrates a high performance buffered VCO, PLL circuit and discrete loop filter in a surface mount package. The SMT packaging provides electrical shielding, easy PCB assembly and repeatable performance. The synthesizer is designed for use in PCS CDMA base stations and is optimised for coverage of the PCS band with 50 kHz step size and low phase noise and spurious.

M/A-COM synthesizers are manufactured in an ISO 9001 certified facility, incorporating surface mount assembly and automated electrical testing. This ensures consistent electrical performance and quality over volume production quantities.

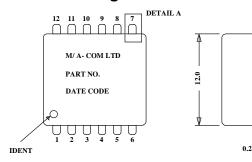

## 12 Lead Package

# Electrical Specifications<sup>1</sup>, $T_A = +25$ °C, $V_{cc} = +5V$ , $\Delta F = 50$ kHz, $F_R = 15$ MHz (unless otherwise stated)

| Parameter                                          | Test Conditions                                                              | Units    | Min.  | Тур. | Max.  |

|----------------------------------------------------|------------------------------------------------------------------------------|----------|-------|------|-------|

| Frequency Range $(F_{OUT})^2$                      | Over T <sub>OP</sub>                                                         | MHz      | 1720  | _    | 1800  |

| RF Output Power (P <sub>OUT</sub> ) <sup>3</sup>   | Over T <sub>OP</sub>                                                         | dBm      | -3.0  | _    | +3.0  |

| Harmonic Output                                    |                                                                              | dBc      |       | -15  | -10   |

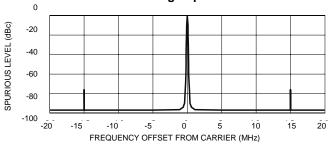

| Spurious Output                                    | Phase comparison frequency $(F_{OUT} \pm \Delta F)$                          | dBc      |       | -75  | -60   |

|                                                    | Reference breakthrough (F <sub>OUT</sub> ±F <sub>R</sub> )                   | dBc      |       | -75  |       |

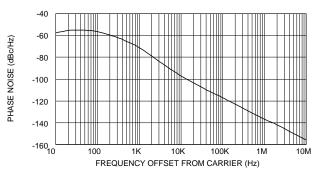

| Phase Noise <sup>4</sup>                           | SSB at 1 kHz offset from carrier                                             | dBc/Hz   |       | -70  | -65   |

|                                                    | SSB at 10 kHz offset from carrier                                            | dBc/Hz   |       | -95  | -90   |

|                                                    | SSB at 100 kHz offset from carrier                                           | dBc/Hz   |       | -115 | -110  |

|                                                    | SSB at 1.25 MHz offset from carrier                                          | dBc/Hz   |       | -136 |       |

| Integrated Phase Noise                             | 300 Hz to 3 kHz bandwidth                                                    | mrad rms |       | 26   |       |

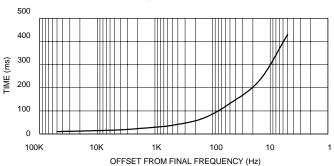

| Frequency Switching Time <sup>5,6</sup>            | Over F <sub>OUT</sub> , measured to within ±500 Hz                           | ms       |       | 35   |       |

| VCO Supply Current (I <sub>CC1</sub> )             |                                                                              | mA       |       | 19   | 21    |

| PLL Supply Current (I <sub>CC2</sub> )             |                                                                              | mA       |       | 12   | 14    |

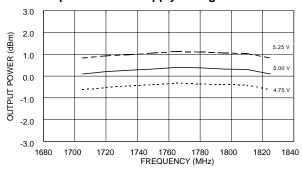

| VCO Supply Voltage (V <sub>CC1</sub> )             | Recommended operating limit                                                  | V        | +4.75 |      | +5.25 |

| PLL Supply Voltage (V <sub>CC2</sub> )             | Recommended operating limit                                                  | V        | +4.75 |      | +5.25 |

| Step Size (ΔF) <sup>7</sup>                        | Recommended operating limit                                                  | kHz      |       | 50   |       |

| Reference Frequency (F <sub>R</sub> ) <sup>8</sup> | 0.5 to 2.0 Vpp sine wave into a.c. coupled CMOS. Recommended operating limit | MHz      | 3     |      | 20    |

- 1. All specification limits are indicated values and apply over  ${\rm F_{OUT}}$  and for  $50\Omega$  load impedance.

- Programming control is 3 wire serial CMOS or TTL levels, in accordance with National Semiconductor LMX 2325.

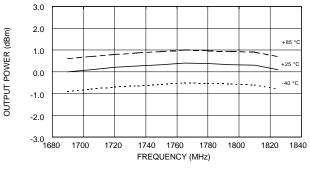

- Output power window includes variation over operating temperature range (T<sub>OP</sub>) -40°C to +85°C and output frequency range (F<sub>OUT</sub>).

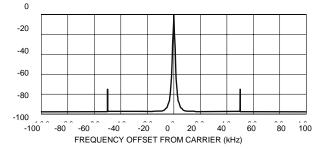

- 4. See plot for typical phase noise at other frequency offsets.

- See plot for typical full band switching time measured to within other offsets from final frequency.

- Integral PLL lock monitor output, TTL high locked, TTL low unlocked.

- 7. Device designed for loop bandwidth of 200 Hz.

- 8. Reference frequency input impedance  $10k\Omega$  min.

V2.00

## **Functional Configuration**

| Lead | Function                   | Lead | Function                     |

|------|----------------------------|------|------------------------------|

| 1    | Ground                     | 7    | Ground                       |

| 2    | Clock Input                | 8    | Reference<br>Frequency Input |

| 3    | V <sub>CC1</sub> (VCO)     | 9    | V <sub>CC2</sub> (PLL)       |

| 4    | PLL Lock<br>Monitor Output | 10   | Data Input                   |

| 5    | RF Output                  | 11   | Strobe/Enable Input          |

| 6    | Ground                     | 12   | Ground                       |

### **Environmental Specifications**

Devices are designed to function over the operating temperature range ( $T_{OP}$ ) of -40°C to +85°C and after exposure to the shock, vibration, thermal shock and moisture conditions typically encountered in base station and other infrastructure environments.

## **Typical Performance**

#### **Phase Noise**

#### **Output Power vs Temperature**

#### Phase Comparator Spurious

## **Absolute Maximum Ratings**<sup>1,2</sup>

| Parameter                                | Absolute Maximum   |  |  |

|------------------------------------------|--------------------|--|--|

| VCO Supply Voltage $(V_{CC1})^3$         | +6.5V              |  |  |

| PLL Supply Voltage $(V_{CC2})^3$         | +6.5V              |  |  |

| Reference Frequency Voltage              | -0.3V to +6.5V     |  |  |

| Data, Clock, Strobe Voltages             | -0.3V to +6.5V     |  |  |

| Storage Temperature (T <sub>STOR</sub> ) | -45°C to +125°C    |  |  |

| Solder Assembly Temperature              | See App Note M2032 |  |  |

- 1. Exceeding these limits may cause permanent damage.

- 2. Static sensitive, observe appropriate handling precautions.

- An external series resistor and bypass capacitor will allow operation at higher supply voltage and will improve power supply decoupling and noise suppression.

## **Ordering Information**

Synthesizers are available in either tape and reel or tube packaging. To order devices in tape and reel requires the suffix TR to be added to the part number, i.e. MLS9228-01760TR. Quantity 500 per 13 inch reel, see Application Note M2030.

#### **Full Band Switching Time**

#### **Output Power vs Supply Voltage**

#### Reference Breakthrough Spurious

V2.00

SPURIOUS LEVEL (dBc)