# LP2996

# DDR ターミネーション・レギュレータ

### 概要

LP2996 は、JEDEC 標準の SSTL-2 仕様に適合する DDR-SDRAM ターミネーションのリニア・レギュレータです。 LP2996 は 負荷変動に対して優れた応答を発揮する高速オペアンプを内蔵しています。出力段は 1.5A の連続電流を供給でき、さらに DDR-SDRAM ターミネーションに求められる最大 3A の変動ピークにも対応していますが、貫通電流は発生しません。 V<sub>SENSE</sub> 端子を介した電圧監視により優れた出力負荷レギュレーションを実現するとともに、チップセットや DDR DIMM に必要な V<sub>REF</sub> 電圧も生成して出力します。

このほか LP2996 は、Suspend-to-RAM (STR) 機能をサポートするアクティブ LOW のシャットダウン ( $\overline{\text{SD}}$ ) 端子を備えています。  $\overline{\text{SD}}$  を LOW にすると、 $V_{\text{TT}}$  出力は TRI-STATE のハイ・インピーダンスとなりますが、 $V_{\text{REF}}$  はアクティブを保ちます。 本モードでは待機時消費電流が小さくなるため、電力節減を図れます。

### 特長

電流ソースおよび電流シンク 低出力電圧オフセット 外付け抵抗不要 リニア・トポロジー Suspend-to-RAM (STR) 機能 少ない外付け部品 サーマル・シャットダウン SO-8、PSOP-8、LLP-16 パッケージで供給

# アプリケーション

DDR-IとDDR-II ターミネーション電圧に対応 SSTL-2とSSTL-3 ターミネーション HSTL ターミネーション

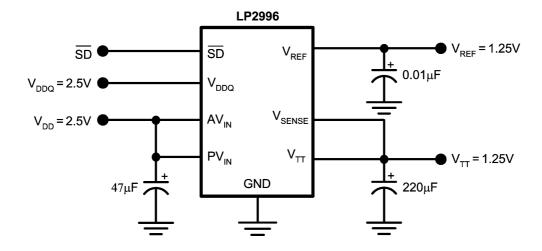

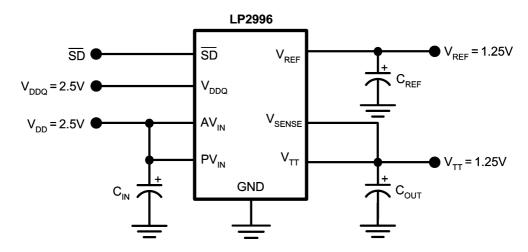

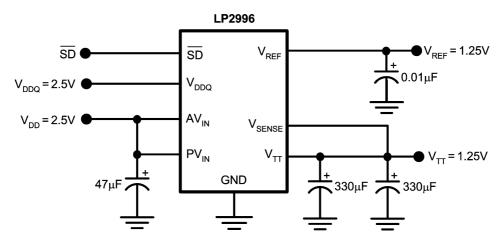

### 代表的なアプリケーション回路

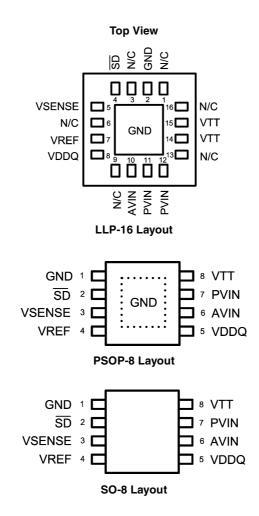

# ピン配置図

# 端子説明

| SO-8 ピンまたは<br>PSOP-8 ピン | LLPピン              | 端子名                      | 機能                                           |

|-------------------------|--------------------|--------------------------|----------------------------------------------|

| 1                       | 2                  | GND                      | グラウンド                                        |

| 2                       | 4                  | $\overline{\mathrm{SD}}$ | シャットダウン                                      |

| 3                       | 5                  | $V_{SENSE}$              | レギュレートされた $V_{TT}$ の電圧フィードバック入力端子            |

| 4                       | 7                  | $V_{ m REF}$             | 内部リファレンス電圧 V <sub>DDQ</sub> /2 のバッファ出力       |

| 5                       | 8                  | $V_{\mathrm{DDQ}}$       | 内部リファレンス電圧 $V_{\mathrm{DDQ}}/2$ を生成するための入力電圧 |

| 6                       | 10                 | AV <sub>IN</sub>         | 内部制御回路電源入力端子                                 |

| 7                       | 11, 12             | PV <sub>IN</sub>         | パワー・オペアンプ出力段専用電源入力端子                         |

| 8                       | 14, 15             | V <sub>TT</sub>          | ターミネーション抵抗に接続するターミネーション電圧出力                  |

| -                       | 1, 3, 6, 9, 13, 16 | NC                       | 内部接続なし                                       |

# 製品情報

| Order Number    | Package Type   | NSC Package Drawing                | Supplied As              |  |

|-----------------|----------------|------------------------------------|--------------------------|--|

| LP2996M SO-8    |                | M08A                               | 95 Units per Rail        |  |

| LP2996MX        | 96MX SO-8 M08A |                                    | 2500 Units Tape and Reel |  |

| LP2996MR        | PSOP-8         | MRA08A 95 Units Tape and Reel      |                          |  |

| LP2996MRX       | PSOP-8         | -8 MRA08A 2500 Units Tape and Reel |                          |  |

| LP2996LQ LLP-16 |                | LQA16A                             | 1000 Units Tape and Reel |  |

| LP2996LQX       | LLP-16         | LQA16A                             | 4500 Units Tape and Reel |  |

## 絶対最大定格 (Note 1)

本データシートには軍用・航空宇宙用の規格は記載されていません。リード温度 (ハンダ付け、10 秒間)260関連する電気的信頼性試験方法の規格を参照下さい。ESD 耐圧 (Note 2)1k

動作定格

GND 基準の  $PV_{IN}$ 、  $AV_{IN}$ 、  $V_{DDQ}$  各電圧  $\phantom{V_{DDQ}}$  - 0.3V ~ + 6V

保存温度範囲 - 65 ~ + 150

接合部温度 接合部温度範囲 (Note 3) 150 0 ~ + 125 SO-8 熱抵抗 ( <sub>JA</sub>) GND 基準の AV<sub>IN</sub> 電圧 2.2V ~ 5.5V 151 /W PSOP-8 熱抵抗 (JA) 43 /W PV<sub>IN</sub> 電源電圧  $0 \sim AV_{IN}$ LLP-16 熱抵抗 ( <sub>IA</sub>) 51 /W SD 入力電圧  $0 \sim AV_{IN}$

電気的特性

標準字体で記載された仕様は  $T_J$  = 25 の場合であり、太字で記載されたリミット値は「動作温度範囲」  $(T_J$  = 0  $\mathbb C$  ~ + 125  $\mathbb C$ ) に適用されます (Note 4)。 特記のない限り、 $AV_{IN}$  =  $PV_{IN}$  = 2.5V、 $V_{DDO}$  = 2.5V です (Note 5)。

| Symbol                             | Parameter                             | Conditions                            | Min   | Тур   | Max   | Units   |

|------------------------------------|---------------------------------------|---------------------------------------|-------|-------|-------|---------|

| V <sub>REF</sub>                   | V <sub>REF</sub> Voltage              | VIN = VDDQ = 2.3V                     | 1.135 | 1.158 | 1.185 |         |

|                                    |                                       | VIN = VDDQ = 2.5V                     | 1.235 | 1.258 | 1.285 | V       |

|                                    |                                       | VIN = VDDQ = 2.7V                     | 1.335 | 1.358 | 1.385 |         |

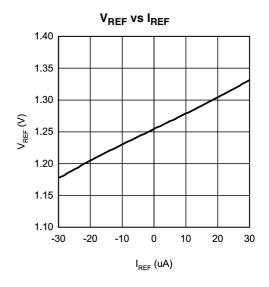

| Z <sub>VREF</sub>                  | V <sub>REF</sub> Output Impedance     | I <sub>REF</sub> = -30 to +30 μA      |       | 2.5   |       | kΩ      |

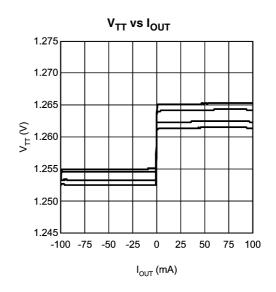

| V <sub>TT</sub>                    | V <sub>TT</sub> Output Voltage        | I <sub>OUT</sub> = 0A                 |       |       |       |         |

|                                    |                                       | VIN = VDDQ = 2.3V                     | 1.125 | 1.159 | 1.190 |         |

|                                    |                                       | VIN = VDDQ = 2.5V                     | 1.225 | 1.259 | 1.290 |         |

|                                    |                                       | VIN = VDDQ = 2.7V                     | 1.325 | 1.359 | 1.390 | V       |

|                                    |                                       | $I_{OUT} = \pm 1.5A \text{ (Note 8)}$ |       |       |       | ] V     |

|                                    |                                       | VIN = VDDQ = 2.3V                     | 1.125 | 1.159 | 1.190 |         |

|                                    |                                       | VIN = VDDQ = 2.5V                     | 1.225 | 1.259 | 1.290 |         |

|                                    |                                       | VIN = VDDQ = 2.7V                     | 1.325 | 1.359 | 1.390 |         |

| Vos <sub>TT</sub> /V <sub>TT</sub> | V <sub>TT</sub> Output Voltage Offset | I <sub>OUT</sub> = 0A                 | -20   | 0     | 20    |         |

|                                    | (V <sub>REF</sub> -V <sub>TT</sub> )  | I <sub>OUT</sub> = -1.5A (Note 8)     | -25   | 0     | 25    | mV      |

|                                    |                                       | $I_{OUT} = +1.5A \text{ (Note 8)}$    | -25   | 0     | 25    |         |

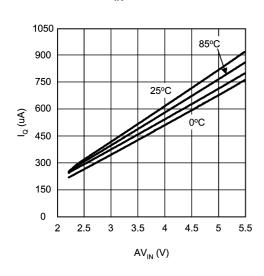

| la                                 | Quiscent Current (Note 6)             | I <sub>OUT</sub> = 0A (Note 4)        |       | 320   | 500   | μA      |

| Z <sub>VDDQ</sub>                  | VDDQ Input Impedance                  |                                       |       | 100   |       | kΩ      |

| I <sub>SD</sub>                    | Quiescent Current in                  | SD = 0V                               |       | 115   | 150   | μΑ      |

|                                    | Shutdown (Note 6)                     |                                       |       |       |       |         |

| $I_{Q\_SD}$                        | Shutdown Leakage                      | SD = 0V                               |       | 2     | 5     | μA      |

|                                    | Current                               |                                       |       |       |       |         |

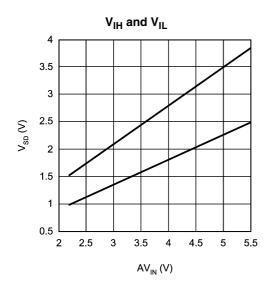

| V <sub>IH</sub>                    | Minimum Shutdown High                 |                                       | 1.9   |       |       | V       |

|                                    | Level                                 |                                       |       |       |       |         |

| V <sub>IL</sub>                    | Minimum Shutdown Low                  |                                       |       |       | 0.8   | V       |

|                                    | Level                                 |                                       |       |       |       |         |

| I <sub>V</sub>                     | V <sub>TT</sub> Leakage Current in    | SD = 0V                               |       | 1     | 10    | μΑ      |

|                                    | Shutdown                              | V <sub>TT</sub> = 1.25V               |       |       |       |         |

| SENSE                              | V <sub>SENSE</sub> Input Current      |                                       |       | 13    |       | nA      |

| T <sub>SD</sub>                    | Thermal Shutdown                      | (Note 7)                              |       | 165   |       | Celcius |

| T <sub>SD</sub> HYS                | Thermal Shutdown                      |                                       |       | 10    |       | Celcius |

|                                    | Hysteresis                            |                                       |       |       |       |         |

# 電気的特性(つづき)

標準字体で記載された仕様は  $T_J$  = 25 の場合であり、太字で記載されたリミナ値は「動作温度範囲」  $(T_J$  = 0  $\mathbb C$  ~ + 125  $\mathbb C$ ) に適用されます (Note 4)。 特記のない限り、  $AV_{IN}$  =  $PV_{IN}$  = 2.5V、 $V_{DDO}$  = 2.5V です (Note 5)。

- Note 1: 「絶対最大定格」とは、デバイスが破壊する可能性のあるリミット値をいいます。「動作定格」とはデバイスが正しく機能する条件を示しますが、特定の性能限界を保証するものでありません。保証された仕様、およびそのテスト条件については「電気的特性」を参照してください。仕様の保証は、表記のテスト条件にのみ適用されます。記載のテスト条件以外でデバイスを動作させると、性能特性が低下することがあります。

- Note 2: 使用したテスト回路は人体モデルに基づき、100pFのコンデンサから直列抵抗 1.5k を通して各端子に放電させます。

- Note 3: 高温では、熱抵抗に基づいてデバイスをディレーティングする必要があります。 SO-8 パッケージでは、ヒート・シンクなしで接合部から周囲への熱抵抗 JA = 151.2 /W でディレーティングしてください。

- Note 4: 25 時の「戸ット値は 100%テストされます。全動作温度範囲における「戸ット値は、統計的品質管理 (SQC) 方式によって決められた補正データを加味して保証されています。 これらの「戸ット値は、ナショナル セミコンダクター社の平均出荷品質レベル (AOQL) の計算に使用されます。

- Note 5:  $V_{\rm IN}$  は、 $V_{\rm IN}$  =  ${\rm AV}_{\rm IN}$  =  ${\rm PV}_{\rm IN}$  として定義されます。

- Note 6: 非動作時電流は  $\mathrm{AV}_{\mathrm{IN}}$  に流れ込む電流として定義されています。

- Note 7: 最大許容消費電力は、最大接合部温度  $T_{J\,(MAX)}$ 、接合部・周囲間熱抵抗  $_{JA}$ 、周囲温度  $T_{A}$  の関数です。 最大許容消費電力を超えると、ダイ温度が極端に上昇してレギュレータはサーマル・シャットダウン状態に入ります。

- Note 8:  $V_{TT}$  負荷レギュレーションは 10 ms の電流パルスを用いて  $V_{TT}$  を測定しテストされています。

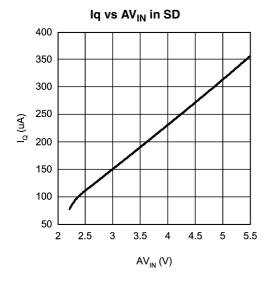

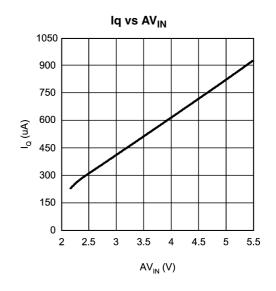

# 代表的な性能特性

# 代表的な性能特性(つづき)

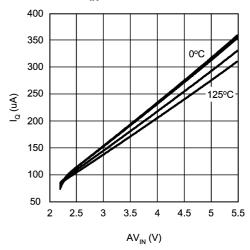

## Iq vs AV<sub>IN</sub> in SD Temperature

Iq vs AV<sub>IN</sub> Temperature

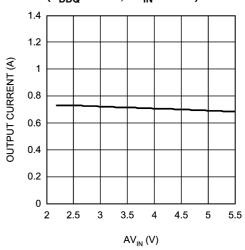

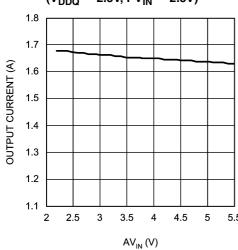

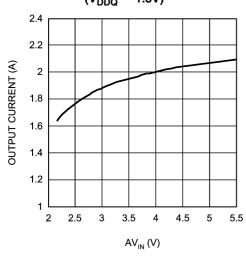

Maximum Sourcing Current vs  $AV_{IN}$ ( $V_{DDQ} = 2.5V, PV_{IN} = 1.8V$ )

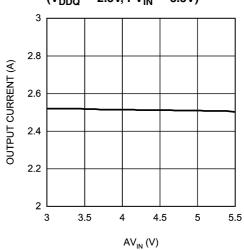

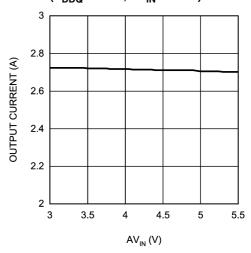

Maximum Sourcing Current vs  $AV_{IN}$ ( $V_{DDQ} = 2.5V$ ,  $PV_{IN} = 2.5V$ )

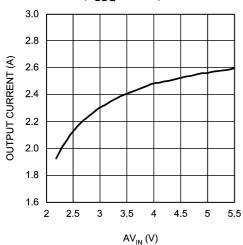

Maximum Sourcing Current vs  $AV_{IN}$ ( $V_{DDQ} = 2.5V, PV_{IN} = 3.3V$ )

# 代表的な性能特性(つづき)

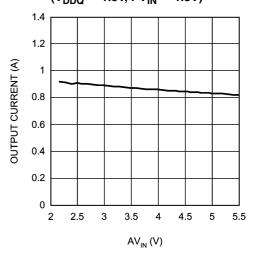

# Maximum Sourcing Current vs $AV_{IN}$ ( $V_{DDQ} = 1.8V, PV_{IN} = 3.3V$ )

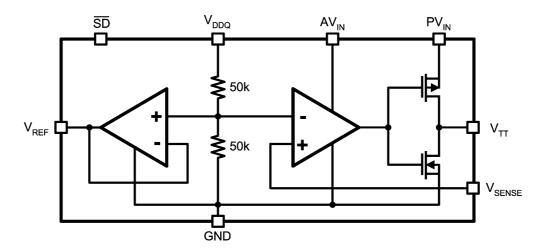

### ブロック図

### 説明

LP2996 は、JEDEC 標準の SSTL-2 仕様に適合する DDR-SDRAM パス・ターミネーションのリニア・レギュレータです。 V<sub>TT</sub> 出力には V<sub>DDQ</sub>/2 に等しいレギュレート電圧が得られ、電流はシンクとソースの両方に対応しています。 出力段は優れた負荷レギュレーションを維持するように設計されており、 貫通電流の発生が防止されています。 また、LP2996 は 2 種類の異なる電源レール (電圧)での動作に対応しており、パワー出力段とアナログ回路を分離できます。 電源を分割すると、内部消費電力の低減を図れます。また LP2996 は、次世代の DDR-SDRAM メモリ (DDR II) に対応したターミネーション・ソリューションを構成可能です。 また、SSTL-3 や HSTL といった、異なるロジック I/F 用のターミネーション電圧も生成できます。

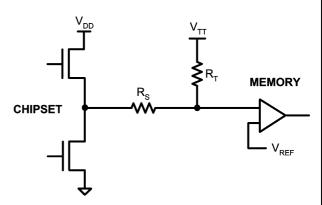

シリーズ・スタブ・ターミネーテッド・ロジック (SSTL) は、メモリバスのデータ転送時の信号品質を改善するために開発されました。このターミネーション方式は、高い周波数で DDR-SDRAM のデータ転送を行う際に、信号反射によるデータ・エラーを防ぐためには不可欠と言えます。 最も一般的なターミネーション回路形式は、チップセットとメモリの間に 1 つの直列抵抗  $R_S$  を設け、さらにターミネーション抵抗  $R_T$  を 1 つ用いる、Class II シグナル・パラレル・ターミネーションです。 回路の例を Figure 1 に示します。

FIGURE 1. SSTL-Termination Scheme

#### 端子説明

#### AV<sub>IN</sub> および PV<sub>IN</sub>

${

m AV_{IN}}$  および  ${

m PV_{IN}}$  は  ${

m LP2996}$  の電源端子です。  ${

m AV_{IN}}$  は、全内 部回路の電源として用いられます。 $PV_{IN}$ は、 $V_{TT}$ 生成用の出力 段専用電源です。アプリケーションによっては両電源端子に異な る電源を与えて動作させるのも可能です。 V<sub>TT</sub> に近い電圧の場 合 RSDON によって出力が制限されますが、 $PV_{IN}$  に高電圧を与 えれば最大連続出力電流を増加させることができます。ただし、 PV<sub>IN</sub> に高電圧を与えると内部電力損失が増え、設計が熱的な 制約を受ける問題点が生じます。 SSTL-2 アプリケーションでは、  $AV_{IN}$ と $PV_{IN}$ をともに 2.5V レールに接続するのが最も妥当です。 短絡により2 つの端子を個別にバイパスする必要はありません。 入力電圧の選択に対する唯一の制約として、 $PV_{IN}$  は  $AV_{IN}$  以下 でなければなりません。過度の内部電力消費による熱リミットへの 到達を防ぐため、 $\mathrm{PV}_{\mathrm{IN}}$  は 3.3V 以下の電圧レールに接続すること を推奨します。接合部温度がサーマル・シャットダウン温度超える と、デバイスはマニュアルでのシャットダウン時と同じ状態に入り、  $V_{RFF}$  はそのまま維持されますが、 $V_{TT}$  は TRI-STATE になります。

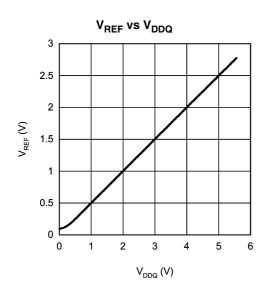

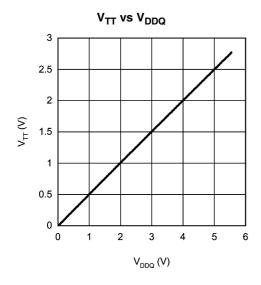

### $V_{DDQ}$

$V_{DDQ}$  は入力で、 $V_{TT}$  のレギュレートに必要な内部リファレンス電圧の生成に使われます。リファレンス電圧は 2 個の 50k 内蔵抵抗の分圧によって生成されます。これによって、 $V_{TT}$  の  $V_{DDQ}$ /2 に対する正確な追従が得られます。リモート・センスとなるように  $V_{DDQ}$  端子に配線してください。 $AV_{IN}$  または  $PV_{IN}$  の代わいに、DIMM 点の 2.5V を  $V_{DDQ}$  に直接接続すればよいでしょう。こうすると内部リファレンス電圧は、電源配線での電圧降下の影響を受けずに、DDRメモリ部の電源電圧に正確に追従します。SSTL-2 アプリケーションで  $V_{DDQ}$  は 2.5V なので、9ーミネーション電圧  $V_{TT}$  として 1.25V が生成されます。 (温度に対する  $V_{TT}$  の変化範囲の正確な値は「電気的特性」の表を参照してください)。

### VSENSE

本センス端子の目的は、遠端の負荷レギュレーションの改善にあります。多くのマザーボードでは、 $V_{TT}$  は長い配線を通ってターミネーション抵抗に接続されます。このとき LP2996 の出力点で電圧のセンスを行うと、長い配線によって起こる大きな電圧降下により、バス端のターミネーション電圧はバスの他点は) たばくなってしまう問題が生じます。そこでバスの中点付近の電圧を  $V_{SENSE}$  端子に与え、バス遠端で電圧が低下する問題を改善するようにしてください。この方法によりバス全体の電圧が良好に保たれます。遠端での負荷レギュレーションを行わない場合は、 $V_{SENSE}$  端子には  $V_{TT}$  を与えなければな) ません。  $V_{SENSE}$  には  $V_{TT}$  を与えなければな) ません。  $V_{SENSE}$  信号の配線をメモリに近接して実装する際は注意が必要です。  $V_{SENSE}$  配線にノイズが重畳すると $V_{TT}$ の正確なレギュレーションに影響を与える場合があります。  $V_{SENSE}$  端子の近くに 0.1 µF セラミック・コンデンサを設けると、高周波数信号がフィルタされるので、誤動作を防げます。

### シャットダウン

LP2996 は、 $V_{TT}$  出力を TRI-STATE にするアクティブ LOW のシャットダウン端子を備えています。シャットダウン中は  $V_{TT}$  に  $AV_{IN}$  を超える電圧を与えてはなりません。シャットダウン端子を LOW にした場合、LP2996 の待機時消費電流は下がりますが、 $V_{DDQ}$  のインピーダンスは内部リファレンス電圧の生成のために100k で一定です。 そのため、シャットダウン時の総電力損失の計算では、両方の電流 (待機時消費電流と $V_{DDQ}$ を流れる電流)を考慮する必要があります。 詳細は「放熱」の項を参照してください。シャットダウン端子は内部でプルアップされているため、デバイスをターンオンする場合はシャットダウン端子を  $AV_{IN}$  に接続するか開放にします。

#### VREF

$V_{REF}$  は内部リファレンス電圧  $V_{DDQ}/2$  のバッファ出力です。本出力は、ノースブリッジ・チップセットとメモリに対するリファレンス電圧として使用します。通常それらの入力のインピーダンスは高いので、 $V_{REF}$  端子を流れる電流はわずかです。 ノイズ対策として端子近くにバイパス・コンデンサを設けると、レギュレーション性能が改善されます。 推奨品は  $0.1\,\mu F$  から  $0.01\,\mu F$  のセラミック・コンデンサです。  $V_{REF}$  出力は、Suspend-to-RAM 機能をサポートするため、シャットダウン時およびサーマル・シャットダウン時もアクティブ状態を維持します。

#### $V_{TT}$

$V_{\rm TT}$ はバスのターミネーション抵抗に与えられるレギュレート電圧出 力です。  $V_{\mathrm{DDO}}/2$  電圧に高い精度で追従し、併せて電流ソース と電流シンクの能力を備えています。LP2996は、高速応答によっ て最大±3Aまでのピーク電流変動に対応できるように設計されて います。最大連続電流は $\,{

m V_{IN}}\,$ の関数で、「代表的な性能特性」 に記載されています。最大連続電流定格を超える変動が長時間 にわたり見込まれるのであれば、出力コンデンサ容量を十分大き くして過度の電圧低下の発生を防いでください。 LP2996 は出力 電流の大きな変動にも耐え得るように設計されていますが、すべ ての条件のもとで、そのような状況に長時間対応するのは困難で す。その理由は、小型の標準パッケージを採用しているため、過 大な内部電力損失によって生じる熱を逃がせないためです。 長 時間にわたり大電流が求められる場合は、最大接合部温度を超 えないように注意が必要です。 熱に応じて、使用定格を適切に 下げるようにしてください(「放熱」を参照)。接合部温度がサー マル・シャットダウン・ポイントを超えると、ヒシテリシスを持つトリッ プ・ポイント温度を下回るまで、V<sub>TT</sub> は TRI-STATE となります。

#### 部品の選択

#### 入力コンデンサ

LP2996 は、入力安定化を目的とする入力コンデンサは必要ではありません。ただし大きな負荷変動時に入力電圧の低下を防ぐために、入力コンデンサの使用を推奨します。 入力コンデンサは、可能な限り  $PV_{IN}$  の近くに配置します。 アプリケーションの要件によって推奨条件が異なります。 アルミ電解コンデンサを用いた場合、推奨容量は  $50\mu F$  です。 セラミック・コンデンサを用いる場合は、容量は  $10\mu F$  前後とし、誘電体の温度特性が X5R 以上のコンデンサが理想的といえます。 なお、LP2996 が 2.5V DC-DCコンバータの出力コンデンサの近くにレイアウトされている場合は、入力コンデンサを省略しても構いません。 2 系統の電源レール  $(AV_{IN}$  と  $PV_{IN}$ )を使用する場合、 $PV_{IN}$  端子の可能な限り近くに47 $\mu F$  コンデンサを配置してください。また、デバイスに過度のノイズがカップリングしないは入  $AV_{IN}$  端子に  $0.1\mu F$  セラミック・コンデンサを追加しても構いません。

### 部品の選択(つづき)

#### 出力コンデンサ

LP2996 は、出力コンデンサの容量および ESR ( 等価直列抵抗 ) に依存しないよう設計されています。 そのため柔軟にコンデンサを選択できます。 出力コンデンサは、アプリケーションと負荷変動に対するV<sub>TT</sub>の応答要求に基づいて決めてください。DDR-SDRAMを用いた SSTL アプリケーションでは、100µF 以上の低 ESR コンデンサを一般的に推奨します。 このうち ESR は、見込まれる最大電流スパイクと、許容される出力電圧低下から決定してください。 入手可能なコンデンサ類のうち、代表的な品種について次に説明します。

AL - アルミ電解コンデンサは 120Hz におけるインピーダンスのみを規定している点に注意が必要で、これは高い周波数領域では特性が劣ることを示しています。LP2996 回路にアルミ電解コンデンサを適用できる条件は、20kHz ~ 100kHz の高い周波数領域でもインピーダンスが規定されている場合に限られます。アルミ電解コンデンサを複数個並列に接続すると総ESRを下げられます。ただし問題点はESR が温度により変化することで、低温になるとESR が急激に増大します。

セラミック・セラミック・コンデンサは、一般的に容量は 10μF ~ 100μF と大きくありませんが、ESR が極めて小さい (通常 10m以下)ため、優れたノイズ・バイパス特性を備えています。しかし使用している誘電体の種類よっては、電圧と温度に対して充分な特性を備えていない 他のも存在します。一般的に容量が小さいといった理由により、セラミック・コンデンサはアルミ電解コンデンサなどに並列接続しての使用を推奨します。また使用するすべてのセラミック・コンデンサには、誘電体の温度特性が X5R 以上の品種を推奨します。

化合物 - OS-CON (有機半導体)や SP (機能性高分子)のような化合物を用いたコンデンサが、数社からリリースされています。これらのコンデンサは低 ESR を維持しながら大きな容量を実現しています。 他のコンデンサに比べてコストは高くなりますが、実装サイズと性能が重要な場合に最適なソリューションといえます。

# 放熱

LP2996 はリニア・レギュレータなので、熱の原因となる内部損失が  $V_{TT}$  電流によって発生します。デバイスを損壊から守るには最大許容接合部温度を超えてはならないので、見込まれる最大周囲温度と消費電力にもとづき、デバイスを定格以下で動作させるよう注意を払う必要があります。最大許容内部温度上昇  $(T_{Rmax})$  は、アプリケーションで与えられる最大周囲温度  $(T_{Amax})$  と、最大許容接合部温度  $(T_{Imax})$  から求められます。

$$T_{Rmax} = T_{Jmax} - T_{Amax}$$

この式から、デバイスの最大消費電力  $(P_{Dmax})$  は次式で示されます。

$$P_{Dmax} = T_{Rmax} / J_A$$

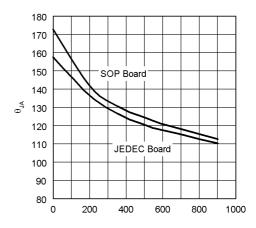

LP2996の  $_{\rm JA}$  は、使用しているパッケージ、プリント基板の銅箔 厚み、ピアの数、エアフローで決まります。たとえば  $_{\rm SO-8}$  パッケージを、標準的な  $_{\rm 203}$  x  $_{\rm 102mm}$ 、銅箔厚み  $_{\rm 35}$   $_{\rm µm}$  の基板に実装し、エアフローなしの室温で  $_{\rm 0.5}$  W を消費させた場合の  $_{\rm JA}$  は、 $_{\rm 163}$  /W です。また JEDEC スタンダードの  $_{\rm 76}$  x  $_{\rm 102mm}$ 、 $_{\rm 70}$   $_{\rm µm}$  厚銅箔の基板を用いると、  $_{\rm JA}$  は  $_{\rm 151.2}$  /W に低下します。 Figure 2 に上記 2 つの基板における、エアフローに対する  $_{\rm JA}$  の変化を示します。

AIRFLOW (Linear Feet per Minute)

FIGURE 2. JA vs Airflow (SO-8)

デバイスの実装とグラウンド内層に熱を放出するためにビアをうまく使用すると、さらなる改善が図れます。基板表面層に幅広かつ銅箔厚を厚くした配線を適用しても同じ効果が得られます。基板のレイアウト設計を注意深く行えば、Figure 2 に示される公称値より先低い JA になります。

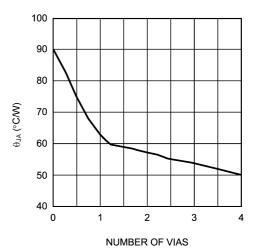

LLP パッケージの出力電流を最大限に引き出す上で、基板レイアウトも極めて重要です。 DAP 直下に単純にビアを打つだけでも  $_{

m JA}$  を大幅に低下できます。 Figure 3 は、 $18\,\mu{

m m}/35\,\mu{

m m}/35\,\mu{

m m}/18\,\mu{

m m}$  の銅箔で構成される 4 層 JEDEC 基板に実装した場合の LLP パッケージの熱特性です。 ビアを間隔 1.27mm にて最大 4 つに増やしたとき、50.41 /W の  $_{

m JA}$  が得られています。このグラフにおけるビアのメッキ厚は  $36\,\mu{

m m}$  です。

FIGURE 3. LLP-16 JA vs # of Vias (4 Layer JEDEC Board))

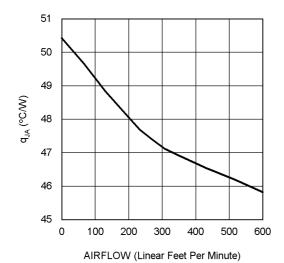

パッケージに定常的なエアフローを与えても $_{

m JA}$ は低下します。上記条件で  $2\times 2$  のビア配列を用いた場合、エアフローによる $_{

m JA}$  の低下を Figure 4 に示します。

### 放熱(つづき)

FIGURE 4. JA vs Airflow Speed (JEDEC Board with 4 Vias)

$_{

m JA}$  の最適化を行い、あわせて周囲温度が低い基板領域に LP2996 を配置すれば、デバイスをより大きな消費電力で使用可能になります。 内部消費電力は主に、シンクかソースに依らない  $V_{

m TT}$  の出力電流、 $AV_{

m IN}$  の待機時消費電流、 $V_{

m DDQ}$  の待機時消費電流といった 3 種類の損失の合計として求められます。 シャッ

トダウンが LOW ではないアクティブ状態では、内部消費電力は次の式で算出されます。

$$\begin{split} P_{\rm D} &= P_{\rm AVIN} + P_{\rm VDDQ} + P_{\rm VTT} \\ P_{\rm AVIN} &= I_{\rm AVIN} \times V_{\rm AVIN} \\ P_{\rm VDDO} &= V_{\rm VDDO} \times I_{\rm VDDO} = (V_{\rm VDDO})^2 \div R_{\rm VDDO} \end{split}$$

$V_{TT}$  の最大消費電力を求める場合、電流がシンク時とソース時の両状態で  $V_{TT}$  を検討する必要があります。 ただし  $V_{TT}$  はシンクとソースの両方の状態を同時に採り得ないため、合計ではどちらか 1 つの値のみを加算します。

$$P_{VTT}$$

=  $V_{VTT}$  ×  $I_{LOAD}$ (シンク時)

$P_{VTT}$  = ( $V_{PVIN}$  -  $V_{VTT}$ ) ×  $I_{LOAD}$ (ソース時)

シャットダウン・ステートにある LP2996 の消費電力も計算可能です。 $V_{TT}$  出力は TRI-STATE となりシンク電流もソース電流も流れないため、電力計算において該当項は取り除いて考えます (漏れ電流は無視できる)。シャットダウン中は、低減されてはいるものの  $AV_{IN}$  の待機時消費電流と、 $V_{DDQ}$  端子に現れる一定のインピーダンスにより、若干の損失が生じます。

$$\begin{split} P_{\rm D} &= P_{\rm AVIN} + P_{\rm VDDQ} \\ P_{\rm AVIN} &= I_{\rm AVIN} \times V_{\rm AVIN} \\ P_{\rm VDDQ} &= V_{\rm VDDQ} \times I_{\rm VDDQ} = (V_{\rm VDDQ})^2 \div R_{\rm VDDQ} \\ R_{\rm VDDO} &= 50 \text{k} + 50 \text{k} \end{split}$$

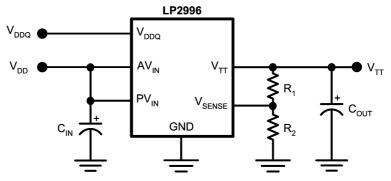

### 代表的なアプリケーション回路

LP2996 が構成上とり得るオプションを示すために、さまざまなアプリケーション回路を Figure  $5\sim14$  に示します。 個々の回路の性能は、このデータシートの前半にある「代表的な性能特性」のグラフに、 $AV_{IN}$  と  $PV_{IN}$  の電圧によって最大出力電流がどのように影響を受けるかが示されています。

#### SSTL-2 アプリケーション

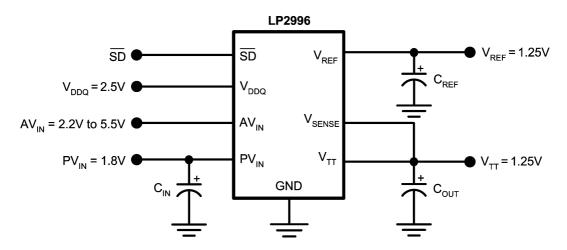

SSTL-2 ターミネーション方式の実装をするアプリケーションでは、すべての入力レールを 2.5V レールに接続することを推奨します。 消費電力、部品点数、部品選択のトレードオフで最適となるからです。 回路例を Figure 5 に示します。

FIGURE 5. Recommended SSTL-2 Implementation

消費電力または効率が設計上の大きな課題となっている場合は、LP2996を分割電源で動作させます。 出力段  $(PV_{IN})$  は 1.8V 程度の低電圧で動作させ、アナログ回路  $(AV_{IN})$  には 2.5V、3.3V、または 5V といった高電圧を与えます。 このようにすると、 $V_{TT}$  から電流が供給されたときでも内部消費電力を小さくできます。この

回路の問題点は低電圧動作により最大連続電流が小さくなることですが、SSTL-2 アプリケーションのあらゆるマザーボードでは充分です。 出力コンデンサを大きくすると、大きな負荷電流遷移に対応できる時間を長くできます。

FIGURE 6. Lower Power Dissipation SSTL-2 Implementation

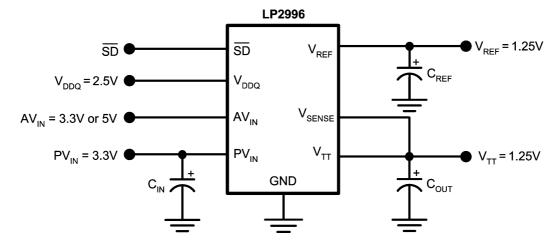

SSTL-2 アプリケーションの第 3 のオプションは、1.8V 電源レールがなく、かつ 2.5V を使用するのが望ましくない状態で、LP2996 の  $PV_{\rm IN}$ を 3.3V レールに接続した場合です。  $AV_{\rm IN}$  は  $PV_{\rm IN}$  より低くはできないため、この場合  $AV_{\rm IN}$  は、3.3V または 5V レールに限られます。この構成では放熱が大きくなる反面、最大連続出

力電流が得られます。LP2996が接合部温度を最大定格を超えてしまう大電流レベルの状況にならないように注意が必要です。このようなリスクがあるため、出力段に公称3.3V より注高い電圧を与えることは推奨されません。

FIGURE 7. SSTL-2 Implementation with higher voltage rails

#### DDR-II アプリケーション

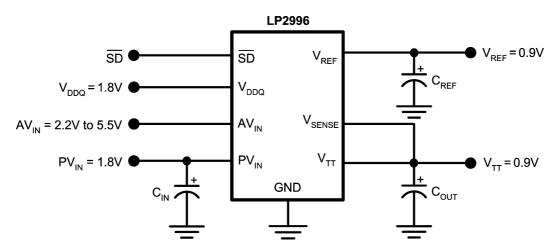

$V_{\mathrm{DDQ}}$ 端子と内部抵抗分圧回路は他の回路と切り離されていますので、LP2996 を DDR-II メモリ・アプリケーションに適用することも可能です。 Figure 8、9 は推奨回路の実装例です。 出力特性

は「代表的な性能特性」のグラフに示されています。Figure 8 は DDR-II アプリケーションの推奨回路構成です。 出力段を 1.8V レールに接続し、 $AV_{\rm IN}$ 端子を3.3Vまたは5Vレールに接続します。

FIGURE 8. Recommended DDR-II Termination

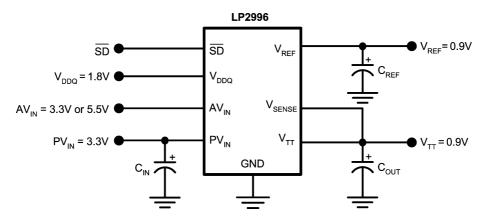

1.8V レールを出力段に使用できない場合は、3.3V レールを接続する案も考えられます。  $V_{TT}$  出力電圧が低いため、熱損失の増大によって最大接合部温度を超えないように注意が必要です。そ

のため、 $PV_{IN}$  に公称 3.3V 以上の電圧レールを与えるのは推奨されません。この構成の利点は、ソースとシンクで、最大連続電流を大きくできることです。

FIGURE 9. DDR-II Termination with higher voltage rails

# レベル・シフト

SSTL-3 など、SSTL-2 以外のスタンダードに適用するために、 $V_{\rm DDQ}$  に対して 0.5 倍以外の係数で出力電圧のレギュレーションを行いたい場合があります。係数を変えて任意の電圧を得るにはいくつかの方法があります。その 1 つは、 $V_{\rm TT}$  から  $V_{\rm SENSE}$  端子に帰還抵抗を追加して、出力のレベル・シフトを行う方法です。

この方法を用いた回路を Figure 10、11 に示します。 Figure 10 は、2 個の追加抵抗を使って、内部リファレンス電圧  $V_{DDQ}/2$  より も高い電圧にレベル・シフトする回路です。  $V_{TT}$  の正確な電圧は次の式から求められます。

$$V_{TT} = V_{DDQ}/2 (1 + R1/R2)$$

FIGURE 10. Increasing V<sub>TT</sub> by Level Shifting

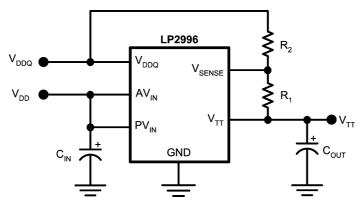

逆に、抵抗 R2 を  $V_{SENSE}$  と  $V_{DDQ}$  の間に置けば、 $V_{TT}$  出力を内部リファレンス電圧  $V_{DDQ}/2$  お先低くできます。 $V_{TT}$  と抵抗の関係は次の式で表されます。

$$V_{TT} = V_{DDQ}/2 (1 - R1/R2)$$

FIGURE 11. Decreasing  $V_{TT}$  by Level Shifting

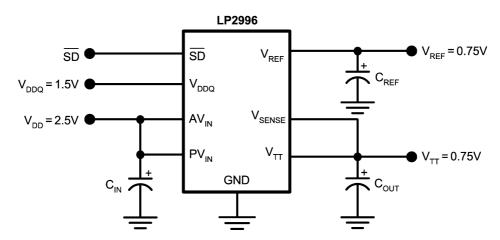

#### HSTL アプリケーション

LP2996 は、 $V_{\rm DDQ}$  に  $1.5{\rm V}$  レールを接続するだけで、簡単に HSTL アプリケーションに適用できます。ターミネーション抵抗に与えられる  $V_{\rm TT}$  と  $V_{\rm REF}$  電圧はおよそ  $0.75{\rm V}$  になけます。 最適な性能を得るために  $AV_{\rm IN}$ と  $PV_{\rm IN}$  は  $2.5{\rm V}$  レールに接続してください。

FIGURE 12. HSTL Application

#### QDR アプリケーション

クワッド・データ・レート (QDR) アプリケーションは高いメモリ性能を得るために複数のチャネルを使用します。そのためバス信号線数が増え、ターミネーションに必要な電流レベルも大きくなります。そこでターミネーションでは、複数チャネルの各チャネルごとに個別の LP2996 を使用することを推奨します。基板レイアウトを単純化でき、各レギュレータの内部消費電力も抑えられます。 各レギュレータから出力される個々の VREF 信号を各 DIMM バンクに与えます。チップセット用のリファレンス電圧は、局所的に抵抗分圧を

行うか、LP2996 のうちの 1 つから与えます。  $V_{REF}$  は  $V_{TT}$  に追従することが見込まれ、またデバイス間のばらつきは小さいため、各 LP2996 のリファレンス電圧の差はわずかです。

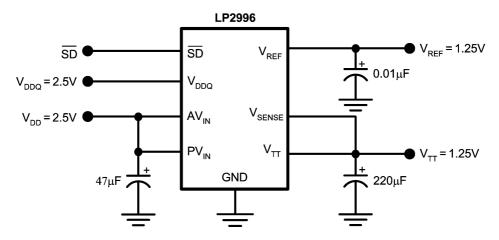

#### 出力コンデンサの選択

LP2996をSSTL-2 I/O 信号のターミネーション用に使用したアプリケーションでは、Figure 13 に示す代表的アプリケーション回路を適用可能です。

FIGURE 13. Typical SSTL-2 Application Circuit

この回路は、最小の基板面積と最小の部品点数でターミネーション回路を実現しています。選択すべきコンデンサの容量は、ターミネーションする信号線数と最大負荷電流に依存して異なりますが、V<sub>TT</sub>が長い配線で分配されているマザーボードやアプリケーションでは、複数のバルク・コンデンサを使用し、さらに高周波デ

カップリング・コンデンサを追加することが望まれます。次の Figure 14 に、2 個のバルク出力コンデンサを、最適な位置である V<sub>TT</sub> 層の両端に配置した回路例を示します。 ESR が小さくかつコストが低い大容量アルミ電解コンデンサを使用しています。

FIGURE 14. Typical SSTL-2 Application Circuit for Motherboards

一般の PC アプリケーションでは、モジュールに実装された DDR-SDRAM DIMM によって長いインターコネクトが生じるため、多数のデカップリングが必要です。そのため、通常 1000μF の容量範囲のアルミ電解コンデンサをバルク・コンデンサとして使用します。

#### PCB 設計に関する考慮

- 1. パワー・レールの入力コンデンサは、可能な限 $\mathfrak{I}$  PV $_{

m IN}$  端子の近くに配置してください。

- V<sub>SENSE</sub> 端子には、V<sub>TT</sub>ターミネーションされるバスのレギュレーションが必要な点に接続してください。マザーボード・アプリケーションではターミネーション・バスの中点が理想的です。

- 3. V<sub>DDQ</sub> 入力は、DIMM またはチップセットの V<sub>DDQ</sub> 電源に対してリモート・センスとなるように接続します。 内部リファレンス電圧を最も精度高く生成できるようになります。

- 4. 熱特性を改善するには、パッケージからの放熱量を増やすために表面層の銅箔を大きくしてください。 グラウンド配線と内部グラウンド・プレーンを接続する多数のビアも放熱を助けます。 さらに、製造基準として許容されるのであれば、ビアはパッケージ下部にも配置してください。

- $5.~V_{SENSE}$  信号の配線設計では、スイッチングする I/O 信号から ノイズを拾わないように注意が必要です。  $V_{SENSE}$  端子の近くに  $0.1\,\mu\text{F}$  セラミック・コンデンサを置くと、好ましくない高周波信号をフィルタリングできます。  $V_{SENSE}$  配線が長い場合、とくに検討を要します。

- $6.\,V_{REF}$ にはレギュレーション性能の改善のため、 $0.1\,\mu F\sim0.01\,\mu F$  のセラミック・コンデンサを接続してノイズをバイパスしてください。 コンデンサは  $V_{REF}$  端子の可能な限り近くに配置してください。

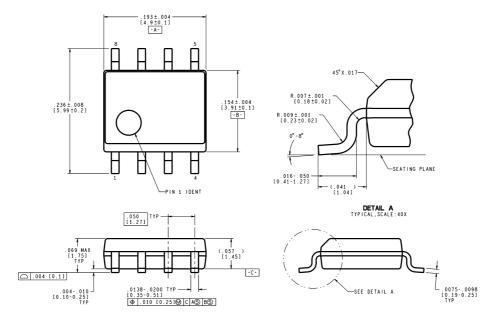

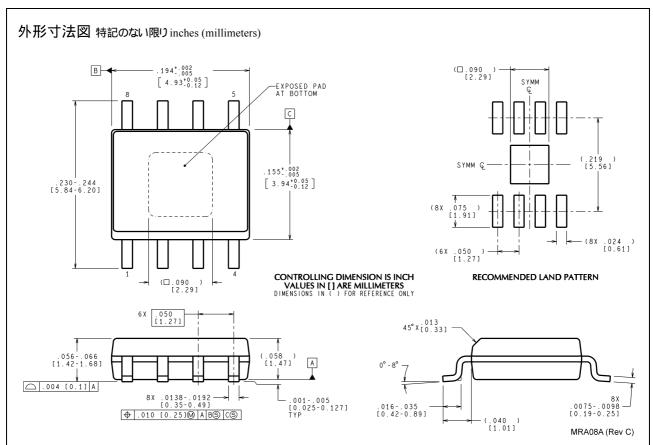

# 外形寸法図 特記のない限り inches (millimeters)

#### CONTROLLING DIMENSION IS INCI-VALUES IN 1 I ARE MILLIMETERS

M08A (Rev J)

### 8-Lead Small Outline Package (M8) NS Package Number M08A

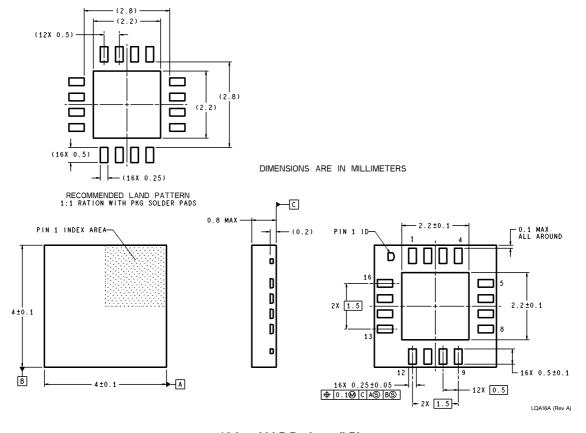

16-Lead LLP Package (LD) NS Package Number LQA16A 当付け millimaters

単位は millimeters

#### 8-Lead PSOP Package (PSOP-8) NS Package Number MRA08A

### 生命維持装置への使用について

弊社の製品はナショナル セミコンダクター社の書面による許可なくしては、生命維持用の装置またはシステム内の重要な部品として使用することはできません。

- 1. 生命維持用の装置またはシステムとは (a) 体内に外科的に使用されることを意図されたもの、または (b) 生命を維持あるいは支持するものをいい、ラベルにより表示される使用法に従って適切に使用された場合に、これの不具合が使用者に身体的障害を与えると予想されるものをいいます。

- 2. 重要な部品とは、生命維持にかかわる装置またはシステム内のすべての部品をいい、これの不具合が生命維持用の装置またはシステムの不具合の原因となりそれらの安全性や機能に影響を及ぼすことが予想されるものをいいます。

# ナショナル セミコンダクター ジャパン株式会社

本社 / 〒 135-0042 東京都江東区木場 2-17-16

TEL.(03)5639-7300

技術資料(日本語/英語)はホームページより入手可能です。

その他のお問い合わせはフリーダイヤルをご利用下さい。

www.national.com/jpn/

0120-666-116