# 1.1GHz-band PLL IC for Mobile Communications

# **Descriptions**

The CXA1786N is a frequency synthesizer PLL IC developed for use in mobile communication systems. This IC has low current consumption, small package and is suitable for portable sets of cellular telephone and others.

#### **Features**

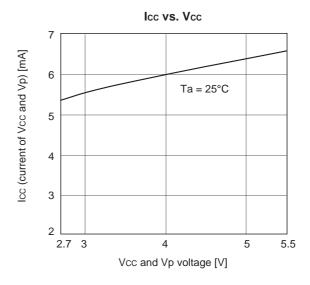

- Low current consumption

lcc = 6.0mA (typ.)

0.3mA (typ.) in power saving mode

- Maximum operating frequency 1.1GHz guaranteed

- Operating supply voltage range 2.7 to 5.5V

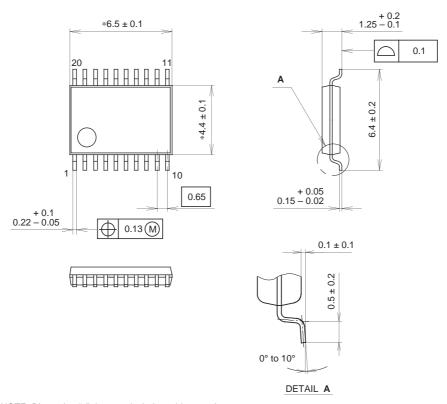

- Ultra small 20-pin SSOP package

- Two types of phase comparator output:

For external charge pump φR φP

Two internal charge pumps Do1 Do2

# **Applications**

1.1GHz-band mobile communication equipment such as cellular telephones

#### Structure

Bipolar silicon monolithic IC

# **Absolute Maximum Ratings**

| Supply voltage          | Vcc                 | 7                                                                                     | V                                                                                                      |

|-------------------------|---------------------|---------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| Operating temperature   | Topr                | -35 to +85                                                                            | °C                                                                                                     |

| Storage temperature     | Tstg                | -65 to +150                                                                           | °C                                                                                                     |

| Allowable power dissipa | ation               |                                                                                       |                                                                                                        |

|                         | Pp                  | 300                                                                                   | mW                                                                                                     |

|                         | Storage temperature | Operating temperature Topr<br>Storage temperature Tstg<br>Allowable power dissipation | Operating temperature Topr -35 to +85 Storage temperature Tstg -65 to +150 Allowable power dissipation |

## **Operating Condition**

Supply voltage Vcc 2.7 to 5.5

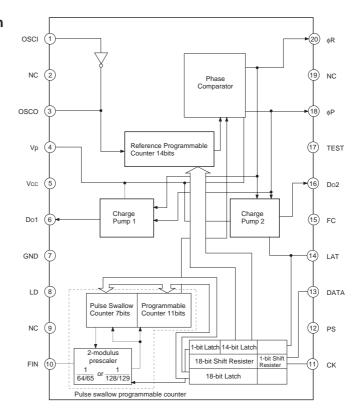

# **Block Diagram and Pin Configuration**

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

# **Pin Description**

| Pin<br>No. | Symbol | Typical pin voltage (DC) | Equivalent circuit         | Description                                                                                                                                                                                     |

|------------|--------|--------------------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | OSCI   | 2.2V                     | Vcc<br>1                   | Reference frequency signal input.                                                                                                                                                               |

| 10         | FIN    |                          | 10 GND                     | VCO signal input.                                                                                                                                                                               |

| 2          | NO     |                          |                            |                                                                                                                                                                                                 |

| 9          | NC     | _                        | _                          | No connected.                                                                                                                                                                                   |

| 3          | osco   | High: 2.2V<br>Low: 2.0V  | Vcc<br>3<br>500Ω<br>GND    | Reference frequency signal output. Oscillator is formed by connecting the crystal resonator between this pin and the OSCI pin; the oscillator signal is used as the reference frequency signal. |

| 4          | VP     | 3V                       |                            | Power supply for the charge pump outputs (Do1, Do2) and phase comparator outputs ( $\phi$ R, $\phi$ P).                                                                                         |

| 5          | Vcc    | 3V                       | _                          | Power supply.                                                                                                                                                                                   |

| 6          | Do1    |                          | ─ <del>•</del> Vp          | Charge pump 1 output.                                                                                                                                                                           |

| 16         | Do2    | _                        | 6<br>16<br>GND             | Charge pump 2 output. Outputs only when the LAT pin is High; in high impedance when the LAT pin is Low.                                                                                         |

| 7          | GND    | _                        |                            | Ground.                                                                                                                                                                                         |

| 8          | LD     |                          | V <sub>p</sub> (LD is Vcc) | Lock detection signal output.                                                                                                                                                                   |

| 18         | φР     | High: 2.2V<br>Low: 0.1V  | 8 18                       | Phase comparator output. Used for the external                                                                                                                                                  |

| 20         | φR     |                          | ② T GND                    | charge pump.                                                                                                                                                                                    |

| 11         | СК     |                          | Vcc                        | Clock input.                                                                                                                                                                                    |

| 13         | DATA   | Open Low                 | (1)                        | Data input.                                                                                                                                                                                     |

| 14         | LAT    |                          | (14) GND                   | Latch input.                                                                                                                                                                                    |

| Pin<br>No. | Symbol | Typical pin voltage (DC) | Equivalent circuit | Description                                                                                                                             |

|------------|--------|--------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 12         | PS     |                          | Vcc                | Power saving pin. Power saving mode when this pin is Low.                                                                               |

| 15         | FC     | Open High                | 12<br>15<br>GND    | Switching for the phases of phase comparator output and the output signals of counter (reference, programmable) output to the TEST pin. |

| 17         | TEST   | High: 2.2V<br>Low: 2.0V  | 17                 | The signal output which is frequency-divided at the counter.                                                                            |

# **Electrical Characteristics** (Vcc = Vp = 3V, Ta = 25°C, refer to the Electrical Characteristics Measurement Circuit)

| Item                               |                               | Symbol      | Conditions                                                                | Min.      | Тур.  | Max.      | Unit |

|------------------------------------|-------------------------------|-------------|---------------------------------------------------------------------------|-----------|-------|-----------|------|

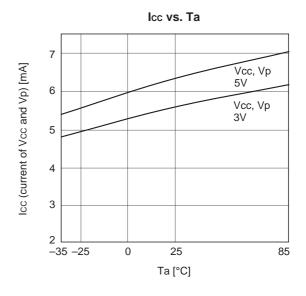

| Current consumption                |                               | Icc         |                                                                           |           | 5.84  | 8.7       | mA   |

|                                    | consumption<br>r saving mode) | Icc<br>(PS) |                                                                           |           | 360   | 510       | μA   |

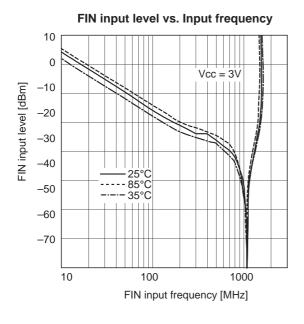

| FIN oper                           | ating frequency               | fin         | Vcc = Vp = 2.7V  to  5.5V<br>$Ta = -35^{\circ}C \text{ to } +85^{\circ}C$ | 100       |       | 1100      | MHz  |

| FIN input                          | level                         | Pin         | Vcc = Vp = 2.7V  to  5.5V<br>$Ta = -35^{\circ}C \text{ to } +85^{\circ}C$ | -10       |       | 10        | dBm  |

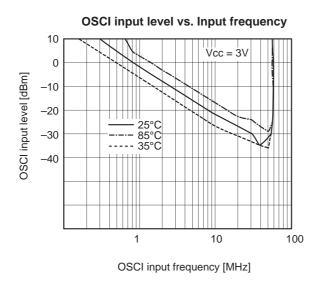

| OSCI op                            | erating frequency             | fosc        | Vcc = Vp = 2.7V  to  5.5V<br>$Ta = -35^{\circ}C \text{ to } +85^{\circ}C$ | 5         |       | 20        | MHz  |

| OSCI inp                           | ut level                      | Vosc        | Vcc = Vp = 2.7V  to  5.5V<br>$Ta = -35^{\circ}C \text{ to } +85^{\circ}C$ | 0.5       |       | 2         | Vpp  |

| Do1<br>Do2 High output current     |                               | Іон         |                                                                           |           |       | -1        | mA   |

| Do1<br>Do2 Low output current      |                               | loL         |                                                                           | 1         |       |           | mA   |

| Do2 lea                            | ]                             |             |                                                                           | <b>–1</b> |       | 1         | μA   |

| φR<br>φP High output voltage<br>LD |                               | Vон         | IL = 0.1mA                                                                | 2         | 2.18  |           | V    |

| φR<br>φP Low output voltage<br>LD  |                               | Vol         | IL = 0.1mA                                                                |           | 70.3  | 500       | mV   |

| СК                                 | High input voltage            | ViH         |                                                                           | Vcc×0.7   |       |           | V    |

| DATA                               | High input current            | Іон         | VIN = VCC                                                                 | -1        |       | 1         | μΑ   |

| LAT<br>PS                          | Low input voltage             | VIL         |                                                                           |           |       | Vcc × 0.3 | V    |

|                                    | Low input current             | lıL         | VIN = GND except for PS                                                   | -1        |       | 1         | μA   |

| PS                                 | Low input current             | lı∟         | VIN = GND                                                                 | -30       | -15.5 |           | μA   |

|                         | Item               | Symbol | Conditions                                  | Min.       | Тур.  | Max.      | Unit |

|-------------------------|--------------------|--------|---------------------------------------------|------------|-------|-----------|------|

|                         | High input voltage | ViH    |                                             | Vcc - 0.05 |       |           | V    |

| FC                      | High input current | Іін    | VIN = VCC                                   | -1         |       | 1         | μA   |

|                         | Low input voltage  | VIL    |                                             |            |       | 0.05      | ٧    |

|                         | Low input current  | lı∟    | Vin = GND                                   | -50        | -18.9 | 1         | μA   |

|                         | High input voltage | Vін    | Vcc = Vp = 5.5V                             | Vcc × 0.7  |       |           | ٧    |

| CK<br>DATA<br>LAT<br>PS | High input current | Іін    | Vcc = Vp = 5.5V,<br>Vin = Vcc               | -1         |       | 1         | μA   |

|                         | Low input voltage  | VIL    | Vcc = Vp = 5.5V                             |            |       | Vcc × 0.3 | V    |

|                         | Low input current  | lı∟    | Vcc = VP = 5.5V,<br>VIN = GND except for PS | -20        | 0     | 1         | μΑ   |

| PS                      | Low input current  | lıL    | Vcc = Vp = 5.5V,<br>Vin = GND               | -60        | -27.7 |           | μΑ   |

|                         | High input voltage | ViH    | Vcc = Vp = 5.5V                             | Vcc - 0.05 |       |           | V    |

| FC                      | High input current | Іін    | Vcc = Vp = 5.5V,<br>Vin = Vcc               | -1         |       | 1         | μΑ   |

|                         | Low input voltage  | VIL    | Vcc = Vp = 5.5V                             |            |       | 0.05      | V    |

|                         | Low input current  | lıL    | Vcc = Vp = 5.5V,<br>Vin = GND               | -60        | -34.7 | 1         | μA   |

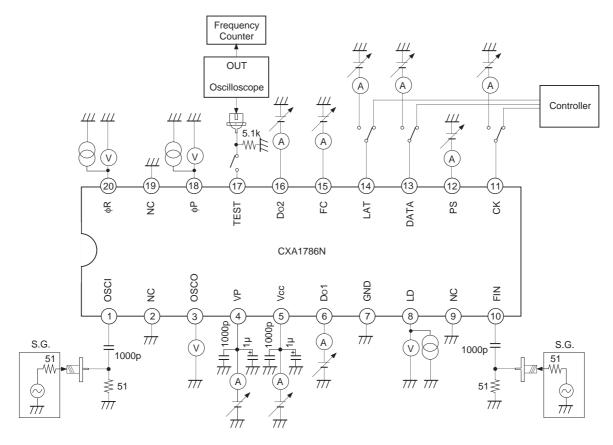

## **Electrical Characteristics Measurement Circuit**

Application circuits shown are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits or for any infringement of third party patent and other right due to same.

# **Description of Operation**

# 1. Data Setting Method

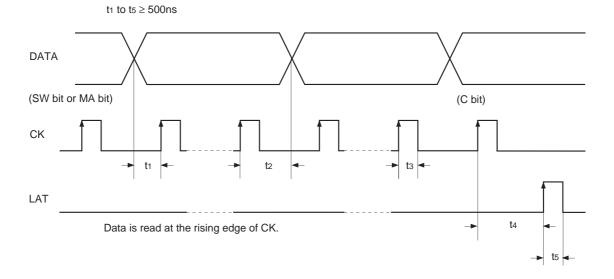

The data is set using three signals — CK, DATA, and LAT in this IC. In that case, the serial data as described below is input.

### (1) Data input method

The 15 bits of data should be input to the reference counter latch and the 18 bis of data to the pulse swallow programmable counter latch to set the all initializing state in this IC. Every one bit of data is retrieved into the shift resister at the rising edge of clock input to the CK pin when the data is input to the DATA pin. The input data is retrieved into the reference counter latch or the pulse swallow programmable counter latch according to the state of the final bit C.

The data is latched when the latch pulse is input to the LAT pin after 16 bits of data or 19 bits of data, which were added with the bit C, are sent to the shift resister.

For actual use, first input the 16 bits (including the frequency division setting bit SW for 2-modulus prescaler) of reference counter data from the controller as indicated above. In this time, set the final bit C High.

Next, input the 19 bits of pulse swallow programmable counter data in the same way. In this time, set the final bit C Low. Then, all of the interior state has been set. Hereafter, when only the programmable counter data is to be changed, only the latter 19 bits of programmable counter data should be changed. (In this case, set the bit C Low.)

#### (2) Control data construction

The control data consists of 16 bits for the reference counter and 19 bits for the pulse swallow programmable counter. The final bit of them is the identification code and the contents of data are discriminated by identifying the code. The frequency division value is composed of the binary values whose head is MSB as described on the next page.

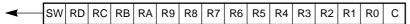

# (a) Data structure of reference counter

#### Input direction

(First, input the SW bit and input the C bit last.)

R0 to RD: Frequency division number of reference counter (Binary value with R0 as LSB)

SW: Switching bit of frequency division numbers of 2-modulus pre-scaler block for programmable counter.

| SW                        | 1                        | 0                          |

|---------------------------|--------------------------|----------------------------|

| Frequency division number | 64/65-frequency division | 128/129-frequency division |

C: This code decides the latch direction of data; set to High.

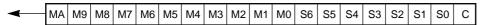

### (b) Data structure of pulse swallow programmable counter

#### Input direction

(First, input the MA bit and input the C bit last.)

M0 to MA: Frequency division number of main counter (Binary value with M0 as LSB)

S0 to S6: Frequency division number of swallow counter (Binary value with S0 as LSB)

C: This code decides the latch direction of data; set to Low.

The frequency division value of programmable counter can be obtained with the following equation;

N × M + S N: Frequency division value of 2-modulus pre-scaler (64 or 128)

(M > S) M: Main counter value

S: Swallow counter value

# (1) Data input timing

### 2. Power Save Pin (PS)

This pin is left High when it is open and in power saving mode at Low.

All circuits except for reference counter latch and pulse swallow programmable counter latch are set to off in the power saving mode. At that mode, Do1 and Do2 are high impedance and the data cannot be set.

\* The data of reference counter and programmable counter are hold in power saving mode.

#### 3. Do1 and Do2 Pins

These are the charge pump output pins. Do1 operates always. Do2 operates only when the LAT pin is High; it is in high impedance state when the LAT pin is Low.

#### 4. FC Pin

This pin switches the charge pump outputs (Do1, Do2) and the phases of phase comparator outputs ( $\phi P$ ,  $\phi R$ ). (Refer to the Table 1.)

#### 5. TEST Pin

This pin is for monitoring the counter output signal. The reference counter output and the pulse swallow programmable counter output are switched according to the FC state as shown at Table 1.

This pin is emitter follower output High level = Vcc - Vf and Low level = Vcc - Vf - 200mV (200mV amplitude). The DC bias current is decreased to save the power consumption so that the amplitude may not be monitored for monitoring the waveforms with oscilloscope. In that case, connect the TEST pin to ground with an approximately  $5k\Omega$  resistor.

Table 1. Phase comparator and TEST Pin outputs

|         | FC: High or open |    |    |      | FC: Low |    |    |      |

|---------|------------------|----|----|------|---------|----|----|------|

|         | Do1 (2)          | φR | φР | TEST | Do1 (2) | φR | φР | TEST |

| fr > fp | Н                | L  | L  | fr   | L       | Н  | Н  | fp   |

| fr = fp | Z                | L  | Н  | fr   | Z       | L  | Н  | fp   |

| fr < fp | L                | Н  | Н  | fr   | Н       | L  | L  | fp   |

<sup>\*</sup> Z: High impedance

fr: Output frequency of reference counter

H: High

fp: Output frequency of programmable counter

L: Low

CXA1786N

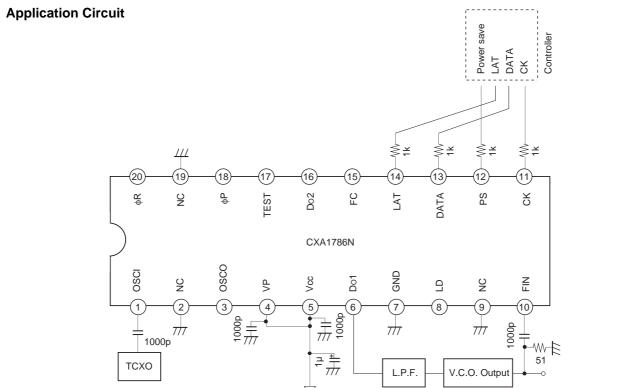

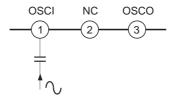

# 6. Reference signal (the input signal of reference counter)

The external oscillator signal can be used as the reference signal by inputting the signal of the external oscillator to the OSCI pin, and the reference signal can be also generated by connecting the crystal resonator to the OSCI and OSCO pins.

(1) Generation of the reference signal by the external oscillator Input the signal to the OSCI pin via a capacitor as shown below when the external oscillator signal is use as the reference signal.

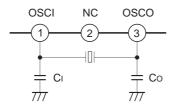

(2) Generation of the reference signal by the built-in oscillator

Connect the crystal resonator between OSCI and OSCO pins as shown below. Use the crystal resonator of several MHz and confirm the stability of the oscillation and others. The capacitance ratio of C<sub>I</sub> and Co should be 1 to 2:1, and their values should be selected so that the serial capacitance of C<sub>I</sub> and Co may be the load capacitance specified by the crystal vibrator.

## **Notes on Operation**

- Be careful to use this IC because the electrostatic resistance is the rank "A" due to handling the higher frequency signal of 1GHz

- Make the input route of the RF signal from the VCO as short as possible.

- Connect the Vcc and Vp pins to the ground respectively via the by-pass capacitors as short as possible because the frequency of signal used in this IC is higher.

# **Example of Representative Characteristics**

SONY CXA1786N

# Package Outline Unit: mm

# 20PIN SSOP (PLASTIC)

NOTE: Dimension "\*" does not include mold protrusion.

# PACKAGE STRUCTURE

|            |                | PACKAGE MATERIAL | EPOXY RESIN                   |

|------------|----------------|------------------|-------------------------------|

| SONY CODE  | SSOP-20P-L01   | LEAD TREATMENT   | SOLDER / PALLADIUM<br>PLATING |

| EIAJ CODE  | SSOP020-P-0044 | LEAD MATERIAL    | 42/COPPER ALLOY               |

| JEDEC CODE |                | PACKAGE MASS     | 0.1g                          |

|            |                |                  |                               |

**NOTE: PALLADIUM PLATING**

This product uses S-PdPPF (Sony Spec.-Palladium Pre-Plated Lead Frame).