**TOSHIBA TA8069F**

**TENTATIVE**

TOSHIBA BIPOLAR LINEAR INTEGRATED CIRCUIT SILICON MONOLITHIC

# TA8069F

## 4CH LOW SIDE DRIVER

TA8069F is built into four 0.5A low-side driver ICs which drive lamp, relay, and solenoid actuators. Inputs from DI1, DI2, DI3, and DI4 switch ON and OFF modes. Inputs are TTL-compatible, thus the device can also be directly controlled from a CPU or other control system. The device is equipped with low-standby (with all outputs off), self-diagnosis, and protection functions.

Weight: 0.79g (Typ.)

#### **FEATURES**

- 0.5A low-side driver

- Four built-in circuits (power supply, self-diagnosis, and protection functions for each circuit)

- Low standby current 0.1mA (Max.)

- Self-diagnosis output

Short: 1A (Typ.)

DG1 : OR output of OUT1 & OUT2; DG2 : OR output of OUT3 & OUT4

- Multiple protection functions Short, thermal, and overvoltage protection functions

- Built-in diodes for absorbing counter electromotive force

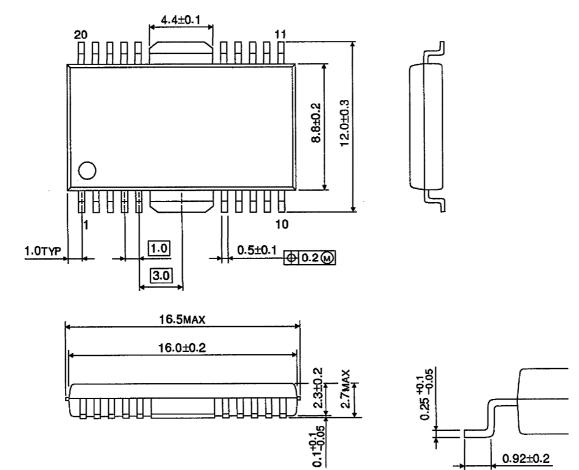

- 20-pin surface mount type plastic package: HSOP20-P-450

TOSHIBA is continually working to improve the quality and the reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to observe standards of safety, and to avoid situations in which a malfunction or failure of a TOSHIBA product could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent products specifications. Also, please keep in mind the precautions and conditions set forth in the TOSHIBA Semiconductor Reliability Handbook.

The products described in this document are subject to foreign exchange and foreign trade control laws.

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

The information contained herein is subject to change without notice.

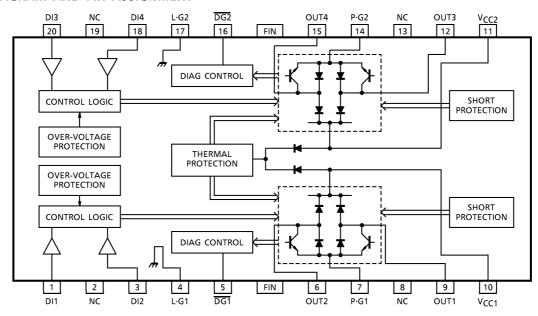

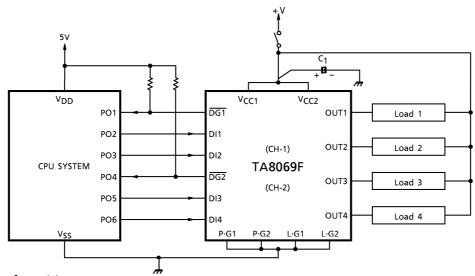

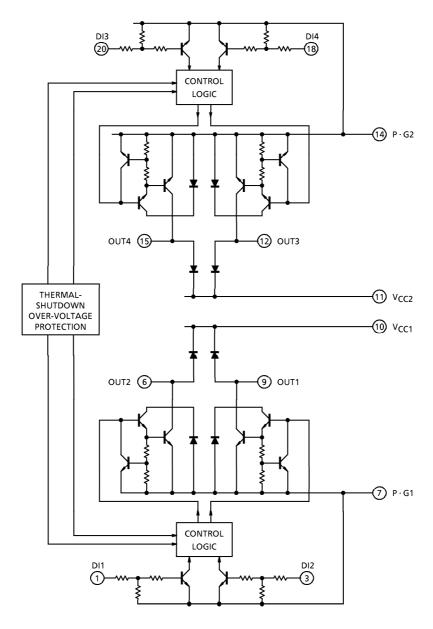

#### **BLOCK DIAGRAM AND PIN ASSIGNMENT**

## **PIN DESCRIPTION**

| PIN No.        | SYMBOL                              | DESCRIPTION                                                                                                                                                                                                                                                                                 |

|----------------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 20          | DI1, DI3                            | Input pins used to control output. H: output on                                                                                                                                                                                                                                             |

| 3, 18          | DI2, DI4                            | (See Table 1, Truth Table.)                                                                                                                                                                                                                                                                 |

| 4, 17          | L·G1, L·G2                          | Ground pins for logic portion.                                                                                                                                                                                                                                                              |

| 5, 16          | DG1, DG2                            | Self-diagnosis output pins (See Table 2, Truth Table & Timing Chart.)  NPN transistor open-collector output. When output becomes overcurrent, set to on; duty 97% on (low). At normal operation, set to open (high)."  DG1: OR output of OUT1 & OUT2  DG2: OR output of OUT3 & OUT4         |

| 6, 15<br>9, 12 | OUT2, OUT4<br>OUT1, OUT3            | Connected to load, with sink 0.5A. Features overcurrent detection function to protect IC from instantaneous destruction at load short (See section on Multiple Protections below.) Features diodes for absorbing counter electromotive force built into both V <sub>CC</sub> and GND sides. |

| 7, 14          | P·G1, P·G2                          | Ground pins for output portion.                                                                                                                                                                                                                                                             |

| 10, 11         | V <sub>CC1</sub> , V <sub>CC2</sub> | Power supply pins. When more than 30V is applied, overvoltage protection function turns off output to protect the IC and motor load.                                                                                                                                                        |

| 2, 8, 13, 19   | NC                                  | Not connected.                                                                                                                                                                                                                                                                              |

TRUTH TABLE 1: I/O

| INPUT     | OUTPUT               | OPERATING MODE |  |

|-----------|----------------------|----------------|--|

| DI1/2/3/4 | OUT1/2/3/4           | OPERATING MODE |  |

| Н         | ON                   |                |  |

| L         | OFF                  |                |  |

| ALL L     | OFF (high impedance) | standby        |  |

## TRUTH TABLE 2: SELF DIAGNOSIS

| OUT    | OUTPUT |        | DIAG |  |

|--------|--------|--------|------|--|

| OUT1/3 | OUT2/4 | LOAD   | DIAG |  |

| ON     | OFF    | Normal | Н    |  |

| ON     | OFF    | Short  | L*   |  |

| OFF    | ON     | Normal | Н    |  |

| OFF    | ON     | Short  | L*   |  |

| OFF    | OFF    | _      | Н    |  |

| ON     | ON     | Normal | Н    |  |

|        |        | Short  | L*   |  |

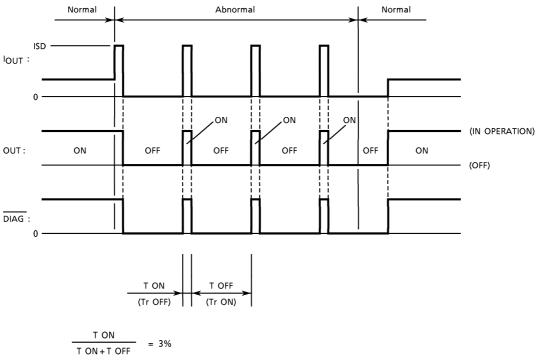

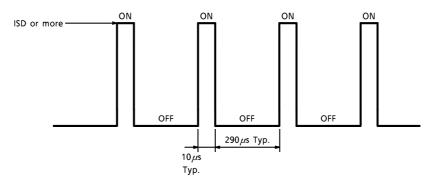

\*TIMING CHART

## **SELF DIAGNOSIS TIMING CHART**

$$\frac{\text{T ON}}{\text{T ON + T OFF}} = 3\%$$

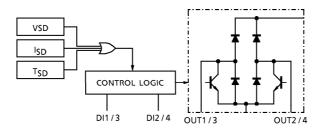

### Multiple protection operation

TA8069F features built-in overvoltage ( $V_{SD}$ ), overcurrent ( $I_{SD}$ ), and thermal ( $I_{SD}$ ) protection functions. These functions protect TA8069F (sometimes motors, too) from deterioration or destruction due to overpower stress.

The functions are independent from each other.

Functions are described below.

#### 1. Overvoltage protection (VSD)

#### Outline

When the voltage supplied to the V<sub>CC</sub> pin is less than the V<sub>SD</sub> detection voltage, output is controlled by input signals. When the V<sub>CC</sub> voltage is greater than the V<sub>SD</sub> detection voltage, output becomes high impedance (off) regardless of input signals.

#### Operation

The V<sub>SD</sub> voltage is detected by comparing the zener voltage with the voltage obtained by dividing V<sub>CC</sub> by the resistance. If the center voltage of the resistance is higher than the zener voltage, a transistor-off instruction is issued to the control logic portion; if lower, the logic portion is controlled by input signals.

## 2. Thermal protection (TSD)

#### Outline

When the junction temperature (chip temperature) is less than the T<sub>SD</sub> detection temperature, output is controlled by input signals. When the junction temperature is greater than the detection temperature, output becomes high impedance regardless of input signals.

#### Operation

The temperature is detected by monitoring  $V_F$  of diodes on the chip. If the diode  $V_F$  is lower than the internal reference voltage, a transistor-off instruction is issued to the logic portion; if higher, the logic portion is controlled by input signals.

## 3. Overcurrent protection (ISD)

#### Outline

When the output current is less than the  $I_{SD}$  detection current, output is controlled by input signals. When the output current is greater than the detection current, output changes to switching waveform as in Figure 1.

Figure 1 Switching Waveforms

#### Operation

The output current is detected by monitoring the sense resistance. Detection circuits are connected to the self-diagnosis output pins ( $\overline{DG1}$  and  $\overline{DG2}$ ), then further connected to the short circuit protection circuits. When current exceeding the I<sub>SD</sub> detection current flows to one of the two channels of self-diagnosis output, the corresponding short circuit protection circuit is activated. The short circuit protection circuit is built into the timer. If overcurrent mode continues  $10\mu s$  (Typ.), the circuit changes the output to high impedance mode, then returns to on mode after  $290\mu s$  (Typ.). The above switching waveform is output repeatedly as long as the circuit is in overcurrent mode.

## • Caution for application

The overcurrent protection is used to protect the IC from instantaneous destruction due to short circuits. If overcurrent continues, configure a system which changes the IC to standby mode using the self diagnosis signal.

Note that the time required for switching the IC from output short (overcurrent detection) to standby must be 1s or less.

## **MAXIMUM RATING** (Ta = 25°C)

| CHARACTERISTIC        | SYMBOL           | RATING                     | UNIT |

|-----------------------|------------------|----------------------------|------|

| Bower Supply Voltage  | V <sub>CC</sub>  | 30                         |      |

| Power Supply Voltage  | V <sub>CC</sub>  | 60 (1s)                    | V    |

| Input Voltage         | V <sub>IN</sub>  | -0.3~V <sub>CC</sub> + 0.3 | ٧    |

| Output Current        | IO.AVE           | 0.5                        | Α    |

| Operating Temperature | T <sub>opr</sub> | <b>- 40∼110</b>            | °C   |

| Storage Temperature   | T <sub>stg</sub> | <b>-</b> 55∼150            | °C   |

| Lead Temperature Time | T <sub>sol</sub> | 260 (10s)                  | °C   |

## **HSOP20-P-450 THERMAL RESISTANCE DATA** (Ta = 25°C)

| CHARACTERISTIC   | SYMBOL | UNIT | TEST CONDITION                                  |

|------------------|--------|------|-------------------------------------------------|

| $R_{\theta j-a}$ | 125    | °C/W | _                                               |

| $R_{\theta j-c}$ | 13     | °C/W | _                                               |

| P <sub>D1</sub>  | 1.0    | W    | Without radiation board                         |

| P <sub>D2</sub>  | 1.5    | W    | 60×30×1.6mm 50% Cu mounted                      |

| P <sub>D3</sub>  | 3.2    | W    | $50 \times 50 \times 1.0$ mm Iron board mounted |

| P <sub>D4</sub>  | 9.6    | W    | Infinite radiation board mounted                |

**ELECTRICAL CHARACTERISTICS** (Unless otherwise specified,  $V_{CC} = 8 \sim 16V$ ,  $T_{C} = -40 \sim 110^{\circ}C$ )

| CHARACTERISTIC               | SYMBOL           | PIN                                | TEST<br>CIR-<br>CUIT | TEST CONDITION                     | MINO. | TYP. | MAX. | UNIT    |

|------------------------------|------------------|------------------------------------|----------------------|------------------------------------|-------|------|------|---------|

| Power Supply Current         | l <sub>CC1</sub> | V <sub>CC1</sub> /V <sub>CC2</sub> |                      | Output all off (standby)           | _     | I    | 0.1  | - mA    |

| rower supply current         | l <sub>CC2</sub> | Total                              |                      | _                                  |       | 30   | 50   |         |

| Input Voltage                | $V_{IL}$         | DI1/2/3/4                          | _                    | _                                  |       |      | 0.8  | V       |

| Imput voitage                | V <sub>IH</sub>  | D11727374                          | —                    | _                                  | 2.0   | _    | _    |         |

| Input Current                | V <sub>IL</sub>  | DI1/2/3/4                          | _                    | V <sub>IN</sub> = 0.4V             | _     | 10   | 20   | ا ۸٫۸   |

| Impat Carrent                | V <sub>IH</sub>  | D11727374                          | _                    | V <sub>IN</sub> = 5V               | _     | 300  | 600  | μΑ      |

| Output Saturation<br>Voltage | V <sub>sat</sub> | OUT1/2/3/4                         | _                    | I <sub>O</sub> = 0.4A              | _     | 1.1  | 1.3  | V       |

| Output Leakage               | ILEAK-U          | OUT1/2/3/4                         |                      | V <sub>OUT</sub> = 0V              | - 10  | _    | _    |         |

| Current                      | ILEAK-L          | 0011/2/3/4                         |                      | V <sub>OUT</sub> = V <sub>CC</sub> |       |      | 10   | $\mu$ A |

| Diode Forward Voltage        | V <sub>F-U</sub> | OUT1/2/3/4                         | _                    | I <sub>F</sub> = 0.4A              | _     | 1.5  | _    | V       |

|                              | $V_{F-L}$        |                                    | _                    |                                    | _     | 1.5  | _    |         |

| Output Voltage               | V <sub>OL</sub>  | DIAG 1/2                           |                      | $I_{OL} = 3mA$                     | _     |      | 0.5  | ٧       |

| Output Leakage<br>Current    | ILEAK            | DIAG 1/2                           |                      | V <sub>OUT</sub> = V <sub>CC</sub> | 1     | 1    | 10   | μΑ      |

| Overcurrent Detection        | ISD              | _                                  | —                    | _                                  |       | 1.0  | _    | Α       |

| Shutdown Temperature         | T <sub>SD</sub>  | _                                  | _                    | _                                  |       | 150  | _    | °C      |

| Over-voltage Detection       | $V_{SD}$         | _                                  |                      | _                                  | _     | 30   | _    | V       |

| Transfor Dolay Time          | t <sub>pLH</sub> | _                                  | _                    | _                                  |       | 1    | 10   |         |

| Transfer Delay Time          | t <sub>pHL</sub> | _                                  | _                    | _                                  | _     | 1    | 10   | $\mu$ s |

## **APPLICATION CIRCUIT**

\* Cautions for wirings C<sub>1</sub> is used for absorbing disturbance or noise. Connect C1 as near the IC as possible.

## I/O EQUIVALENT CIRCUIT

**TOSHIBA**

## **OUTLINE DRAWING**

HSOP12-P-450-1.00

Unit: mm

Weight: 0.79g (Typ.)

0.92±0.2