### SONY

### **CXD2597Q**

### CD Digital Signal Processor with Built-in Digital Servo and DAC

### **Description**

The CXD2597Q is a digital signal processor LSI for CD players. This LSI incorporates a digital servo, digital filter, zero detection circuit, 1-bit DAC and analog low-pass filter on a single chip.

### **Features**

Digital Signal Processor (DSP) Block

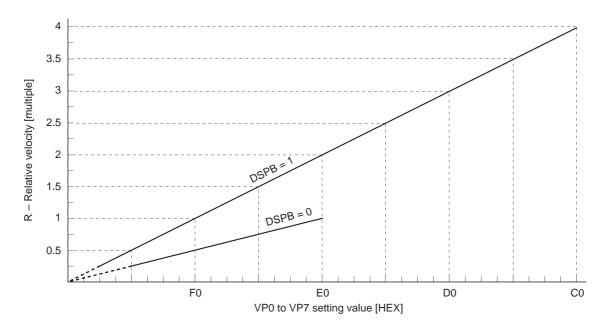

- Playback mode supporting CAV (Constant Angular Velocity)

- Frame jitter free

- 0.5× to 4× continuous playback possible

- · Allows relative rotational velocity readout

- Wide capture range playback mode

- · Spindle rotational velocity following method

- Supports normal-speed to 4× speed playback

- 16K RAM

- EFM data demodulation

- Enhanced EFM frame sync signal protection

- SEC strategy-based error correction

- Subcode demodulation and Sub Q data error detection

- Digital spindle servo

- 16-bit traverse counter

- · Asymmetry correction circuit

- CPU interface on serial bus

- Error correction monitor signal, etc. output from a new CPU interface

- · Servo auto sequencer

- Digital audio interface outputs

- Digital level meter, peak meter

- CD TEXT data demodulation

### Digital Servo (DSSP) Block

- Microcomputer software-based flexible servo control

- Offset cancel function for servo error signal

- Auto gain control function for servo loop

- E:F balance, focus bias adjustment functions

Digital Filter, DAC and Analog Low-Pass Filter Blocks

- DBB (digital bass boost) function

- Double-speed playback supported

- Digital de-emphasis

- Digital attenuation

- Zero detection function

- 8Fs oversampling digital filter

- S/N: 100dB or more (master clock: 384Fs, typ.)

Logical value: 109dB

- THD + N: 0.007% or less (master clock: 384Fs, typ.)

- Rejection band attenuation: -60dB or less

### **Applications**

CD players

### Structure

Silicon gate CMOS IC

### **Absolute Maximum Ratings**

| <ul> <li>Supply voltage</li> </ul>      | VDD  | -0.3 to $+7.0$ V          |

|-----------------------------------------|------|---------------------------|

| <ul> <li>Input voltage</li> </ul>       | Vı   | –0.3 to +7.0 V            |

|                                         |      | (Vss - 0.3V to Vdd + 0.3) |

| <ul> <li>Output voltage</li> </ul>      | Vo   | –0.3 to +7.0 V            |

| <ul> <li>Storage temperature</li> </ul> | Tstg | −40 to +125 °C            |

• Supply voltage difference

Vss – AVss –0.3 to +0.3 V Vpp – AVpp –0.3 to +0.3 V

Note) AVDD includes XVDD and AVss includes XVss.

### **Recommended Operating Conditions**

Supply voltage

VDD

+2.7 to +5.5

V

Operating temperature

Topr

-20 to +75

°C

Note)

The VDD for the CXD2597Q varies according to the playback speed selection.

| Playback | Vdd [V]      |            |  |  |  |

|----------|--------------|------------|--|--|--|

| speed    | CD-DSP block | DAC block  |  |  |  |

| 4×       | 4.75 to 5.25 |            |  |  |  |

| 2×       | 3.0 to 5.5   | 4.5 to 5.5 |  |  |  |

| 1×       | 2.7 to 5.5   | 2.7 to 5.5 |  |  |  |

### I/O Capacitance

| <ul> <li>Input capacitance</li> </ul>  | Cı   | 11 (Max.) | рF |

|----------------------------------------|------|-----------|----|

| <ul> <li>Output capacitance</li> </ul> | Co   | 11 (Max.) | pF |

| <ul> <li>I/O capacitance</li> </ul>    | CI/O | 11 (Max.) | рF |

**Note)** Measurement conditions VDD = VI = 0VfM = 1MHz

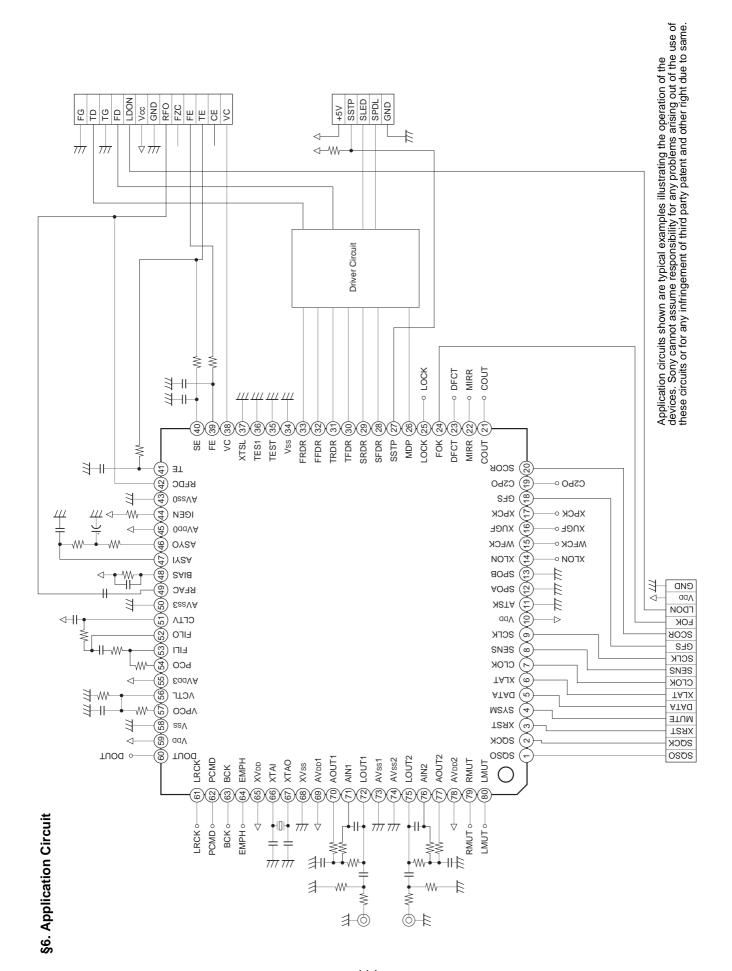

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

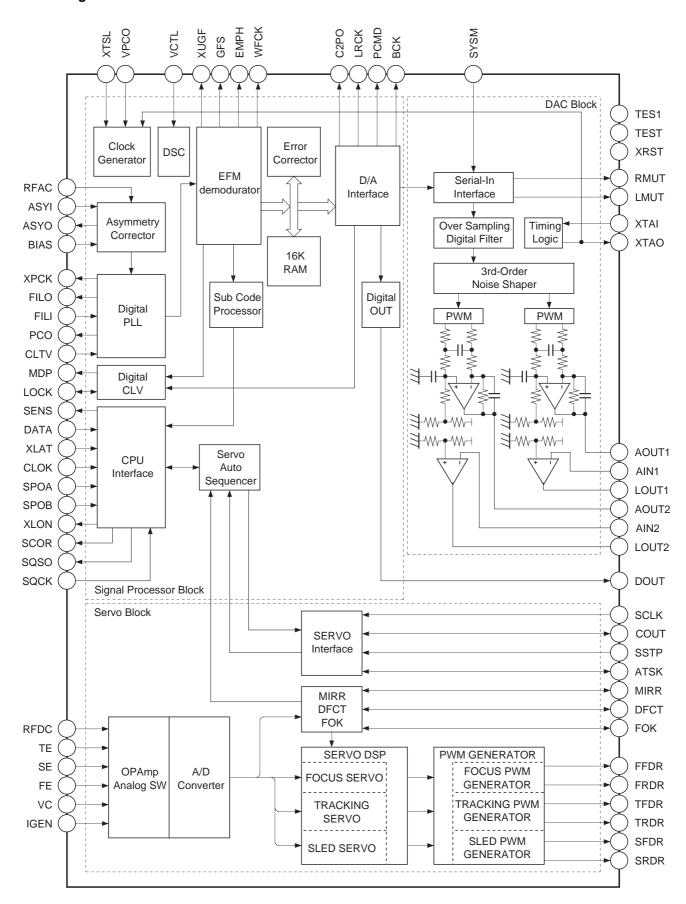

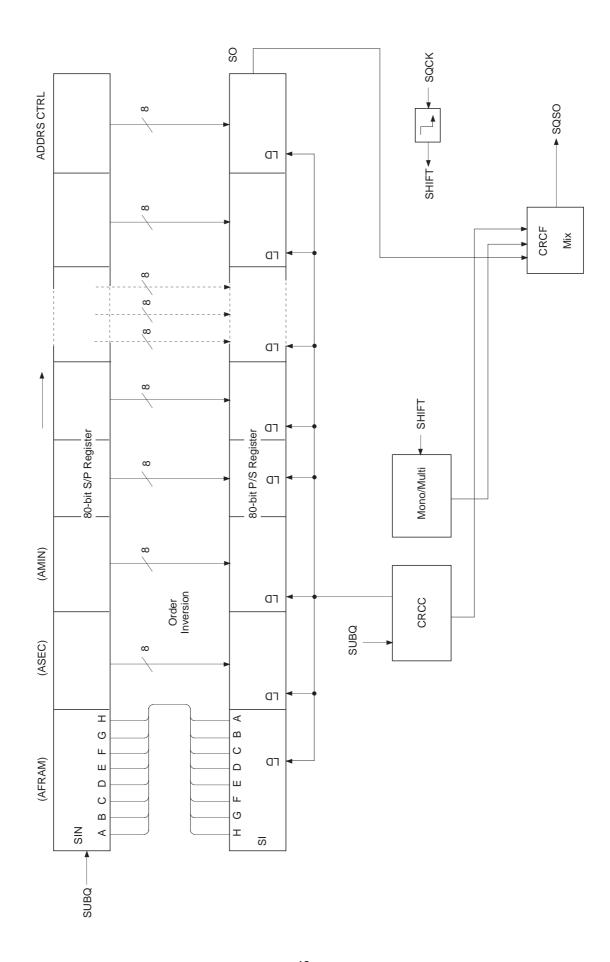

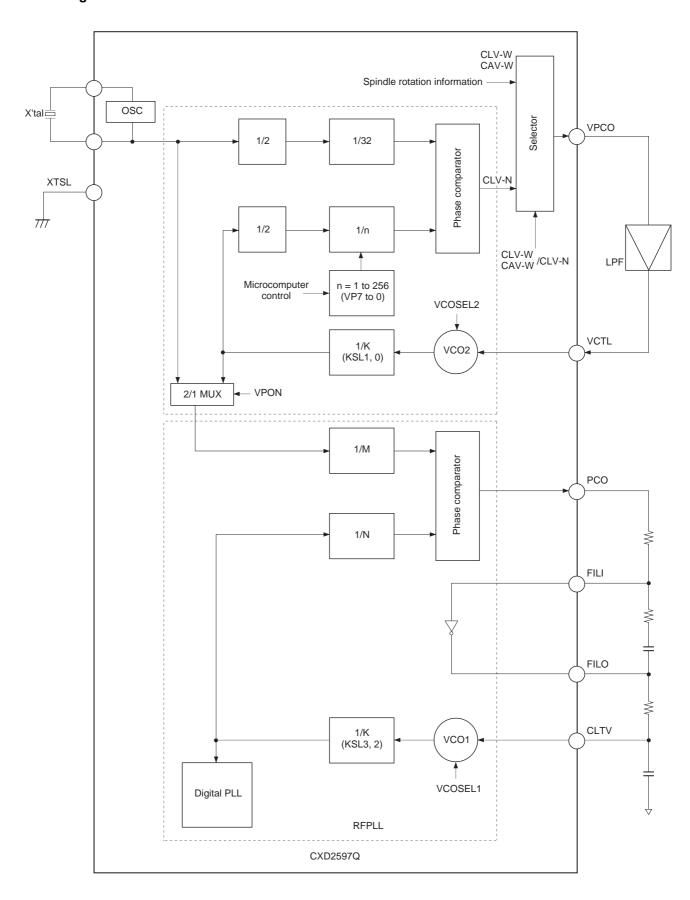

### **Block Diagram**

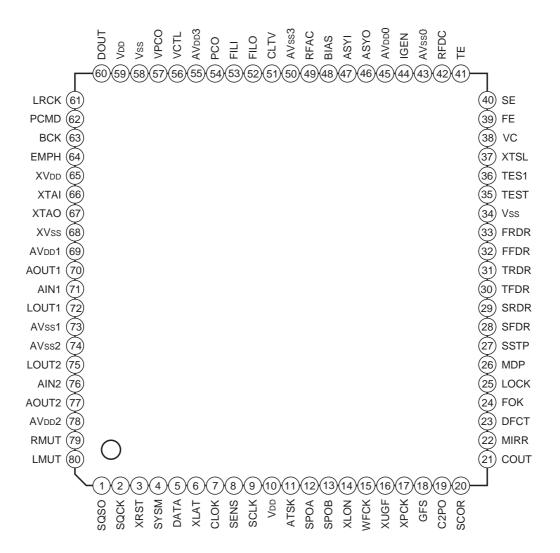

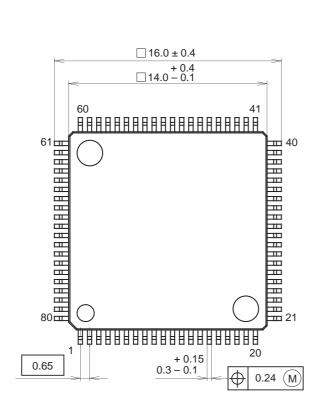

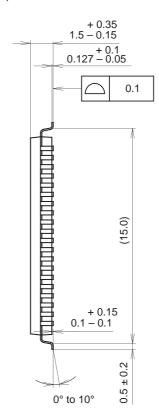

### **Pin Configuration**

### **Pin Description**

| Pin<br>No. | Symbol | I/O |         | Description                                                                                                                                                       |

|------------|--------|-----|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

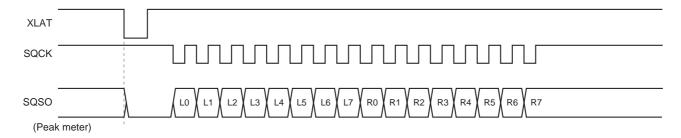

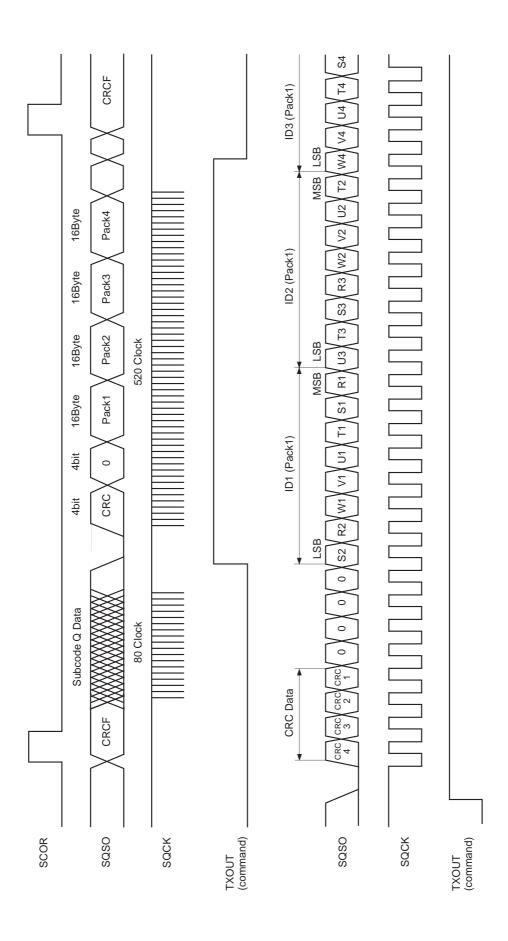

| 1          | SQSO   | 0   | 1, 0    | Sub Q 80-bit, PCM peak and level data outputs. CD TEXT data output.                                                                                               |

| 2          | SQCK   | I   |         | SQSO readout clock input.                                                                                                                                         |

| 3          | XRST   | I   |         | System reset. Reset when low.                                                                                                                                     |

| 4          | SYSM   | I   |         | Mute input. Muted when high.                                                                                                                                      |

| 5          | DATA   | I   |         | Serial data input from CPU.                                                                                                                                       |

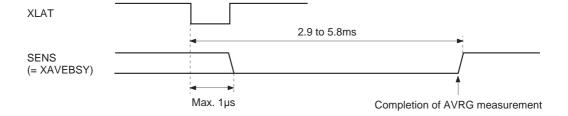

| 6          | XLAT   | I   |         | Latch input from CPU. Serial data is latched at the falling edge.                                                                                                 |

| 7          | CLOK   | I   |         | Serial data transfer clock input from CPU.                                                                                                                        |

| 8          | SENS   | 0   | 1, 0    | SENS output to CPU.                                                                                                                                               |

| 9          | SCLK   | ı   |         | SENS serial data readout clock input.                                                                                                                             |

| 10         | VDD    | _   | _       | Digital power supply.                                                                                                                                             |

| 11         | ATSK   | I/O | 1, 0    | Anti-shock input/output.                                                                                                                                          |

| 12         | SPOA   | ı   |         | Microcomputer extension interface (input A)                                                                                                                       |

| 13         | SPOB   | I   |         | Microcomputer extension interface (input B)                                                                                                                       |

| 14         | XLON   | 0   | 1, 0    | Microcomputer extension interface (output)                                                                                                                        |

| 15         | WFCK   | 0   | 1, 0    | WFCK output.                                                                                                                                                      |

| 16         | XUGF   | 0   | 1, 0    | XUGF output. MINT1 or RFCK is output by switching with the command.                                                                                               |

| 17         | XPCK   | 0   | 1, 0    | XPCK output. MNT0 is output by switching with the command.                                                                                                        |

| 18         | GFS    | 0   | 1, 0    | GFS output. MNT3 or XROF is output by switching with the command.                                                                                                 |

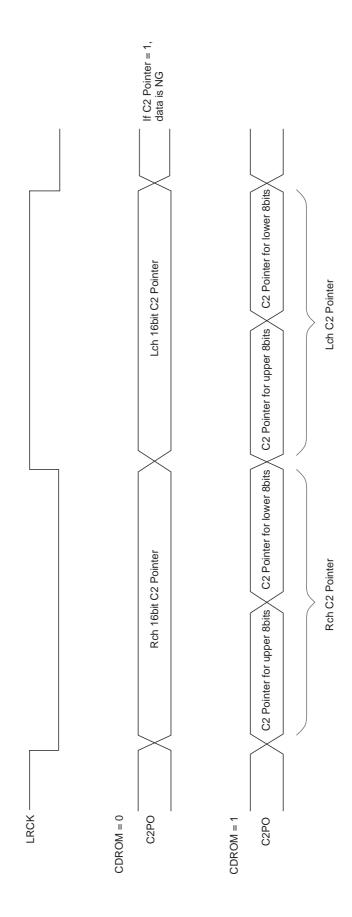

| 19         | C2PO   | 0   | 1, 0    | C2PO output. GTOP is output by switching with the command.                                                                                                        |

| 20         | SCOR   | 0   | 1, 0    | Outputs a high signal when either subcode sync S0 or S1 is detected.                                                                                              |

| 21         | COUT   | I/O | 1, 0    | Track count signal input/output.                                                                                                                                  |

| 22         | MIRR   | I/O | 1, 0    | Mirror signal input/output.                                                                                                                                       |

| 23         | DFCT   | I/O | 1, 0    | Defect signal input/output.                                                                                                                                       |

| 24         | FOK    | I/O | 1, 0    | Focus OK signal input/output.                                                                                                                                     |

| 25         | LOCK   | I/O | 1, 0    | GFS is sampled at 460Hz; when GFS is high, this pin outputs a high signal. If GFS is low eight consecutive samples, this pin outputs low. Or input when LKIN = 1. |

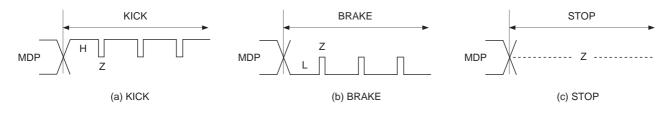

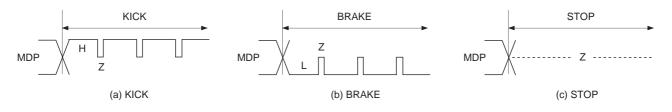

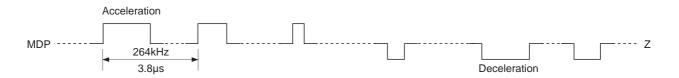

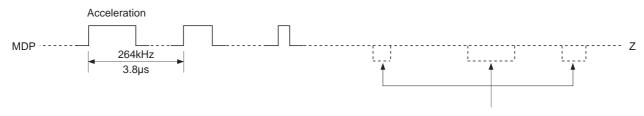

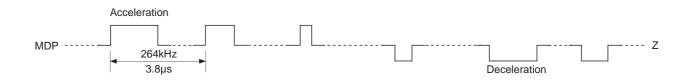

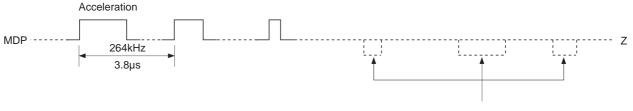

| 26         | MDP    | 0   | 1, Z, 0 | Spindle motor servo control output.                                                                                                                               |

| 27         | SSTP   | I   |         | Disc innermost track detection signal input.                                                                                                                      |

| 28         | SFDR   | 0   | 1, 0    | Sled drive output.                                                                                                                                                |

| 29         | SRDR   | 0   | 1, 0    | Sled drive output.                                                                                                                                                |

| 30         | TFDR   | 0   | 1, 0    | Tracking drive output.                                                                                                                                            |

| 31         | TRDR   | 0   | 1, 0    | Tracking drive output.                                                                                                                                            |

| 32         | FFDR   | 0   | 1, 0    | Focus drive output.                                                                                                                                               |

| 33         | FRDR   | 0   | 1, 0    | Focus drive output.                                                                                                                                               |

| 34         | Vss    | _   | _       | Digital GND.                                                                                                                                                      |

| 35         | TEST   | I   |         | Test pin. Normally, GND.                                                                                                                                          |

| Pin<br>No. | Symbol             | I/O |         | Description                                                                                            |

|------------|--------------------|-----|---------|--------------------------------------------------------------------------------------------------------|

| 36         | TES1               | ı   |         | Test pin. Normally, GND.                                                                               |

| 37         | XTSL               | I   |         | Crystal selection input. Low when the crystal is 16.9344MHz; high when the crystal is 33.8688MHz.      |

| 38         | VC                 | ı   |         | Center voltage input.                                                                                  |

| 39         | FE                 | _   |         | Focus error signal input.                                                                              |

| 40         | SE                 | _   |         | Sled error signal input.                                                                               |

| 41         | TE                 | _   |         | Tracking error signal input.                                                                           |

| 42         | RFDC               | _   |         | RF signal input.                                                                                       |

| 43         | AVss0              | _   | _       | Analog GND.                                                                                            |

| 44         | IGEN               | ı   |         | Operational amplifier constant current input.                                                          |

| 45         | AVDD0              | _   | _       | Analog power supply.                                                                                   |

| 46         | ASYO               | 0   | 1, 0    | EFM full-swing output. (low = Vss, high = VDD)                                                         |

| 47         | ASYI               | I   |         | Asymmetry comparator voltage input.                                                                    |

| 48         | BIAS               | I   |         | Asymmetry circuit constant current input.                                                              |

| 49         | RFAC               | ı   |         | EFM signal input.                                                                                      |

| 50         | AVss3              |     | _       | Analog GND.                                                                                            |

| 51         | CLTV               | I   |         | Multiplier VCO1 control voltage input.                                                                 |

| 52         | FILO               | 0   | Analog  | Master PLL filter output. (slave = digital PLL)                                                        |

| 53         | FILI               | ı   |         | Master PLL filter input.                                                                               |

| 54         | PCO                | 0   | 1, Z, 0 | Master PLL charge pump output.                                                                         |

| 55         | AVDD3              | _   | _       | Analog power supply.                                                                                   |

| 56         | VCTL               | ı   |         | Wide-band EFM PLL VCO2 control voltage input.                                                          |

| 57         | VPCO               | 0   | 1, Z, 0 | Wide-band EFM PLL charge pump output.                                                                  |

| 58         | Vss                |     | _       | Digital GND.                                                                                           |

| 59         | VDD                | _   | _       | Digital power supply.                                                                                  |

| 60         | DOUT               | 0   | 1, 0    | Digital Out output.                                                                                    |

| 61         | LRCK               | 0   | 1, 0    | D/A interface. LR clock output f = Fs.                                                                 |

| 62         | PCMD               | 0   | 1, 0    | D/A interface. Serial data output. (two's complement, MSB first)                                       |

| 63         | вск                | 0   | 1, 0    | D/A interface. Bit clock output.                                                                       |

| 64         | EMPH               | 0   | 1, 0    | Outputs a high signal when the playback disc has emphasis, and a low signal when there is no emphasis. |

| 65         | XVDD               | _   | _       | Master clock power supply.                                                                             |

| 66         | XTAI               | I   |         | Crystal oscillation circuit input. Master clock is externally input from this pin.                     |

| 67         | XTAO               | 0   |         | Crystal oscillation circuit output.                                                                    |

| 68         | XVss               | _   | _       | Master clock GND.                                                                                      |

| 69         | AV <sub>DD</sub> 1 | _   | _       | Analog power supply.                                                                                   |

| 70         | AOUT1              | 0   |         | L ch analog output.                                                                                    |

| 71         | AIN1               | ı   |         | L ch operational amplifier input.                                                                      |

| Pin<br>No. | Symbol | I/O |      | Description                        |

|------------|--------|-----|------|------------------------------------|

| 72         | LOUT1  | 0   |      | L ch LINE output.                  |

| 73         | AVss1  | _   | _    | Analog GND.                        |

| 74         | AVss2  | _   | _    | Analog GND.                        |

| 75         | LOUT2  | 0   |      | R ch LINE output.                  |

| 76         | AIN2   | ı   |      | R ch operational amplifier output. |

| 77         | AOUT2  | 0   |      | R ch analog output.                |

| 78         | AVDD2  | _   | _    | Analog power supply.               |

| 79         | RMUT   | 0   | 1, 0 | R ch zero detection flag.          |

| 80         | LMUT   | 0   | 1, 0 | L ch zero detection flag.          |

### **Notes)** • PCMD is a MSB first, two's complement output.

- GTOP is used to monitor the frame sync protection status. (High: sync protection window opens.)

- XUGF is the frame sync obtained from the EFM signal, and is negative pulse. It is the signal before sync protection.

- XPCK is the inverse of the EFM PLL clock. The PLL is designed so that the falling edge and the EFM signal transition point coincide.

- The GFS signal goes high when the frame sync and the insertion protection timing match.

- RFCK is derived from the crystal accuracy, and has a cycle of 136µs.

- C2PO represents the data error status.

- XROF is generated when the 16K RAM exceeds the ±4F jitter margin.

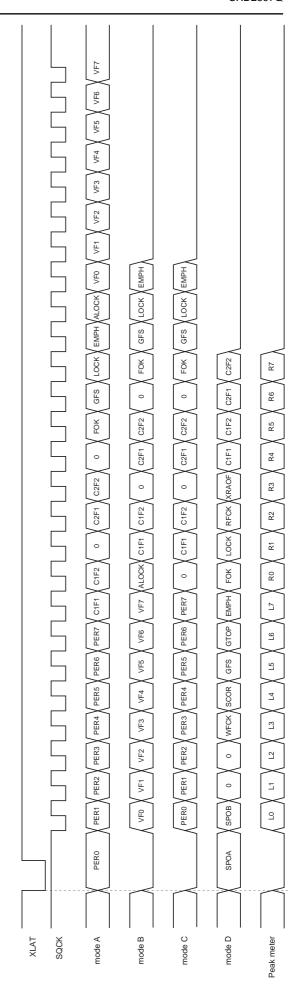

### **Monitor Pin Output Combinations**

| Comm  | and bit | Output data |      |      |      |  |  |  |

|-------|---------|-------------|------|------|------|--|--|--|

| MTSL1 | MTSL0   | Output data |      |      |      |  |  |  |

| 0     | 0       | XUGF        | XPCK | GFS  | C2PO |  |  |  |

| 0     | 1       | MNT1        | MNT0 | MNT3 | C2PO |  |  |  |

| 1     | 0       | RFCK        | XPCK | XROF | GTOP |  |  |  |

### **Electrical Characteristics**

### 1. DC Characteristics

$(VDD = AVDD = 5.0V \pm 5\%, Vss = AVss = 0V, Topr = -20 to +75°C)$

|                        | Item                      |          | Conditions                 | Min.      | Тур. | Max.   | Unit                           | Applicable pins |  |

|------------------------|---------------------------|----------|----------------------------|-----------|------|--------|--------------------------------|-----------------|--|

| Input                  | High level input voltage  | ViH (1)  |                            | 0.7Vdd    |      |        | V                              | *4 **0          |  |

| voltage (1)            | Low level input voltage   | Vı∟ (1)  |                            |           |      | 0.3Vpd | V                              | *1, *9          |  |

| Input                  | High level input voltage  | VIH (2)  | Schmitt input              | 0.8Vpp    |      |        | V                              | *0 *40          |  |

| voltage (2)            | Low level input voltage   | VIL (2)  | Scrimitt input             |           |      | 0.2VDD | /DD V DD V DD V DD V DD V DD V | - *2, *10       |  |

| Input<br>voltage (3)   | Input voltage             | VIN(3)   | Analog input               | Vss       |      | VDD    | V                              | *3, *7, *8      |  |

| Output                 | High level output voltage | Vон (1)  | Iон = −2mA                 | VDD - 0.8 |      | VDD    | V                              | 4.4             |  |

| voltage (1)            | Low level output voltage  | Vol (1)  | IoL = 4mA                  | Vss       |      | 0.4    | V                              | *4              |  |

| Output                 | High level output voltage | Vон (2)  | Iон = −6mA                 | VDD - 0.8 |      | VDD    | V                              | - *5            |  |

| voltage (2)            | Low level output voltage  | Vol. (2) | IoL = 4mA                  | Vss       |      | 0.4    | V V V V V V V                  | *5              |  |

| Output                 | High level output voltage | Vон (3)  | Iон = -0.28mA              | VDD - 0.5 |      | VDD    | V                              | - *6            |  |

| voltage (3)            | Low level output voltage  | Vol (3)  | IoL = 0.36mA               | Vss       |      | 0.4    | V                              | ***             |  |

| Input leak co          | urrent (1)                | I⊔ (1)   | VIN = Vss<br>or VDD        | -10       |      | 10     | μA                             | *1, *2          |  |

| Input leak current (2) |                           | Iu (2)   | VIN = Vss<br>or VDD        | -40       |      | 40     | μA                             | *9, *10         |  |

| Input leak co          | urrent (3)                | I⊔ (3)   | Vı = 1.5 to 3.5V           | -20       |      | 20     | μΑ                             | *7              |  |

| Input leak co          | urrent (4)                | I⊔ (4)   | $V_1 = 0 \text{ to } 5.0V$ | -40       |      | 600    | μΑ                             | *8              |  |

### Applicable pins

- \*1 SYSM, DATA, XLAT, SSTP, XTSL, TEST, TES1

- \*2 SQCK, XRST, CLOK

- \*3 ASYI, RFAC, CLTV, FILI, VCTL

- \*4 SQSO, SENS, ATSK, XLON, WFCK, XUGF, XPCK, GFS, C2PO, SCOR, COUT, MIRR, DFCT, FOK, LOCK, SFDR, SRDR, TFDR, TRDR, FFDR, FRDR, ASYO, DOUT, LRCK, PCMD, BCK, EMPH, RMUT, LMUT

- \*5 MDP, PCO, VPCO

- \*6 FILO

- \*7 VC, FE, SE, TE

- \*8 RFDC

- \*9 ATSK, COUT, MIRR, DFCT, FOK, LOCK

- \*10 SCLK, SPOA, SPOB

### 2. AC Characteristics

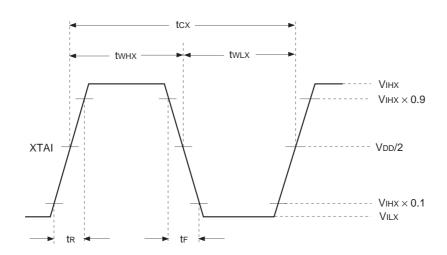

### (1) XTAI pin

### (a) When using self-excited oscillation

$$(Topr = -20 \text{ to } +75^{\circ}C, VDD = AVDD = 5.0V \pm 5\%)$$

| Item                  | Symbol | Min. | Тур. | Max. | Unit |

|-----------------------|--------|------|------|------|------|

| Oscillation frequency | fmax   | 7    |      | 34   | MHz  |

### (b) When inputting pulses to XTAI pin

$$(Topr = -20 \text{ to } +75^{\circ}C, VDD = AVDD = 5.0V \pm 5\%)$$

| Item                   | Symbol      | Min.      | Тур. | Max.  | Unit |

|------------------------|-------------|-----------|------|-------|------|

| High level pulse width | twnx        | 13        |      | 500   | ns   |

| Low level pulse width  | twLx        | 13        |      | 500   | ns   |

| Pulse cycle            | <b>t</b> cĸ | 26        |      | 1,000 | ns   |

| Input high level       | Vihx        | VDD - 1.0 |      |       | V    |

| Input low level        | VILX        |           |      | 0.8   | V    |

| Rise time, fall time   | tr, tr      |           |      | 10    | ns   |

### (c) When inputting sine waves to XTAI pin via a capacitor

$$(Topr = -20 \text{ to } +75^{\circ}C, VDD = AVDD = 5.0V \pm 5\%)$$

| Item            | Symbol | Min. | Тур. | Max.      | Unit |

|-----------------|--------|------|------|-----------|------|

| Input amplitude | Vı     | 2.0  |      | VDD + 0.3 | Vp-p |

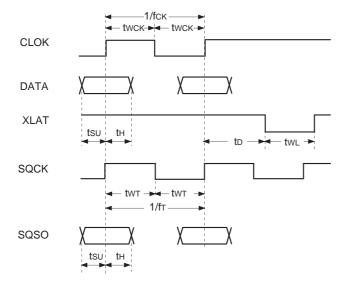

### (2) CLOK, DATA, XLAT and SQCK pin

$(VDD = AVDD = 5.0V \pm 5\%, Vss = AVss = 0V, Topr = -20 to +75°C)$

| Item              | Symbol      | Min.      | Тур. | Max.       | Unit |

|-------------------|-------------|-----------|------|------------|------|

| Clock frequency   | fск         |           |      | 0.65       | MHz  |

| Clock pulse width | twck        | 750       |      |            | ns   |

| Setup time        | <b>t</b> su | 300       |      |            | ns   |

| Hold time         | tн          | 300       |      |            | ns   |

| Delay time        | <b>t</b> D  | 300       |      |            | ns   |

| Latch pulse width | twL         | 750       |      |            | ns   |

| SQCK frequency    | f⊤          |           |      | 0.65 Note) | MHz  |

| SQCK pulse width  | <b>t</b> wT | 750 Note) |      |            | ns   |

**Note)** In quasi double-speed playback mode, except when SQSO is Sub Q Read, the SQCK maximum operating frequency is 300kHz and its minimum pulse width is 1.5µs.

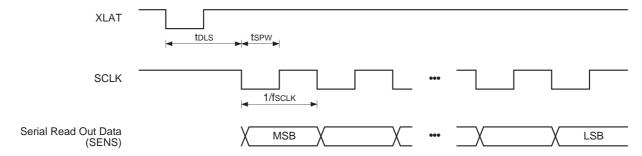

### (3) SCLK pin

| Item             | Symbol       | Min. | Тур. | Max. | Unit |

|------------------|--------------|------|------|------|------|

| SCLK frequency   | fsclk        |      |      | 16   | MHz  |

| SCLK pulse width | <b>t</b> spw | 31.3 |      |      | ns   |

| Delay time       | tols         | 15   |      |      | μs   |

### (4) COUT, MIRR and DFCT pins

### **Operating frequency**

$$(VDD = AVDD = 5.0V \pm 5\%, Vss = AVss = 0V, Topr = -20 to +75°C)$$

| Item                             | Symbol | Min. | Тур. | Max. | Unit | Conditions |

|----------------------------------|--------|------|------|------|------|------------|

| COUT maximum operating frequency | fсоит  | 40   |      |      | kHz  | *1         |

| MIRR maximum operating frequency | fmirr  | 40   |      |      | kHz  | *2         |

| DFCT maximum operating frequency | fdгстн | 5    |      |      | kHz  | *3         |

\*1 When using a high-speed traverse TZC.

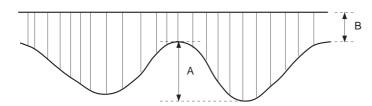

\*2

When the RF signal continuously satisfies the following conditions during the above traverse.

•

$$A = 0.12VDD$$

to  $0.26VDD$

•

$$\frac{B}{A+B} \le 25\%$$

\*3 During complete RF signal omission.

When settings related to DFCT signal generation are Typ.

### 1-bit DAC and LPF Block Analog Characteristics

Analog characteristics (VDD = AVDD = 5.0V, Vss = AVss = 0V, Ta = 25°C)

| Item            | Symbol | Conditions                 | Crystal | Min. | Тур.   | Max.   | Unit |

|-----------------|--------|----------------------------|---------|------|--------|--------|------|

| Total harmonic  | THD    | 1kHz, 0dB data             | 384Fs   |      | 0.0050 | 0.0070 | %    |

| distortion      | טווו   | TKTIZ, OUD data            | 768Fs   |      | 0.0045 | 0.0065 | 70   |

| Signal-to-noise | S/N    | 1kHz, 0dB data             | 384Fs   | 96   | 100    |        | dB   |

| ratio           | 3/14   | (Using A-weighting filter) | 768Fs   | 96   | 100    |        | ub   |

Fs = 44.1kHz in all cases.

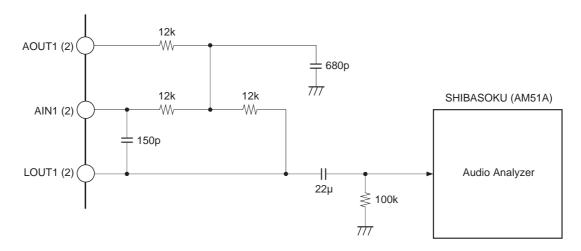

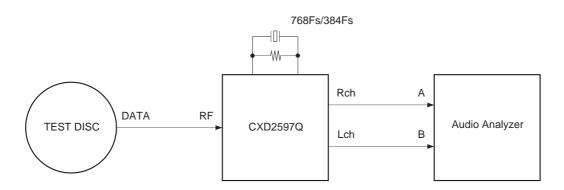

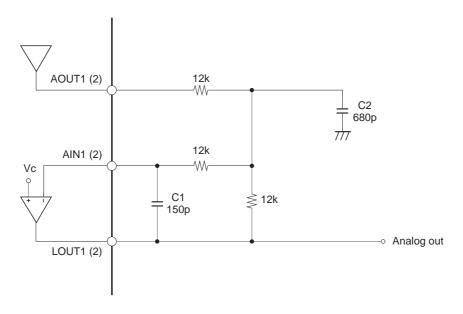

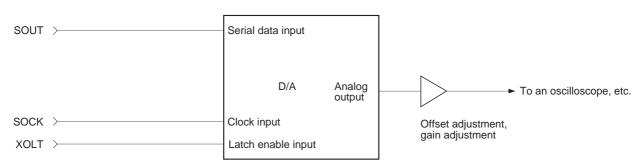

The total harmonic distortion and signal-to-noise ratio measurement circuits are shown below.

### LPF external circuit diagram

### Block diagram of analog characteristics measurement

$$(VDD = AVDD = 5.0V, Vss = AVss = 0V, Topr = -20 to +75°C)$$

| Item            | Symbol | Min. | Тур. | Max. | Unit | Applicable pins |

|-----------------|--------|------|------|------|------|-----------------|

| Output voltage  | Vouт   |      | 1.12 |      | Vrms | *1              |

| Load resistance | RL     | 8    |      |      | kΩ   | *1              |

<sup>\*</sup> Measurement is conducted for the LPF external circuit diagram with the sine wave output of 1kHz and 0dB.

### Applicable pins

<sup>\*1</sup> LOUT1, LOUT2

### Contents

| §1. CPU         | J Interface                                                       |     |

|-----------------|-------------------------------------------------------------------|-----|

| §1-1.           | CPU Interface Timing                                              | 13  |

| §1-2.           | CPU Interface Command Table                                       | 13  |

| §1-3.           | CPU Command Presets                                               |     |

| §1-4.           | Description of SENS Signals and Commands                          | 28  |

| §2. Sub         | code Interface                                                    |     |

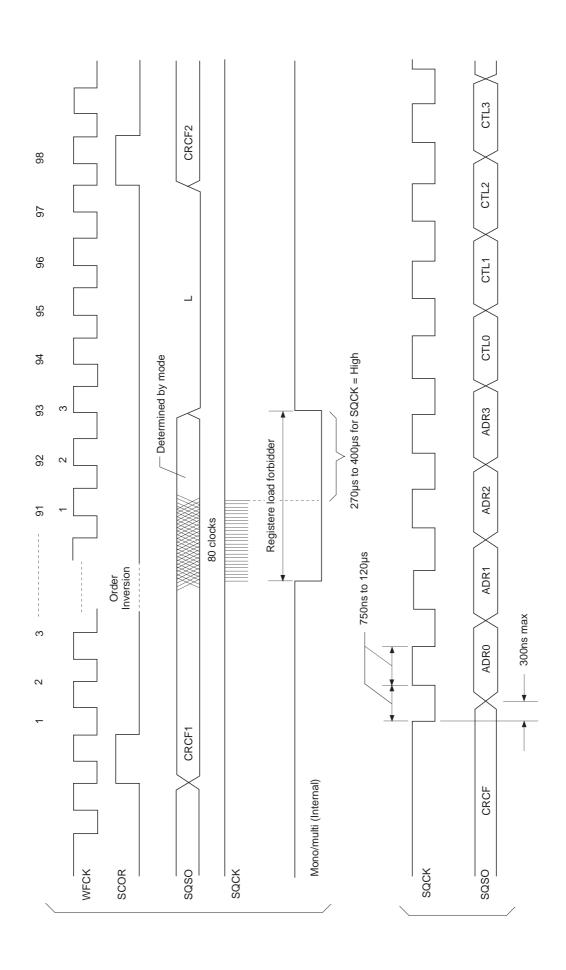

| §2-1.           | 80-bit Sub Q Readout                                              | 47  |

| §3. Des         | cription of Modes                                                 |     |

| §3-1.           | CLV-N Mode                                                        |     |

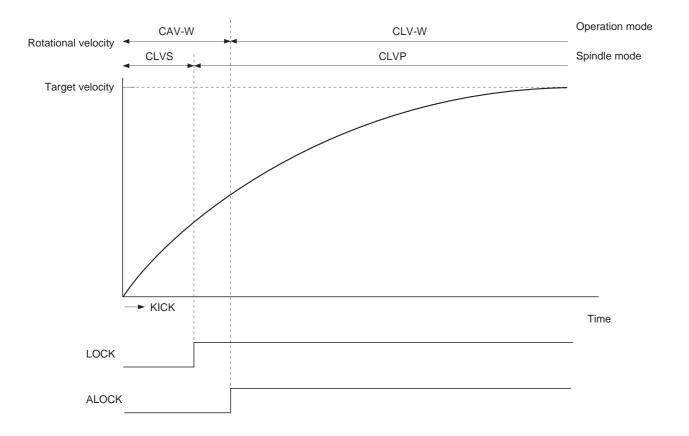

| §3-2.           | CLV-W Mode                                                        |     |

| §3-3.           | CAV-W Mode                                                        | 51  |

|                 | cription of Other Functions                                       |     |

| §4-1.           | Channel Clock Recovery by Digital PLL Circuit                     | 53  |

| §4-2.           | Frame Sync Protection                                             |     |

| §4-3.           | Error Correction                                                  |     |

| §4-4.           | DA Interface                                                      |     |

| §4-5.           | Digital Out                                                       |     |

| §4-6.           | Servo Auto Sequence                                               |     |

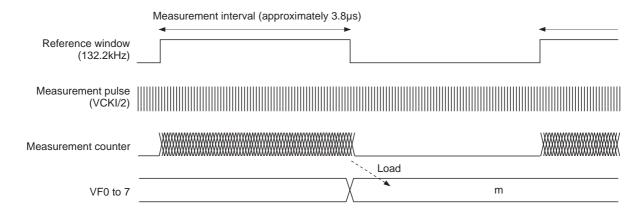

| §4-7.           | Digital CLV                                                       |     |

| §4-8.<br>§4-9.  | CD-DSP Block Playback Speed  DAC Block Playback Speed             |     |

| §4-9.<br>§4-10. |                                                                   |     |

|                 | LPF Block                                                         |     |

|                 | Asymmetry Correction                                              |     |

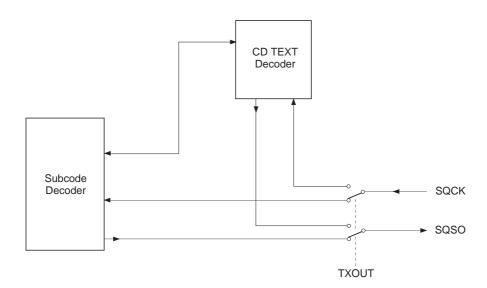

|                 | CD TEXT Data Demodulation                                         |     |

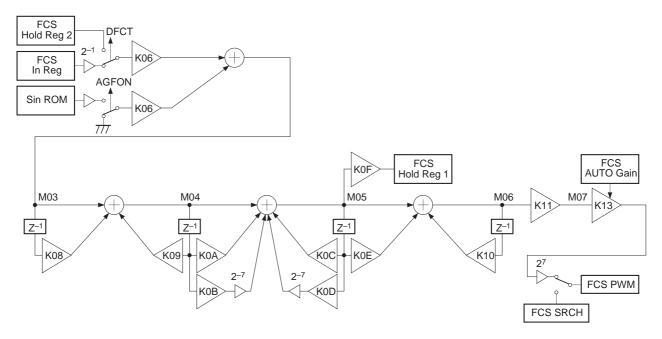

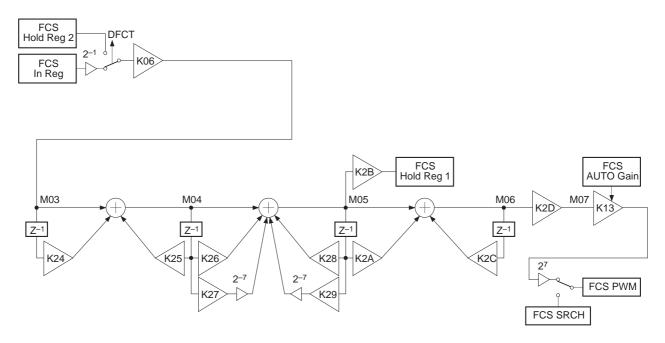

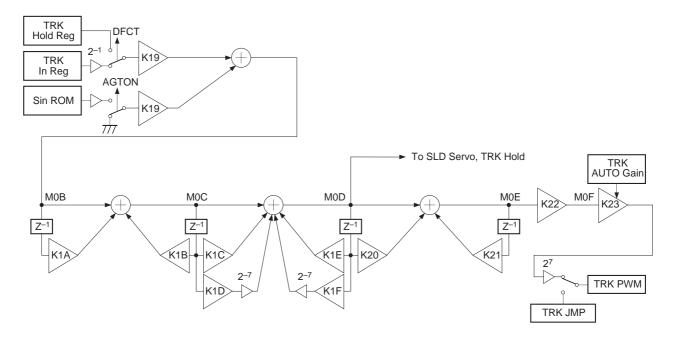

| 85 Desi         | cription of Servo Signal Processing System Functions and Commands |     |

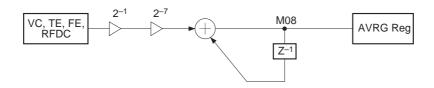

| §5-1.           | General Description of Servo Signal Processing System             | 74  |

| §5-2.           | Digital Servo Block Master Clock (MCK)                            |     |

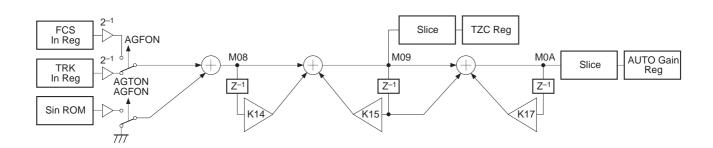

| §5-3.           | AVRG Measurement and Compensation                                 |     |

| §5-4.           | E:F Balance Adjustment Function                                   |     |

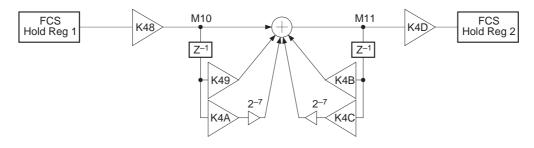

| §5-5.           | FCS Bias Adjustment Function                                      |     |

| §5-6.           | AGCNTL Function                                                   |     |

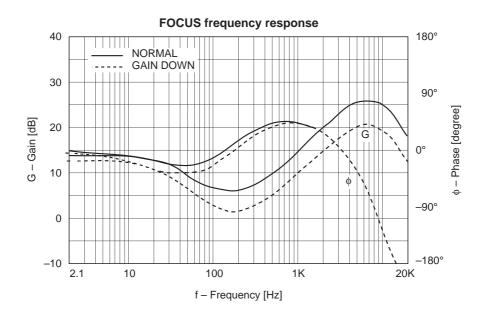

| §5-7.           | FCS Servo and FCS Search                                          | 81  |

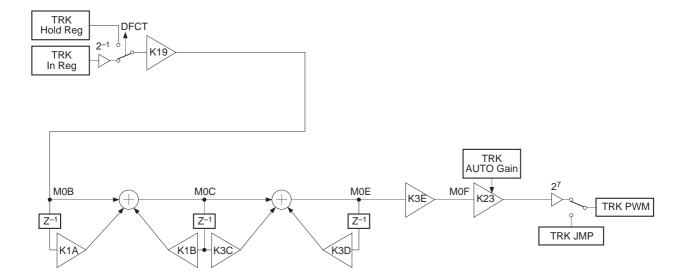

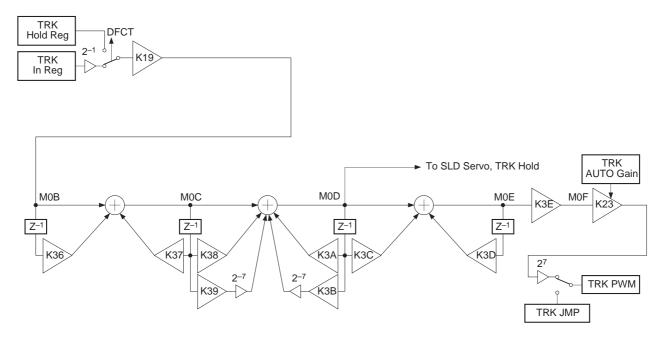

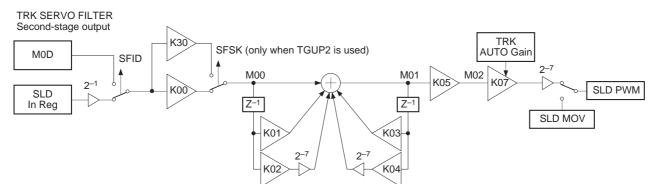

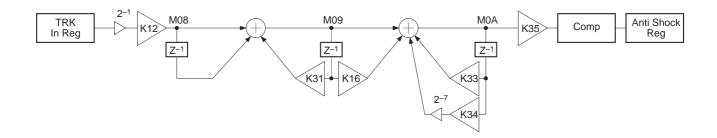

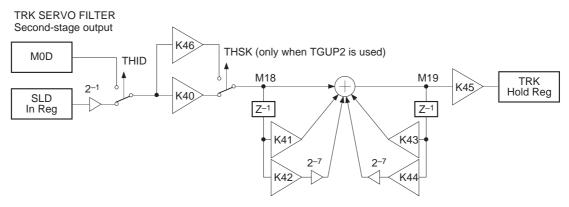

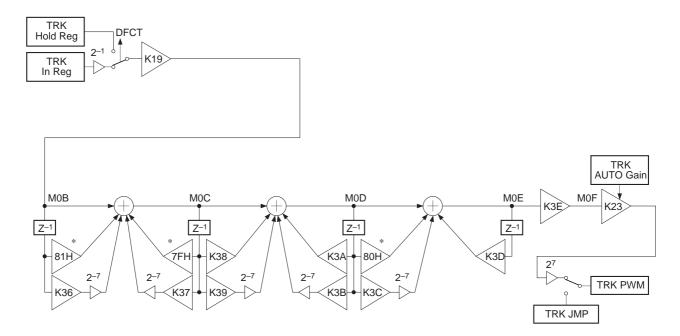

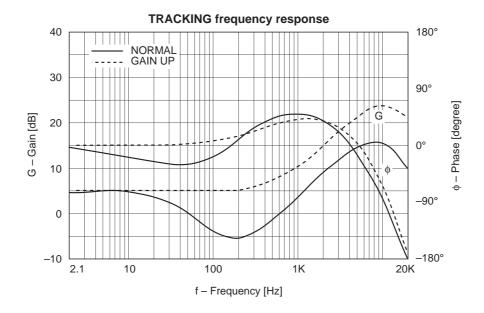

| §5-8.           | TRK and SLD Servo Control                                         | 82  |

| §5-9.           | MIRR and DFCT Signal Generation                                   | 83  |

|                 | DFCT Countermeasure Circuit                                       |     |

|                 | Anti-Shock Circuit                                                |     |

|                 | Brake Circuit                                                     |     |

|                 | COUT Signal                                                       |     |

|                 | Serial Readout Circuit                                            |     |

|                 | Writing to Coefficient RAM                                        |     |

|                 | PWM Output                                                        |     |

|                 | Servo Status Changes Produced by LOCK Signal                      |     |

|                 | Description of Commands and Data Sets                             |     |

|                 | List of Servo Filter Coefficients                                 |     |

|                 | Filter CompositionTRACKING and FOCUS Frequency Response           |     |

| 30-Z1.          | TRACKING and FOCOS Frequency Response                             | 113 |

| 86 Ann          | lication Circuit                                                  | 114 |

Explanation of abbreviations

AVRG: Average

AGCNTL: Auto gain control

FCS: Focus

TRK: Tracking

SLD: Sled

DFCT: Defect

### §1. CPU Interface

### §1-1. CPU Interface Timing

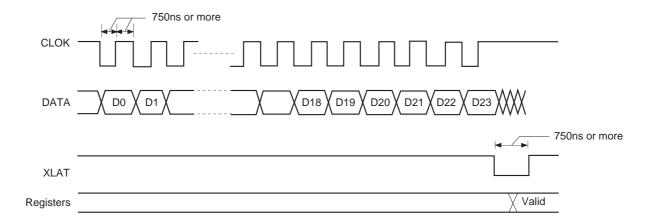

• CPU interface

This interface uses DATA, CLOK and XLAT to set the modes.

The interface timing chart is shown below.

• The internal registers are initialized by a reset when XRST = 0.

Note) Be sure to set SQCK to high when XLAT is low.

### §1-2. CPU Interface Command Table

Total bit length for each register

| Register | Total bit length |

|----------|------------------|

| 0 to 2   | 8 bits           |

| 3        | 8 to 24 bits     |

| 4 to 6   | 8 bits           |

| 7        | 20 bits          |

| 8        | 28 bits          |

| 9        | 24 bits          |

| А        | 28 bits          |

| В        | 16 bits          |

| С        | 8 bits           |

| D        | 16 bits          |

| Е        | 20 bits          |

Command Table (\$0X to 1X)

|           |            | FOCUS SERVO ON<br>(FOCUS GAIN<br>NORMAL) | FOCUS SERVO ON<br>(FOCUS GAIN<br>DOWN) | FOCUS SERVO OFF,<br>0V OUT | FOCUS SERVO OFF,<br>FOCUS SEARCH<br>VOLTAGE OUT | FOCUS SEARCH<br>VOLTAGE DOWN | FOCUS SEACH<br>VOLTAGE UP | ANTI SHOCK ON | ANTI SHOCK OFF | BRAKE ON | BRAKE OFF | TRACKING GAIN<br>NORMAL                                                                | TRACKING GAIN UP | TRACKING GAIN UP<br>FILTER SELECT 1 | TRACKING GAIN UP<br>FILTER SELECT 2 |

|-----------|------------|------------------------------------------|----------------------------------------|----------------------------|-------------------------------------------------|------------------------------|---------------------------|---------------|----------------|----------|-----------|----------------------------------------------------------------------------------------|------------------|-------------------------------------|-------------------------------------|

|           | 00         | I                                        | I                                      | I                          | I                                               | I                            | I                         | I             | I              | I        | I         | 1                                                                                      | I                | I                                   | I                                   |

| Data 5    | 5          | I                                        | I                                      | I                          | I                                               | I                            | I                         |               | I              | I        | I         | 1                                                                                      | I                | I                                   | I                                   |

| Dat       | D2         | I                                        | I                                      | I                          | I                                               | I                            | I                         |               | I              | I        | I         | 1                                                                                      | I                | I                                   | 1                                   |

|           | <u>D3</u>  | I                                        | I                                      | I                          | I                                               | I                            | I                         |               | I              | I        | I         | 1                                                                                      | I                | I                                   | I                                   |

|           | D4         | I                                        | I                                      | ı                          | I                                               | I                            | I                         | I             | I              | I        | I         | 1                                                                                      | I                | I                                   | I                                   |

| Data 4    | D2         | I                                        | I                                      | I                          | I                                               | I                            | I                         |               | I              | I        | I         |                                                                                        | I                | I                                   | I                                   |

| Dat       | 90         | I                                        | I                                      | I                          | I                                               | I                            | I                         |               | I              | I        | I         | 1                                                                                      | I                | I                                   | I                                   |

|           | D7         | I                                        | I                                      | I                          | I                                               | I                            | ı                         |               | I              | I        | I         | 1                                                                                      | I                | I                                   | I                                   |

|           | D8         | I                                        | I                                      | ı                          | I                                               | I                            | ı                         | I             | I              | I        | I         | 1                                                                                      | I                | I                                   | I                                   |

| a 3       | 60         | I                                        | I                                      | I                          | I                                               | ı                            | ı                         | ı             | I              | I        | ı         | 1                                                                                      | I                | I                                   | I                                   |

| Data 3    | D10        | I                                        | I                                      | ı                          | I                                               | I                            | ı                         |               | ı              | I        | I         | 1                                                                                      | I                | I                                   | I                                   |

|           | 111        | I                                        | I                                      | I                          | I                                               | ı                            | ı                         | ı             | I              | I        | ı         | 1                                                                                      | I                | I                                   | I                                   |

|           | D12        | I                                        | I                                      | ı                          | I                                               | I                            | ı                         | ı             | ı              | ı        | I         | 1                                                                                      | I                | I                                   | I                                   |

| Data 2    | D13        | I                                        | I                                      | I                          | I                                               | I                            | I                         |               | I              | I        | I         |                                                                                        | I                | I                                   | I                                   |

| Dat       | D14        | I                                        | I                                      | I                          | I                                               | I                            | ı                         | ı             | I              | I        | I         | 1                                                                                      | I                | I                                   | I                                   |

|           | D15        | I                                        | I                                      | I                          | I                                               | I                            | I                         |               | I              | I        | I         |                                                                                        | I                | I                                   | I                                   |

|           | D16        | I                                        | I                                      | I                          | I                                               | 0                            | -                         | ı             | I              | I        | I         | I                                                                                      | I                | -                                   | 0                                   |

| a<br>1    | D17        | I                                        | I                                      | 0                          | -                                               | -                            | -                         |               | I              | I        | I         | 0                                                                                      | -                | I                                   | I                                   |

| Data 1    | D18        | 0                                        | -                                      | I                          | I                                               | I                            | I                         | 0             | I              | ~        | 0         |                                                                                        | I                | I                                   | I                                   |

|           | D19        | ~                                        | ~                                      | 0                          | 0                                               | 0                            | 0                         | -             | 0              | I        | I         | I                                                                                      | I                | I                                   | I                                   |

| Address   | D23 to D20 |                                          |                                        | 0000                       |                                                 |                              |                           |               |                |          | 0         | -<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>- |                  |                                     |                                     |

| Pac and C |            |                                          |                                        | FOCUS                      |                                                 |                              |                           |               |                |          | TRACKING  | CONTROL                                                                                |                  |                                     |                                     |

| Dodistor  | nagisia.   |                                          |                                        | 0                          |                                                 |                              |                           |               |                |          | •         | <del>-</del>                                                                           |                  |                                     |                                     |

-: Don't care

Command Table (\$2X to 3X)

|         |            | ERVO OFF           | SERVO ON          | SACK JUMP          | ACK JUMP           | ) OFF          | NO C          | LED MOVE          | ED MOVE           |          |            | .EVEL<br>.e) (Default)                       | EVEL<br>alue)                         | EVEL<br>alue)                        | .EVEL           |

|---------|------------|--------------------|-------------------|--------------------|--------------------|----------------|---------------|-------------------|-------------------|----------|------------|----------------------------------------------|---------------------------------------|--------------------------------------|-----------------|

|         |            | TRACKING SERVO OFF | TRACKING SERVO ON | FORWARD TRACK JUMP | REVERSE TRACK JUMP | SLED SERVO OFF | SLED SERVO ON | FORWARD SLED MOVE | REVERSE SLED MOVE |          |            | SLED KICK LEVEL (±1 × basic value) (Default) | SLED KICK LEVEL<br>(±2 × basic value) | SLED KICK LEVEL (±3 × basic value)   | SLED KICK LEVEL |

|         | 00         | I                  | ı                 | ı                  | I                  | ı              | ı             | ı                 | ı                 |          | 8          | ı                                            | ı                                     | I                                    | I               |

| 3.5     | 70         | I                  | I                 | ı                  | I                  | I              | ı             | ı                 | I                 | 3.5      | 2          | I                                            | I                                     | I                                    | I               |

| Data 5  | D2         | I                  | I                 | ı                  | I                  | ı              | ı             | ı                 | ı                 | Data 5   | D2         | ı                                            | I                                     | I                                    | I               |

|         | D3         | I                  | I                 | ı                  | ı                  | ı              | ı             | ı                 | ı                 |          | D3         | ı                                            | I                                     | I                                    | I               |

|         | 7          | I                  | I                 | ı                  | I                  | ı              | ı             | ı                 | ı                 |          | D4         | ı                                            | I                                     | I                                    | ı               |

| a 4     | DS         | I                  | I                 | ı                  | I                  | I              | ı             | ı                 | ı                 | a 4      | D2         | ı                                            | I                                     | I                                    | ı               |

| Data 4  | 90         | I                  | I                 | ı                  | I                  | ı              | ı             | ı                 | ı                 | Data 4   | 90         | ı                                            | I                                     | I                                    | ı               |

|         | D7         | I                  | I                 | ı                  | I                  | I              | ı             | ı                 | ı                 |          | 70         | ı                                            | I                                     | I                                    | ı               |

|         | B0         | I                  | I                 | I                  | I                  | I              | ı             | ı                 | I                 |          | 80         | ı                                            | I                                     | I                                    | ı               |

| 33      | 60         | I                  | I                 | ı                  | ı                  | ı              | ı             | ı                 | ı                 | a 3      | 60         | ı                                            | I                                     | I                                    | ı               |

| Data 3  | D10        | I                  | I                 | ı                  | I                  | ı              | ı             | ı                 | ı                 | Data 3   | D10        | ı                                            | I                                     | I                                    | ı               |

|         | D11        |                    | I                 | ı                  | I                  | ı              | ı             | ı                 | ı                 |          | 110        | ı                                            | I                                     | I                                    | ı               |

|         | D12        | I                  | I                 | I                  | I                  | I              | I             | I                 | I                 |          | D12        | I                                            | I                                     | I                                    | ı               |

| Data 2  | D13        | I                  | I                 | I                  | I                  | I              | ı             | I                 | I                 | Data 2   | D13        | I                                            | I                                     | I                                    | I               |

| Dat     | D14        | I                  | I                 | ı                  | I                  | I              | ı             | ı                 | I                 | Dat      | D14        | ı                                            | I                                     | I                                    | ı               |

|         | D15        | I                  | I                 | ı                  | I                  | I              | ı             | ı                 | I                 |          | D15        | ı                                            | I                                     | I                                    | I               |

|         | D16        | I                  | I                 | I                  | I                  | 0              | -             | 0                 | -                 | Data 1   | D16        | 0                                            | -                                     | 0                                    | -               |

| Data 1  | D17        | I                  | I                 | ı                  | I                  | 0              | 0             | -                 | -                 | Dai      | D17        | 0                                            | 0                                     | -                                    | _               |

| Dat     | D18        | 0                  | -                 | 0                  | -                  | I              | I             | ı                 | I                 |          | D18        | 0                                            | 0                                     | 0                                    | c               |

|         | D19        | 0                  | 0                 | -                  | -                  | I              | ı             | ı                 | I                 | Address  | D19        | 0                                            | 0                                     | 0                                    | c               |

| Address | D23 to D20 |                    |                   |                    | 0                  | 0              |               |                   |                   | Addi     | D23 to D20 |                                              | 0                                     | -<br>-<br>-<br>-<br>-<br>-<br>-<br>- |                 |

|         | Command    |                    |                   |                    | TRACKING           | MODE           |               |                   |                   | Common   |            |                                              | E C                                   |                                      |                 |

| 100     | Kegister   |                    |                   |                    | c                  | ٧              |               |                   |                   | Dogistor | i pigliga  |                                              | c                                     | n                                    |                 |

-: Don't care

# Command Table (\$340X)

|             |            | KRAM DATA (K00)<br>SLED INPUT GAIN | KRAM DATA (K01)<br>SLED LOW BOOST FILTER A-H | KRAM DATA (K02)<br>SLED LOW BOOST FILTER A-L | KRAM DATA (K03)<br>SLED LOW BOOST FILTER B-H | KRAM DATA (K04)<br>SLED LOW BOOST FILTER B-L | KRAM DATA (K05)<br>SLED OUTPUT GAIN | KRAM DATA (K06)<br>FOCUS INPUT GAIN | KRAM DATA (K07)<br>SLED AUTO GAIN | KRAM DATA (K08)<br>FOCUS HIGH CUT FILTER A | KRAM DATA (K09)<br>FOCUS HIGH CUT FILTER B | KRAM DATA (K0A)<br>FOCUS LOW BOOST FILTER A-H | KRAM DATA (K0B)<br>FOCUS LOW BOOST FILTER A-L | KRAM DATA (K0C)<br>FOCUS LOW BOOST FILTER B-H | KRAM DATA (K0D)<br>FOCUS LOW BOOST FILTER B-L | KRAM DATA (K0E)<br>FOCUS PHASE COMPENSATE FILTER A | KRAM DATA (K0F)<br>FOCUS DEFECT HOLD GAIN |

|-------------|------------|------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|-------------------------------------|-------------------------------------|-----------------------------------|--------------------------------------------|--------------------------------------------|-----------------------------------------------|-----------------------------------------------|-----------------------------------------------|-----------------------------------------------|----------------------------------------------------|-------------------------------------------|

|             | D0         | KD0                                | KD0                                          | KD0                                          | KD0                                          | KD0                                          | KD0                                 | KD0                                 | KD0                               | KD0                                        | KD0                                        | KD0                                           | KD0                                           | KD0                                           | KD0                                           | KD0                                                | KD0                                       |

| Data 2      | 5          | KD 4                               | ξQ.                                          | KD 4                                         | KD 4                                         | ð                                            | δ                                   | Ą                                   | ξQ.                               | δ                                          | KD 4                                       | δ                                             | ξ<br>Σ                                        | KD1                                           | KD1                                           | ξ<br>Σ                                             | KD1                                       |

| Da          | D2         | KD2                                | KD2                                          | KD2                                          | KD2                                          | KD2                                          | KD2                                 | KD2                                 | KD2                               | KD2                                        | KD2                                        | KD2                                           | KD2                                           | KD2                                           | KD2                                           | KD2                                                | KD2                                       |

|             | D3         | KD3                                | KD3                                          | KD3                                          | KD3                                          | KD3                                          | KD3                                 | KD3                                 | KD3                               | KD3                                        | KD3                                        | KD3                                           | KD3                                           | KD3                                           | KD3                                           | KD3                                                | КДЗ                                       |

|             | D4         | KD4                                | KD4                                          | KD4                                          | KD4                                          | KD4                                          | KD4                                 | KD4                                 | KD4                               | KD4                                        | KD4                                        | KD4                                           | KD4                                           | KD4                                           | KD4                                           | KD4                                                | KD4                                       |

| a 1         | D2         | KD5                                | KD5                                          | KD5                                          | KD5                                          | KD5                                          | KD5                                 | KD5                                 | KD5                               | KD5                                        | KD5                                        | KD5                                           | KD5                                           | KD5                                           | KD5                                           | KD5                                                | KD5                                       |

| Data 1      | 90         | KD6                                | KD6                                          | KD6                                          | KD6                                          | KD6                                          | KD6                                 | KD6                                 | KD6                               | KD6                                        | KD6                                        | KD6                                           | KD6                                           | KD6                                           | KD6                                           | KD6                                                | KD6                                       |

|             | 70         | KD7                                | KD7                                          | KD7                                          | KD7                                          | KD7                                          | KD7                                 | KD7                                 | KD7                               | KD7                                        | KD7                                        | KD7                                           | KD7                                           | KD7                                           | KD7                                           | KD7                                                | KD7                                       |

|             | D8         | 0                                  | -                                            | 0                                            | -                                            | 0                                            | -                                   | 0                                   | -                                 | 0                                          | -                                          | 0                                             | -                                             | 0                                             | -                                             | 0                                                  | -                                         |

| ss 4        | 60         | 0                                  | 0                                            | -                                            | -                                            | 0                                            | 0                                   | -                                   | -                                 | 0                                          | 0                                          | -                                             | -                                             | 0                                             | 0                                             | -                                                  | -                                         |

| Address 4   | D10        | 0                                  | 0                                            | 0                                            | 0                                            | -                                            | -                                   | -                                   | -                                 | 0                                          | 0                                          | 0                                             | 0                                             | -                                             | -                                             | -                                                  | -                                         |

|             | 111        | 0                                  | 0                                            | 0                                            | 0                                            | 0                                            | 0                                   | 0                                   | 0                                 | -                                          | -                                          | -                                             | -                                             | -                                             | -                                             | -                                                  | -                                         |

| Address 3   | D15 to D12 |                                    |                                              |                                              |                                              |                                              |                                     |                                     | 0                                 |                                            |                                            |                                               | •                                             |                                               |                                               |                                                    |                                           |

| Address 2   | D19 to D16 |                                    |                                              |                                              |                                              |                                              |                                     |                                     | 2                                 | )<br>-<br>-                                |                                            |                                               |                                               |                                               |                                               |                                                    |                                           |

| Address 1   | D23 to D20 | 0 0 0 1                            |                                              |                                              |                                              |                                              |                                     |                                     |                                   |                                            |                                            |                                               |                                               |                                               |                                               |                                                    |                                           |

| 7000        |            | SELECT                             |                                              |                                              |                                              |                                              |                                     |                                     |                                   |                                            |                                            |                                               |                                               |                                               |                                               |                                                    |                                           |

| - Consistor | negister   |                                    |                                              |                                              |                                              |                                              |                                     |                                     | c                                 | n                                          |                                            |                                               |                                               |                                               |                                               |                                                    |                                           |

# Command Table (\$341X)

|                                          |                                          | i                                                  |                                      |                                          |                                    | i .                                                     |                                                         |                                                  |                                                        |                                                                                   |                                        | <del></del>                                   |                                               |                                                  | i                                                |                                                  |                                                  |

|------------------------------------------|------------------------------------------|----------------------------------------------------|--------------------------------------|------------------------------------------|------------------------------------|---------------------------------------------------------|---------------------------------------------------------|--------------------------------------------------|--------------------------------------------------------|-----------------------------------------------------------------------------------|----------------------------------------|-----------------------------------------------|-----------------------------------------------|--------------------------------------------------|--------------------------------------------------|--------------------------------------------------|--------------------------------------------------|

|                                          |                                          | KRAM DATA (K10)<br>FOCUS PHASE COMPENSATE FILTER B | KRAM DATA (K11)<br>FOCUS OUTPUT GAIN | KRAM DATA (K12)<br>ANTI SHOCK INPUT GAIN | KRAM DATA (K13)<br>FOCUS AUTO GAIN | KRAM DATA (K14)<br>HPTZC / AUTO GAIN HIGH PASS FILTER A | KRAM DATA (K15)<br>HPTZC / AUTO GAIN HIGH PASS FILTER B | KRAM DATA (K16)<br>ANTI SHOCK HIGH PASS FILTER A | KRAM DATA (K17)<br>HPTZC / AUTO GAIN LOW PASS FILTER B | KRAM DATA (K18)<br>FIX                                                            | KRAM DATA (K19)<br>TRACKING INPUT GAIN | KRAM DATA (K1A)<br>TRACKING HIGH CUT FILTER A | KRAM DATA (K1B)<br>TRACKING HIGH CUT FILTER B | KRAM DATA (K1C)<br>TRACKING LOW BOOST FILTER A-H | KRAM DATA (K1D)<br>TRACKING LOW BOOST FILTER A-L | KRAM DATA (K1E)<br>TRACKING LOW BOOST FILTER B-H | KRAM DATA (K1F)<br>TRACKING LOW BOOST FILTER B-L |

|                                          | 00                                       | KD0                                                | KD0                                  | KD0                                      | KD0                                | KD0                                                     | KD0                                                     | KD0                                              | KD0                                                    | KD0                                                                               | KD0                                    | KD0                                           | KD0                                           | KD0                                              | KD0                                              | KD0                                              | KD0                                              |

| Data 2                                   | 5                                        | KD1                                                | KD1                                  | KD1                                      | KD1                                | KD1                                                     | KD1                                                     | KD1                                              | KD1                                                    | KD1                                                                               | KD1                                    | KD1                                           | KD1                                           | KD1                                              | KD1                                              | KD1                                              | KD1                                              |

| Dat                                      | D2                                       | KD2                                                | KD2                                  | KD2                                      | KD2                                | KD2                                                     | KD2                                                     | KD2                                              | KD2                                                    | KD2                                                                               | KD2                                    | KD2                                           | KD2                                           | KD2                                              | KD2                                              | KD2                                              | KD2                                              |

|                                          | D3                                       | KD3                                                | KD3                                  | KD3                                      | KD3                                | KD3                                                     | KD3                                                     | KD3                                              | KD3                                                    | KD3                                                                               | KD3                                    | KD3                                           | KD3                                           | KD3                                              | KD3                                              | KD3                                              | KD3                                              |

|                                          | 7                                        | KD4                                                | KD4                                  | KD4                                      | KD4                                | KD4                                                     | KD4                                                     | KD4                                              | KD4                                                    | KD4                                                                               | KD4                                    | KD4                                           | KD4                                           | KD4                                              | KD4                                              | KD4                                              | KD4                                              |

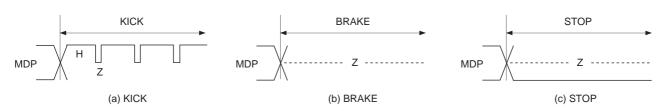

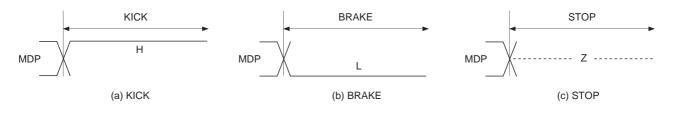

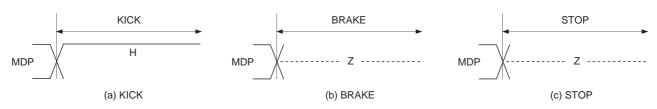

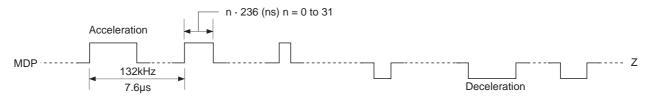

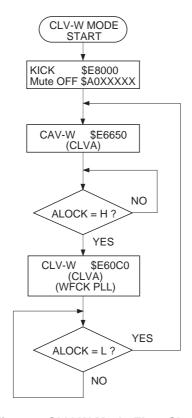

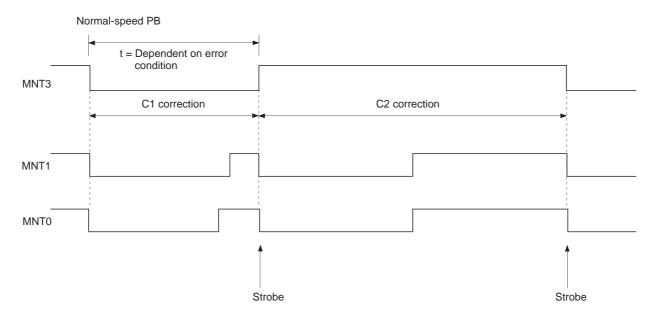

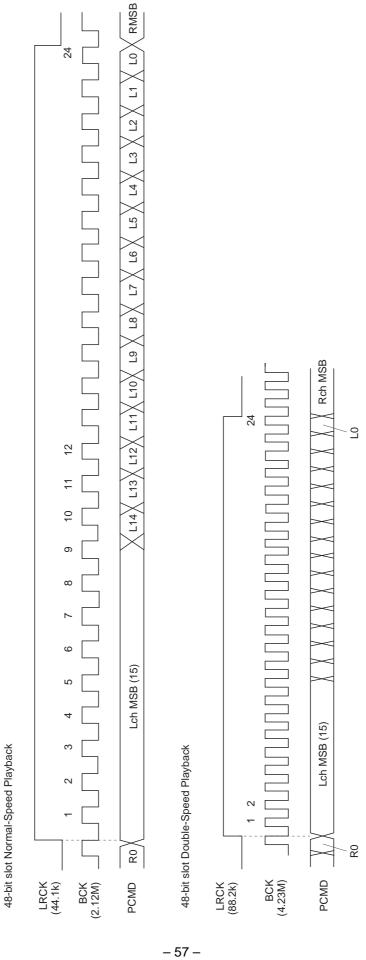

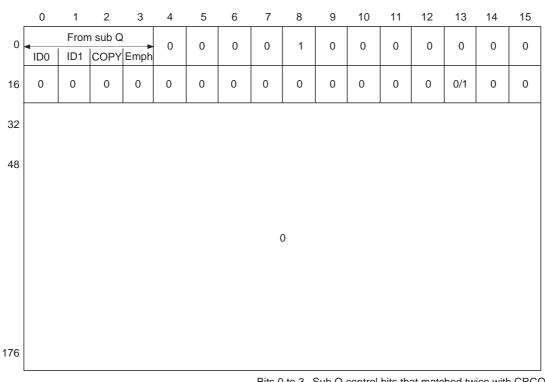

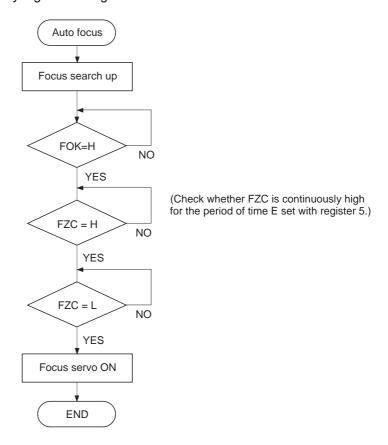

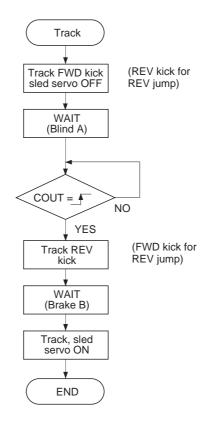

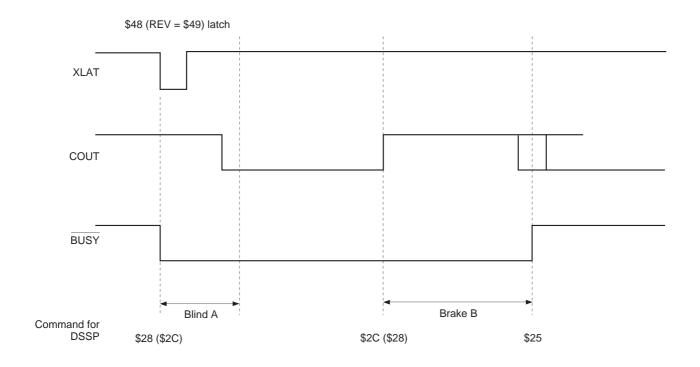

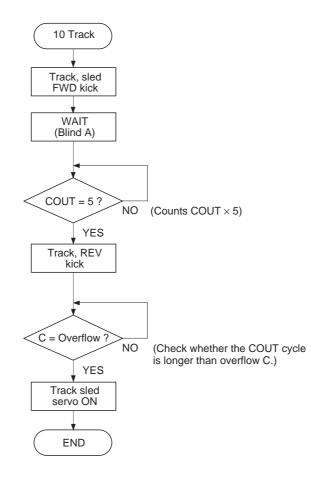

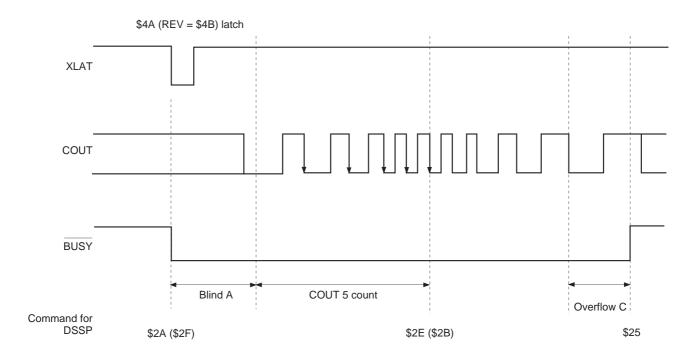

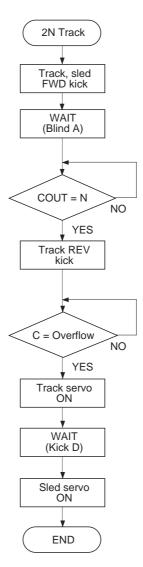

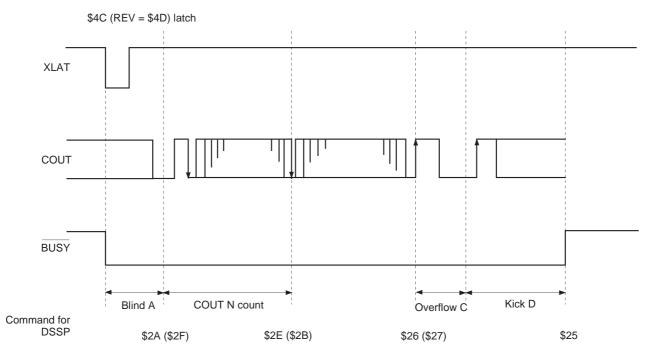

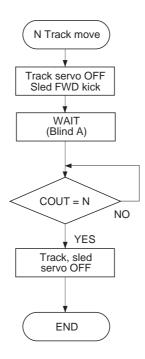

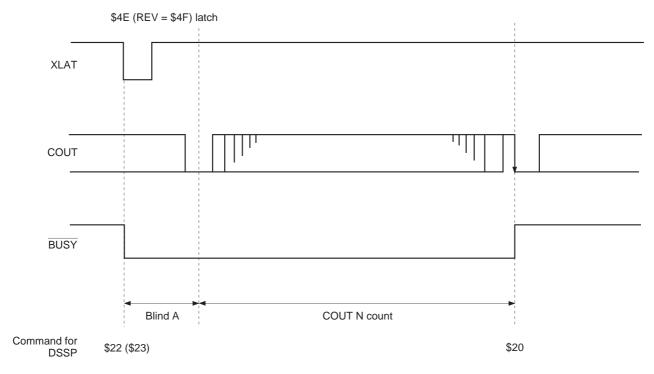

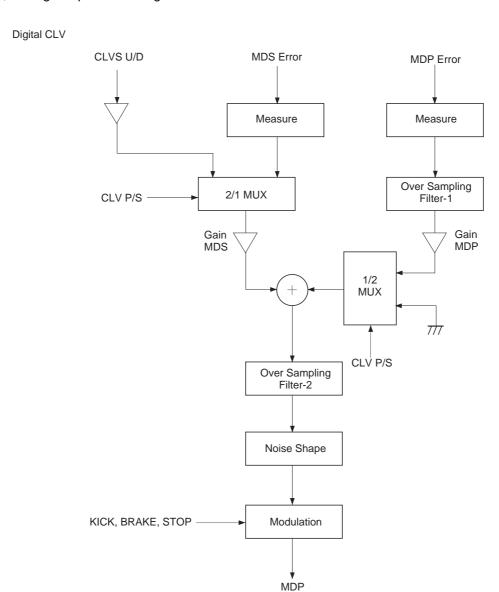

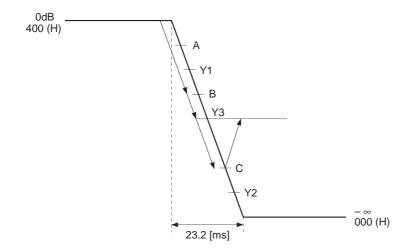

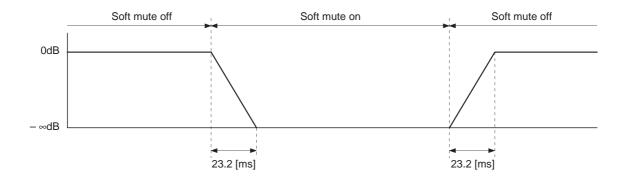

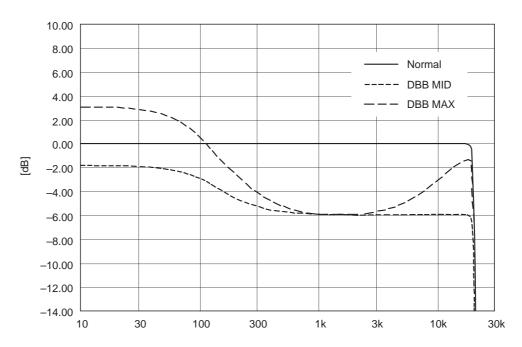

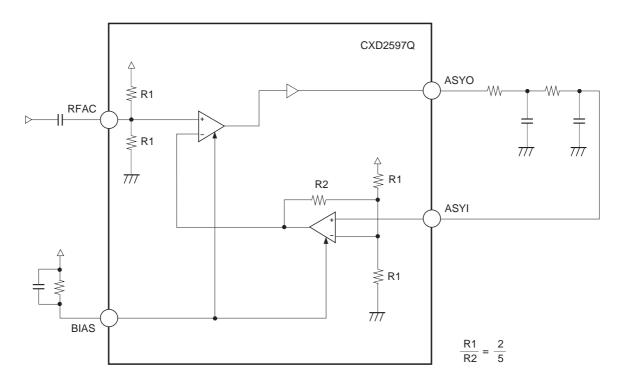

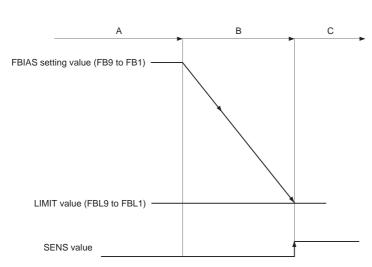

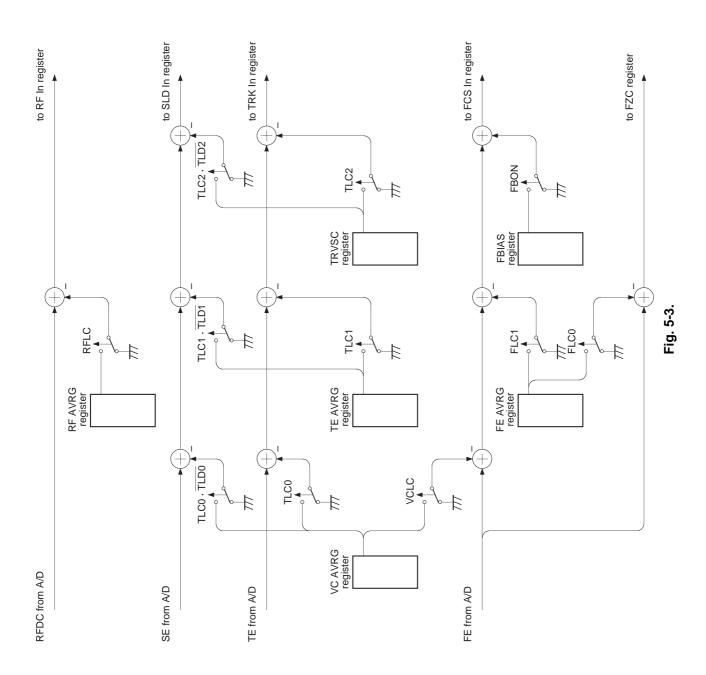

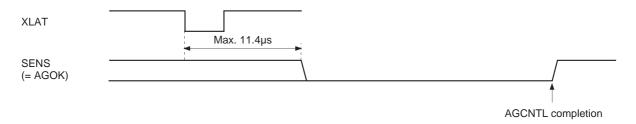

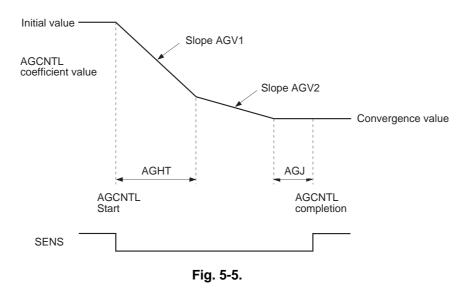

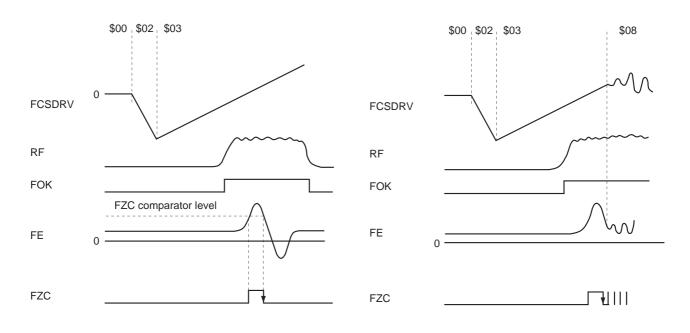

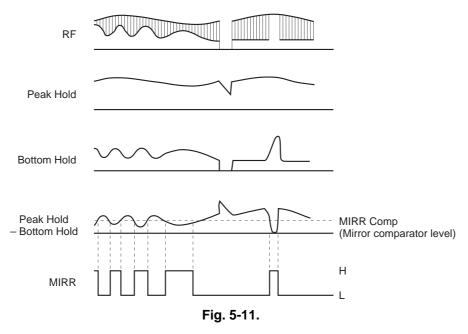

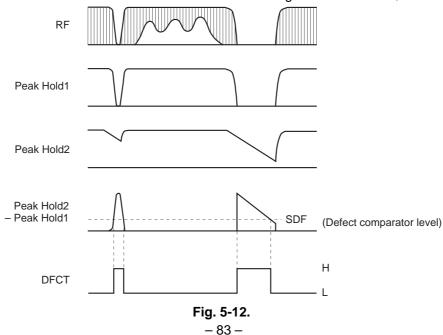

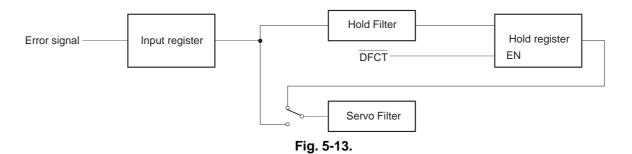

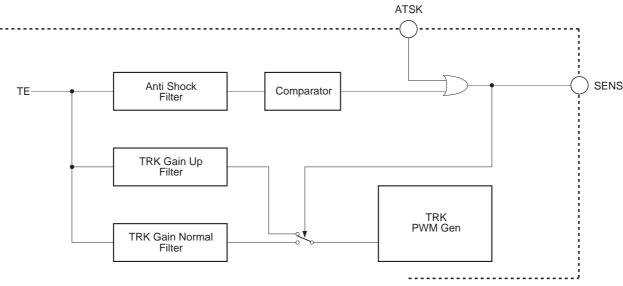

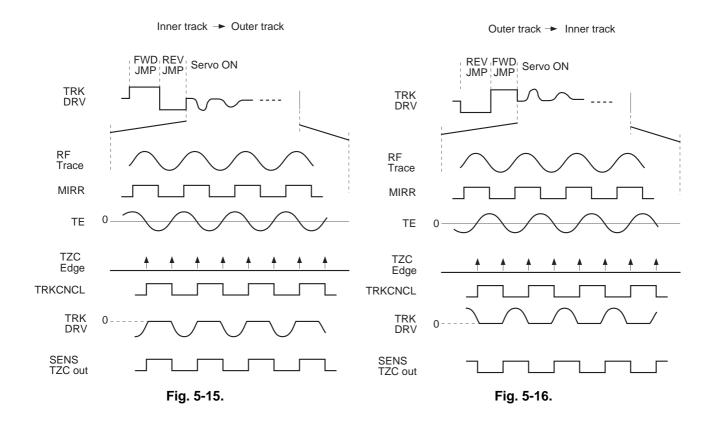

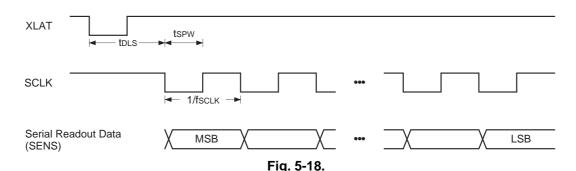

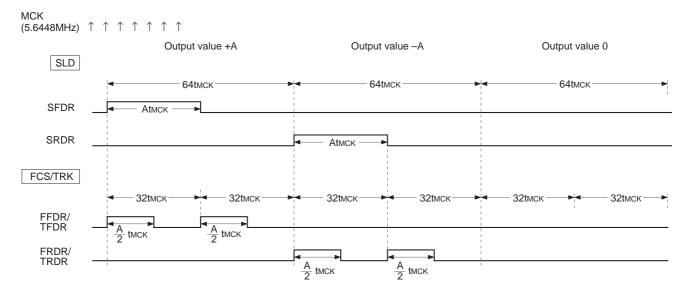

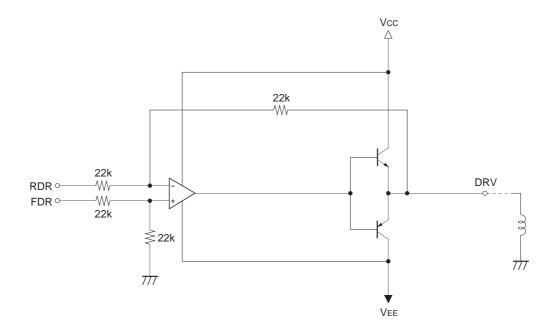

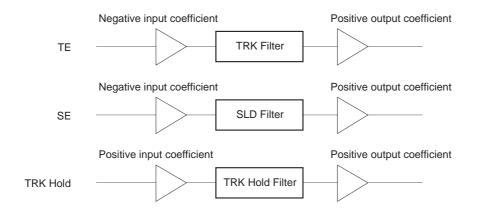

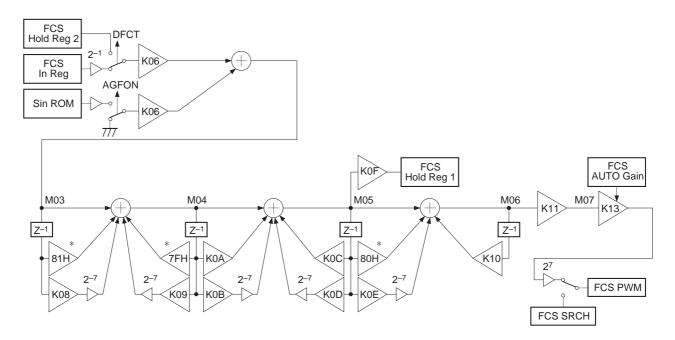

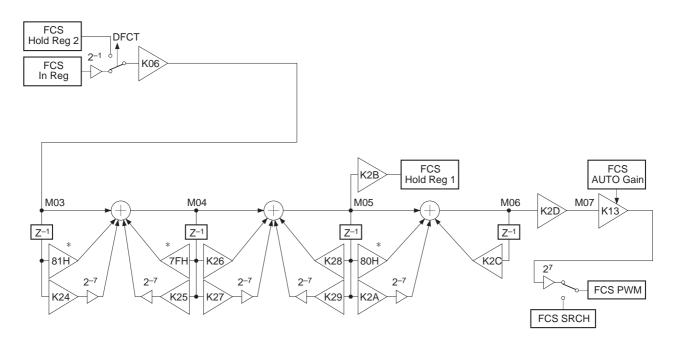

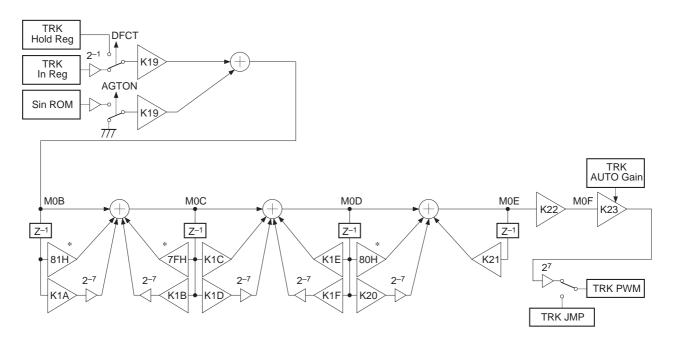

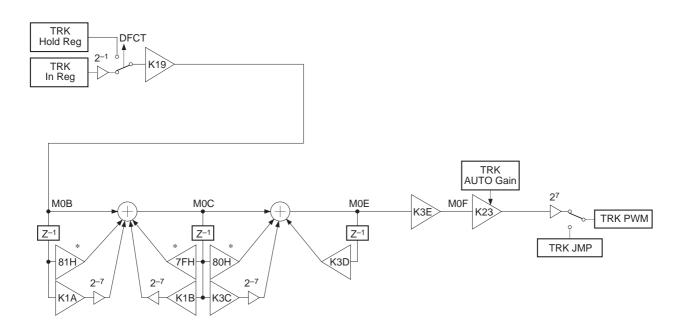

| E                                        | D2                                       | KD5                                                | KD5                                  | KD5                                      | KD5                                | KD5                                                     | KD5                                                     | KD5                                              | KD5                                                    | KD5                                                                               | KD5                                    | KD5                                           | KD5                                           | KD5                                              | KD5                                              | KD5                                              | KD5                                              |