- Inputs are TTL- and CMOS-Voltage Compatible

- Interfaces Mechanical Devices to Data Bus

- Identifies and Measures Forward or Backward Rotation or Direction

- Measures Pulse Duration and Frequency

- Cascadable 16-Bit Up/Down Counter

- 8-Bit Parallel 3-State Bus with Each Output Capable of Driving up to 15 LSTTL Loads

- Dependable Texas Instruments Quality and Reliability

## description

The THCT2000 direction discriminator can determine the direction and displacement of a mechanical device based on input signals from two transducers in quadrature. It can also measure a pulse duration using a known clock rate, or a frequency over a known time interval. It includes a 16-bit counter, which can be used separately. Several of these devices may be cascaded to provide accuracy greater than 16-bits.

The device may be used in many diverse applications, and is specifically designed for use in many types of microprocessor-based systems. Some of the possibilities include motor controls, robotics, tracker balls (mice), lathe or tooling machines, automobiles, and conveyer belts or other transport mechanisms.

The THCT2000M is characterized for operation over the full military temperature range of  $-55\,^{\circ}\text{C}$  to 125 $\,^{\circ}\text{C}$ . The THCT2000E is characterized for operation from  $-40\,^{\circ}\text{C}$  to 85 $\,^{\circ}\text{C}$ .

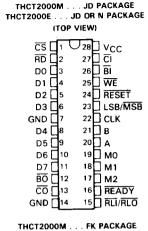

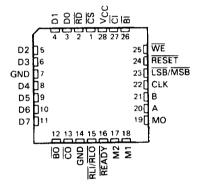

THCT2000M . . . FK PACKAGE

THCT2000E . . . FN PACKAGE

(TOP VIEW)

POST OFFICE BOX 225012 . DALLAS, TEXAS 75265

2

†This symbol is in accordance with ANSI/IEEE Std 91-1984.

## functional block diagram

M0 M1 M2 ÇI · <u>co</u> MEASUREMENT 16-BIT COUNTER LOGIC 12 BO CLOCK -16-BIT REGISTER RESET -DMUX 16-TO-8 MUX cs. CONTROL BUFFER  $\overline{RD}$ LOGIC WE -READY LSB/MSB RLI/RLO -

LSI Devices

| PIN        |              | DESCRIPTION                                                                                                   |

|------------|--------------|---------------------------------------------------------------------------------------------------------------|

| NAME       | NUMBER       |                                                                                                               |

| A, B       | 20, 21       | Signal measurement inputs.                                                                                    |

| Bī         | 26           | Cascade input for counting down. In mode 0, BI is used as the clock input for counting down.                  |

|            |              | Triggering occurs on the high-to-low transition.                                                              |

| 80         | 12           | Counter output underflow signal. Active (low) for a duration equal to the low level of the input clock.       |

| CI         | 27           | Cascade input for counting up. In mode 0, Cl is used as the clock input for counting up. Triggering           |

|            |              | occurs on the high-to-low transition.                                                                         |

| CLK        | 22           | Clock input. Used for internal synchronization and control timing.                                            |

| co         | 13           | Counter output overflow signal. Active (low) for a duration equal to the low level of the input clock.        |

| CS         | 1            | Chip select input. This active-low input is used to enable read and write functions. For additional           |

|            |              | details, see read and write timing diagrams.                                                                  |

| D0-D7      | 3, 4, 5, 6,  | Counter load inputs/register output data lines.                                                               |

|            | 8, 9, 10, 11 |                                                                                                               |

| GND        | 7, 14        | Pins 7 and 14 are both internally connected to the ground rail of the integrated circuit but both should      |

|            |              | be connected to the system ground for proper operation.                                                       |

| LSB/MSB    | 23           | Byte select input. During read operations, a high level selects the least significant byte, while a low       |

| İ          |              | level selects the most significant byte. For write operations, this input directs the data on the bus         |

|            |              | into the least significant or most significant byte position of the counter. See write timing diagrams        |

|            |              | for additional details.                                                                                       |

| M0, M1, M2 | 19, 18, 17   | Mode select inputs.                                                                                           |

| RD         | 2            | Read input. When active (low) in conjunction with CS low, the data stored in the output register will         |

|            |              | be present on the data bus as selected by the LSB/MSB input. See read timing diagrams for additional          |

| Į          | _            | details.                                                                                                      |

| READY      | 16           | Ready output. When active (low), this output indicates to the processor that it may complete the read         |

|            |              | or write operation. READY is synchronous with the negative-going edge of CLK. This output requires            |

| ì          |              | a pullup resistor (1 kΩ nominal).                                                                             |

| RESET      | 24           | Counter and control logic reset. When active (low), the counter is asynchronously reset to zero while         |

| 1          |              | the control logic is asynchronously initialized to the proper state as determined by the mode control         |

|            |              | inputs. The output register is not affected by RESET.                                                         |

| RLI/RLO    | 15           | Register load input/register load output (open drain). This pin can be used as an input to directly load      |

| 1          |              | the output register, or it can be used as an output to detect whenever the output register has been           |

|            |              | loaded. When used as an output, a pullup resistor (1 $k\Omega$ nominal) is required. See read timing diagrams |

|            |              | for additional details.                                                                                       |

| Vcc        | 28           | Power supply voltage.                                                                                         |

| WE         | 25           | Write enable input. When active (low) in conjunction with CS low, the data present on D0-D7 will be           |

|            |              | asynchronously loaded into the counter as selected by LSB/MSB. See write timing diagrams for                  |

|            |              | additional details.                                                                                           |