TOSHIBA BIPOLAR DIGITAL INTEGRATED CIRCUIT SILICON MONOLITHIC

# T D 6 2 4 4 5 F N

## LOW-SATURATION-TYPE SINK DRIVER WITH 4-CIRCUIT OVER-CURRENT **DETECTION FUNCTION**

The TD62445FN is a sink driver with over-current detector circuits. Each of four circuits can setting the limit current. Using an internal comparator, the TD62445FN detects over-current by comparing the current output through the external resistors as voltage. Over current detection is detected by the ERR terminal which is an open collector, comes on.

Construct a system so that the input signal turns off immediately the ERR pin comes on.

Weight: 0.08g (Typ.)

### **FEATURES**

Includes current limiter circuits:

By connecting external resistors, each bit can be set to any limit current value.

• Includes an error detection signal filter pin:

Connecting any capacitor between the LP pin and the GND filters the internal comparator detection signal and outputs this to the ERR pin.

Over-current monitor detection output:

Includes an ERR pin output to warn when current exceeds the limit. Construct a system so that the input signal turns off immediately the ERR pin comes on (open collector).

Common input pin (CO-IN (pin 4)):

Using this pin, the four over-current detector circuits can be forcibly turned off together.

Low-saturation-type output (open collector):

The voltage drop between the collector and emitter is  $V_{Ol,1} = 0.4V$  (max.) @  $I_{O} = 100$ mA.

Supply voltage :  $V_{CC} = 4.5$  to 5.5

Input is TTL compatible.

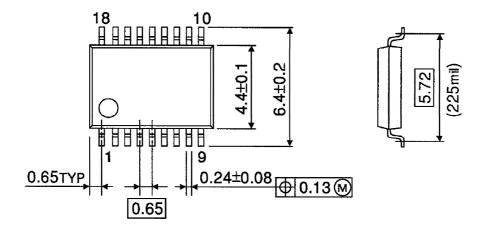

Ultra-compact package: VSOP 18 pins (0.65mm pitch) Output rating :  $V_{CEO} = 30V$ ,  $I_{O} = 150 \text{mA/ch}$ Packing : Embossed taping only

■ TOSHIBA is continually working to improve the quality and the reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to observe standards of safety, and to avoid situations in which a malfunction or failure of a TOSHIBA product could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent products specifications. Also, please keep in mind the precautions and conditions set forth in the TOSHIBA Semiconductor Reliability Handbook.

The products described in this document are subject to foreign exchange and foreign trade control laws.

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

The information contained herein is subject to change without notice.

The information contained herein is subject to change without notice.

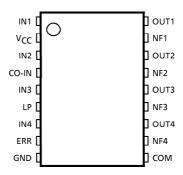

### PIN CONNECTION (Top View)

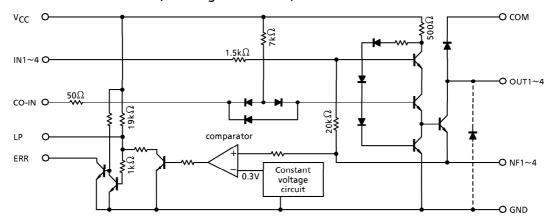

### **EQUIVALENT CIRCUIT DIAGRAM** (Showing One Circuit)

- When the output pins of this IC are connected to the load power supply, over-current may

flow to the outputs. While the device includes an over-current detection function, the device

is not designed for applications where the output pins and load power supply are

intentionally connected.

- Be sure to use the device with the NF1 to 4 and the GND pins connected via resistors or directly connected. Do not use with the NF1 to 4 pins open.

This also applies to unused channels. If the pins are not connected, the operation of the over-current detection function is unstable.

Note that if the NF1 to 4 and GND pins are directly connected, the over-current detection function does not operate.

- A parasitic diode is installed between the GND and output pins. While current is supplied to this diode, other circuit outputs may come on or be otherwise affected. If this phenomenon adversely affects the operation of the device, Toshiba recommends connecting an external diode.

### TRUTH TABLE

| IN1~4 | CO-IN | OUT1~4 | VOLTAGE BETWEEN<br>NF1 TO 4 AND GND | ERR |

|-------|-------|--------|-------------------------------------|-----|

| L     | Н     | OFF    | 0V                                  | OFF |

| Н     | Н     | ON     | 0.3V max                            | OFF |

| Н     | Н     | ON     | 0.3V min                            | ON  |

| Х     | L     | OFF    | 0V                                  | OFF |

(Note) The above comparator circuit assumes some resistance connected between the NF1 to 4 and GND pins when the circuit operates.

### **PIN DESCRIPTION**

| PIN No.        | PIN NAME        | FUNCTION                                                                                                                                                                     |

|----------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 3, 5, 7     | IN1 to 4        | Driver input pins. TTL compatible input level. At high level the output is on; at low level the output is off.                                                               |

| 2              | V <sub>CC</sub> | Power supply voltage pin.                                                                                                                                                    |

| 4              | CO-IN           | Output control pin. When high the output operates in accordance with input logic; when low the output is forcibly turned off regardless of the input logic.                  |

| 6              | LP              | CR filter circuit pin. Connecting a capacitor to the GND creates a filter for the over-current detection signal from the comparator. When not in use, leave open.            |

| 8              | ERR             | Over-current detection signal output pin. Comes on when excess current is detected. Normally, set to high impedance.                                                         |

| 9              | GND             | GND pin.                                                                                                                                                                     |

| 10             | СОМ             | Clamp diode's common cathode pin.                                                                                                                                            |

| 17, 15, 13, 11 | NF1 to 4        | Resistor connecting pins for over-current detection setting. By connecting resistors between these pins and GND, the detection level can be set separately for each circuit. |

| 18, 16, 14, 12 | OUT1 to 4       | Open collector output pins.                                                                                                                                                  |

### **MAXIMUM RATINGS**

|                                | 1                    | Ī                         |      |

|--------------------------------|----------------------|---------------------------|------|

| CHARACTERISTIC                 | SIGNAL               | RATING                    | UNIT |

| Power Supply Voltage           | Vcc                  | 7.0                       | V    |

| COM Pin Voltage                | Vсом                 | 30.0                      | ٧    |

| Output Voltage                 | V <sub>CEO</sub>     | 30.0                      | V    |

| ERR Pin Output Voltage         | V <sub>ERR</sub>     | 7.0                       | ٧    |

| Output Sink Current            | IOUT                 | 0~150                     | mA   |

| ERR Pin Sink Current           | IERR                 | 10                        | mΑ   |

| Input Voltage                  | VIN                  | -0.3~V <sub>CC</sub> +0.3 | ٧    |

| NF Pin Voltage                 | VIN (NF)             | -0.3~1.0                  | ٧    |

| LP Pin Voltage                 | V <sub>IN</sub> (LP) | $-0.3 \sim V_{CC} + 0.3$  | V    |

| Clamp Diode Reverse Voltage    | V <sub>r1</sub>      | 30                        | ٧    |

| Clamp Diode Forward Current    | lf1                  | 150                       | mA   |

| Output Parasitic Diode Forward | lea                  | 100                       | mΑ   |

| Current                        | l <sub>f2</sub>      | 100                       | IIIA |

| Power Dissipation              | P <sub>D</sub> (*)   | 960                       | mW   |

| Operating Temperature          | T <sub>opr</sub>     | <b>- 10∼85</b>            | °C   |

| Storage Temperature            | T <sub>stg</sub>     | <b>-</b> 55∼150           | °C   |

(\*) When the device is mounted on a PCB (with one surface  $50 \times 50 \times 1.6$ mm Cu 40% glass epoxy) When operating at an ambient temperature of 25°C or higher, derate the power dissipation at 7.6mW/°C.

### **RECOMMENDED OPERATING CONDITIONS** (Unless otherwise specified, $V_{CC} = 5.0V$ , $T_0 = -10$ to $85^{\circ}C$ )

| CHARACTERISTIC       | SYMBOL           | TEST CONDITION                            | MIN | TYP. | MAX                   | UNIT |

|----------------------|------------------|-------------------------------------------|-----|------|-----------------------|------|

| Power Supply Voltage | V <sub>C</sub> C | _                                         | 4.5 | 5.0  | 5.5                   | V    |

| Output Voltage       | V <sub>CEO</sub> | OUT1~4                                    | 0   | _    | 30.0                  | V    |

|                      | V <sub>ERR</sub> | ERR                                       | 0   | _    | V <sub>CC</sub> + 0.3 | V    |

| Output Current       | IOUT             | _                                         | 0   | _    | 120                   | mA   |

|                      | I <sub>ERR</sub> | ERR                                       | 0   | _    | 8                     | mA   |

| Input Voltage        | VIN              | V <sub>CC</sub> = 5.0V : IN1~4, CO-IN, LP | 0   | _    | Vcc                   | V    |

| Power Dissipation    | P <sub>D1</sub>  | Ta = 60°C                                 | _   | _    | 0.69                  | W/IC |

|                      | P <sub>D2</sub>  | Ta = 85°C                                 | _   | _    | 0.50                  | W/IC |

### **ELECTRICAL CHARACTERISTICS**

(Unless otherwise specified,  $V_{CC} = 5.0V \pm 10\%$ ,  $T_a = -10$  to  $85^{\circ}$ C,  $V_{IN}$  (NF) = GND)

| CHARACTERISTIC                          | SYMBOL                                    | TEST<br>CIR-<br>CUIT | TEST CONDITION                                                    | MIN  | TYP.        | MAX         | UNIT        |

|-----------------------------------------|-------------------------------------------|----------------------|-------------------------------------------------------------------|------|-------------|-------------|-------------|

| Operating Power Supply<br>Voltage       | Vcc                                       | _                    | _                                                                 | 4.5  | 5.0         | 5.5         | \ \         |

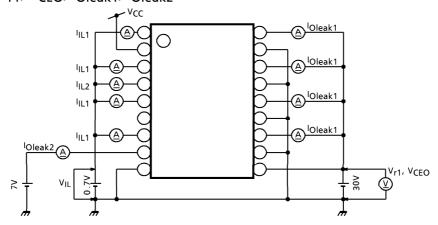

| Output Lookage Current                  | lOleak1                                   | 1                    | $V_{CE} = 30V, V_{IN} = 0V,$<br>$Ta = 25^{\circ}C : OUT1 \sim 4$  | 0    | _           | 100         | <           |

| Output Leakage Current                  | lOleak2                                   | 1                    | $V_{CE} = 7.0V, V_{NF} = 0V,$<br>Ta = 25°C : ERR                  | 0    | _           | 50          | μΑ          |

| Output Saturation Voltage               | V <sub>OL1</sub>                          | 2                    | I <sub>OUT</sub> = 100mA,<br>R <sub>NF</sub> = 0 : OUT1~4         | 0    | 0.15        | 0.40        | V           |

|                                         | V <sub>OL2</sub>                          | 3                    | I <sub>OL</sub> = 10mA : ERR                                      | 0    | 0.20        | 0.60        |             |

|                                         | V <sub>I+</sub>                           | 3                    | $V_{ERR} = "L",$ $T_{a} = -10 \sim 85^{\circ}C : NF1 \sim 4$      | 0.25 | 0.30        | 0.35        | <b>&gt;</b> |

| Input Voltage                           | $V_{IH}$                                  | 2                    | IN1~4, CO-IN                                                      | 2.50 | _           | 1           | ]           |

|                                         | $V_{IL}$                                  | 1                    | NF1~4, CO-IN                                                      | _    | _           | 0.70        |             |

|                                         | lιΗ                                       | 2                    | $V_{IN} = 2.5V$ , $Ta = 25^{\circ}C : IN1 \sim 4$                 | _    | + 0.5       | + 0.1       | mA          |

| Input Current                           | I <sub>IL1</sub>                          | 1                    | $V_{IN} = 0.7V$ , $Ta = 25^{\circ}C : IN1 \sim 4$                 |      | + 0.1       | + 0.1       |             |

|                                         | l <sub>IL2</sub>                          | 1                    | $V_{IN} = 0.7V$ , $Ta = 25^{\circ}C$ : $CO-IN$                    | _    | - 1.0       | - 3.4       |             |

| Power Supply Current When Not Operating | lcc                                       | 4                    | $V_{IN} = 0.7V$ : CO-IN, IN1~4,<br>Ta = 25°C All outputs off      | _    | 8           | 10          | mA / IC     |

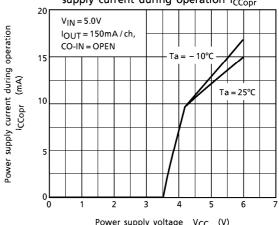

| Power Supply Current<br>When Operating  | I <sub>CCopr</sub>                        | 4                    | $V_{IN} = 2.5V$ , $I_{OUT} = 150$ mA,<br>Ta = 25°C All outputs on | _    | 40          | 70          | mA / IC     |

| Clamp Diode Forward<br>Voltage          | V <sub>f1</sub>                           | 5                    | I <sub>f</sub> =100mA : OUT1~4 to COM                             | _    | 1.20        | 2.00        | <           |

| Clamp Diode Reverse<br>Voltage          | V <sub>r1</sub>                           | 1                    | $I_r = 100 \mu A$ : COM to OUT1~4                                 | 30   | _           | _           | ٧           |

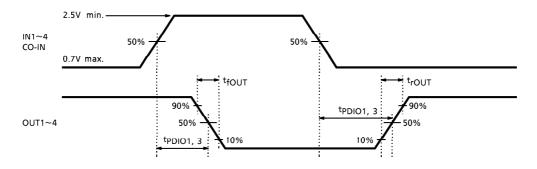

| Input/Output Delay Time                 | <sup>t</sup> PDIO1<br>(t <sub>pLH</sub> ) | 6                    | Ta = 25°C, V <sub>CE</sub> = 30V,<br>I <sub>OUT</sub> = 150mA,    |      | (*)<br>0.25 | (*)<br>1.25 | ,,,         |

|                                         | <sup>t</sup> PDIO1<br>(t <sub>pHL</sub> ) | 6                    | C <sub>L</sub> = 10pF : IN1~4 to OUT1~4                           | _    | (*)<br>0.40 | (*)<br>2.00 | $\mu$ s     |

(\*) The switching characteristic values indicate the guaranteed design limits.

| CHARACTERISTIC          | SYMBOL                                    | TEST<br>CIR-<br>CUIT | TEST CONDITION                                                                                            | MIN | TYP.        | MAX         | UNIT       |

|-------------------------|-------------------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------|-----|-------------|-------------|------------|

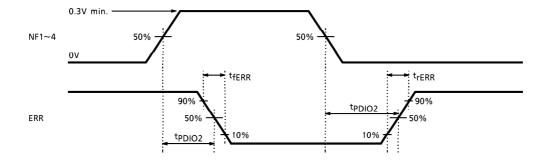

| Input/Output Delay Time | t <sub>PDIO2</sub><br>(t <sub>pLH</sub> ) | 7                    | Ta = 25°C, V <sub>ERR</sub> = 5.0V,<br>I <sub>OL</sub> = 10mA, C <sub>L</sub> = 10pF,                     | _   | (*)<br>0.30 | (*)<br>1.50 |            |

|                         | t <sub>PDIO2</sub><br>(t <sub>pHL</sub> ) | 7                    | V <sub>NF</sub> = 0 to 0.4V :<br>NF1~4 to ERR                                                             | _   | (*)<br>5.00 | (*)<br>15.0 |            |

|                         | t <sub>PDIO3</sub><br>(t <sub>pLH</sub> ) | 6                    | Ta = 25°C, $V_{CE}$ = 30V,<br>$I_{OUT}$ = 150mA,<br>$C_{L}$ = 50pF : CO-IN to OUT1~4                      | _   | (*)<br>0.25 | (*)<br>1.25 | $\mu$ s    |

|                         | t <sub>PDIO3</sub><br>(t <sub>pHL</sub> ) | 6                    |                                                                                                           | _   | (*)<br>0.40 | (*)<br>2.00 |            |

| Output Rise Time        | (t <sub>pLH</sub> )                       | 6                    | Ta = 25°C, V <sub>CE</sub> = 30V,<br>I <sub>OUT</sub> = 150mA, C <sub>L</sub> = 50pF,<br>10%-90% : OUT1~4 | _   | (*)<br>0.40 | (*)<br>1.00 |            |

|                         | <sup>t</sup> rERR                         | 7                    | Ta = 25°C, $V_{ERR}$ = 5.0V, $I_{OL}$ = 10mA, $C_{L}$ = 10pF, $10\%$ -90% : ERR                           | _   | (*)<br>0.40 | (*)<br>1.00 | μ <b>s</b> |

| Output Fall Time        | <sup>t</sup> fOUT                         | 6                    | Ta = 25°C, V <sub>CE</sub> = 30V,<br>I <sub>OUT</sub> = 150mA, C <sub>L</sub> = 50pF,<br>90%-10% : OUT1~4 | _   | (*)<br>0.10 | (*)<br>1.00 |            |

|                         | <sup>t</sup> fERR                         | 7                    | Ta = 25°C, $V_{ERR}$ = 5.0V, $I_{OL}$ = 10mA, $C_{L}$ = 10pF, $90\%$ -10% : ERR                           | _   | (*)<br>0.02 | (*)<br>1.00 | μs         |

(\*) The switching characteristic values indicate the guaranteed design limits.

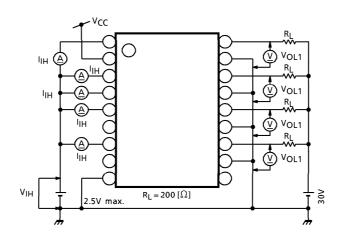

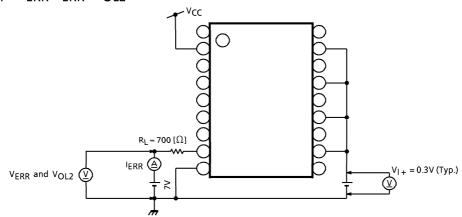

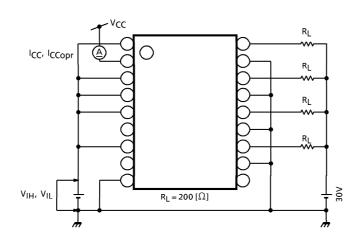

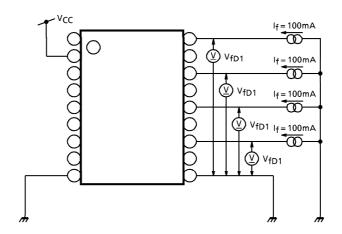

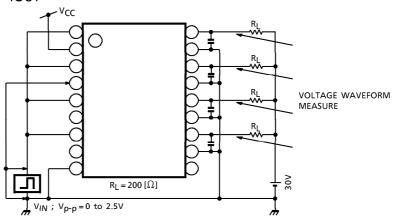

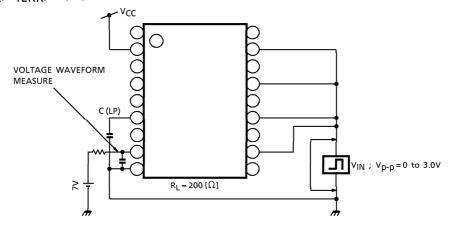

### **TEST CIRCUIT**

(1)  $V_{IL}$ ,  $I_{IL1\sim2}$ ,  $V_{r1}$ ,  $V_{CEO}$ ,  $I_{Oleak1}$ ,  $I_{Oleak2}$

(2) V<sub>IH</sub>, I<sub>IH</sub>, V<sub>OL1</sub>

(3) V<sub>I+</sub>, V<sub>ERR</sub>, I<sub>ERR</sub>, V<sub>OL2</sub>

(4) I<sub>CC</sub>, I<sub>CCopr</sub>

(5) V<sub>f1</sub>

(6) tpDiO1, tpDiO3, trOUT, tfOUT

(7) t<sub>PDIO2</sub>, t<sub>rERR</sub>, t<sub>fERR</sub>, C (LP)

### **SWITCHING WAVEFORM**

[tpDIO1, 3, trOUT, tfOUT]

## [tpDIO2, trerr, tferr]

**TOSHIBA**

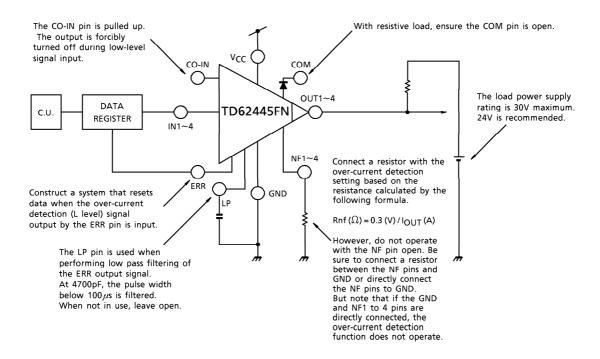

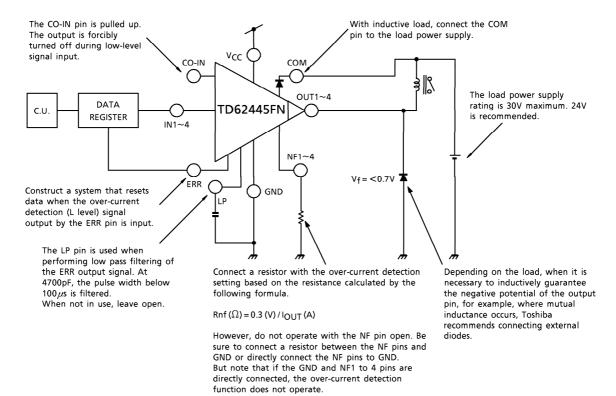

### **APPLICATION CIRCUIT**

### 1. Using resistive load drive

### 2. Using inductive load (eg, relay) drive

### PRECAUTIONS for USING

Utmost care is necessary in the design of the output line,  $V_{CC}$ , COMMON and GND line since IC may be destroyed due to short-circuit between outputs, air contamination fault, or fault by improper grounding.

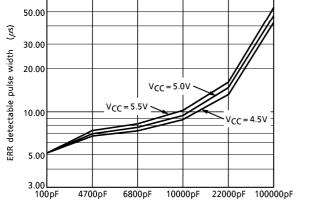

### Capacitor between LP and GND pins vs ERR detectable pulse width (At Ta = 25°C, ERR pin outputs a low-level pulse width of $1\mu$ s.)

Capacitor between LP and GND pins (pF)

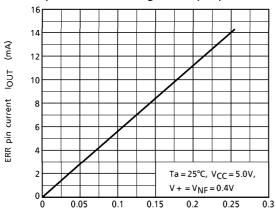

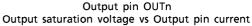

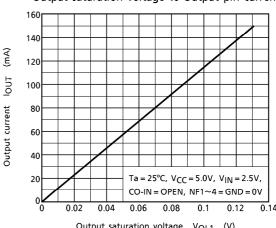

ERR pin Output saturation voltage vs Output pin current

ERR pin output saturation voltage  $V_{OL1}$  (V)

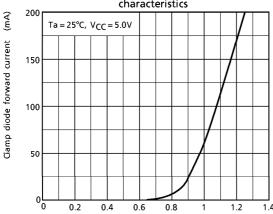

Clamp diode COM Forward voltage Vf vs Forward current If characteristics

Output saturation voltage  $V_{OL1}$  (V)

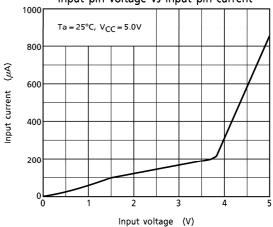

Input pin INn Input pin voltage vs Input pin current

Power supply voltage  $V_{CC}$  Applied power supply voltage  $V_{CC}$  vs Power supply current during operation I<sub>CCopr</sub>

Power supply voltage V<sub>CC</sub> (V)

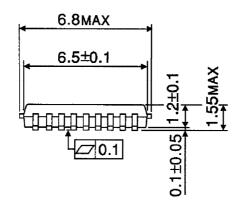

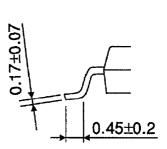

## OUTLINE DRAWING

Weight: 0.08g (Typ.)