**TOSHIBA** TC9299P

TOSHIBA CMOS DIGITAL INTEGRATED CIRCUIT SILICON MONOLITHIC

# T C 9 2 9 9 P

# ELECTRONIC VOLUME CONTROL IC

TC9299P is electronic volume control IC developed for use in audio equipment such as home stereo sets.

This IC control balance and rear speaker.

The volume, balance and loudness circuits can be controlled by serial data which are input externally.

#### **FEATURES**

- Thirty-two level volume control in 1dB steps from 0dB to 30dB,  $\infty$  dB.

- The volume circuit features 2 built-in channels which can be controlled independently, thus controlling balance.

Weight: 1.0g (Typ.)

- Single and dual power supply operation.

- Chip select input allows control of up to four of these chips on the same bus.

- Polysilicon resistors enables low-distortion, high-performance volume systems.

- Package is DIP16 Pin.

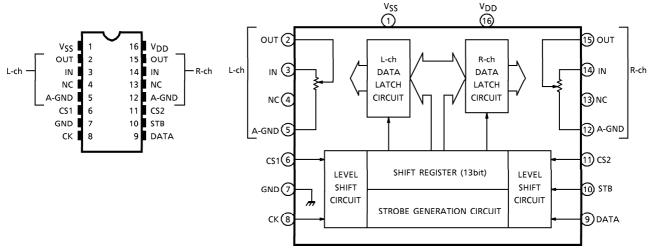

#### PIN CONNECTION

#### **BLOCK DIAGRAM**

- TOSHIBA is continually working to improve the quality and the reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to observe standards of safety, and to avoid situations in which a malfunction or failure of a TOSHIBA product could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent products specifications. Also, please keep in mind the precautions and conditions set forth in the TOSHIBA Semiconductor Reliability Handbook.

The products described in this document are subject to the foreign exchange and foreign trade laws.

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

The information contained herein is subject to change without notice.

# **PIN FUNCTION**

| PIN No. | SYMBOL          | PIN NAME                  | FUNCTION AND OPERATION                                               | NOTE                     |  |

|---------|-----------------|---------------------------|----------------------------------------------------------------------|--------------------------|--|

| 1       | V <sub>SS</sub> | Negative power supply pin | Dual power supply $V_{DD} = 6.0 \sim 17V$<br>$V_{DD} = 6.0 \sim 17V$ |                          |  |

| 7       | GND             | Digital ground pin        | $V_{SS} = -6.0 \sim -17V$                                            | _                        |  |

| 16      | V <sub>DD</sub> | Positive power supply pin | Single power supply $V_{DD} = 6.0 \sim 18V$<br>$V_{SS} = GND = 0V$   |                          |  |

| 2       | L-OUT           | Volume output nine        | Volume circuit                                                       |                          |  |

| 15      | R-OUT           | Volume output pins        | оит О———                                                             |                          |  |

| 3       | L-IN            | Valuma input pins         | IN O                                                                 |                          |  |

| 14      | R-IN            | Volume input pins         | <u></u>                                                              | _                        |  |

| 5       | L-A-GND         | Analas araund nina        | A-GND O                                                              |                          |  |

| 12      | R-A-GND         | Analog ground pins        |                                                                      |                          |  |

| 6       | CS1             | Chip select input pins    | Switching chip select code allows control of                         |                          |  |

| 11      | CS2             | Chip select hiput phis    | up to 4 chips simultaneously on one bus.                             | _                        |  |

| 8       | СК              | Clock input pin           | Clock input for data transfer                                        | Low                      |  |

| 9       | DATA            | Data input pin            | Serial data input for setting volume                                 | threshold<br>value input |  |

| 10      | STB             | Strobe input pin          | Strobe input for writing data                                        | pins                     |  |

| 4, 13   | NC              | Not connected             |                                                                      | _                        |  |

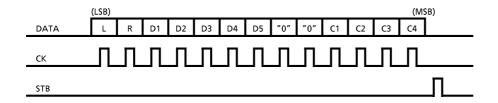

#### **OPERATIONS**

1. Setting volume values (Attenuation)

The volume values are set using 13bit serial data.

• Data format

- L is left channel select data, R is right channel select data.

When L=1, left channel volume is set. When R=1, right channel volume is set.

(When R=L=1, both channel volumes are set simultaneously)

- 2) 8, 9bit data is set to "0".

- 3) "D1"  $\sim$  "D5" are volume value setting data.

| VOLUME<br>VALUE | D1 | D2 | D3 | D4 | D5 |

|-----------------|----|----|----|----|----|

| 0dB             | 0  | 0  | 0  | 0  | 0  |

| 1               | 1  | 0  | 0  | 0  | 0  |

| 2               | 0  | 1  | 0  | 0  | 0  |

| 3               | 1  | 1  | 0  | 0  | 0  |

| 4               | 0  | 0  | 1  | 0  | 0  |

| 5               | 1  | 0  | 1  | 0  | 0  |

| 6               | 0  | 1  | 1  | 0  | 0  |

| 7               | 1  | 1  | 1  | 0  | 0  |

| 8               | 0  | 0  | 0  | 1  | 0  |

| 9               | 1  | 0  | 0  | 1  | 0  |

| 10              | 0  | 1  | 0  | 1  | 0  |

| 11              | 1  | 1  | 0  | 1  | 0  |

| 12              | 0  | 0  | 1  | 1  | 0  |

| 13              | 1  | 0  | 1  | 1  | 0  |

| 14              | 0  | 1  | 1  | 1  | 0  |

| 15              | 1  | 1  | 1  | 1  | 0  |

| VOLUME<br>VALUE | D1 | D2 | D3 | D4 | D5 |

|-----------------|----|----|----|----|----|

| 16dB            | 0  | 0  | 0  | 0  | 1  |

| 17              | 1  | 0  | 0  | 0  | 1  |

| 18              | 0  | 1  | 0  | 0  | 1  |

| 19              | 1  | 1  | 0  | 0  | 1  |

| 20              | 0  | 0  | 1  | 0  | 1  |

| 21              | 1  | 0  | 1  | 0  | 1  |

| 22              | 0  | 1  | 1  | 0  | 1  |

| 23              | 1  | 1  | 1  | 0  | 1  |

| 24              | 0  | 0  | 0  | 1  | 1  |

| 25              | 1  | 0  | 0  | 1  | 1  |

| 26              | 0  | 1  | 0  | 1  | 1  |

| 27              | 1  | 1  | 0  | 1  | 1  |

| 28              | 0  | 0  | 1  | 1  | 1  |

| 29              | 1  | 0  | 1  | 1  | 1  |

| 30              | 0  | 1  | 1  | 1  | 1  |

| ∞               | 1  | 1  | 1  | 1  | 1  |

4) "C1"~"C4" are chip select code data.

Code data are set according to CS1 and CS2 input.

| CS1 | CS2 | C1 | C2 | <b>C</b> 3 | C4 |

|-----|-----|----|----|------------|----|

| L   | L   | 0  | 0  | 1          | 1  |

| Н   | L   | 1  | 0  | 1          | 1  |

| L   | Η   | 0  | 1  | 1          | 1  |

| Н   | Н   | 1  | 1  | 1          | 1  |

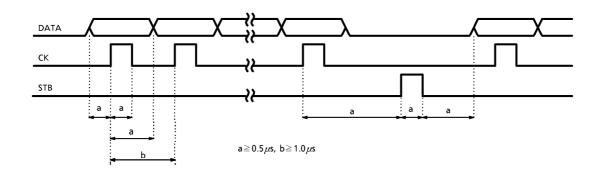

#### 2. Serial data timing

Input CK, DATA and STB according to the following timing.

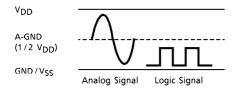

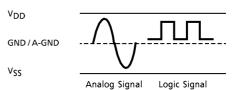

# 3. Single and dual power supply operation

TC9299P is operate with single or dual power supplies. With single or dual power supply, serial data logic level can be  $0\sim5$ V.

• Single power supply operation

Dual power supply operation

# **MAXIMUM RATINGS** (Ta = 25°C)

| CHARACTERISTIC                | SYMBOL               | RATING                           | UNIT |

|-------------------------------|----------------------|----------------------------------|------|

| Power Supply Voltage (1)      | $V_{DD}$ - $V_{SS}$  | -0.3~36                          | V    |

| Power Supply Voltage (2)      | V <sub>DD</sub> -GND | -0.3~20                          | V    |

| GND Input Voltage             | V <sub>IN</sub> (1)  | -0.3~V <sub>DD</sub> +0.3        | V    |

| V <sub>SS</sub> Input Voltage | V <sub>IN</sub> (2)  | $V_{SS} - 0.3 \sim V_{DD} + 0.3$ | V    |

| Power Dissipation             | PD                   | 300                              | mW   |

| Operating Temperature         | T <sub>opr</sub>     | -40~85                           | °C   |

| Storage Temperature           | T <sub>stg</sub>     | <b>-65∼150</b>                   | °C   |

#

| CHARACTERISTIC                    |                         | SYMBOL                           | TEST<br>CIR-<br>CUIT | TEST CONDITION                                                                                 |                       | MIN.                | TYP.  | MAX.                | UNIT             |

|-----------------------------------|-------------------------|----------------------------------|----------------------|------------------------------------------------------------------------------------------------|-----------------------|---------------------|-------|---------------------|------------------|

| Operating Supply Voltage (1)      |                         | V <sub>DD</sub> -V <sub>SS</sub> | _                    | Dual power supply operation                                                                    |                       | 12.0                | ~     | 34                  | V                |

| Operating Supply Voltage (2)      |                         | V <sub>DD</sub> -GND             | _                    | Single power supply operation                                                                  |                       | 6.0                 | ~     | 18                  | V                |

| Operating Sup                     | ply Current             | IDD                              | 1                    | No load, No input                                                                              |                       | _                   | 0.5   | 1.0                 | mΑ               |

| Innut Valtage                     | "H" Level               | V <sub>IH</sub> (1)              |                      | CK, DATA, STB                                                                                  | terminal              | 4.0                 | ~     | $V_{DD}$            | v                |

| Input Voltage                     |                         | V <sub>IL</sub> (1)              |                      | $V_{DD} = 6.0 \sim 18V$                                                                        | 1                     | GND                 | ?     | 1.0                 | <b>'</b>         |

| Input Valtage                     | "H" Level               | V <sub>IH</sub> (2)              |                      | CS1, CS2 terminal                                                                              |                       | $V_{DD} \times 0.7$ | ~     | $V_{DD}$            | V                |

| Input Voltage                     | "L" Level               | V <sub>IL</sub> (2)              | _                    |                                                                                                |                       | GND                 | ~     | $V_{DD} \times 0.3$ | ·                |

| Innest Commant                    | "H" Level               | <sup>1</sup> ін                  |                      | CK, DATA,<br>STB, CS1, CS2<br>terminal                                                         | V <sub>IH</sub> = 15V | _                   | _     | 1.0                 |                  |

| Input Current                     | "L" Level               | ПL                               | _                    |                                                                                                | V <sub>IL</sub> = 0V  | - 1.0               | _     | _                   | $\mu$ A          |

| Operating Frequency<br>Range      |                         | fop                              | _                    | CK, DATA, STB terminal                                                                         |                       | 0                   | ~     | 1.0                 | MHz              |

| Minimum Clock                     | Minimum Clock Frequency |                                  |                      |                                                                                                |                       | 0.5                 | _     | _                   | μs               |

| Volume Resista                    | nce Value               | R <sub>VR</sub>                  | _                    | _                                                                                              |                       | 30                  | 43    | 57                  | kΩ               |

| Step Deviation                    |                         | ∆VR                              | _                    | Volume step deviation                                                                          |                       | - 0.5               | _     | 0.5                 | dB               |

| Analog Switch ON<br>Resistance    |                         | RON                              |                      | Internal analog switch                                                                         |                       | _                   | 350   | 600                 | Ω                |

| Analog Switch OFF Leak<br>Current |                         | lOFF                             | _                    |                                                                                                |                       | - 0.1               | _     | 0.1                 | $\mu$ A          |

| Total Harmonic Distortion         |                         | THD                              |                      | $f_{IN} = 1kHz$ $V_{IN} = 1V_{rms}$ $R_g = 600\Omega, R_L = 100k\Omega$ $BW = 20Hz \sim 20kHz$ |                       | _                   | 0.005 | _                   | %                |

| Maximum Attenuation               |                         | ATTMAX                           | _                    |                                                                                                |                       | _                   | 100   | _                   | dB               |

| Output Noise Voltage              |                         | ٧N                               | ]                    |                                                                                                |                       | _                   | 1.0   | _                   | $\mu$ V $_{rms}$ |

| Cross Talk                        | Cross Talk              |                                  |                      |                                                                                                |                       |                     | 100   | _                   | dB               |

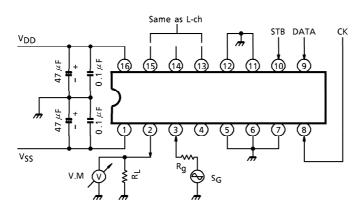

TEST CIRCUIT 1 (IDD/THD/ATTMAX/VN/C·T)

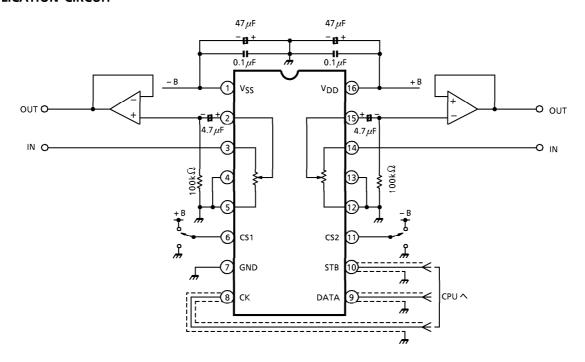

# **APPLICATION CIRCUIT**

(Note) High-frequency digital signals are input to pins CK, DATA and STB.

Since these signals may cause noise in analog circuits, either use shield wire for CK,

DATA, and STB signal lines, or design the pattern so that these signal lines are

protected by the ground line.

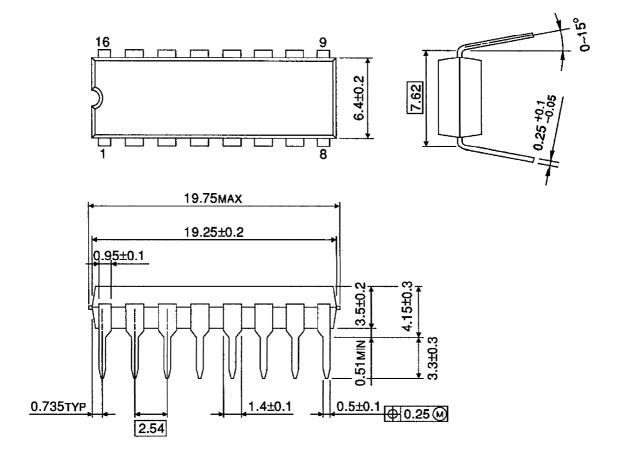

#### OUTLINE DRAWING DIP16-P-300-2.54A

Unit: mm

Weight: 1.0g (Typ.)