# **CMOS CURRENT MODE PWM CONTROLLER**

## **FEATURES**

| Isolated Output Drive                   |

|-----------------------------------------|

| Low Power CMOS Construction             |

| Low Supply Current2mA Typ.              |

| Wide Supply Voltage Operation8V to 18V  |

| Latch-Up Immunity 500mA on Outputs      |

| Above and Below Rail Input Protection6V |

| High Output Drive500mA Peak             |

| Current Mode Control                    |

| Fast Rise/Fall Time50nsec @ 1000pF      |

| High Frequency Operation500kHz          |

| UV Hysteresis Guaranteed                |

| Programmable Current Limit              |

| Shutdown Pin Available                  |

| Double Ended                            |

| Soft Start                              |

| Low Prop Delay Current Amp              |

| to Output < 350nsec Typ.                |

| Low Prop Delay Shutdown                 |

| to Output< 400nsec Typ.                 |

|                                         |

TC38C46Pin Compatible with Unitrode UC3846 ESD Protected ...... ±2 kV

## **GENERAL DESCRIPTION**

The TC38C46 is a current mode CMOS PWM control IC. It draws only 2 mA supply current, so it can be driven without a costly 50-60 Hz transformer. The output drive stage is capable of high drive currents, 300mA typical.

The TC38C46 is pin compatible with earlier bipolar products so that designers can easily update older designs. A number of improvements have been added.

This second generation part has been designed with an isolated drive stage. Unlike its cousin, the TC170, the output stage of the TC38C46 can be run from a separate power supply such as a secondary winding on an output transformer. This allows for bootstrap start-up of the power supply.

## ORDERING INFORMATION

| Part No.   | Configuration | Pkg./Temperature            |

|------------|---------------|-----------------------------|

| TC18C46MJE | Non-Inverting | 16-Pin CerDIP               |

|            |               | − 55°C to +125°C            |

| TC28C46EOE | Non-Inverting | 16-Pin SOIC (Wide)          |

|            |               | − 40 °C to +85°C            |

| TC28C46EPE | Non-Inverting | 16-Pin Plastic DIP (Narrow) |

|            |               | − 40°C to +85°C             |

| TC38C46COE | Non-Inverting | 16-Pin SOIC (Wide)          |

|            |               | 0°C to +70°C                |

| TC38C46CPE | Non-Inverting | 16-Pin Plastic DIP (Narrow) |

|            |               | 0°C to +70°C                |

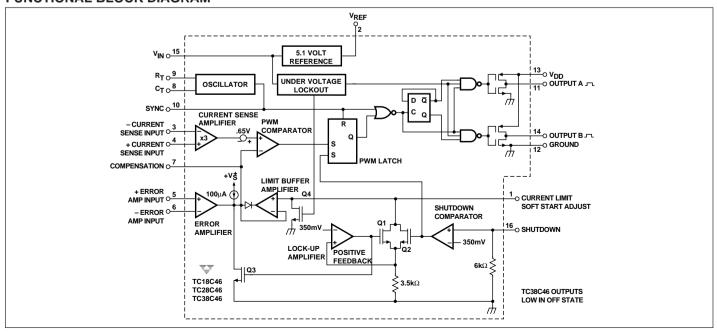

## **FUNCTIONAL BLOCK DIAGRAM**

TC18C46 TC28C46 TC38C46

## **ABSOLUTE MAXIMUM RATINGS**

| Output Current, Source or Sink (Pins 1, 14) | 500mA                |

|---------------------------------------------|----------------------|

| Analog Inputs (Pins 3, 4, 5, 6, 16)         | $-0.3V$ to $+V_{IN}$ |

| Reference Output Current (Pin 2)            | 30 mA                |

| Sync Output Current (Pin 10)                | 5mA                  |

| Error Amplifier Output Current (Pin 7)      | – 5mA                |

| Soft Start Sink Current (Pin 1)             | 50mA                 |

| Oscillator Charging Current (Pin 9)         | 5mA                  |

| Supply Voltage                              | 18V                  |

| Maximum Chip Temperature                    | 150°C                |

| Storage Temperature – 6                     | 5°C to +150°C        |

|                                             |                      |

| Lead Temperature (Soldering, 10 sec) | 300°C   |

|--------------------------------------|---------|

| Package Thermal Resistance           |         |

| CerDIP R <sub>0J-A</sub>             | 150°C/W |

| CerDIP R <sub>0J-C</sub>             | 55°C/W  |

| PDIP R <sub>0J-A</sub>               |         |

| PDIP R <sub>0J-C</sub>               | 45°C/W  |

| SOIC R <sub>0J-A</sub>               | 250°C/W |

| SOIC R <sub>0J-C</sub>               |         |

#### NOTES:

- 1. All voltages are with respect to Ground, Pin 12. Currents are positive into, negative out of the specified terminal.

- 2. Static-sensitive device. Unused devices must be stored in conductive material. Protect devices from static discharge and static fields. Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to Absolute Maximum Rating Conditions for extended periods may affect device reliability.

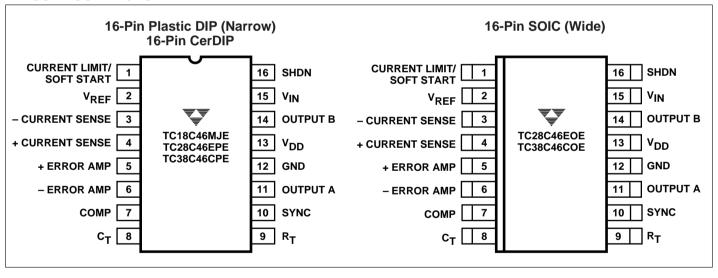

#### PIN CONFIGURATIONS

**ELECTRICAL CHARACTERISTICS:** unless otherwise stated, these specifications apply for  $T_A = -55^{\circ}C$  to +125°C for TC18C46;  $-40^{\circ}C$  to +85°C for the TC28C46; and 0°C to +70°C for the TC38C46;  $V_{IN} = V_{DD} = 16V$ ;  $V_{IN} = V_{DD} = 16V$ .

| $K_T = 30.1K$ , $C_T = 270pr$ | •                                                | 1                       | ΓC18C4 | 16    |                         |      |       |         |

|-------------------------------|--------------------------------------------------|-------------------------|--------|-------|-------------------------|------|-------|---------|

|                               |                                                  | TC28C46                 |        |       | TC38C46                 |      |       |         |

| Parameter                     | Test Conditions                                  | Min                     | Тур    | Max   | Min                     | Тур  | Max   | Units   |

| Reference Section             |                                                  |                         |        |       |                         |      |       |         |

| Output Voltage                | $T_f = 25^{\circ}C, I_O = 1mA$                   | 5.0                     | 5.1    | 5.2   | 5.0                     | 5.1  | 5.2   | V       |

| Line Regulation               | V <sub>IN</sub> = 8V to 16V                      | T —                     | ±4     | ±20   | _                       | ±4   | ±20   | mV      |

| Load Regulation               | I <sub>O</sub> = 1mA to 10mA                     | _                       | ±4     | ±20   | _                       | ±4   | ±20   | mV      |

| Temp Coefficient              | Over Operating Range, (Note 1)                   | _                       | ±0.2   | ±0.5  | _                       | ±0.2 | ±0.5  | mV/°C   |

| Total Output Range            | Line, Load, and Temperature (Note 1)             | 4.97                    | _      | 5.24  | 4.94                    | _    | 5.26  | V       |

| Long Term Drift               | T <sub>f</sub> = 125°C, 1000 Hrs (Note 1)        | _                       | ±50    | _     | _                       | ±50  | _     | mV      |

| Short Circuit                 | V <sub>REF</sub> = 0V                            | 20                      | _      | 70    | 20                      | _    | 70    | mA      |

| Output Current                |                                                  |                         |        |       |                         |      |       |         |

| Output Noise Voltage          | 10 Hz $\leq$ f $\leq$ 10 kHz, Tf = 25°C (Note 1) | _                       | 22     | _     |                         | 22   | _     | μV(rms) |

| Oscillator Section            |                                                  |                         |        |       |                         |      |       |         |

| Initial Accuracy              | T <sub>f</sub> = 25°C                            | 96.5                    | 102    | 106.5 | 96.5                    | 101  | 106.5 | kHz     |

| Voltage Coefficient           | V <sub>IN</sub> = 8V to 16V                      | _                       | ±.1    | 2.0   | _                       | ±.1  | ±1.5  | %/V     |

| Temp Coefficient              | Over Operating Range (Note 1)                    | _                       | ±.04   | ±0.06 | _                       | ±.04 | ±0.06 | %/°C    |

| Clock Ramp                    |                                                  | 1.2                     | 2      | 3     | 1.2                     | 2    | 3     | mA      |

| Reset Current                 |                                                  |                         |        |       |                         |      |       |         |

| Osc Ramp Amplitude            |                                                  | 3.6                     | 3.8    | 4     | 3.6                     | 3.8  | 4     | V       |

| Sync Output High Level        | (Note 1)                                         | V <sub>DD</sub><br>-0.5 | _      | _     | V <sub>DD</sub><br>-0.5 | _    | _     | V       |

| Sync Output Low Level         | (Note 1)                                         | _                       | _      | 0.5   | _                       | _    | 0.5   | V       |

| Sync Input High Level         | Pin 8 = 0V, (Note 1)                             | _                       | 8.5    | _     | _                       | 8.5  | _     | V       |

| Sync Input Low Level          | Pin 8 = 0V, (Note 1)                             | _                       | 8.5    | 5     | _                       | 8.5  | 5     | V       |

| Sync Input Current            | Sync Voltage = 5.25V, Pin 8 = 0V                 | _                       | ±5     | ±50   | _                       | ±5   | ±50   | nA      |

| Error Amp Section             |                                                  |                         |        |       |                         |      |       |         |

| Input Offset Voltage          |                                                  | _                       | ±5     | ±25   | _                       | ±5   | ±25   | mV      |

| Input Bias Current            |                                                  | _                       | ±10    | ±100  | _                       | ±0.1 | ±0.5  | nA      |

| Input Offset Current          |                                                  | _                       | ±10    | ±100  | _                       | ±0.1 | ±0.5  | nA      |

| Open Loop Voltage Gain        | $\Delta V_O = 1V$ to 6V, $R_L = 100k$            | 70                      | 90     | _     | 70                      | 90   | _     | dB      |

| Gain Bandwidth Product        | T <sub>f</sub> = 25°C (Note 1)                   | 0.7                     | 1      | _     | 0.7                     | 1    | _     | MHz     |

| CMRR                          | V <sub>CM</sub> = 0V to 11V                      | 70                      | 90     | _     | 70                      | 90   | _     | dB      |

| PSRR                          | V <sub>IN</sub> = 8V to 16V                      | 70                      | 90     | _     | 70                      | 90   | _     | dB      |

| Output Sink Current           | V(EA -) = 5V, V(EA+) = 4.9V,<br>V(CMPTR) = 1.2V  | 2                       | 4      | _     | 2                       | 4    | _     | mA      |

| Output Source Current         | V(EA -) = 5V, V(EA+) = 5.1V,<br>V(CMPTR) = 2.5V  | 5                       | 10     | _     | 5                       | 10   | _     | mA      |

| High Level Output Volt        | $R_L = (CMPTR) 5k\Omega$ to GND, $A_{CL} = 300$  | 4.75                    | 4.9    | 5.1   | 4.75                    | 4.9  | 5.1   | V       |

| Low Level Output Volt         | $R_L$ = (CMPTR) 5kΩ to GND, $A_{CL}$ = 300       | <u> </u>                | 0.4    | 0.9   | _                       | 0.4  | 0.9   | V       |

| Slew Rate                     |                                                  | 1.3                     | 2      | _     | 1.3                     | 2    | _     | V/µsec  |

TC18C46 TC28C46 TC38C46

**ELECTRICAL CHARACTERISTICS** (Cont): Unless otherwise stated, these specifications apply for  $T_A = -55^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$  for TC18C46;  $-40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$  for the TC28C46; and  $0^{\circ}\text{C}$  to  $+70^{\circ}\text{C}$  for the TC38C46;  $V_{IN} = V_{DD} = 16V$ ;  $R_T = 30.1k$ ;  $C_T = 270pF$ .

|                                                                            |                                       | TC18C46<br>TC28C46 |      |                 | TC38C46 |      |                 |       |

|----------------------------------------------------------------------------|---------------------------------------|--------------------|------|-----------------|---------|------|-----------------|-------|

| Parameter                                                                  | Test Conditions                       | Min                | Тур  | Max             | Min     | Тур  | Max             | Units |

| Current Sense Section                                                      |                                       |                    | 1    |                 |         | 1    |                 |       |

| Amplifier Gain                                                             | (Notes 2, 3)                          | 2.7                | 3    | 3.6             | 2.7     | 3    | 3.4             | V/V   |

| Max Differential<br>Input Signal (V <sub>Pin 4</sub> -V <sub>Pin 3</sub> ) | (Note 2)                              | 1.1                | 1.5  | 1.8             | 1.1     | 1.5  | 1.8             | V     |

| Input Offset Voltage                                                       | (Note 2)                              | 0.4                | 0.65 | 0.85            | 0.4     | 0.65 | 0.85            | V     |

| CMRR                                                                       | V <sub>CM</sub> = 1V to 12V, (Note 2) | 40                 | 60   | _               | 40      | 60   | _               | dB    |

| PSRR                                                                       | V <sub>IN</sub> = 8V to 16V, (Note 2) | 40                 | 60   | _               | 40      | 60   | _               | dB    |

| Input Bias Current                                                         | (Note 1)                              | _                  | ±1   | ±100            | _       | ±1   | ±100            | nA    |

| Input Offset Current                                                       | (Note 1)                              | _                  | ±0.1 | ±2              | _       | ±0.1 | ±2              | nA    |

| Input Common Mode Range                                                    | (Note 1)                              | 0                  | _    | 11              | 0       | _    | 11              | V     |

| Delay to Outputs                                                           | $T_f = 25^{\circ}C$ , (Note 1)        | 150                | 225  | 400             | 150     | 225  | 400             | nsec  |

| <b>Current Limit Adjust Section</b>                                        |                                       |                    |      |                 |         |      |                 |       |

| Current Limit Voltage Offset                                               | _                                     | ±1                 | ±25  | _               | ±1      | ±25  | mV              |       |

| Input Impedance                                                            | (Shutdown Unlatched)                  | 3                  | 3.5  | 4               | 3       | 3.5  | 4               | kΩ    |

| Shutdown Terminal Section                                                  |                                       |                    |      |                 |         |      |                 |       |

| Threshold Voltage                                                          |                                       | 320                | 360  | 400             | 320     | 360  | 400             | mV    |

| Input Voltage Range                                                        | (Note 1)                              | 0                  | _    | V <sub>IN</sub> | 0       | _    | V <sub>IN</sub> | V     |

| Min Latching Current (I <sub>Pin 1</sub> )                                 | (Note 4)                              | 140                | _    | _               | 140     | _    | _               | μА    |

| Max Non-Latching<br>Current (I <sub>Pin1</sub> )                           | (Note 5)                              | _                  | _    | 60              | _       | _    | 65              | μА    |

| Min Pulse Width                                                            | (Note 1)                              | 100                | 50   | _               | 100     | 50   | _               | nsec  |

| Delay to Outputs                                                           | (Note 1)                              | 125                | 250  | 400             | 125     | 250  | 400             | nsec  |

| Output Section                                                             |                                       |                    |      |                 |         |      |                 |       |

| Output Low Level r <sub>DS (ON)</sub>                                      | I <sub>SINK</sub> = 20mA              |                    | 10   | 20              | _       | 10   | 20              | Ω     |

| Output High Level r <sub>DS (ON)</sub>                                     | I <sub>SOURCE</sub> = 20mA            | _                  | 20   | 35              | _       | 20   | 35              | Ω     |

| Output Rise Time                                                           | C <sub>L</sub> = 1 μF                 | T -                | 55   | 90              | _       | 55   | 90              | nsec  |

| Output Fall Time                                                           | C <sub>L</sub> = 1 μF                 | _                  | 55   | 90              | _       | 55   | 90              | nsec  |

| Undervoltage Lockout Section                                               |                                       |                    |      |                 |         |      |                 |       |

| Undervoltage Threshold                                                     |                                       | 6.5                | 7    | 7.3             | 6.5     | 7    | 7.3             | V     |

| Start Threshold                                                            |                                       | 7.4                | 7.8  | 8               | 7.4     | 7.8  | 8               | V     |

| Threshold Hysteresis                                                       |                                       | 0.6                | 0.8  | 1               | 0.6     | 0.8  | 1               | V     |

| Total Standby Current                                                      |                                       |                    |      |                 | •       | •    |                 |       |

| Supply Current                                                             |                                       | _                  | 1.2  | 2.5             | _       | 1.2  | 2               | mA    |

| Start-Up Current                                                           |                                       | _                  | 250  | 350             | _       | 250  | 350             | μΑ    |

NOTES: 1. These parameters, although guaranteed over the recommended operating conditions, are not tested in production.

3. Amplifier gain is defined as:

$$G = \frac{\Delta V Pin 7}{\Delta V Pin 4}$$

; \( \Delta V Pin 4 = 0V \) to 1V

- Current into Pin 1 guaranteed to latch circuit in shutdown state

- 5. Current into Pin 1 guaranteed not to latch circuit in shutdown state.

<sup>2.</sup> Parameter measured at trip point of latch with  $V_{Pin\ 6} = V_{REF}, V_{Pin\ 16} = 0V.$

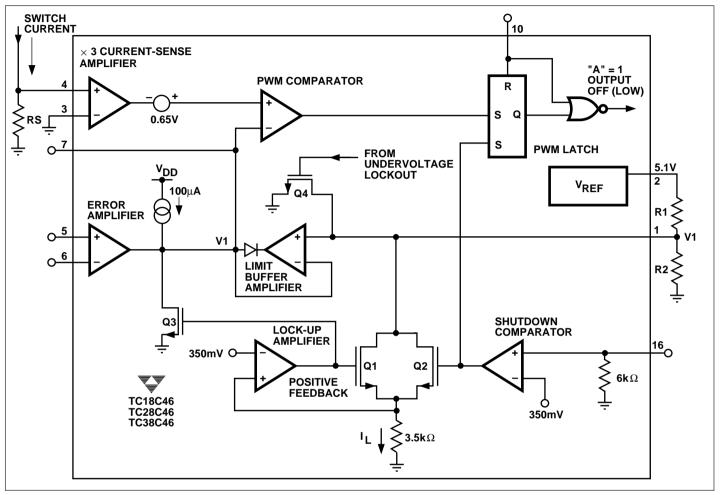

# **Peak Current Limit Setup**

Resistors R1 and R2 at the CURRENT LIMIT input (pin 1) set the peak current limit (Figure 1). The potential at pin 1 is easily calculated:

$$V1 = V_{REF} \frac{R2}{R1 + R2}$$

R1 should be selected first. The shutdown circuit feature is not latched for  $(V_{REF}-0.35)/R1 < 65\mu A$  and is latched for currents greater than 140 $\mu A$ .

The error amplifier output voltage is clamped from going above V1 through the limit buffer amplifier. Peak current is sensed by RS and amplified by the current amplifier which has a fixed gain of 3.

I<sub>PCL</sub>, the peak current limit, is the current that causes the PWM comparator noninverting input to exceed V1, the potential at the inverting input. Once the comparator trip point is exceeded, both outputs are disabled.

I<sub>PCL</sub> is easily calculated:

$$I_{PCL} = \frac{V1 - 0.65V}{3 \text{ (RS)}}$$

where:

$$V1 = V_{REF} \qquad \frac{R2}{R1 + R2}$$

V<sub>REF</sub> = Internal voltage reference = 5.1V 3 = Gain of current-sense amplifier 0.65V = Current limit offset

Both driver OUTPUTs (pins 11 and 14) are OFF (LOW) when the peak current limit is exceeded. When the sensed current goes below I<sub>PCL</sub>, the circuit operates normally.

# Output Shutdown

The outputs can be turned OFF quickly through the SHUTDOWN input (pin 16). A signal greater than 360 mV at pin 16 forces the shutdown comparator output HIGH. The PWM latch is held set, disabling the outputs.

Q2 is also turned ON. If  $V_{REF}/R1$  is greater than 140µA, positive feedback through the lock-up amplifier and Q1 keeps the inverting PWM comparator inverting input below 0.65V. Q3 remains ON even after the shutdown input signal is removed. This is because the lock-up amplifier is in latched mode driving Q3 ON. This state can be cleared only through a power-up cycle. Outputs will be disabled whenever the potential at pin 1 is below 0.65V.

The shutdown terminal gives a fast, direct way to disable the PWM controller output transistors. System protection and remote shutdown applications are possible.

The input pulse to pin 16 should be at least 100nsec wide and have an amplitude of at least 1V in order to get the minimum propagation delay from input to output. If these parameters are met, the delay should be less than 400nsec at 25°C; however, the delay time will increase as the device temperature rises.

## **Soft Restart From Shutdown**

A soft restart can be programmed if nonlatched shutdown operation is used.

A capacitor at pin 1 will cause a gradual increase in potential toward V1. When the voltage at pin 1 reaches 0.75V, the PWM latch set input is removed and the circuit establishes a regulated output voltage. The soft-start operation forces the PWM output drivers to initially operate with minimum duty cycle and low peak currents.

Even if a soft start is not required, it is necessary to insert a capacitor between pin 1 and ground if the current  $I_L$  is greater than 140 $\mu$ A. This capacitor will prevent "noise triggering" of the latch, yet minimize the soft-start effect.

# **Soft-Start Power-Up**

During power-up, a capacitor at R1, R2 initiates a soft-start cycle. As the input voltage (pin 15) exceeds the under-voltage lockout potential (7V), Q4 is turned OFF, ending undervoltage lockout. Whenever the PWM comparator inverting input is below 0.65V, both outputs are disabled.

When the undervoltage lockout start threshold is exceeded, the capacitor begins to charge. The PWM duty cycle increases until the operating output voltage is reached. Soft-start operation forces the PWM output drivers to initially operate with minimum duty cycle and low peak current.

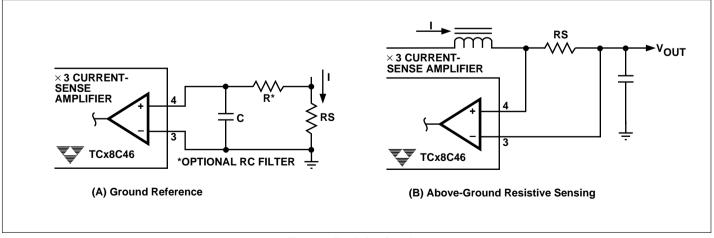

# **Current-Sense Amplifier**

The current-sense amplifier operates at a fixed gain of 3. Maximum differential input voltage ( $V_{PIN4}-V_{PIN3}$ ) is 1.1V. Common-mode input voltage range is 0V to  $V_{IN}-3V$ .

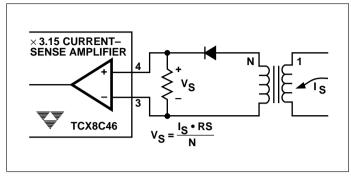

Resistive-sensing methods are shown in Figure 2. In Figure 2(A), a simple RC filter limits transient voltage spikes at pin 4, caused by external output transistor-collector capacitance. Transformer coupling (Figure 3) offers isolation and better power efficiency, but cost and complexity increase.

In order to minimize the propagation delay from the input to the current amplifier to the output terminals, the current ramp should be in the order of 1µsec in width (min). Typical time delay values are in the 225nsec region at 25°C. The delay time increases with device temperature so that at  $50^{\circ}\text{C}$ , the delay times may be increased by as much as 100nsec.

Figure 1. R1 and R2 Set Maximum Peak Output Current

Figure 2. Resistive Sensing

Figure 3. Transformer Isolated Current Sense

## **Under Voltage Lockout**

The under voltage lockout circuit forces the PWM controller outputs OFF (LOW) if the supply voltage is below 7V. Threshold hysteresis is 0.8V and guarantees clean, jitterfree turn-ON and turn-OFF points. The hysteresis also reduces capacitive filtering requirements at the PWM controller supply input (pin 15).

# **Circuit Synchronization**

Current-mode-controlled power supplies can be operated in parallel with a common load. Paralleled converters will equally share the load current. Voltage-mode controllers unequally share the load current, decreasing system reliability.

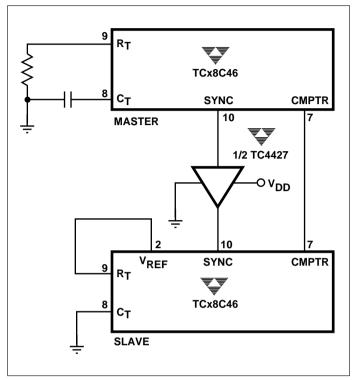

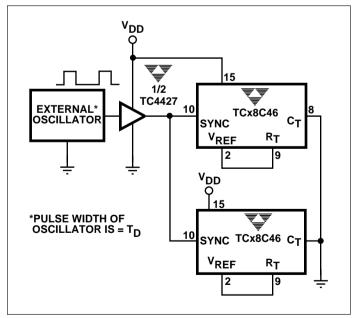

Two or more of these PWM controllers can be slaved together for parallel operation. Circuits can operate from a master PWM controller internal oscillator with an external driver (Figure 4). Devices can also be slaved to an external oscillator (Figure 5). Disable internal slave device oscillators by grounding pin 8. Slave controllers derive an oscillator from the bidirectional synchronization output signal at pin 10.

Pin 10 is bidirectional in that it is intended to be both a sync output and input. This is accomplished by making the output driver "weak." This is advantageous in that it eliminates an additional pin from the package but does not enable the device to directly drive another device. In order to make it an effective driver, a buffer is required (Figure 4). In order to use pin 10 as a sync input, it is necessary to overcome the internal driver. This requires a pulse with an amplitude equal to V<sub>S</sub>. Since V<sub>S</sub> must be above 7V for the undervoltage lockout to be disabled, a CMOS or opencollector TTL driver should be used.

Figure 4. Master/Slave Parallel Operation

Figure 5. External Clock Synchronization

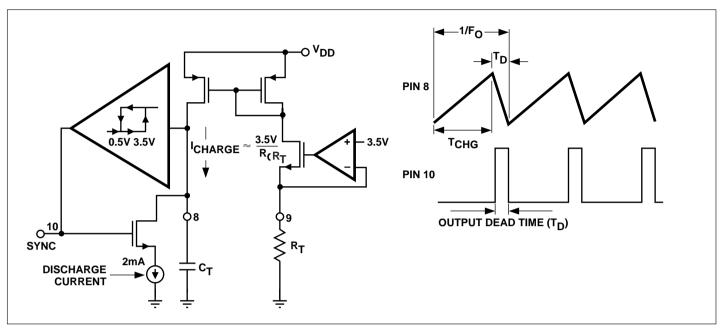

Figure 6. Oscillator Circuit

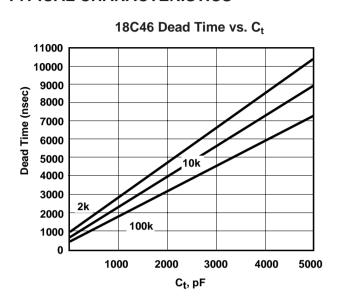

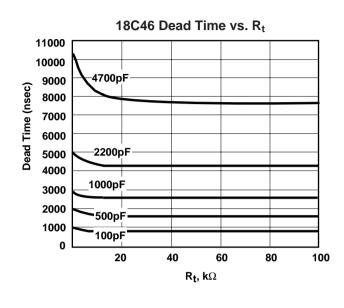

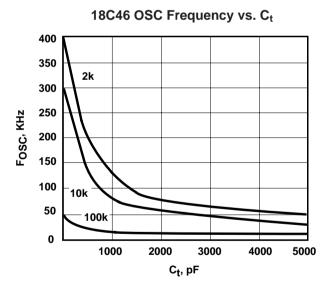

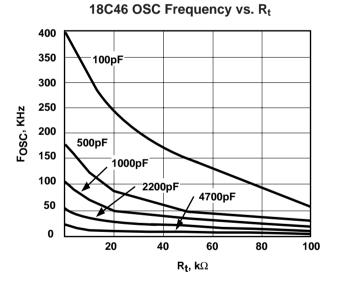

# Selection of Timing Capacitor and Resistor ( $C_T \& R_T$ )

1) First determine the frequency of operation F<sub>O</sub> and the desired " dead" time", T<sub>D</sub> (see Fig.6 graph).

We need to choose R<sub>T</sub> and C<sub>T</sub>.

2) The current mirror in Fig. 6, shows:

$$I_{CHG} = \frac{3.5 \text{ V}}{R_T} \qquad . \qquad \text{Also,}$$

$$I_{CHG} = C_T - \Delta V \over \Delta T$$

Where,  $\Delta V = 3.5 - 0.5$  = 3.0 Volts and  $\Delta T = T_{CHG}$

3) During discharge ( $T_D$ ), the discharge current pulls 2 m A out of  $C_{T,\,}$  minus the  $I_{CHG}$  that keeps trying to charge it:

2 m A - I<sub>CHG</sub> =

$$C_T$$

$\Delta V$  ,where  $\Delta V$ = 3.0 Volts  $\Delta T$ =  $T_D$

Substituting and rearranging,

$$C_{T} = \frac{T_{D}}{3} \quad (.002 - 3.5) \\ \hline R_{T}$$

Knowing Tp choosing RT permits calculation of CT.

## TYPICAL CHARACTERISTICS

TC18C46 TC28C46 TC38C46

# **PIN DESCRIPTION**

| Pin No. Symbol |                           | Description                                                                                                                                                                                                       |  |  |  |  |

|----------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1              | CURRENT LIMIT, SOFT START | Pin for setting the peak current limit threshold of sense inputs pin 3 and pin 4. A second function of this pin is for Soft-Start programming with a capacitor between this pin and ground, pin 12.               |  |  |  |  |

| 2              | $V_{REF}$                 | Pin is an output for the reference supply voltage of 5.1 volts. This reference can supply a minimum of 20mA of output current.                                                                                    |  |  |  |  |

| 3              | – CURRENT SENSE           | Pin is the current sense inverting input for sensing peak current of the pass transistor through the series current monitor resistor.                                                                             |  |  |  |  |

| 4              | + CURRENT SENSE           | Pin is the non-inverting input for sensing peak current of the pass transistor. The positive end of the current sense resistor is connected here.                                                                 |  |  |  |  |

| 5              | + ERROR AMP               | Pin is the non-inverting input for sensing voltage feedback from output for voltage regulation.                                                                                                                   |  |  |  |  |

| 6              | – ERROR AMP               | Pin is the inverting input for sensing the reference voltage to regulate the output.                                                                                                                              |  |  |  |  |

| 7              | COMPENSATION              | Pin for compensating the feedback loop response.                                                                                                                                                                  |  |  |  |  |

| 8              | Ст                        | Pin is the input for timing capacitor, $C_T$ , to set oscillator frequency in conjunction with 9 resistor $R_T$ , input. A second function is for setting the crossover dead time of the outputs, pins 11 and 14. |  |  |  |  |

| 9              | R <sub>T</sub>            | Pin is the input for the timing resistor, $R_{T_i}$ to set oscillator frequency by setting the (constant) current charge rate for capacitor $C_{T_i}$ .                                                           |  |  |  |  |

| 10             | SYNC                      | Pin is the input or output for the oscillator synchronization pulse.                                                                                                                                              |  |  |  |  |

| 11             | OUT <sub>A</sub>          | Pin is the output drive of phase A to drive push pull transistor A.                                                                                                                                               |  |  |  |  |

| 12             | GND                       | Pin is the ground return path for all input and output signals.                                                                                                                                                   |  |  |  |  |

| 13             | $V_{DD}$                  | Pin is the supply power input terminal for the output drivers.                                                                                                                                                    |  |  |  |  |

| 14             | OUT <sub>B</sub>          | Pin is the output drive of phase B to drive push pull transistor B.                                                                                                                                               |  |  |  |  |

| 15             | V <sub>IN</sub>           | Pin is voltage bias supply input for all circuits except the output drivers                                                                                                                                       |  |  |  |  |

| 16             | SHUT                      | Pin is an input for shutdown when a 350mV threshold is exceeded: both output drives will then be terminated.                                                                                                      |  |  |  |  |