# High Speed +3.0V to +5.5V RS-232 Driver/Receiver Pair

- Meets True RS-232 Protocol Operation From A +3.0V to +5.5V Power Supply

- Minimum 250 Kbps Data Rate (SP3220B) or 1Mbps Data Rate (SP3220U) under Fully Load

- 1µA Low-Power Shutdown With Receivers Active

- Interoperable With EIA/TIA 232 and adheres to EIA/TIA 562 Down to +2.7V Power Source

- Pin-Compatible With The MAX3221E Device Without The AUTO ON-LINE® Feature

- ESD Specifications: <u>+</u>2kV Human Body Model

# **DESCRIPTION**

The **SP3220B/U** device is an RS-232 driver/receiver solution intended for portable or hand-held applications such as notebook or palmtop computers. The **SP3220B/U** device has a high-efficiency, charge-pump power supply that requires only  $0.1\mu F$  capacitors in 3.3V operation. This charge pump allows the **SP3220B/U** device to deliver true RS-232 performance from a single power supply ranging from +3.3V to +5.0V.

The **SP3220B/U** device has a low-power shutdown mode where the driver outputs and charge pumps are disabled. During shutdown, the supply current falls to less than  $1\mu$ A.

# **ABSOLUTE MAXIMUM RATINGS**

These are stress ratings only and functional operation of the device at these ratings or any other above those indicated in the operation sections of the specifications below is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability and cause permanent damage to the device.

| V <sub>CC</sub>            | 0.3V to +6.0V |

|----------------------------|---------------|

| V+(NOTE 1)                 | 0.3V to +7.0V |

| V-(NOTE 1)                 |               |

| V++ V-  (NOTE 1)           | +13V          |

|                            |               |

| In (DC Vac or GND current) | +100mA        |

| Input Voltages           TxIN, EN         -0.3V to +6.0V           RxIN <u>+2</u> 5V |

|--------------------------------------------------------------------------------------|

| $\begin{tabular}{lllllllllllllllllllllllllllllllllll$                                |

| Short-Circuit Duration TxOUT Continuous                                              |

| Storage Temperature65°C to +150°C                                                    |

| Power Dissipation Per Package 16-pin SSOP (derate 9.69mW/°Cabove+70°C)               |

NOTE 1: V+ and V- can have maximum magnitudes of 7V, but their absolute difference cannot exceed 13V.

## **SPECIFICATIONS**

Unless otherwise noted, the following specifications apply for  $V_{CC}$  = +3.0V to +5.0V with  $T_{AMB}$  =  $T_{MIN}$  to  $T_{MAX}$ . Typical Values apply at  $V_{CC}$  = +3.3V or +5.0V and  $T_{AMB}$  = 25°C, C1-4=0.1 $\mu$ F.

| PARAMETER                    | MIN.                 | TYP.                 | MAX. | UNITS | CONDITIONS                                                                                                                                                                                |

|------------------------------|----------------------|----------------------|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DC CHARACTERISTICS           |                      |                      |      |       |                                                                                                                                                                                           |

| Supply Current               |                      | 0.3                  | 1.0  | mA    | no load, $T_{AMB}$ = +25°C, $V_{CC}$ = 3.3V TxIN = GND or $V_{CC}$                                                                                                                        |

| Shutdown Supply Current      |                      | 1.0                  | 10   | μΑ    | $\begin{array}{l} \text{SHDN} = \text{GND}, \ \text{T}_{\text{AMB}} = +25^{\circ}\text{C}, \ \text{V}_{\text{CC}} = +3.3\text{V} \\ \text{TxIN} = 0\text{V or V}_{\text{CC}} \end{array}$ |

| LOGIC INPUTS AND RECEIVE     | /ER OUTF             | PUTS                 |      |       |                                                                                                                                                                                           |

| Input Logic Threshold LOW    |                      |                      | 0.8  | V     | TxIN, EN, SHDN, Note 2                                                                                                                                                                    |

| Input Logic Threshold HIGH   | 2.0                  |                      |      | V     | V <sub>CC</sub> = 3.3V, Note 2 or 5.0V, Note 2                                                                                                                                            |

| Input Leakage Current        |                      | ±0.01                | ±1.0 | μΑ    | TxIN, EN, SHDN,<br>$T_{AMB} = +25^{\circ}C V_{IN} = 0V \text{ to } V_{CC}$                                                                                                                |

| Output Leakage Current       |                      | ±0.05                | ±10  | μΑ    | Receivers Disabled V <sub>OUT</sub> = 0V to V <sub>CC</sub>                                                                                                                               |

| Output Voltage LOW           |                      |                      | 0.4  | V     | I <sub>OUT</sub> = 1.6mA                                                                                                                                                                  |

| Output Voltage HIGH          | V <sub>cc</sub> -0.6 | V <sub>cc</sub> -0.1 |      | V     | I <sub>OUT</sub> = -1.0mA                                                                                                                                                                 |

| DRIVER OUTPUTS               |                      |                      |      |       |                                                                                                                                                                                           |

| Output Voltage Swing         | ±5.0                 | ±5.4                 |      | V     | $3k\Omega$ load to ground at all driver outputs,<br>$T_{AMB}$ = +25°C                                                                                                                     |

| Output Resistance            | 300                  |                      |      | Ω     | $V_{CC} = V + = V - = 0V, T_{OUT} = \pm 2V$                                                                                                                                               |

| Output Short-Circuit Current |                      | ±35                  | ±60  | mA    | $V_{OUT} = 0V$                                                                                                                                                                            |

| Output Leakage Current       |                      |                      | ±25  | μΑ    | $V_{OUT} = \pm 12V, V_{CC} = 0V \text{ to } 5.5V, \text{drivers disabled}$                                                                                                                |

# **SPECIFICATIONS** (continued)

Unless otherwise noted, the following specifications apply for  $V_{\rm CC}$  = +3.0V to +5.0V with  $T_{\rm AMB}$  =  $T_{\rm MIN}$  to  $T_{\rm MAX}$ . Typical Values apply at  $V_{\rm CC}$  = +3.3V or +5.0V and  $T_{\rm AMB}$  = 25°C, C1-4=0.1 $\mu$ F.

| PARAMETER                    | MIN.       | TYP.         | MAX.       | UNITS                    | CONDITIONS                                                                                                                                             |

|------------------------------|------------|--------------|------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

|                              |            |              | III/A/A.   | Oitilo                   | CONDITIONS                                                                                                                                             |

| RECEIVER INPUTS              |            |              |            |                          |                                                                                                                                                        |

| Input Voltage Range          | -25        |              | +25        | V                        |                                                                                                                                                        |

| Input Threshold LOW          | 0.6<br>0.8 | 1.2<br>1.5   |            | V                        | V <sub>cc</sub> =3.3V<br>V <sub>cc</sub> =5.0V                                                                                                         |

| Input Threshold HIGH         |            | 1.5<br>1.8   | 2.4<br>2.4 | V                        | V <sub>cc</sub> =3.3V<br>V <sub>cc</sub> =5.0V                                                                                                         |

| Input Hysteresis             |            | 0.3          |            | V                        |                                                                                                                                                        |

| Input Resistance             | 3          | 5            | 7          | kΩ                       |                                                                                                                                                        |

| TIMING CHARACTERISTICS       |            |              |            |                          |                                                                                                                                                        |

| Maximum Data Rate            | 250        |              |            | Kbps                     | $R_L=3k\Omega$ , $C_L=1000pF$ (SP3220EB)                                                                                                               |

| Maximum Data Rate            | 1000       |              |            | Kbps                     | $R_L=3k\Omega$ , $C_L=250pF$ (SP3220EU)                                                                                                                |

| Receiverr Propagation Delay  |            | 0.15<br>0.15 |            | μ <b>s</b><br>μ <b>s</b> | $t_{\rm PHL}$ , RxIN to RxOUT, $C_{\rm L} = 150 {\rm pF}$<br>$t_{\rm PHL}$ , RxIN to RxOUT, $C_{\rm L} = 150 {\rm pF}$                                 |

| Receiver Output Enable Time  |            | 200          |            | ns                       |                                                                                                                                                        |

| Receiver Output Disable Time |            | 200          |            | ns                       |                                                                                                                                                        |

| Driver Skew                  |            | 100          |            | ns                       | t <sub>PHL</sub> - t <sub>PLH</sub>  , T <sub>AMB</sub> = 25°C                                                                                         |

| Receiver Skew                |            | 50           |            | ns                       | t <sub>PHL</sub> - t <sub>PLH</sub>                                                                                                                    |

| Transition-Region Slew Rate  |            |              | 30         | V/µs                     | $V_{\rm CC}$ = 3.3V, R <sub>L</sub> = 3K $\Omega$ , T <sub>AMB</sub> = 25°C,<br>measurements taken from -3.0V to +3.0V<br>or +3.0V to -3.0V (SP3220EB) |

|                              |            | 90           |            | V/μs                     | (SP3220EU)                                                                                                                                             |

**NOTE 2:** Driver input hysteresis is typically 250mV.

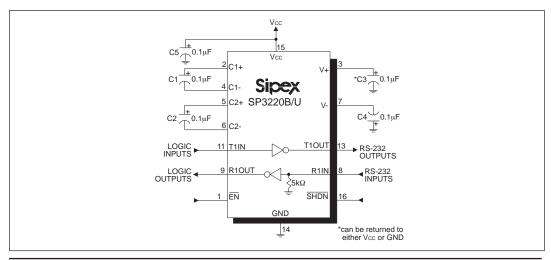

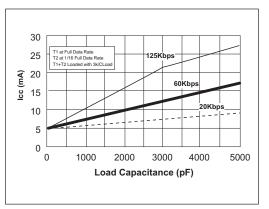

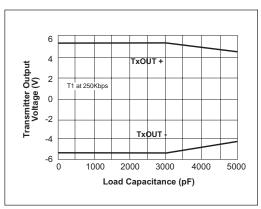

### TYPICAL PERFORMANCE CHARACTERISTICS

Unless otherwise noted, the following performance characteristics apply for  $V_{CC}$  = +3.3V, 250kbps data rates, all drivers loaded with 3k $\Omega$ , 0.1 $\mu$ F charge pump capacitors, and  $T_{AMR}$  = +25°C.

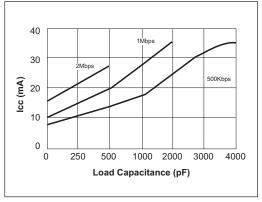

Figure 1.  $I_{cc}$  vs Load Capacitance for the SP3220B.

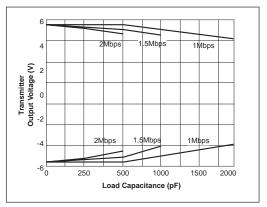

Figure 2. Transmiter Output Voltage vs Load Capacitance for the SP3220B..

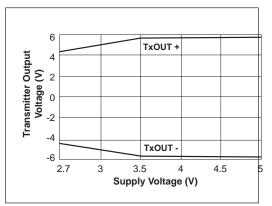

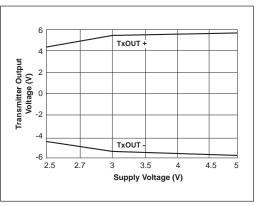

Figure 3. Transmitter Output Voltage vs Supply Voltage for the SP3220B.

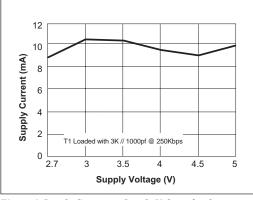

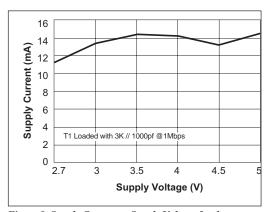

Figure 4. Supply Current vs Supply Voltage for the SP3220B.

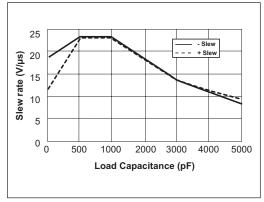

Figure 5. Slew Rate vs Load Capacitance for the SP3220B.

Figure 4. Supply Current vs Supply Voltage for the SP3220U.

# **TYPICAL PERFORMANCE CHARACTERISTICS: Continued**

Unless otherwise noted, the following performance characteristics apply for  $V_{CC}$  = +3.3V, 250kbps data rates, all drivers loaded with  $3k\Omega$ ,  $0.1\mu F$  charge pump capacitors, and  $T_{AMB}$  = +25°C.

Figure 7. Transmitter Output Voltage vs Load Capacitance for the SP3220U.

Figure 8. Transmiter Output Voltage vs Supply Voltage for the SP3220U.

Figure 9. Supply Current vs Supply Voltage for the SP3220U.

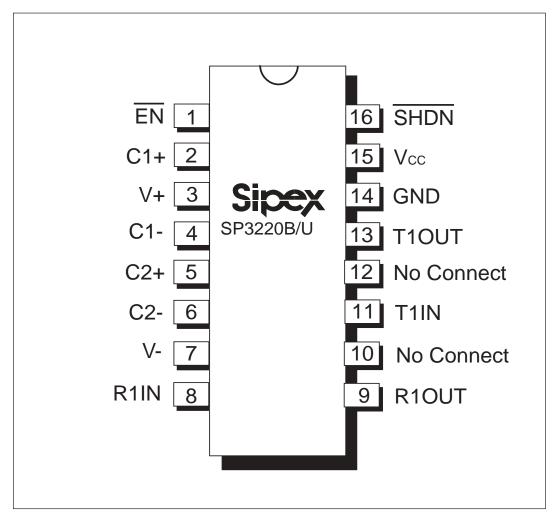

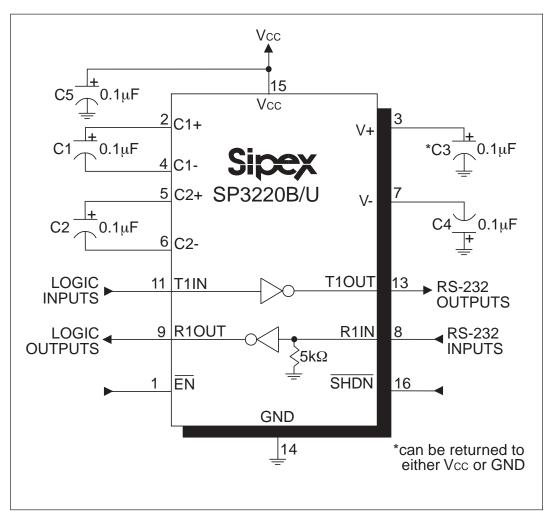

| NAME            | FUNCTION                                                                                                                                                     | PIN NUMBER |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| EN              | Receiver Enable Control. Drive LOW for normal operation. Drive HIGH to Tri-State the receiver outputs (high-Z state).                                        | 1          |

| C1+             | Positive terminal of the voltage doubler charge-pump capacitor.                                                                                              | 2          |

| V+              | +5.5V generated by the charge pump.                                                                                                                          | 3          |

| C1-             | Negative terminal of the voltage doubler charge-pump capacitor.                                                                                              | 4          |

| C2+             | Positive terminal of the inverting charge-pump capacitor.                                                                                                    | 5          |

| C2-             | Negative terminal of the inverting charge-pump capacitor.                                                                                                    | 6          |

| V-              | -5.5V generated by the charge pump.                                                                                                                          | 7          |

| R1IN            | RS-232 receiver input.                                                                                                                                       | 8          |

| R1OUT           | TTL/CMOS reciever output.                                                                                                                                    | 9          |

| N.C.            | No Connect.                                                                                                                                                  | 10, 12     |

| T1IN            | TTL/CMOS driver input.                                                                                                                                       | 11         |

| T1OUT           | RS-232 driver output.                                                                                                                                        | 13         |

| GND             | Ground.                                                                                                                                                      | 14         |

| V <sub>cc</sub> | +3.0V to +5.5V supply voltage                                                                                                                                | 15         |

| SHDN            | Shutdown Control Input. Drive HIGH for normal device operation. Drive LOW to shutdown the drivers (high-Z output) and the on-board charge pump power supply. | 16         |

Table 1. Device Pin Description

Figure 10. Pinout Configurations for the SP3220B/U

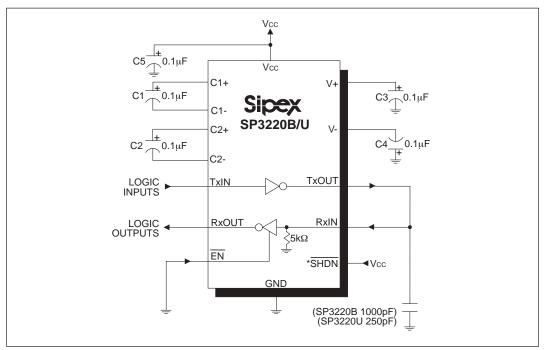

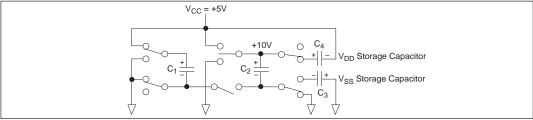

Figure 11. SP3220B/U Typical Operating Circuits

#### **DESCRIPTION**

The SP3220B/U device meets the EIA/TIA-232 and V.28/V.24 communication protocols and can be implemented in battery-powered, portable, or hand-held applications such as notebook or palmtop computers. The SP3220B/U device features Sipex's proprietary on-board charge pump circuitry that generates 2 x V<sub>CC</sub> for RS-232 voltage levels from a single +3.0V to +5.5V power supply. This series is ideal for +3.3V-only systems, mixed +3.0V to +5.5V systems, or +5.0V-only systems that require true RS-232 performance. The SP3220B device has a driver that can operate at a data rate of 250Kbps fully loaded. The SP3220U can Operate at 1000Kbps

The SP3220B/U is a 1-driver/1-receiver device ideal for portable or hand-held applications. The SP3220B/U features a 1μA shutdown mode that reduces power consumption and extends battery life in portable systems. Its receivers remain active in shutdown mode, allowing external devices such as modems to be monitored using only 1μA supply current.

#### THEORY OF OPERATION

The **SP3220B/U** device is made up of three basic circuit blocks: 1. Drivers, 2. Receivers, and 3. the Sipex proprietary charge pump.

#### **Drivers**

The drivers are inverting level transmitters that convert TTL or CMOS logic levels to  $\pm 5.0$ V EIA/TIA-232 levels inverted relative to the input logic levels. Typically, the RS-232 output voltage swing is  $\pm 5.5$ V with no load and at least  $\pm 5$ V minimum fully loaded. The driver outputs are protected against infinite short-circuits to ground without degradation in reliability. Driver outputs will meet EIA/TIA-562 levels of  $\pm 3.7$ V with supply voltages as low as 2.7V.

The **SP3220B** drivers typically can operate at a data rate of 250Kbps fully loaded with  $3K\Omega$  in parallel with 1000pF, ensuring compatibility with PC-to-PC communication software.

The SP3220U drivers can guarantee a data rate of 1000Kbps fully loaded with  $3\Omega$  in parallel with 250pF.

The slew rate of the SP3220B output is internally limited to a maximum of  $30V/\mu s$  in order to meet the EIA standards (EIA RS-232D 2.1.7, Paragraph 5). The transition of the loaded output from HIGH to LOW also meets the monotonicity requirements of the standard.

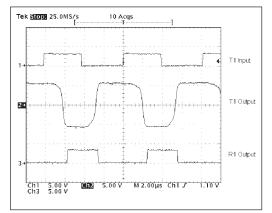

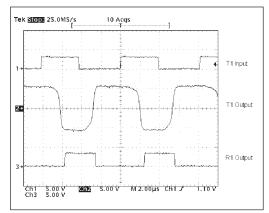

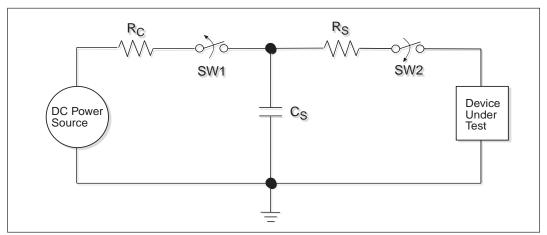

Figure 12 shows a loopback circuit used to test the RS-232 driver. Figure 13 shows the test results of the loopback circuit with the SP3220B driver active at 250Kbps with an RS-232 load in parallel with a 1000pF capacitor. Figure 14 shows the test results where the SP3220U driver was active at 1000Kbps and loaded with an RS-232 receiver in parallel with a 250pF capacitor. A solid RS-232 data transmission rate of 250Kbps provides compatibility with many designs in personal computer peripherals and LAN applications.

The **SP3220B/U** driver's output stage is turned off (high-Z) when the device is in shutdown mode. When the power is off, the **SP3220B/U** device permits the outputs to be driven up to  $\pm 12V$ . The driver's input does not have pull-up resistors. Designers should connect an unused input to  $V_{CC}$  or GND.

In the shutdown mode, the supply current falls to less than  $1\mu A$ , where  $\overline{SHDN} = LOW$ . When the SP3220B/U device is shut down, the device's driver output is disabled (high-Z) and the charge pump is turned off with V+ pulled down to  $V_{cc}$  and V- pulled to GND. The time required to exit shutdown is typically  $100\mu s$ . Connect  $\overline{SHDN}$  to  $V_{cc}$  if the shutdown mode is not used.  $\overline{SHDN}$  has no effect on RxOUT. Note that the driver is enabled only when the magnitude of V- exceeds approximately 3V.

Figure 12. SP3220B/U Driver Loopback Test Circuit

Figure 13. SP3220B Driver Loopback Test Results at 250Kbps

Figure 14. SP3220U Driver Loopback Test Results at 1Mbps

### Receivers

The receiver converts EIA/TIA-232 levels to TTL or CMOS logic output levels. The receiver has an inverting high-impedance output. This receiver output (RxOUT) is at high-impedance when the enable control  $\overline{EN} = HIGH$ . In the shutdown mode, the receiver can be active or inactive.  $\overline{EN}$  has no effect on TxOUT. The truth table logic of the **SP3220B/U** driver and receiver outputs can be found in *Table 2*.

Since receiver input is usually from a transmission line where long cable lengths and system interference can degrade the signal, the inputs have a typical hysteresis margin of 300mV. This ensures that the receiver is virtually immune to noisy transmission lines. Should an input be left unconnected, a  $5k\Omega$  pulldown resistor to ground will commit the output of the receiver to a HIGH state.

# **Charge Pump**

The charge pump is a **Sipex**–patented design (U.S. 5,306,954) and uses a unique approach compared to older less–efficient designs. The charge pump still requires four external capacitors, but uses a four–phase voltage shifting technique to attain symmetrical 5.5V power supplies. The internal power supply consists of a regulated dual charge pump that provides output voltages 5.5V regardless of the input voltage ( $V_{CC}$ ) over the +3.0V to +5.5V range.

| SHDN | EN | TxOUT     | RxOUT     |

|------|----|-----------|-----------|

| 0    | 0  | Tri-state | Active    |

| 0    | 1  | Tri-state | Tri-state |

| 1    | 0  | Active    | Active    |

| 1    | 1  | Active    | Tri-state |

Table 2. Truth Table Logic for Shutdown and Enable Control

In most circumstances, decoupling the power supply can be achieved adequately using a  $0.1\mu F$  bypass capacitor at C5 (refer to Figures 11). In applications that are sensitive to power-supply noise, decouple  $V_{CC}$  to ground with a capacitor of the same value as charge-pump capacitor C1. Physically connect bypass capacitors as close to the IC as possible.

The charge pumps operate in a discontinuous mode using an internal oscillator. If the output voltages are less than a magnitude of 5.5V, the charge pumps are enabled. If the output voltage exceed a magnitude of 5.5V, the charge pumps are disabled. This oscillator controls the four phases of the voltage shifting. A description of each phase follows.

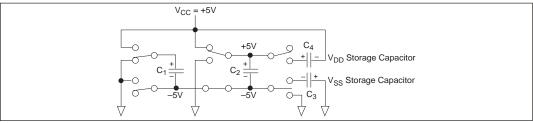

#### Phase 1

—  $V_{ss}$  charge storage — During this phase of the clock cycle, the positive side of capacitors  $C_1$  and  $C_2$  are initially charged to  $V_{cc}$ .  $C_1^+$  is then switched to GND and the charge in  $C_1^-$  is transferred to  $C_2^-$ . Since  $C_2^+$  is connected to  $V_{cc}$ , the voltage potential across capacitor  $C_2$  is now 2 times  $V_{cc}$ .

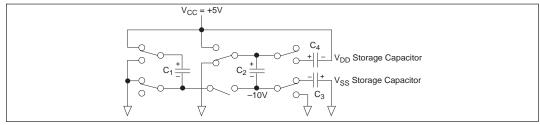

### Phase 2

—  $V_{ss}$  transfer — Phase two of the clock connects the negative terminal of  $C_2$  to the  $V_{ss}$  storage capacitor and the positive terminal of  $C_2$  to GND. This transfers a negative generated voltage to  $C_3$ . This generated voltage is regulated to a minimum voltage of -5.5V. Simultaneous with the transfer of the voltage to  $C_3$ , the positive side of capacitor  $C_1$  is switched to  $V_{cc}$  and the negative side is connected to GND.

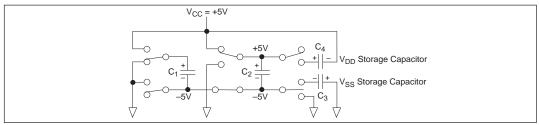

#### Phase 3

—  $V_{DD}$  charge storage — The third phase of the clock is identical to the first phase — the charge transferred in  $C_1$  produces  $-V_{CC}$  in the negative terminal of  $C_1$ , which is applied to the negative side of capacitor  $C_2$ . Since  $C_2^+$  is at  $V_{CC}$ , the voltage potential across  $C_2$  is 2 times  $V_{CC}$ .

#### Phase 4

—  $V_{\rm DD}$  transfer — The fourth phase of the clock connects the negative terminal of  $C_2$  to GND, and transfers this positive generated voltage across  $C_2$  to  $C_4$ , the  $V_{\rm DD}$  storage capacitor. This voltage is regulated to +5.5V. At this voltage, the internal oscillator is disabled. Simultaneous with the transfer of the voltage to  $C_4$ , the positive side of capacitor  $C_1$  is switched to  $V_{\rm CC}$  and the negative side is connected to GND, allowing the charge pump cycle to begin again. The charge pump cycle will continue as long as the operational conditions for the internal oscillator are present.

Since both  $V^+$  and  $V^-$  are separately generated from  $V_{CC}$ ; in a no–load condition  $V^+$  and  $V^-$  will be symmetrical. Older charge pump approaches that generate  $V^-$  from  $V^+$  will show a decrease in the magnitude of  $V^-$  compared to  $V^+$  due to the inherent inefficiencies in the design.

The clock rate for the charge pump typically operates at 250 kHz. The external capacitors can be as low as  $0.1 \mu F$  with a 16V breakdown voltage rating.

### **ESD Tolerance**

The SP3220B/U device incorporates ruggedized ESD cells on all driver output and receiver input pins. The ESD structure is improved over our previous family for more rugged applications and environments sensitive to electro-static discharges and associated transients.

The Human Body Model has been the generally accepted ESD testing method for semiconductors. This method is also specified in MIL-STD-883, Method 3015.7 for ESD testing. The premise of this ESD test is to simulate the human body's potential to store electro-static energy and discharge it to an integrated circuit. The simulation is performed by using a test model as shown in *Figure 20*. This method will test the IC's capability to withstand an ESD transient during normal handling such as in manufacturing areas where the ICs tend to be handled frequently.

Figure 15. Charge Pump — Phase 1

Figure 16. Charge Pump — Phase 2

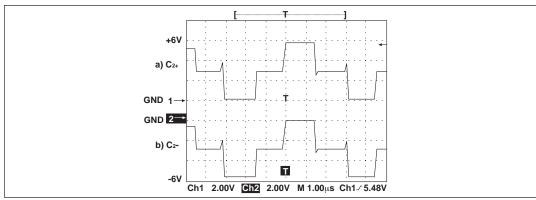

Figure 17. Charge Pump Waveforms

Figure 18. Charge Pump — Phase 3

Figure 19. Charge Pump — Phase 4

Figure 20. ESD Test Circuit for Human Body Model

For the Human Body Model, the current limiting resistor  $(R_{_S})$  and the source capacitor  $(C_{_S})$  are 1.5k $\Omega$  and 100pF, respectively.

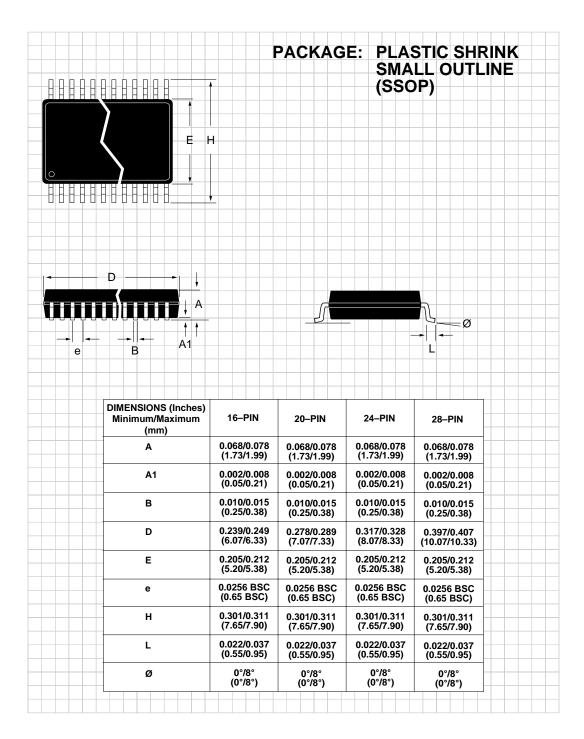

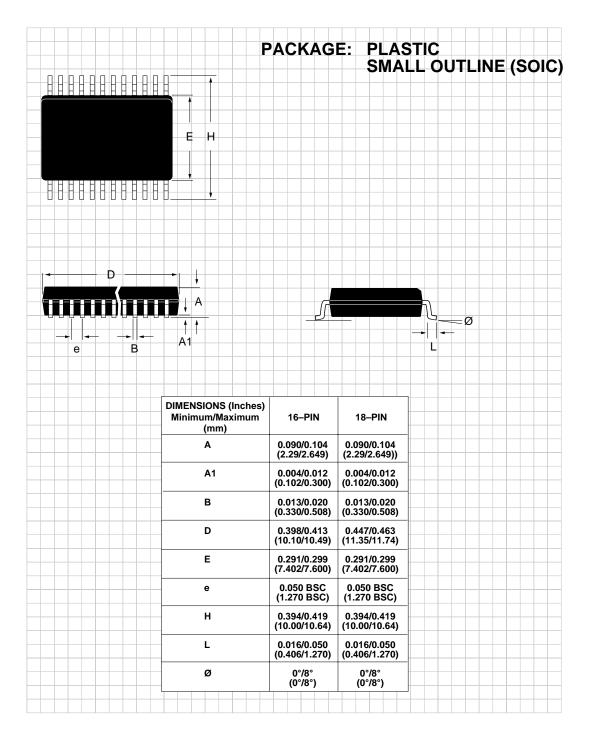

### ORDERING INFORMATION

|           |                | 16-Pin SSOP      |

|-----------|----------------|------------------|

|           |                |                  |

| SP3220BET | -40°C to +85°C | 16-Pin Wide SOIC |

| SP3220UCT |                | 16-Pin Wide SOIC |

|           | 0°C to +70°C   |                  |

| SP3220UET | -40°C to +85°C | 16-Pin Wide SOIC |

ANALOG EXCELLENCE

### **Sipex Corporation**

Headquarters and Sales Office 233 South Hillview Drive Milpitas, CA 95035 TEL: (408) 934-7500 FAX: (408) 935-7600

Sales Office 22 Linnell Circle Billerica, MA 01821 TEL: (978) 667-8700

TEL: (978) 667-8700 FAX: (978) 670-9001 e-mail: sales@sipex.com

Sipex Corporation reserves the right to make changes to any products described herein. Sipex does not assume any liability arising out of the application or use of any product or circuit described hereing; neither does it convey any license under its patent rights nor the rights of others.