October 2002 Revision 1.2

# PC87372 LPC SuperI/O with Glue Functions

## **General Description**

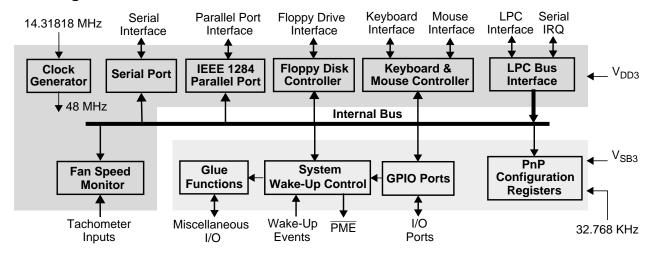

The National Semiconductor® PC87372 Advanced I/O product is a member of the PC8737x SuperI/O family. All PC8737x devices are highly integrated and are pin and software compatible, thus providing drop-in interchangeability and enabling a variety of assembly options using only a single motherboard and BIOS.

PC87372 integration allows for a smaller system board size and saves on total system cost.

The PC87372 includes legacy Superl/O functions, system glue functions, fan monitoring and control, commonly used functions such as GPIO, and ACPI-compliant Power Management support.

The PC87372 integrates miscellaneous analog and digital system glue functions to reduce the number of discrete components required. The host communicates with the functions integrated in the PC87372 device through an LPC Bus Interface.

The PC87372 Legacy functions are: a serial port (UART), a fully compliant IEEE 1284 Parallel Port, a Floppy Disk Controller (FDC) and a Keyboard/Mouse Controller (KBC).

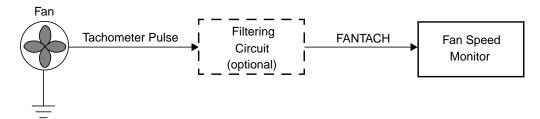

The Fan Speed Monitor (FSM) module allows the system to monitor two fans.

The PC87372 extended wake-up support complements the ACPI controller in the chipset. The System Wake-Up Control (SWC) module, powered by  $V_{SB3}$ , supports a flexible wake-up mechanism.

There are 13 General-Purpose Input/Output (GPIO) ports; these allow system control and wake-up on system events.

#### **Outstanding Features**

- Legacy modules: Parallel Port, Floppy Disk Controller (FDC), Serial Port and a Keyboard and Mouse Controller (KBC)

- Glue functions to complement the South Bridge functionality

- Fan Speed monitoring of two fans

- V<sub>SB3</sub>-powered Power Management with 20 wake-up sources

- Controls three LED indicators

- 13 GPIO ports with a variety of wake-up options

- LPC interface, based on Intel's LPC Interface Specification Revision 1.0, September 29th, 1997

- PC01 Revision 1.0 and Advanced Configuration and Power Interface (ACPI) Specification Revision 2.0 compliant

- 128-pin PQFP package

## **Block Diagram**

National Semiconductor and TRI-STATE are registered trademarks of National Semiconductor Corporation. All other brand or product names are trademarks or registered trademarks of their respective holders.

#### **Features**

#### **Bus Interface**

- LPC Bus Interface

- Based on Intel's LPC Interface Specification Revision 1.0, September 29, 1997

- Synchronous cycles using up to 33 MHz bus clock

- 8-bit I/O read and write cycles

- Up to four 8-bit DMA channels

- Serial IRQ (SERIRQ)

- Reset input (PCI\_RESET)

- Optional power-down support (LPCPD)

- Configuration Control

- PnP Configuration Register structure

- Compliant with PC01 Specification Revision 1.0, 1999-2000

- Base Address strap (BADDR) to setup the address of the Index-Data register pair (defaults to 2Eh/2Fh)

- Flexible resource allocation for all logical devices:

- Relocatable base address

- 15 IRQ routing options to serial IRQ

- Up to four optional 8-bit DMA channels

- Configurable feature sets:

- Software selectable

- □ V<sub>SB3</sub>-powered pin multiplexing

#### **Legacy Modules**

- Serial Port

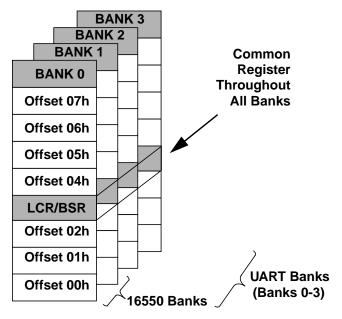

- Software compatible with the NS16550A and the NS16450

- Supports shadow register for write-only bit monitoring

- Data rates up to 1.5 Mbaud

- IEEE 1284-compliant Parallel Port

- ECP, with Level 2 (14 mA sink and source output buffers)

- Software or hardware control

- Enhanced Parallel Port (EPP) compatible with EPP 1.7 and EPP 1.9

- Supports EPP as mode 4 of the Extended Control Register (ECR)

- Selection of internal pull-up or pull-down resistor for Paper End (PE) pin

- Supports a demand DMA mode mechanism and a DMA fairness mechanism for improved bus utilization

- Protection circuit that prevents damage to the parallel port when a printer connected to it is powered up or is operated at high voltages (in both cases, even if the PC87372 is in power-down state)

- Floppy Disk Controller (FDC)

- Software compatible with the PC8477 (the PC8477 contains a superset of the FDC functions in the μDP8473, NEC μPD765A/B and N82077 devices)

- Error-free handling of data overrun and underrun

- Programmable write protect

- Supports FM and MFM modes

- Supports Enhanced mode command for three-mode Floppy Disk Drive (FDD)

- Perpendicular recording drive support for 2.88 MBytes

- Burst (16-byte FIFO) and Non-Burst modes

- Full support for IBM Tape Drive Register (TDR) implementation of AT and PS/2 drive types

- High-performance digital separator

- Supports fast tape drives (2 Mbps) and standard tape drives (1 Mbps, 500 Kbps and 250 Kbps)

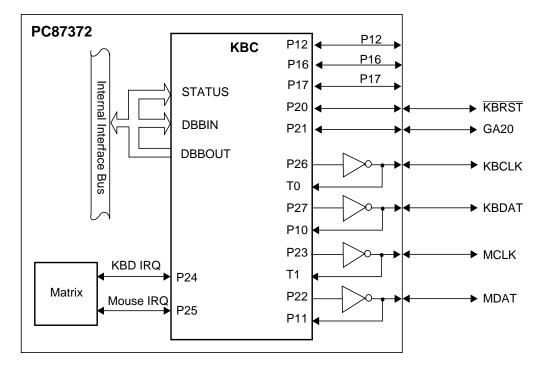

- Keyboard and Mouse Controller (KBC)

- 8-bit microcontroller, software compatible with 8042AH and PC87911

- Standard interface (60h, 64h, IRQ1 and IRQ12)

- Supports two external swapable PS/2 interfaces for keyboard and mouse

- Programmable, dedicated quasi-bidirectional I/O lines (GA20/P21, KBRST/P20)

#### **General-Purpose Modules**

- General-Purpose I/O (GPIO) Ports

- 13 GPIO ports powered by V<sub>SB3</sub>

- Each pin individually configured as input or output

- Programmable features for each output pin:

- Drive type (open-drain, push-pull or TRI-STATE<sup>®</sup>)

- $\Box$  TRI-STATE on detection of falling  $V_{DD3}$  for  $V_{SB3}$ -powered pins driving  $V_{DD}$ -supplied devices

- Programmable option for internal pull-up resistor on each input pin

- Lock option for the configuration and data of each output pin

- 12 GPIO ports generate IRQ/SIOPME for wake-up events; each GPIO has separate:

- □ Enable control of event status routing to IRQ

- □ Enable control of event status routing to SIOPME

- Polarity and edge/level selection

- Programmable debouncing

#### ■ Glue Functions

- Software selectable alternative functionality, through pin multiplexing

- Generates the power-related signals:

- Main Power good

- Power distribution control (for switching between Main and Standby regulators)

- Resume reset (Master Reset) according to the 5V standby supply status

- □ Main power supply turn on (PS\_ON)

- Rambus SCK clock gating

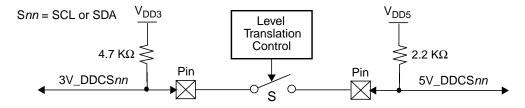

- Voltage translation between 3.3V levels (DDC) and 5V levels (VGA) for the SMBus serial clock and data signals

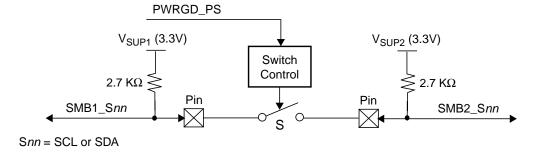

- Isolation circuitry for the SMBus serial clock and data signals

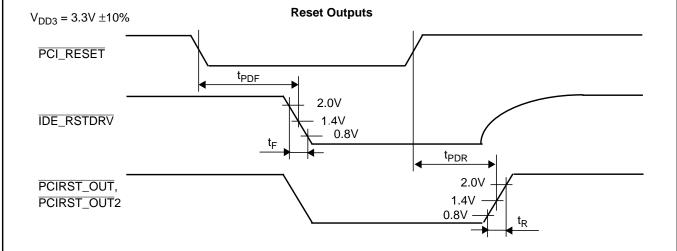

- Buffers PCI\_RESET to generate three reset output signals

#### Features (Continued)

- Generates "highest active supply" reference voltage

- □ Based on 3.3V and 5V Main supplies

- □ Based on 3.3V and 5V Standby supplies

- High-current LED driver control for Hard Disk Drive activity indication

- CNR downstream codec, dynamic control

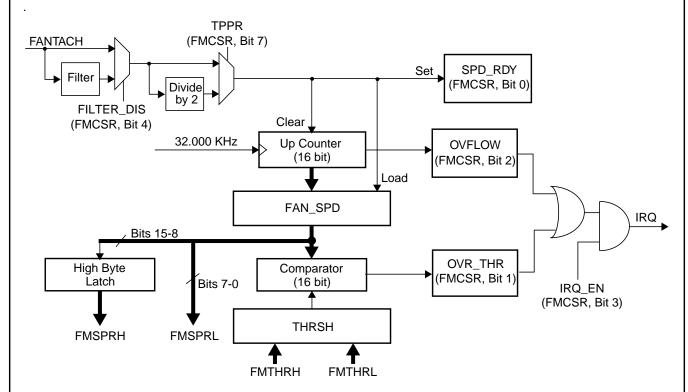

- Fan Speed Monitor (FSM)

- Supports tachometers with one or two pulses per revolution

- Speed monitoring for two fans, including:

- Digital filtering of the tachometer input signal

- □ 16-bit fan speed data

- Alarm for fan speed slower than programed threshold

- Alarm for fan stopped

#### **Power Management**

- Supports ACPI Specification Revision 2.0b, July 27, 2000

- System Wake-Up Control (SWC)

- Optional routing of events to generate SCI (SIOPME) on detection of:

- Keyboard or Mouse events

- □ Ring Indication RI on the serial port

- General-Purpose Input Events from the 12 GPIO pins

- □ IRQs of the Keyboard and Mouse Controller

- IRQs of the other internal modules

- Optional routing of the SCI (SIOPME) to generate IRQ (SERIRQ)

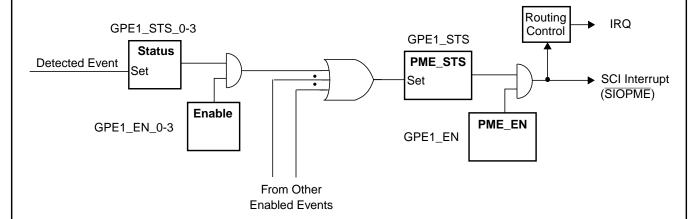

- Implements the GPE1\_BLK of the ACPI General Purpose (Generic) Register blocks with "child" events

- V<sub>SB3</sub>-powered event detection and event-logic configuration

- Enhanced Power Management (PM), including:

- Special configuration registers for power down

- Low-leakage pins

- Low-power CMOS technology

- Ability to disable all modules

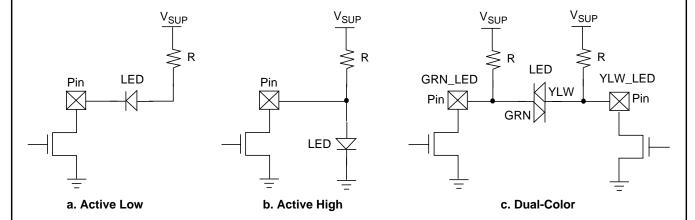

- High-current LED drivers control (two LEDs) for power status indication with:

- Standard blinking, controlled by software

- Advanced blinking, controlled by power supply status, sleep state or software

#### Keyboard Events

- Wake-up on any key

- Supports programmable 8-byte sequence "Password" or "Special Keys" for Power Management

- Simultaneous recognition of three programmable keys (sequences): "Power", "Sleep" and "Resume"

- Wake-up on mouse movement and/or button click

#### Clocking, Supply, and Package Information

#### ■ Clocks

- LPC (PCI) clock input (up to 33 MHz)

- Low-frequency 32.768 KHz clock input, active also in S3-S5 (when V<sub>DD3</sub> is off), for:

- □ System Wake-Up Control (SWC) wake-up timing

- LED blink timing

- Glue Functions timing

- On-chip Clock Generator:

- Generates 48 MHz for the SuperI/O modules and FSM

- □ Based on the 14.31818 MHz clock input

- □ V<sub>DD3</sub> powered

#### ■ Protection

- All device pins are 5V tolerant and back-drive protected (except LPC bus pins

- High ESD protection of all the device pins

- Pin multiplexing selection lock

- Configuration register lock

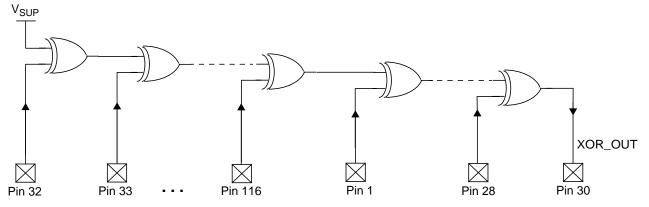

#### Testability

- XOR tree structure

- Includes all the device pins (except the supply and the analog pins)

- □ Selected at power-up by strap input (TEST)

- TRI-STATE device pins, selected at power-up by strap input (TRIS)

#### ■ Power Supply

- 3.3V supply operation

- Separate pin pairs for main ( $V_{DD3}$ ) and standby ( $V_{SB3}$ ) power supplies

- Low standby power consumption

#### ■ Package

— 128-pin PQFP

# **Datasheet Revision Record**

| Revision Date | Status                | Comments               |

|---------------|-----------------------|------------------------|

| January 2002  | Preliminary Datasheet | First issue - Rev 1.0  |

| May 2002      | Datasheet             | Second issue - Rev 1.1 |

| October 2002  | Datasheet             | Third issue - Rev 1.2  |

# Table of Contents

| 1.0 | Sign | nal/Pin Connection and Description                |    |  |  |  |  |  |  |

|-----|------|---------------------------------------------------|----|--|--|--|--|--|--|

|     | 1.1  | CONNECTION DIAGRAMS11                             |    |  |  |  |  |  |  |

|     | 1.2  | BUFFER TYPES AND SIGNAL/PIN DIRECTORY             | 12 |  |  |  |  |  |  |

|     | 1.3  | PIN MULTIPLEXING                                  | 13 |  |  |  |  |  |  |

|     | 1.4  | DETAILED SIGNAL/PIN DESCRIPTIONS                  |    |  |  |  |  |  |  |

|     |      | 1.4.1 LPC Interface                               |    |  |  |  |  |  |  |

|     |      | 1.4.2 Serial Port (UART)                          | 15 |  |  |  |  |  |  |

|     |      | 1.4.3 Parallel Port                               | 16 |  |  |  |  |  |  |

|     |      | 1.4.4 Floppy Disk Controller (FDC)                | 17 |  |  |  |  |  |  |

|     |      | 1.4.5 Keyboard and Mouse Controller (KBC)         | 18 |  |  |  |  |  |  |

|     |      | 1.4.6 General-Purpose I/O (GPIO)                  | 18 |  |  |  |  |  |  |

|     |      | 1.4.7 Fan Speed Monitor (FSM)                     |    |  |  |  |  |  |  |

|     |      | 1.4.8 System Wake-Up Control (SWC)                |    |  |  |  |  |  |  |

|     |      | 1.4.9 Clocks                                      |    |  |  |  |  |  |  |

|     |      | 1.4.10 Glue Functions                             | _  |  |  |  |  |  |  |

|     |      | 1.4.11 Configuration Straps and Testing           |    |  |  |  |  |  |  |

|     |      | 1.4.12 Power and Ground                           |    |  |  |  |  |  |  |

|     | 1.5  | INTERNAL PULL-UP AND PULL-DOWN RESISTORS          | 22 |  |  |  |  |  |  |

| 2.0 | Pow  | ver, Reset and Clocks                             |    |  |  |  |  |  |  |

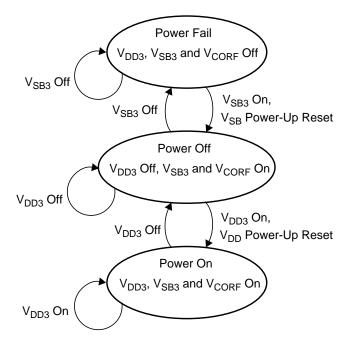

|     | 2.1  | POWER                                             | 24 |  |  |  |  |  |  |

|     |      | 2.1.1 Power Planes                                | 24 |  |  |  |  |  |  |

|     |      | 2.1.2 Power States                                | 24 |  |  |  |  |  |  |

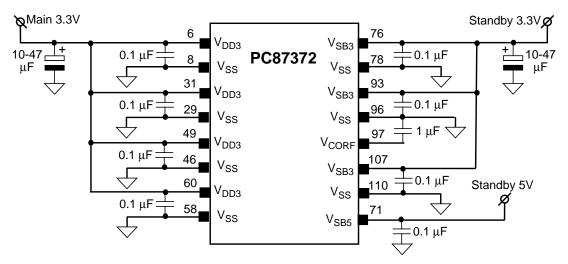

|     |      | 2.1.3 Power Connection and Layout Guidelines      | 25 |  |  |  |  |  |  |

|     | 2.2  | RESET SOURCES AND TYPES                           | 26 |  |  |  |  |  |  |

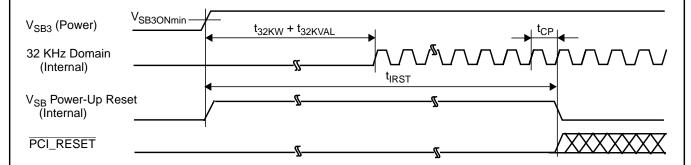

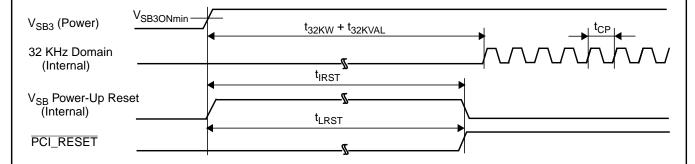

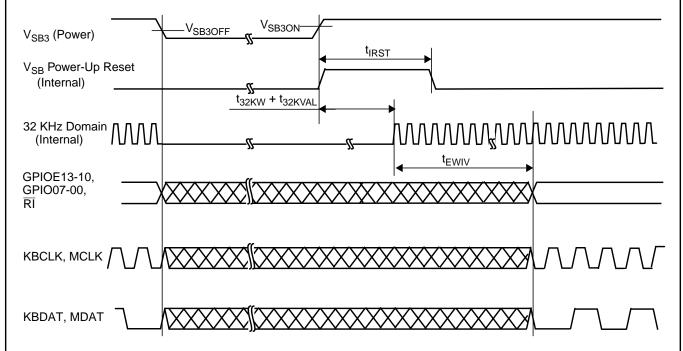

|     |      | 2.2.1 VSB Power-Up Reset                          | 26 |  |  |  |  |  |  |

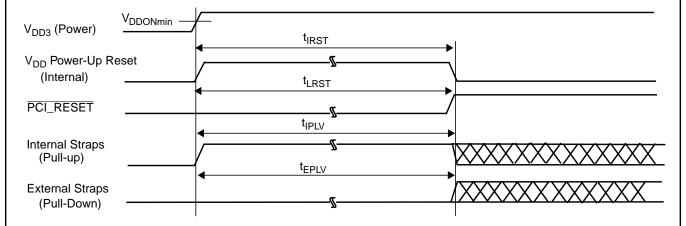

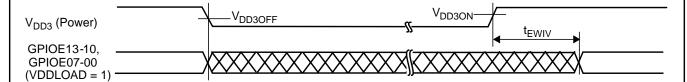

|     |      | 2.2.2 VDD Power-Up Reset                          | 27 |  |  |  |  |  |  |

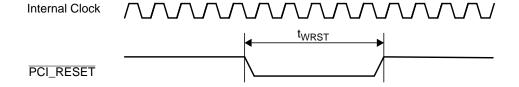

|     |      | 2.2.3 Hardware Reset                              | 27 |  |  |  |  |  |  |

|     |      | 2.2.4 Software Reset                              | 27 |  |  |  |  |  |  |

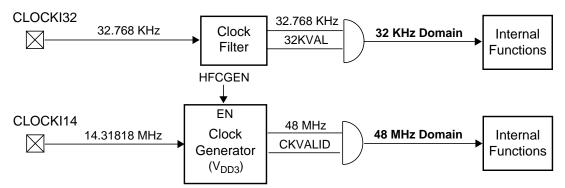

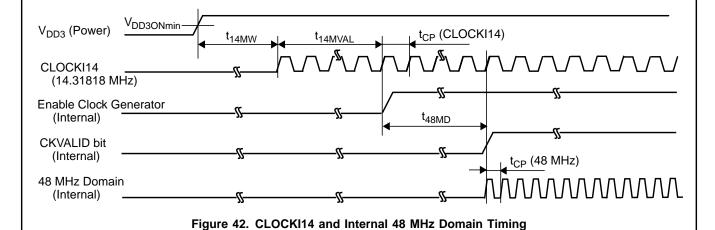

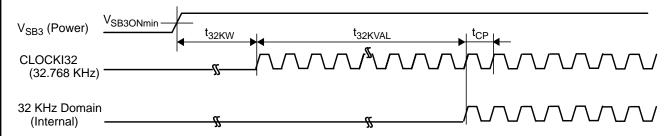

|     | 2.3  | CLOCK DOMAINS                                     | 27 |  |  |  |  |  |  |

|     |      | 2.3.1 LPC Domain                                  | 27 |  |  |  |  |  |  |

|     |      | 2.3.2 48 MHz Domain                               |    |  |  |  |  |  |  |

|     |      | 2.3.3 32 KHz Domain                               | 28 |  |  |  |  |  |  |

|     | 2.4  | TESTABILITY SUPPORT                               | 28 |  |  |  |  |  |  |

|     |      | 2.4.1 ICT                                         |    |  |  |  |  |  |  |

|     |      | 2.4.2 XOR Tree Testing                            | 29 |  |  |  |  |  |  |

| 3.0 | Devi | ice Architecture and Configuration                |    |  |  |  |  |  |  |

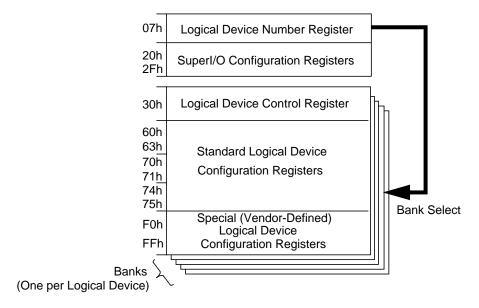

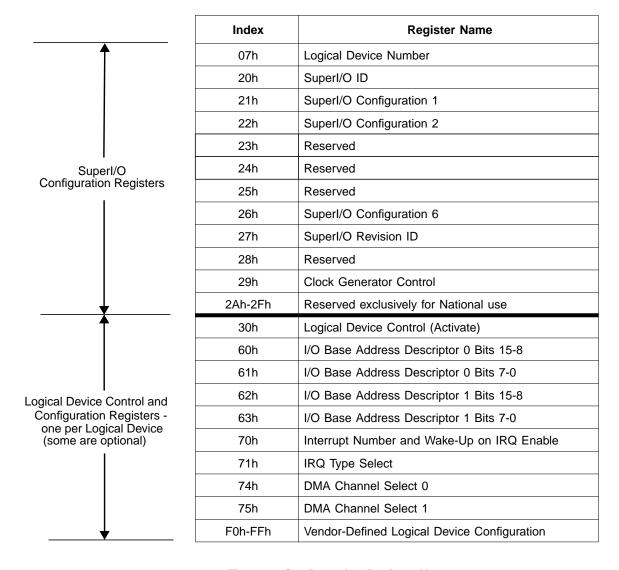

|     | 3.1  | OVERVIEW                                          | 30 |  |  |  |  |  |  |

|     | 3.2  | CONFIGURATION STRUCTURE AND ACCESS                | 30 |  |  |  |  |  |  |

|     |      | 3.2.1 The Index-Data Register Pair                | 30 |  |  |  |  |  |  |

|     |      | 3.2.2 Banked Logical Device Registers Structure   | 31 |  |  |  |  |  |  |

|     |      | 3.2.3 Standard Configuration Register Definitions | 32 |  |  |  |  |  |  |

|     |      | 3.2.4 Standard Configuration Registers            | 34 |  |  |  |  |  |  |

|     |      | 3.2.5 Default Configuration Setup                 | 35 |  |  |  |  |  |  |

|     |      |                                                   |    |  |  |  |  |  |  |

#### Table of Contents (Continued) 3.3 MODULE CONTROL 36 3.3.1 3.3.2 3.4 INTERNAL ADDRESS DECODING ......37 3.5 3.5.1 3.5.2 3.5.3 3.5.4 3.5.5 3.5.6 3.5.7 3.6 3.7 3.7.1 3.7.2 SuperI/O Configuration 1 Register (SIOCF1) ......40 SuperI/O Configuration 2 Register (SIOCF2) ......41 3.7.3 3.7.4 SuperI/O Configuration 6 Register (SIOCF6) ......41 3.7.5 SuperI/O Revision ID Register (SRID) .......42 3.7.6 FLOPPY DISK CONTROLLER (FDC) CONFIGURATION ......44 3.8 3.8.1 Logical Device 0 (FDC) Configuration ......44 3.8.2 3.8.3 FDC Configuration Register ......45 3.8.4 Drive ID Register .......46 PARALLEL PORT (PP) CONFIGURATION ......47 3.9 3.9.1 Logical Device 1 (PP) Configuration ......47 3.9.2 3.9.3 Parallel Port Standard Configuration Register .......48 3.9.4 SERIAL PORT CONFIGURATION ......50 3.10 3.10.1 General Description 50 Logical Device 3 (SP) Configuration ......50 3.10.2 Serial Port Configuration Register ......51 SYSTEM WAKE-UP CONTROL (SWC) CONFIGURATION ......52 3.11 3.11.2 KEYBOARD AND MOUSE CONTROLLER (KBC) CONFIGURATION ......53 3.12.1 Logical Devices 5 and 6 (Mouse and Keyboard) Configuration ......53 3.12.2 KBC Configuration Register ......54 3.12.3 3.13.1 Logical Device 7 (GPIO) Configuration ......56 3.13.2 GPIO Pin Select Register (GPSEL) ......57 3.13.3

| Tabl | e of C     | Contents (Continued)                                                |          |

|------|------------|---------------------------------------------------------------------|----------|

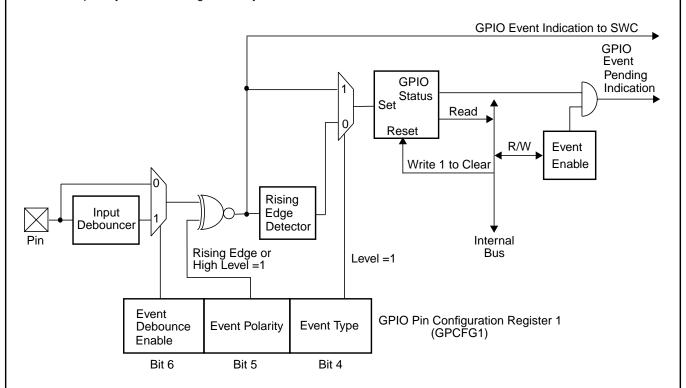

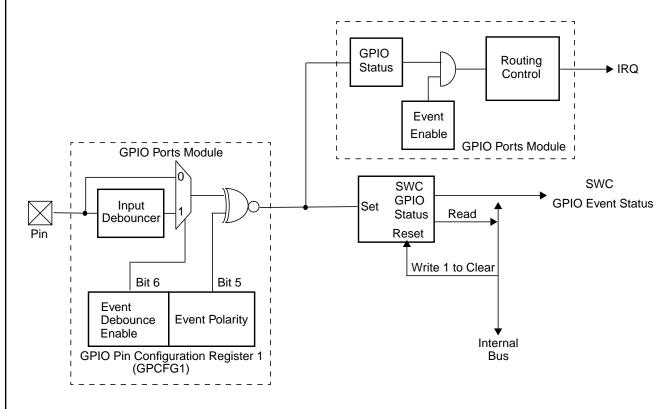

|      |            | 3.13.4 GPIO Pin Configuration Register 1 (GPCFG1)                   | 57       |

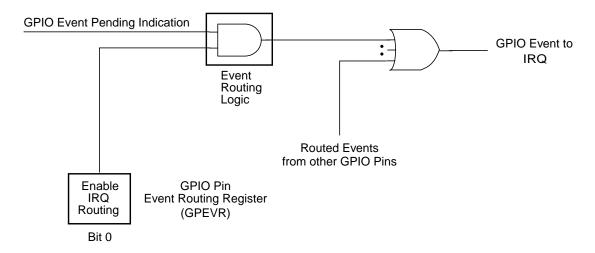

|      |            | 3.13.5 GPIO Event Routing Register (GPEVR)                          |          |

|      |            | 3.13.6 GPIO Pin Configuration Register 2 (GPCFG2)                   | 59       |

|      |            | 3.13.7 GPIO Mode Select Register (GPMODE)                           | 59       |

|      | 3.14       | FAN SPEED MONITOR (FSM) CONFIGURATION                               | 60       |

|      |            | 3.14.1 General Description                                          | 60       |

|      |            | 3.14.2 Logical Device 9 (FSM) Configuration                         |          |

|      |            | 3.14.3 Fan Speed Monitor Configuration Register (FSMCF)             | 61       |

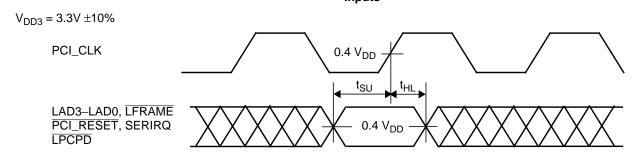

| 4.0  | LPC        | Bus Interface                                                       |          |

|      | 4.1        | OVERVIEW                                                            | 62       |

|      | 4.2        | LPC TRANSACTIONS                                                    | 62       |

|      | 4.3        | LPCPD FUNCTIONALITY                                                 | 62       |

|      | 4.4        | INTERRUPT SERIALIZER                                                | 62       |

|      |            |                                                                     | <u>-</u> |

| 5.0  |            | neral-Purpose Input/Output (GPIO) Ports                             |          |

|      | 5.1        | OVERVIEW                                                            |          |

|      | 5.2        | BASIC FUNCTIONALITY                                                 |          |

|      |            | 5.2.1 Configuration Options                                         |          |

|      |            | ·                                                                   |          |

|      | 5.3        | EVENT HANDLING AND SYSTEM NOTIFICATION                              |          |

|      |            | 5.3.1 Event Configuration                                           |          |

|      | <b>5</b> 4 | •                                                                   |          |

|      | 5.4        | GPIO PORT REGISTERS5.4.1 GPIO Pin Configuration Registers Structure |          |

|      |            | 5.4.2 GPIO Port Runtime Register Map                                |          |

|      |            | 5.4.3 GPIO Data Out Register (GPDO)                                 |          |

|      |            | 5.4.4 GPIO Data In Register (GPDI)                                  |          |

|      |            | 5.4.5 GPIO Event Enable Register (GPEVEN)                           |          |

|      |            | 5.4.6 GPIO Event Status Register (GPEVST)                           |          |

|      |            | 5.4.7 GPIO Data In/Out Register (GPDIO)                             |          |

| 6.0  | Syst       | stem Wake-Up Control (SWC)                                          |          |

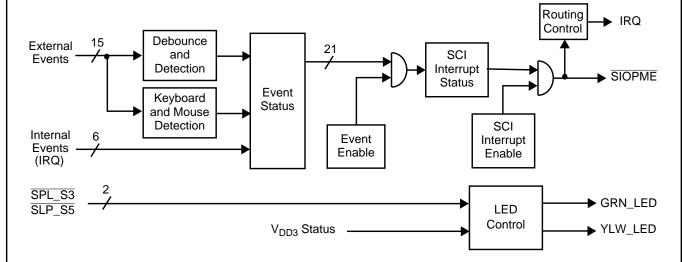

|      | 6.1        | OVERVIEW                                                            | 70       |

|      | 6.2        | FUNCTIONAL DESCRIPTION                                              | 71       |

|      |            | 6.2.1 External Events                                               | 71       |

|      |            | 6.2.2 Internal Events                                               | 74       |

|      |            | 6.2.3 Sleep States                                                  | 74       |

|      |            | 6.2.4 SCI and IRQ Interrupts                                        | 74       |

|      |            | 6.2.5 LED Control                                                   | 75       |

|      | 6.3        | SWC REGISTERS                                                       | 77       |

|      |            | 6.3.1 SWC Register Map                                              | 77       |

|      |            | 6.3.2 Standard LED Control Register (SLEDCTL)                       |          |

|      |            | 6.3.3 SWC Miscellaneous Control Register (SWC_CTL)                  |          |

|      |            | 6.3.4 Advanced LED Control Register (ALEDCTL)                       |          |

|      |            | 6.3.5 LED Blink Control Register (LEDBLNK)                          | 81       |

| Tabl | e of ( | Contents (Continued)                                        |     |

|------|--------|-------------------------------------------------------------|-----|

|      |        | 6.3.6 Keyboard Wake-Up Control Register (KBDWKCTL)          | 82  |

|      |        | 6.3.7 PS2 Protocol Control Register (PS2CTL)                |     |

|      |        | 6.3.8 Keyboard Data Shift Register (KDSR)                   | 84  |

|      |        | 6.3.9 Mouse Data Shift Register (MDSR)                      |     |

|      |        | 6.3.10 PS2 Keyboard Key Data 0 to 7 Registers (PS2KEY0-7)   | 84  |

|      | 6.4    | ACPI REGISTERS                                              | 85  |

|      |        | 6.4.1 ACPI Register Map                                     |     |

|      |        | 6.4.2 General-Purpose Status 1 Register (GPE1_STS)          | 86  |

|      |        | 6.4.3 General-Purpose Enable 1 Register (GPE1_EN)           |     |

|      |        | 6.4.4 General-Purpose Status 1 Register 0 (GPE1_STS_0)      |     |

|      |        | 6.4.5 General-Purpose Status 1 Register 1 (GPE1_STS_1)      | 87  |

|      |        | 6.4.6 General-Purpose Status 1 Register 2 (GPE1_STS_2)      | 88  |

|      |        | 6.4.7 General-Purpose Status 1 Register 3 (GPE1_STS_3)      | 89  |

|      |        | 6.4.8 General-Purpose Enable 1 Register 0 (GPE1_EN_0)       | 90  |

|      |        | 6.4.9 General-Purpose Enable 1 Register 1 (GPE1_EN_1)       | 90  |

|      |        | 6.4.10 General-Purpose Enable 1 Register 2 (GPE1_EN_2)      | 91  |

|      |        | 6.4.11 General-Purpose Enable 1 Register 3 (GPE1_EN_3)      |     |

|      | 6.5    | SYSTEM WAKE-UP CONTROL REGISTER BITMAP                      | 93  |

| 7.0  | Fan    | Speed Monitor                                               |     |

|      | 7.1    | · OVERVIEW                                                  | 95  |

|      | 7.2    | FUNCTIONAL DESCRIPTION                                      | 95  |

|      | 7.3    | FAN SPEED MONITOR REGISTERS                                 |     |

|      | 7.0    | 7.3.1 Fan Speed Monitor Register Map                        |     |

|      |        | 7.3.2 Fan Speed Monitor Threshold Low Register (FMTHRL)     |     |

|      |        | 7.3.3 Fan Speed Monitor Threshold High Register (FMTHRH)    |     |

|      |        | 7.3.4 Fan Speed Monitor Speed Low Register (FMSPRL)         |     |

|      |        | 7.3.5 Fan Speed Monitor Speed High Register (FMSPRH)        | 99  |

|      |        | 7.3.6 Fan Speed Monitor Control and Status Register (FMCSR) |     |

|      | 7.4    | FAN SPEED MONITOR REGISTER BITMAP                           |     |

| 8.0  | Glue   | e Functions                                                 |     |

|      | 8.1    | OVERVIEW                                                    | 101 |

|      | 8.2    | FUNCTIONAL DESCRIPTION                                      | 101 |

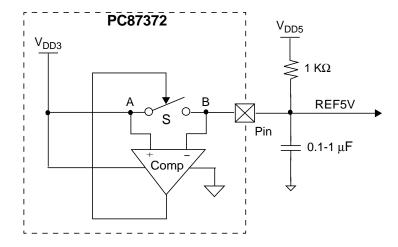

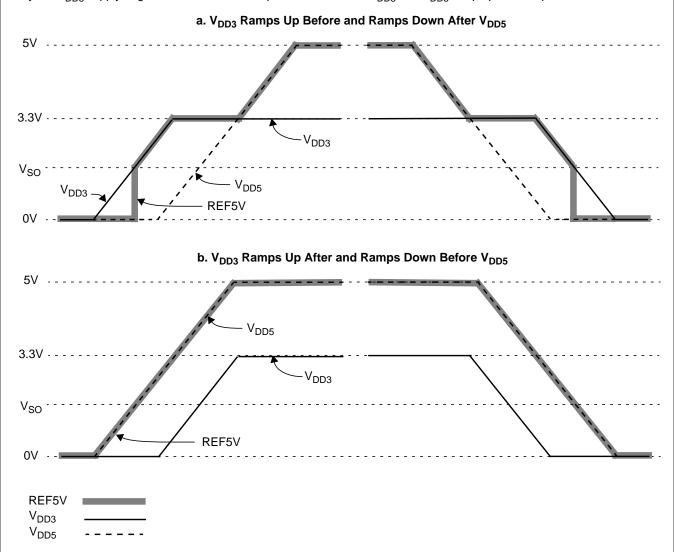

|      |        | 8.2.1 Highest Active Main Supply Reference                  | 101 |

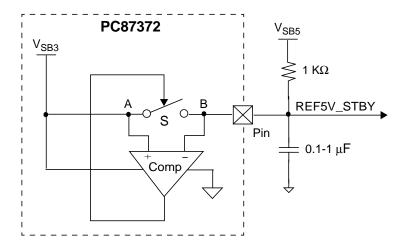

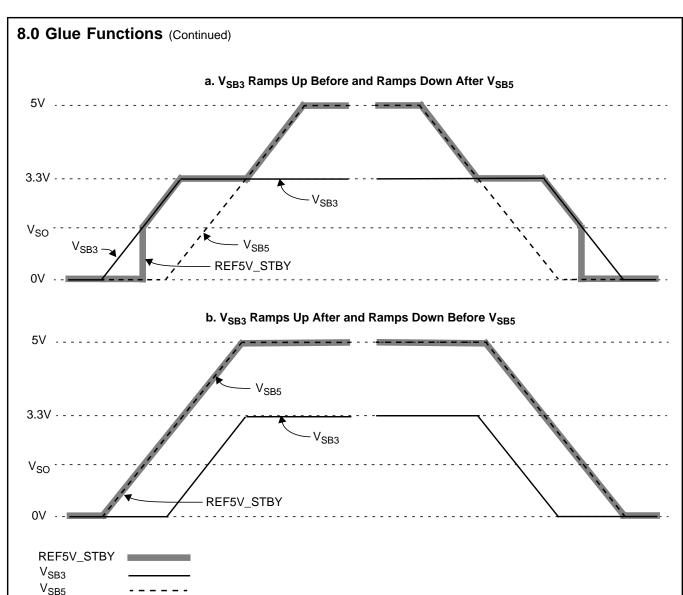

|      |        | 8.2.2 Highest Active Standby Supply Reference               |     |

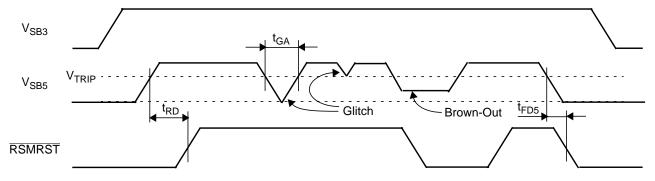

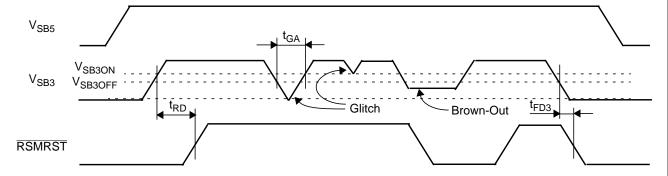

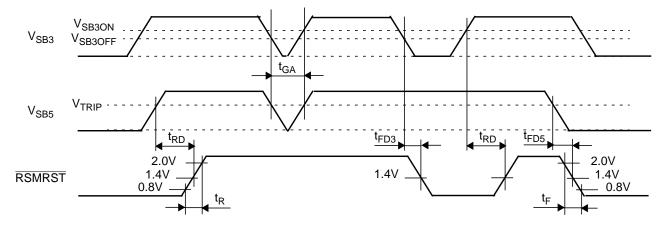

|      |        | 8.2.3 Resume Reset                                          |     |

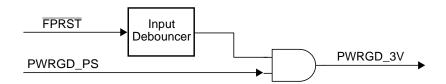

|      |        | 8.2.4 Main Power Good                                       |     |

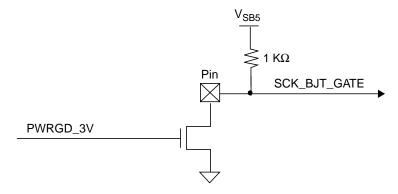

|      |        | 8.2.5 Rambus SCK Clock Gate Control                         | 106 |

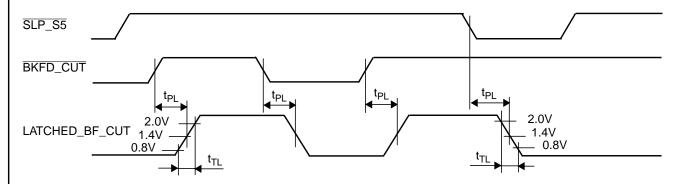

|      |        | 8.2.6 Power Distribution Control                            |     |

|      |        | 8.2.7 Main Power Supply Control                             |     |

|      |        | 8.2.8 CNR Downstream Codec Dynamic Control                  |     |

|      |        | 8.2.9 Hard-Disk LED Indicator Control                       |     |

|      |        | 8.2.10 SMBus Voltage Translation                            |     |

|      |        | 8.2.11 SMBus Isolation                                      |     |

|      |        |                                                             |     |

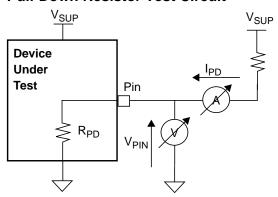

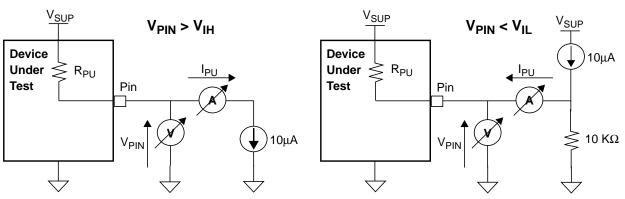

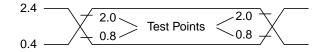

#### Table of Contents (Continued) **Legacy Functional Blocks** 9.0 FLOPPY DISK CONTROLLER (FDC) ......110 9.1 9.1.1 9.1.2 FDC Bitmap Summary ......111 9.2 9.2.1 General Description 112 Parallel Port Register Map .......112 9.2.2 9.2.3 UART FUNCTIONALITY (SERIAL PORT) ......115 9.3 9.3.1 9.3.2 UART Register Bank Overview ......115 9.3.3 9.3.4 SP Bitmap Summary ......117 KEYBOARD AND MOUSE CONTROLLER (KBC) ......119 9.4 9.4.1 9.4.2 9.4.3 10.0 Device Characteristics GENERAL DC ELECTRICAL CHARACTERISTICS ......121 10.1 10.1.2 Absolute Maximum Ratings .......121 10.1.3 10.1.4 10.1.5 DC CHARACTERISTICS OF PINS, BY I/O BUFFER TYPES ......123 10.2 10.2.1 10.2.2 Input, TTL Compatible, with 400 mV Schmitt Trigger ......123 10.2.3 Input, PCI 3.3V Compatible ......124 10.2.4 10.2.5 Output, TTL/CMOS Compatible, Push-Pull Buffer ......124 10.2.6 Output, TTL/CMOS Compatible, Open-Drain Buffer ......124 10.2.7 10.2.8 10.2.9 10.2.10 Input/Output Switch, SMBus Compatible .......125 INTERNAL RESISTORS ......127 10.3 10.3.1 Pull-Down Resistor 127 10.3.2 10.4 10.4.1 10.4.2 10.4.3

# Table of Contents (Continued) 10.4.4 LPC Interface Timing 133 10.4.5 FDC Timing 135 10.4.6 Parallel Port Timing 137 10.4.7 Serial Port Timing 139 10.4.8 Glue Function Timing 140 10.4.9 SWC Timing 143

## 1.0 Signal/Pin Connection and Description

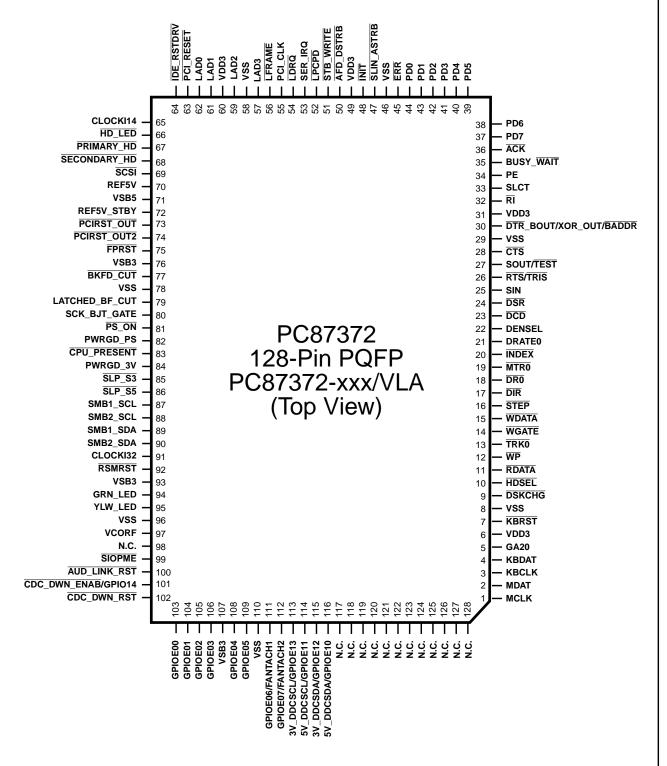

#### 1.1 CONNECTION DIAGRAMS

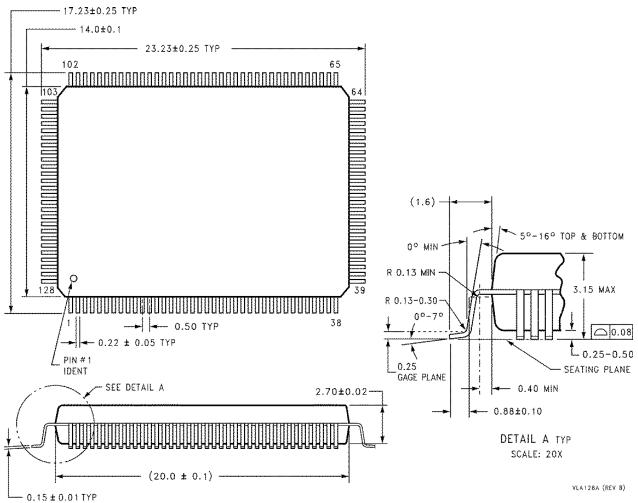

Plastic Quad Flatpack (PQFP), JEDEC Order Number PC87372-xxx/VLA See NS Package Number VLA128A

N.C. = Not Connected xxx = Three-character identifier for National data, and keyboard ROM and/or customer identification code

#### 1.2 BUFFER TYPES AND SIGNAL/PIN DIRECTORY

The signal DC characteristics of the pins described in Section 1.4 on page 14 are denoted by buffer type symbols, which are defined in Table 1 and described in further detail in Section 10.2 on page 123. The pin multiplexing information refers to two different types of multiplexing:

- Multiplexed, denoted by a slash (/) between pins in the diagrams in Section 1.1. Pins are shared between two different functions. Each function is associated with different board connectivity. Normally, the function selection is determined by the board design and cannot be changed dynamically. The multiplexing options must be configured by the BIOS on power-up in order to comply with the board implementation.

- Multiple Mode, denoted by an underscore (\_) between pins in the diagrams in Section 1.1. Pins have two or more modes of operation within the same function. These modes are associated with the same external (board) connectivity. Mode selection may be controlled by the device driver through the registers of the functional block and do not require a special BIOS setup on power-up. These pins are not considered multiplexed pins from the PC87372 configuration perspective. The mode selection method (registers and bits), as well as the signal specification in each mode, are described within the functional description of the relevant functional block.

Table 1. Buffer Types

| Symbol            | Description                                                                                 |

|-------------------|---------------------------------------------------------------------------------------------|

| IN <sub>T</sub>   | Input, TTL compatible                                                                       |

| IN <sub>TS</sub>  | Input, TTL compatible, with Schmitt Trigger                                                 |

| IN <sub>TS4</sub> | Input, TTL compatible, with 400 mV Schmitt Trigger                                          |

| IN <sub>PCI</sub> | Input, PCI 3.3V compatible                                                                  |

| IN <sub>ULR</sub> | Input, power, resistor protected (not characterized)                                        |

| AI                | Input, analog (0-5.5V tolerant)                                                             |

| O <sub>p/n</sub>  | Output, TTL/CMOS compatible, push-pull buffer capable of sourcing $p$ mA and sinking $n$ mA |

| $OD_n$            | Output, TTL/CMOS compatible, open-drain buffer capable of sinking $n$ mA                    |

| O <sub>PCI</sub>  | Output, PCI 3.3V compatible,                                                                |

| AO                | Output, analog (0-5.5V tolerant)                                                            |

| SW <sub>SM</sub>  | Input/Output switch, SMBus compatible                                                       |

| PWR               | Power pin                                                                                   |

| GND               | Ground pin                                                                                  |

#### 1.3 PIN MULTIPLEXING

Table 2 shows only multiplexed pins, their associated functional blocks and the configuration bits for the selection of the multiplexed options used in the PC87372.

**Table 2. Pin Multiplexing Configuration**

| Pin | Default<br>Signal | Function<br>Block | Alternate<br>Signal | Function<br>Block | Alternate<br>Signal | Function<br>Block | Configuration<br>Select | Strap or<br>Wake-Up | Function<br>Block  |

|-----|-------------------|-------------------|---------------------|-------------------|---------------------|-------------------|-------------------------|---------------------|--------------------|

| 30  | DTR_BOUT1         |                   | XOR_OUT             | Config            |                     |                   | TEST (strap)            | BADDR               |                    |

| 26  | RTS               | Serial            |                     |                   |                     |                   |                         | TRIS                | Config<br>(Straps) |

| 27  | SOUT              | Port              |                     |                   |                     |                   |                         | TEST                | ( ,                |

| 32  | RI                |                   |                     |                   |                     |                   |                         | RI                  |                    |

| 3   | KBCLK             |                   |                     |                   |                     |                   |                         | KBCLK               |                    |

| 4   | KBDAT             | KBC               |                     |                   |                     |                   |                         | KBDAT               |                    |

| 1   | MCLK              | NBC               |                     |                   |                     |                   |                         | MCLK                |                    |

| 2   | MDAT              |                   |                     |                   |                     |                   |                         | MDAT                |                    |

| 103 | GPIOE00           |                   |                     |                   |                     |                   |                         | GPIOE00             |                    |

| 104 | GPIOE01           |                   |                     |                   |                     |                   |                         | GPIOE01             |                    |

| 105 | GPIOE02           |                   |                     |                   |                     |                   |                         | GPIOE02             |                    |

| 106 | GPIOE03           |                   |                     |                   |                     |                   |                         | GPIOE03             |                    |

| 108 | GPIOE04           | GPIO              |                     |                   |                     |                   |                         | GPIOE04             |                    |

| 109 | GPIOE05           |                   |                     |                   |                     |                   |                         | GPIOE05             | SWC                |

| 111 | GPIOE06           |                   | FANTACH1            | FSM               |                     |                   | SIOCF2.TACH1EN          | GPIOE06             |                    |

| 112 | GPIOE07           |                   | FANTACH2            | FSIVI             |                     |                   | SIOCF2.TACH2EN          | GPIOE07             |                    |

| 116 | 5V_DDCSDA         |                   | GPIOE10             |                   |                     |                   |                         | GPIOE10             |                    |

| 114 | 5V_DDCSCL         |                   | GPIOE11             |                   |                     |                   | SIOCF2.GPIO03EN         | GPIOE11             |                    |

| 115 | 3V_DDCSDA         |                   | GPIOE12             | GPIO              |                     |                   | SIOCF2.GPIO03EN         | GPIOE12             |                    |

| 113 | 3V_DDCSCL         |                   | GPIOE13             |                   |                     |                   |                         |                     |                    |

| 101 | CDC_DWN_<br>ENAB  |                   | GPIO14              |                   |                     |                   | Note <sup>1</sup>       |                     |                    |

<sup>1.</sup> Both CDC\_DWN\_ENAB and GPIO14 are simultaneously available at the device pin.

# 1.4 DETAILED SIGNAL/PIN DESCRIPTIONS

This section describes all signals of the PC87372 device. The signals are organized by functional group.

#### 1.4.1 LPC Interface

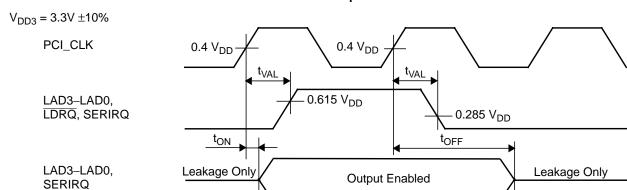

| Signal      | Pin(s)         | I/O | Buffer Type                         | Power Well       | Description                                                                                                                                                                                              |

|-------------|----------------|-----|-------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LAD3-0      | 57,59<br>61,62 | I/O | IN <sub>PCI</sub> /O <sub>PCI</sub> | V <sub>DD3</sub> | LPC Address-Data. Multiplexed command, address bi-directional data and cycle status.                                                                                                                     |

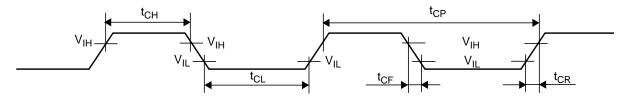

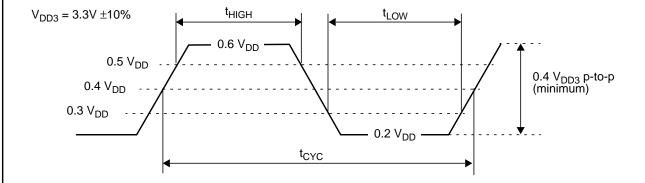

| PCI_CLK     | 55             | ı   | IN <sub>PCI</sub>                   | $V_{DD3}$        | LPC Clock. PCI clock used for the LPC bus (up to 33 MHz).                                                                                                                                                |

| LFRAME      | 56             | I   | IN <sub>PCI</sub>                   | V <sub>DD3</sub> | <b>LPC Frame.</b> Low pulse indicates the beginning of a new LPC cycle or termination of a broken cycle.                                                                                                 |

| LDRQ        | 54             | 0   | O <sub>PCI</sub>                    | $V_{DD3}$        | LPC DMA Request. Encoded DMA request for LPC interface.                                                                                                                                                  |

| PCI_RESET   | 63             | I   | IN <sub>PCI</sub>                   | V <sub>DD3</sub> | <b>LPC Reset.</b> PCI system reset used for the LPC bus (Hardware Reset).                                                                                                                                |

| SER_IRQ     | 53             | I/O | IN <sub>PCI</sub> /O <sub>PCI</sub> | V <sub>DD3</sub> | <b>Serial IRQ.</b> The interrupt requests are serialized over a single pin, where each IRQ level is delivered during a designated time slot.                                                             |

| LPCPD       | 52             | I   | IN <sub>PCI</sub>                   | V <sub>DD3</sub> | <b>Power Down.</b> Indicates that power to the LPC interface is about to be turned off. When LPCPD functionality is not required, an internal pull-up resistor allows this pin to be left floating.      |

| PCIRST_OUT  | 73             | 0   | O <sub>14/14</sub>                  | V <sub>SB3</sub> | <b>PCI Reset Output.</b> PCI system reset. $\overline{\text{PCIRST\_OUT}}$ is a buffered copy of $\overline{\text{PCI\_RESET}}$ when $V_{DD3}$ is on, and it is held at low level when $V_{DD3}$ is off. |

| PCIRST_OUT2 | 74             | 0   | O <sub>14/14</sub>                  | V <sub>SB3</sub> | PCI Reset Output 2. PCI system reset (same behavior as PCIRST_OUT above).                                                                                                                                |

| ĪDE_RSTDRV  | 64             | 0   | OD <sub>6</sub>                     | V <sub>DD3</sub> | IDE Reset Output. IDE drive reset. $\overline{\text{IDE\_RSTDRV}}$ is a buffered copy of $\overline{\text{PCI\_RESET}}$ when $V_{DD3}$ is on, and it is floating when $V_{DD3}$ is off.                  |

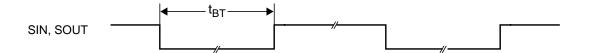

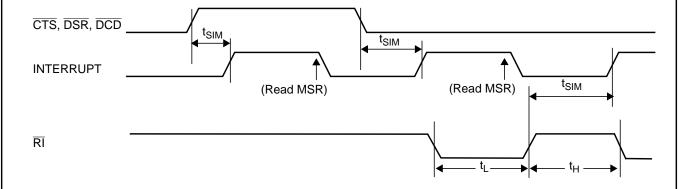

# 1.4.2 Serial Port (UART)

| Signal   | Pin(s) | 1/0 | Buffer Type      | Power Well       | Description                                                                                                                                                                                                                                                                                                                                             |

|----------|--------|-----|------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CTS      | 28     | I   | IN <sub>TS</sub> | V <sub>DD3</sub> | Clear to Send. When low, indicates that the modem or other data transfer device is ready to exchange data.                                                                                                                                                                                                                                              |

| DCD      | 23     | I   | IN <sub>TS</sub> | V <sub>DD3</sub> | Data Carrier Detected. When low, indicates that the modem or other data transfer device has detected the data carrier.                                                                                                                                                                                                                                  |

| DSR      | 24     | I   | IN <sub>TS</sub> | V <sub>DD3</sub> | Data Set Ready. When low, indicates that the data transfer device, e.g., modem, is ready to establish a communications link.                                                                                                                                                                                                                            |

| DTR_BOUT | 30     | 0   | O <sub>3/6</sub> | V <sub>DD3</sub> | Data Terminal Ready. When low, indicates to the modem or other data transfer device that the UART is ready to establish a communications link. After a system reset, these pins provide the DTR function and set these signals to inactive high. Loopback operation holds them inactive.  Baud Output. Provides the associated serial channel baud rate |

|          |        |     |                  |                  | generator output signal if test mode is selected, i.e., bit 7 of EXCR1 register is set.                                                                                                                                                                                                                                                                 |

| RI       | 32     | I   | IN <sub>TS</sub> | V <sub>DD3</sub> | <b>Ring Indicator.</b> When low, indicates that a telephone ring signal was received by the modem. These pins are monitored during $V_{DD}$ power-off for wake-up event detection.                                                                                                                                                                      |

| RTS      | 26     | 0   | O <sub>3/6</sub> | V <sub>DD3</sub> | Request to Send. When low, indicates to the modem or other data transfer device that the corresponding UART is ready to exchange data. A system reset sets these signals to inactive high, and loopback operation holds them inactive.                                                                                                                  |

| SIN      | 25     | I   | IN <sub>TS</sub> | V <sub>DD3</sub> | Serial Input. Receives composite serial data from the communications link (peripheral device, modem or other data transfer device).                                                                                                                                                                                                                     |

| SOUT     | 27     | 0   | O <sub>3/6</sub> | V <sub>DD3</sub> | Serial Output. Sends composite serial data to the communications link (peripheral device, modem or other data transfer device). These signals are set active high after a system reset.                                                                                                                                                                 |

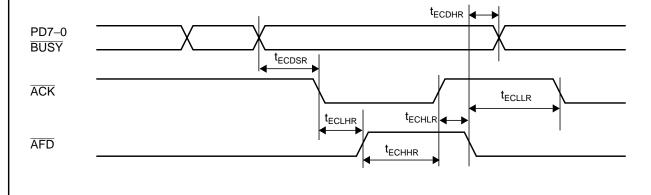

# 1.4.3 Parallel Port

| Signal     | Pin(s) | 1/0 | Buffer Type                           | Power Well         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------|--------|-----|---------------------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

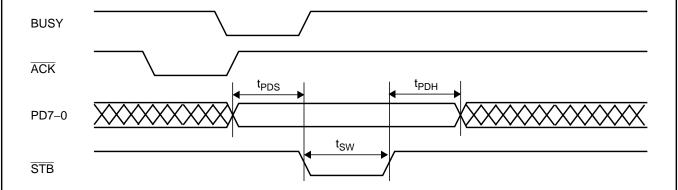

| ĀCK        | 36     | I   | IN <sub>T</sub>                       | V <sub>DD3</sub>   | <b>Acknowledge.</b> Pulsed low by the printer to indicate that it has received data from the parallel port.                                                                                                                                                                                                                                                                                                                                                                     |

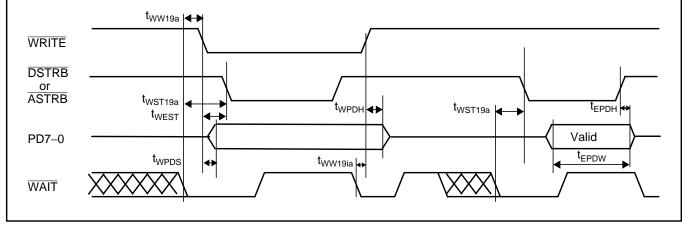

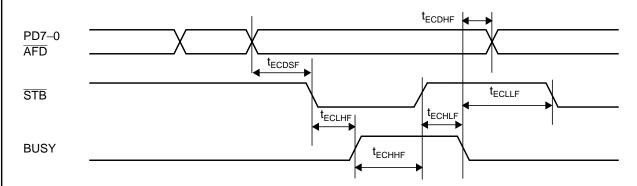

| AFD_DSTRB  | 50     | 0   | OD <sub>14</sub> , O <sub>14/14</sub> | $V_{\mathrm{DD3}}$ | $\overline{\text{AFD}}$ - Automatic Feed. When low, instructs the printer to automatically feed a line after printing each line. This pin is in TRI-STATE after a 0 is loaded into the corresponding control register bit. An external 4.7 KΩ pull-up resistor must be connected to this pin. $\overline{\text{DSTRB}}$ - Data Strobe (EPP). Active low; used in EPP mode to denote a data cycle. When the cycle is aborted, $\overline{\text{DSTRB}}$ becomes inactive (high). |

| BUSY_WAIT  | 35     | I   | IN <sub>T</sub>                       | V <sub>DD3</sub>   | Busy. Set high by the printer when it cannot accept another character.  Wait. In EPP mode, the parallel port device uses this active low signal to extend its access cycle.                                                                                                                                                                                                                                                                                                     |

| ERR        | 45     | ı   | IN <sub>T</sub>                       | V <sub>DD3</sub>   | Error. Set active low by the printer when it detects an error.                                                                                                                                                                                                                                                                                                                                                                                                                  |

| INIT       | 48     | 0   | OD <sub>14</sub> , O <sub>14/14</sub> | V <sub>DD3</sub>   | Initialize. When low, initializes the printer. This signal is in TRI-STATE after a 1 is loaded into the corresponding control register bit. An external 4.7 K $\Omega$ pull-up resistor must be connected to this pin.                                                                                                                                                                                                                                                          |

| PD7-0      | 37-44  | I/O | IN <sub>T</sub> /O <sub>14/14</sub>   | V <sub>DD3</sub>   | Parallel Port Data. Transfers data to and from the peripheral data bus and the appropriate parallel port data register. These signals have a high current drive capability.                                                                                                                                                                                                                                                                                                     |

| PE         | 34     | I   | IN <sub>T</sub>                       | V <sub>DD3</sub>   | Paper End. Set high by the printer when it is out of paper. This pin has an internal weak pull-up or pull-down resistor.                                                                                                                                                                                                                                                                                                                                                        |

| SLCT       | 33     | I   | IN <sub>T</sub>                       | V <sub>DD3</sub>   | <b>Select.</b> Set active high by the printer when the printer is selected.                                                                                                                                                                                                                                                                                                                                                                                                     |

| SLIN_ASTRB | 47     | 0   | OD <sub>14</sub> , O <sub>14/14</sub> | V <sub>DD3</sub>   | SLIN - Select Input. When low, selects the printer. This signal is in TRI-STATE after a 0 is loaded into the corresponding control register bit. An external 4.7 KΩ pull-up resistor must be connected to this pin.  ASTRB - Address Strobe (EPP). Active low, used in EPP mode to denote an address or data cycle. When the cycle is aborted, ASTRB becomes inactive (high).                                                                                                   |

| STB_WRITE  | 51     | 0   | OD <sub>14</sub> , O <sub>14/14</sub> | V <sub>DD3</sub>   | STB - Data Strobe. When low, Indicates to the printer that valid data is available at the printer port. This signal is in TRI-STATE after a 0 is loaded into the corresponding control register bit. An external 4.7 KΩ pull-up resistor must be connected to this pin.  WRITE - Write Strobe. Active low, used in EPP mode to denote an address or data cycle. When the cycle is aborted, WRITE becomes inactive (high).                                                       |

# 1.4.4 Floppy Disk Controller (FDC)

| Signal | Pin(s) | I/O | Buffer Type                          | Power Well       | Description                                                                                                                                                                                |

|--------|--------|-----|--------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DENSEL | 22     | 0   | OD <sub>12</sub> , O <sub>2/12</sub> | V <sub>DD3</sub> | <b>Density Select.</b> Indicates that a high FDC density data rate (500 Kbps, 1 Mbps or 2 Mbps) or a low density data rate (250 or 300 Kbps) is selected.                                  |

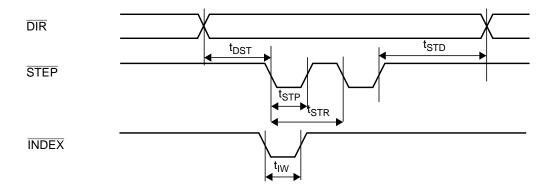

| DIR    | 17     | 0   | OD <sub>12</sub> , O <sub>2/12</sub> | V <sub>DD3</sub> | <b>Direction.</b> Determines the direction of the Floppy Disk Drive (FDD) head movement (active = step in; inactive = step out) during a seek operation.                                   |

| DR0    | 18     | 0   | OD <sub>12</sub> , O <sub>2/12</sub> | V <sub>DD3</sub> | <b>Drive Select.</b> Active low signal controlled by bit 0 of the Digital Output Register (DOR).                                                                                           |

| DRATE0 | 21     | 0   | OD <sub>12</sub> , O <sub>2/12</sub> | V <sub>DD3</sub> | Data Rate. Reflects the value of bit 0 of either Configuration Control Register (CCR) or Data Rate Select Register (DSR), whichever was written to last.                                   |

| DSKCHG | 9      | ı   | IN <sub>TS</sub>                     | V <sub>DD3</sub> | Disk Change. Indicates that the drive door was opened.                                                                                                                                     |

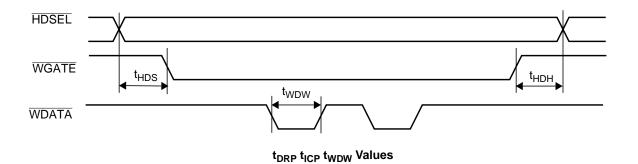

| HDSEL  | 10     | 0   | OD <sub>12</sub> , O <sub>2/12</sub> | V <sub>DD3</sub> | <b>Head Select.</b> Selects which side of the FDD is accessed. Active (low) selects side 1; inactive selects side 0.                                                                       |

| INDEX  | 20     | I   | IN <sub>TS</sub>                     | V <sub>DD3</sub> | Index. Indicates the beginning of an FDD track.                                                                                                                                            |

| MTR0   | 19     | 0   | OD <sub>12</sub> , O <sub>2/12</sub> | V <sub>DD3</sub> | <b>Motor Select.</b> Active low motor enable signal for drive 0, controlled by bit D4 of the Digital Output Register (DOR).                                                                |

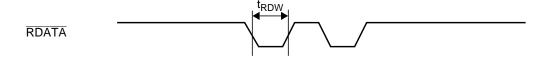

| RDATA  | 11     | ı   | IN <sub>TS</sub>                     | V <sub>DD3</sub> | Read Data. Raw serial input data stream read from the FDD.                                                                                                                                 |

| STEP   | 16     | 0   | OD <sub>12</sub> , O <sub>2/12</sub> | V <sub>DD3</sub> | <b>Step.</b> Issues pulses to the disk drive at a software programmable rate to move the head during a seek operation.                                                                     |

| TRK0   | 13     | Ι   | IN <sub>TS</sub>                     | V <sub>DD3</sub> | <b>Track 0.</b> Indicates to the controller that the head of the selected floppy disk drive is at track 0.                                                                                 |

| WDATA  | 15     | 0   | OD <sub>12</sub> , O <sub>2/12</sub> | V <sub>DD3</sub> | <b>Write Data.</b> Carries out the pre-compensated serial data that is written to the FDD. Pre-compensation is software selectable.                                                        |

| WGATE  | 14     | 0   | OD <sub>12</sub> , O <sub>2/12</sub> | V <sub>DD3</sub> | Write Gate. Enables the write circuitry of the selected FDD. WGATE is designed to prevent glitches during power-up and power-down. This prevents writing to the disk when power is cycled. |

| WP     | 12     | I   | IN <sub>TS</sub>                     | V <sub>DD3</sub> | <b>Write Protected.</b> Indicates that the disk in the selected drive is write protected.                                                                                                  |

# 1.4.5 Keyboard and Mouse Controller (KBC)

| Signal | Pin(s) | I/O | Buffer Type                                            | Power Well       | Description                                                                                                                                                                             |

|--------|--------|-----|--------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| KBCLK  | 3      | I/O | IN <sub>TS</sub> /OD <sub>14</sub>                     | V <sub>DD3</sub> | <b>Keyboard Clock</b> . Keyboard clock signal. External pull-up resistor is required for PS/2 compliance. This pin is monitored during $V_{DD3}$ power-off for wake-up event detection. |

| KBDAT  | 4      | I/O | IN <sub>TS</sub> /OD <sub>14</sub>                     | V <sub>DD3</sub> | <b>Keyboard Data.</b> Keyboard data signal. External pull-up resistor is required for PS/2 compliance. This pin is monitored during $V_{DD3}$ power-off for wake-up event detection.    |

| MCLK   | 1      | I/O | IN <sub>TS</sub> /OD <sub>14</sub>                     | V <sub>DD3</sub> | <b>Mouse Clock.</b> Mouse clock signal. External pull-up resistor is required for PS/2 compliance. This pin is monitored during $V_{DD3}$ power-off for wake-up event detection.        |

| MDAT   | 2      | I/O | IN <sub>TS</sub> /OD <sub>14</sub>                     | V <sub>DD3</sub> | <b>Mouse Data.</b> Mouse data signal. External pull-up resistor is required for PS/2 compliance. This pin is monitored during $V_{DD3}$ power-off for wake-up event detection.          |

| KBRST  | 7      | I/O | IN <sub>T</sub> /OD <sub>8</sub> ,<br>O <sub>4/8</sub> | V <sub>DD3</sub> | KBD Reset. Keyboard reset (P20) quasi-bidirectional output.                                                                                                                             |

| GA20   | 5      | I/O | IN <sub>T</sub> /OD <sub>8</sub> ,<br>O <sub>4/8</sub> | V <sub>DD3</sub> | Gate A20. KBC gate A20 (P21) quasi-bidirectional output.                                                                                                                                |

# 1.4.6 General-Purpose I/O (GPIO)

| Signal                   | Pin(s)              | 1/0 | Buffer Type                                                | Power Well       | Description                                                                                                                                                                                                                                                  |

|--------------------------|---------------------|-----|------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIOE00-07<br>GPIOE10-13 | 108-109,<br>111-112 | I/O | IN <sub>TS</sub> /<br>OD <sub>8</sub> , O <sub>4/8</sub>   | V <sub>SB3</sub> | General-Purpose I/O Ports. Each pin is configured independently as input or I/O, with or without static pull-up and with either open-drain or push-pull output type. These pins have event detection capability to generate a wake-up event or an interrupt. |

| GPIO14                   | 101                 | I/O | IN <sub>TS</sub> /<br>OD <sub>12</sub> , O <sub>2/12</sub> | 353              | General-Purpose I/O Port. This pin is configured independently as input or I/O with or without static pull-up and with either open-drain or push-pull output type.                                                                                           |

# 1.4.7 Fan Speed Monitor (FSM)

| Signal               | Pin(s) | I/O | Buffer Type      | Power Well | Description                                                                                                                                                           |

|----------------------|--------|-----|------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FANTACH1<br>FANTACH2 |        | I   | IN <sub>TS</sub> | 553        | Fan Tachometer Inputs. Input to the Fan Speed Monitor for the fan tachometer pulse. The rising edge indicates the completion of either a half or full fan revolution. |

# 1.4.8 System Wake-Up Control (SWC)

| Signal                    | Pin(s)                          | 1/0 | Buffer Type                        | Power Well       | Description                                                                                                                                                                                                                                        |  |  |

|---------------------------|---------------------------------|-----|------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| GPIOE00-07,<br>GPIOE10-13 | 103-106,<br>108-109,<br>111-116 | I   | IN <sub>TS</sub>                   | V <sub>SB3</sub> | Wake-Up Inputs. Generates a wake-up event. These pins have programmable debouncing. When GPIOE functionality of a pin is not required, the internal pull-up resistor must be enabled to allow the pin to be left floating.                         |  |  |

| RI                        | 32                              | I   | IN <sub>TS</sub>                   | V <sub>SB3</sub> | Ring Indicator Wake-Up. When low, generates a wake-up event, indicating that a telephone ring signal was received by the modem.                                                                                                                    |  |  |

| KBCLK                     | 3                               | I   | IN <sub>TS</sub>                   | V <sub>SB3</sub> | <b>Keyboard Clock Wake-Up.</b> Generates a wake-up event, when a specific keyboard sequence is detected.                                                                                                                                           |  |  |

| KBDAT                     | 4                               | I   | IN <sub>TS</sub>                   | V <sub>SB3</sub> | <b>Keyboard Data Wake-Up.</b> Generates a wake-up event, when a specific keyboard sequence is detected.                                                                                                                                            |  |  |

| MCLK                      | 1                               | I   | IN <sub>TS</sub>                   | V <sub>SB3</sub> | Mouse Clock Wake-Up. Generates a wake-up event, when a specific mouse action is detected.                                                                                                                                                          |  |  |

| MDAT                      | 2                               | I   | IN <sub>TS</sub>                   | V <sub>SB3</sub> | Mouse Data Wake-Up. Generates a wake-up event, when a specific mouse action is detected.                                                                                                                                                           |  |  |

| SIOPME                    | 99                              | 0   | OD <sub>6</sub> , O <sub>3/6</sub> | V <sub>SB3</sub> | Power Management Event (SCI). Active level indicates that a wake-up event occurred, causing the system to exit its current sleep state. This signal has programmable polarity (default is active low).                                             |  |  |

| SLP_S3,<br>SLP_S5         | 85<br>86                        | I   | IN <sub>TS4</sub>                  | V <sub>SB3</sub> | Sleep States 3 to 5. Active (low) level indicates the system is in one of the sleep states S3 or S5. These signals are generated by an external ACPI controller.  Pins SLPS3 SLPS5 Functionality  1 1: Working state (S0) or Sleep states S1 or S2 |  |  |

|                           |                                 |     |                                    |                  | 0 1: Sleep state S3<br>0 0: Sleep state S5<br>1 0: Illegal combination                                                                                                                                                                             |  |  |

| YLW_LED,<br>GRN_LED       | 95, 94                          | 0   | OD <sub>24</sub>                   | V <sub>SB3</sub> | <b>Power LEDs.</b> Yellow and green LED drivers. Each indicates the Main power status or blinks under software control.                                                                                                                            |  |  |

#### 1.4.9 Clocks

| Signal   | Pin(s) | 1/0 | Buffer Type      | Power Well       | ell Description                                                                                                                |  |

|----------|--------|-----|------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------|--|

| CLOCKI32 | 91     | I   | IN <sub>TS</sub> | V <sub>SB3</sub> | <b>Low-Frequency Clock Input.</b> 32.768 KHz clock for the SWC and Glue Functions timing.                                      |  |

| CLOCKI14 | 65     | I   | IN <sub>TS</sub> |                  | <b>High-Frequency Clock Input.</b> 14.31818 MHz clock for the onchip, 48 MHz Clock Generator (for the Legacy modules and FSM). |  |

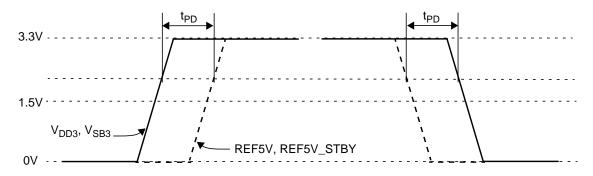

# 1.4.10 Glue Functions

| Signal             | Pin(s) | 1/0 | Buffer Type        | Power Well       | Description                                                                                                                                                                                                                |  |

|--------------------|--------|-----|--------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| REF5V              | 70     | 0   | AO                 | V <sub>SB3</sub> |                                                                                                                                                                                                                            |  |

| REF5V_STBY         | 72     | 0   | AO                 | V <sub>SB3</sub> | Standby Highest Active Supply, Reference Output. Reference voltage equal to the highest voltage between $V_{SB5}$ and $V_{SB3}$ . External pull-up resistor to $V_{SB5}$ is required.                                      |  |

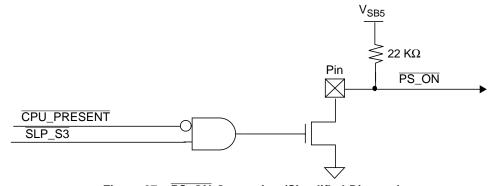

| PS_ON              | 81     | 0   | OD <sub>6</sub>    | V <sub>SB3</sub> | <b>Main Power Supply On/Off Control.</b> Active (low) level turns the main power supply $(V_{DD})$ on. External pull-up resistor to $V_{SB5}$ is required.                                                                 |  |

| PWRGD_PS           | 82     | I   | IN <sub>TS4</sub>  | V <sub>SB3</sub> | Power Good Signal from the Power Supply. Active level indicates the Main power supply voltage is valid.                                                                                                                    |  |

| PWRGD_3V           | 84     | 0   | O <sub>3/6</sub>   | V <sub>SB3</sub> | <b>Power Good Output.</b> Active level indicates the Main supply voltage is valid and the reset button is not pressed.                                                                                                     |  |

| CPU_PRESENT        | 83     | I   | IN <sub>TS4</sub>  | V <sub>SB3</sub> | CPU Present. Active (low) level indicates a processor is currently plugged in.                                                                                                                                             |  |

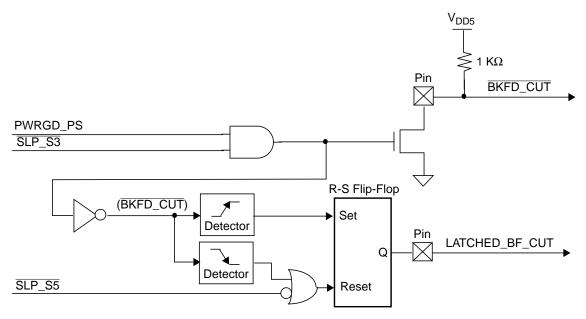

| BKFD_CUT           | 77     | 0   | OD <sub>6</sub>    | V <sub>SB3</sub> | <b>Backfeed-Cut Control.</b> Power distribution control (when switching between main and standby regulators) for system transition into and out of the S3 sleep state. External pull-up resistor to $V_{DD5}$ is required. |  |

| LATCHED_BF_<br>CUT | 79     | 0   | O <sub>14/14</sub> | V <sub>SB3</sub> | Latched Backfeed-Cut. Power distribution control (when switching between main and standby regulators) for system transition into and out of the S5 sleep state.                                                            |  |

| FPRST              | 75     | I   | IN <sub>TS4</sub>  | V <sub>SB3</sub> | Front Panel Reset. Active (low) level indicates that the reset button on the front panel is pressed.                                                                                                                       |  |

| V <sub>SB5</sub>   | 71     | I   | Al                 | V <sub>SB3</sub> | <b>Standby 5V Power Supply.</b> Used for Resume Reset generation (Range: 0-5.5V, Backdrive protected).                                                                                                                     |  |

| RSMRST             | 92     | 0   | O <sub>3/6</sub>   | V <sub>SB3</sub> | <b>Resume Reset.</b> Power-Up reset signal based on the $V_{SB5}$ supply voltage.                                                                                                                                          |  |

| SCK_BJT_GATE       | 80     | 0   | OD <sub>6</sub>    | V <sub>SB3</sub> | Rambus SCK Clock Gate Control. Gates an external circuit that disables the SCK clock to the Rambus socket when the Main supply voltage is invalid. External pull-up resistor to $V_{SB5}$ is required.                     |  |

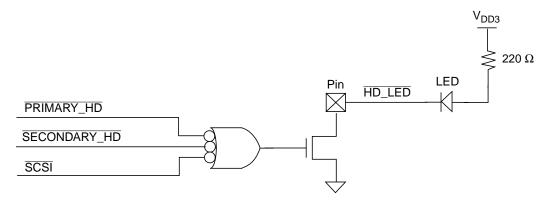

| PRIMARY_HD         | 67     | I   | IN <sub>TS4</sub>  | V <sub>DD3</sub> | <b>Primary Drive.</b> Active (low) level indicates that the primary IDE drive is active.                                                                                                                                   |  |

| SECONDARY_HD       | 68     | I   | IN <sub>TS4</sub>  | V <sub>DD3</sub> | <b>Secondary Drive.</b> Active (low) level indicates that the secondary IDE drive is active.                                                                                                                               |  |

| SCSI               | 69     | I   | IN <sub>TS4</sub>  | V <sub>DD3</sub> | <b>SCSI Drive.</b> Active (low) level indicates that the SCSI drive is active.                                                                                                                                             |  |

| HD_LED             | 66     | 0   | OD <sub>12</sub>   | V <sub>DD3</sub> | <b>Hard Drive LED.</b> Red LED driver. When low, indicates that at least one drive is active.                                                                                                                              |  |

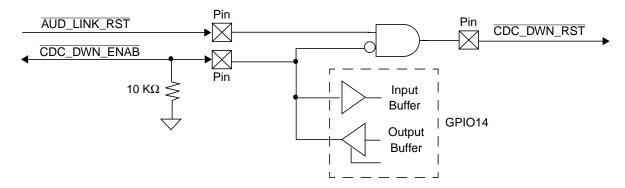

| AUD_LINK_RST       | 100    | I   | IN <sub>T</sub>    | V <sub>SB3</sub> | Audio Link Reset. Controls the downstream codec.                                                                                                                                                                           |  |

| CDC_DWN_ENAB       | 101    | I   | IN <sub>T</sub>    | V <sub>SB3</sub> | Downstream Codec Enable. Controls the downstream codec. The GPIO14 signal is also connected to this pin, allowing the software to control both this input and externa input pins connected to it.                          |  |

| CDC_DWN_RST        | 102    | 0   | O <sub>2/12</sub>  | $V_{SB3}$        | <b>Downstream Codec Reset.</b> Enables the audio CNR Board.                                                                                                                                                                |  |

| Signal    | Pin(s) | 1/0 | Buffer Type      | Power Well                                                                                                                                                                          | Description                                                                                                                                                   |

|-----------|--------|-----|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3V_DDCSCL | 113    | I/O | SW <sub>SM</sub> | V <sub>SB3</sub> 3.3V Level DDC Serial Clock. SMBus serial clock with 3.3V logic levels for Data Display Channel inte External pull-up resistor to V <sub>DD3</sub> is required.    |                                                                                                                                                               |

| 5V_DDCSCL | 114    | I/O | SW <sub>SM</sub> | V <sub>SB3</sub> 5V Level DDC Serial Clock. SMBus serial clock sign 5V logic levels for VGA monitor interface. External puresistor to V <sub>DD5</sub> is required.                 |                                                                                                                                                               |

| 3V_DDCSDA | 115    | I/O | SW <sub>SM</sub> | V <sub>SB3</sub> 3.3V Level DDC Serial Data. SMBus serial data sign 3.3V logic levels for Data Display Channel interface External pull-up resistor to V <sub>DD3</sub> is required. |                                                                                                                                                               |

| 5V_DDCSDA | 116    | I/O | SW <sub>SM</sub> | V <sub>SB3</sub>                                                                                                                                                                    | <b>5V Level DDC Serial Data.</b> SMBus serial data signal with 5V logic levels for VGA monitor interface. External pull-up resistor to $V_{DD5}$ is required. |

| SMB1_SCL  | 87     | I/O | SW <sub>SM</sub> | V <sub>SB3</sub>                                                                                                                                                                    | <b>Bus 1 Serial Clock.</b> Serial clock signal of SMBus 1 (3.3V logic levels). External pull-up resistor to the 3.3V supply is required.                      |

| SMB2_SCL  | 88     | I/O | SW <sub>SM</sub> | V <sub>SB3</sub>                                                                                                                                                                    | <b>Bus 2 Serial Clock.</b> Serial clock signal of SMBus 2 (3.3V logic levels). External pull-up resistor to the 3.3V supply is required.                      |

| SMB1_SDA  | 89     | I/O | SW <sub>SM</sub> | V <sub>SB3</sub>                                                                                                                                                                    | <b>Bus 1 Serial Data.</b> Serial data signal of SMBus 1 (3.3V logic levels). External pull-up resistor to the 3.3V supply is required.                        |

| SMB2_SDA  | 90     | I/O | SW <sub>SM</sub> | V <sub>SB3</sub>                                                                                                                                                                    | <b>Bus 2 Serial Data.</b> Serial data signal of SMBus 2 (3.3V logic levels). External pull-up resistor to the 3.3V supply is required.                        |

# 1.4.11 Configuration Straps and Testing

| Signal | Pin(s) | I/O | Buffer Type      | Power Well       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------|--------|-----|------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BADDR  | 30     | I   | IN <sub>TS</sub> | V <sub>DD3</sub> | Base Address. Sampled at $V_{DD}$ Power-Up reset to determine the base address of the configuration Index-Data register pair, as follows:  No pull-down resistor (default) - 2Eh-2Fh  10 $K\Omega^1$ external pull-down resistor - 4Eh-4Fh The external pull-down resistor must be connected to $V_{SS}$ .                                                                                                                                              |

| TRIS   | 26     | I   | IN <sub>TS</sub> | V <sub>DD3</sub> | <b>TRI-STATE Device.</b> Sampled at $V_{DD}$ Power-Up reset to force the device to float all its output and I/O pins. No pull-down resistor (default) - normal pin operation – 10 $K\Omega^1$ external pull-down resistor - floating device pins – The external pull-down resistor must be connected to $V_{SS}$ . When $\overline{TRIS}$ is set to 0 (by an external pull-down resistor), $\overline{TEST}$ must be 1 (left unconnected).              |

| TEST   | 27     | I   | IN <sub>TS</sub> | V <sub>DD3</sub> | <b>XOR Tree Test Mode.</b> Sampled at $V_{DD}$ Power-Up reset to force the device pins into a XOR tree configuration.  - No pull-down resistor (default) - normal device operation - 10 $K\Omega^1$ external pull-down resistor - pins configured as XOR tree.  The external pull-down resistor must be connected to $V_{SS}$ . When $\overline{TEST}$ is set to 0 (by an external pull-down resistor), $\overline{TRIS}$ must be 1 (left unconnected). |

| Signal  | Pin(s) | I/O | Buffer Type      | Power Well | Description                                                                                                                            |

|---------|--------|-----|------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------|

| XOR_OUT | 30     | 0   | O <sub>3/6</sub> | 550        | <b>XOR Tree Output.</b> All the device pins (except power type and analog type pins) are internally connected in a XOR tree structure. |

<sup>1.</sup> Because the strap function is multiplexed with the Serial Port pins, a CMOS transceiver device is recommended for Serial Port functionality; in this case, the value of the external pull-down resistor is 10 KΩ. If, however, a TTL transceiver device is used, the value of the external pull-down resistor must be 470Ω, and since the Serial Port pins are not able to drive this load, the external pull-down resistor must be disconnected t<sub>EPLV</sub> after V<sub>DD3</sub> power-up (see "VDD Power-Up Reset" on page 130).

#### 1.4.12 Power and Ground

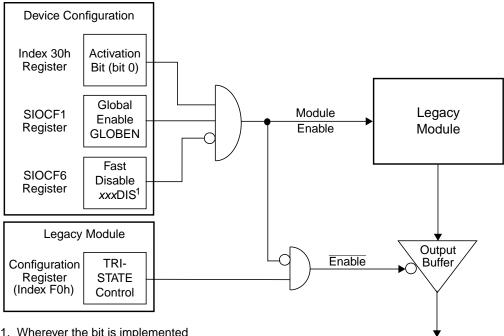

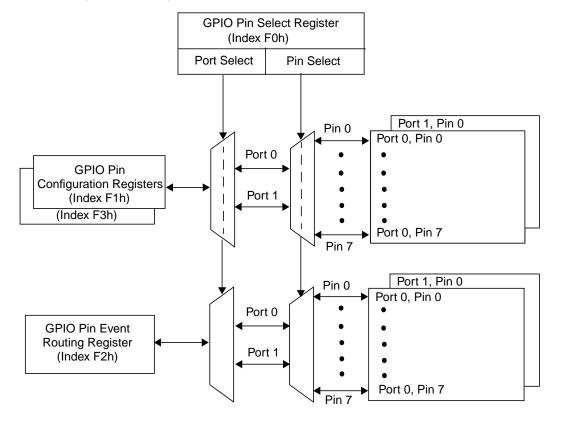

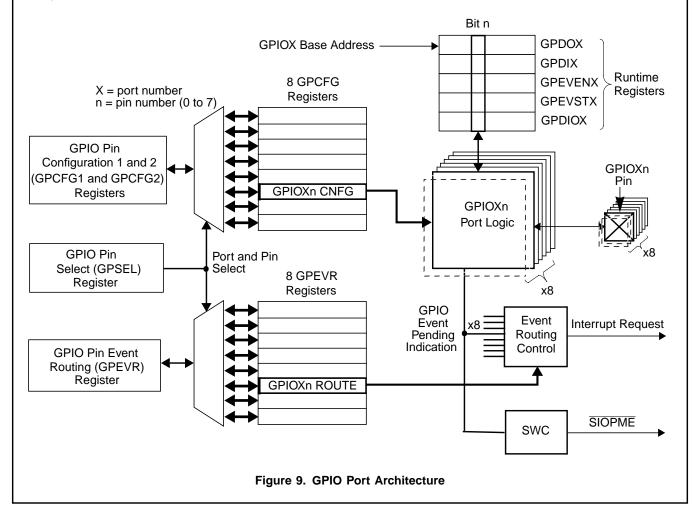

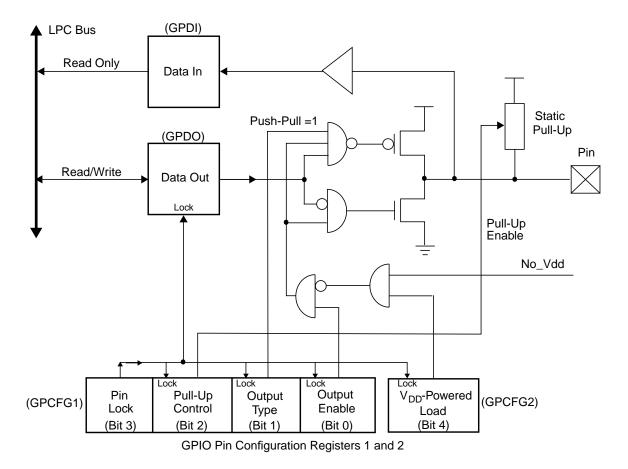

| Signal            | Pin(s)                        | I/O | Buffer Type | Power<br>Well | Description                                                                                                                                                                                                                        |  |